Изобретение относится к автоматике и вычислительной технике и может быть использовано в локальных вычислительных сетях (ЛВС) в качестве станции ЛВС, реализующей интервально-маркерный метод доступа к общей шине с динамически меняющимся интервалом передачи.

Наиболее близким к предлагаемому изобретению техническим решением является устройство для сопряжения источника и приемника информации [1].

Недостатком известного устройства являются ограниченные функциональные возможности.

Целью предлагаемого изобретения является расширение функциональных возможностей устройства.

Поставленная цель достигается тем, что в устройство, содержащее входной регистр, блок элементов И, первый, второй и третий элементы задержки, первый и второй элементы ИЛИ, схему сравнения, первый и второй счетчики адреса, триггер, первый и второй элементы И, блок памяти (БП), содержащий первый и второй дешифраторы, блок элементов ИЛИ, N информационных регистров, N блоков элементов И первой группы, N блоков элементов И второй группы, информационный вход устройства, вход стробирования записи устройства, вход стробирования чтения устройства, вход начальной установки устройства, информационный выход устройства, выход «Готовность записи» устройства и выход «Готовность чтения» устройства, причем первый вход первого элемента ИЛИ является входом начальной установки устройства, выход первого элемента ИЛИ соединен со входами установки первого счетчика адреса, триггера и с установочными входами N информационных регистров, первый вход блока элементов И является информационным входом устройства, второй вход блока элементов И соединен со входом первого элемента задержки и является входом стробирования записи устройства, выход блока элемента И соединен с информационным входом входного регистра, выход которого соединен с соответствующими информационными входами N блоков элементов И первой группы, выходы которых соединены с входами данных N информационных регистров, выходы которых соединены с информационными входами N блоков элементов И второй группы, выходы которых соединены с соответствующими входами блока элементов ИЛИ, выход которого является информационным выходом устройства, выходы первого счетчика адреса соединены со входами первого дешифратора, выходы которого соединены с соответствующими стробирующими входами N блоков элементов И второй группы, выход первого элемента задержки соединен с первым входом первого элемента И, выход которого соединен с соответствующими первыми стробирующими входами N блоков элементов И первой группы и с входом второго элемента задержки, выход которого соединен со счетным входом второго счетчика адреса, выход переполнения которого соединен с единичным входом триггера, прямой и инверсный выходы которого соединены соответственно с первым входом второго элемента ИЛИ и вторым входом первого элемента И, инверсный выход триггера является выходом готовности записи устройства, выход второго элемента ИЛИ соединен с первым входом второго элемента И, второй вход которого является входом стробирования чтения устройства, а выход второго элемента ИЛИ является выходом готовности чтения устройства, выход второго элемента И соединен со вторыми стробирующими входами N блоков элементов И второй группы и с входом третьего элемента задержки, выход которого соединен со счетным входом первого счетчика адреса, выход переполнения которого соединен со вторым входом первого элемента ИЛИ, выход которого соединен с установочным входом второго счетчика адреса, информационные выходы которого соединены с входами второго дешифратора адреса и с первой группой входов схемы сравнения, вторая группа входов которой соединена с информационными выходами первого счетчика адреса, выход схемы сравнения соединен со вторым входом второго элемента ИЛИ, выходы второго дешифратора соединены с соответствующими вторыми стробирующими входами N блоков элементов И первой группы, дополнительно введены второй блок буферной памяти, выполненный идентично первому (ББП2), блок приемника (ПРМ), блок передатчика (ПРД) и управляющий блок (УУ), первый информационный вход устройства, первый информационный выход устройства, вход стробирования чтения устройства, первый вход начальной установки устройства, вход кода адреса устройства, вход кода «маркер» устройства, вход кода «конец сообщения» устройства, вход кода длины сообщения устройства, вход «код интервала» устройства, выход «сообщение передано» устройства, выход «восстановить таймер» устройства, второй информационный вход устройства, вход стробирования записи устройства, второй вход начальной установки устройства, второй информационный выход устройства, причем информационный вход ПРМ является первым информационным входом устройства, вход кода «конец сообщения» ПРМ соединен со входом кода «конец сообщения» ПРД и является входом кода конца сообщения устройства, вход кода «маркер» ПРМ соединен с входом кода «маркер» ПРД и является входом кода маркера устройства, вход кода адреса ПРМ является входом кода адреса устройства, информационный выход ПРМ соединен с информационным входом первого блока буферной памяти (ББП1), выход стробирования записи ПРМ соединен со входом стробирования записи ББП1, выход «маркер» ПРМ соединен со входом «маркер» УУ, вход стробирования чтения ББП1 является входом стробирования чтения устройства, вход начальной установки ББП1 является первым входом начальной установки устройства, информационный выход ББП1 является первым информационным выходом устройства, вход кода длины сообщения УУ является входом кода длины сообщения устройства, вход «код интервала» УУ является входом кода интервала устройства, выход «сообщение передано» УУ является выходом устройства «сообщение передано», выход «восстановить таймер» УУ является выходом устройства «восстановить таймер», выход «0 счетчика слов» УУ соединен со входом «0 счетчика слов» ПРД, выход ТИ УУ соединен со входом ТИ ПРД, выход «запуск» УУ соединен со входом «запуск» ПРД, выход «передать маркер» УУ соединен со входом «передать маркер» ПРД, выход «0 таймера» УУ соединен со входом «0 таймера» ПРД, информационный вход ББП2 является вторым информационным входом устройства, вход стробирования записи ББП2 является входом стробирования записи устройства, вход начальной установки ББП2 является вторым входом начальной установки устройства, информационный выход ББП2 соединен с информационным входом ПРД, выход стробирования чтения которого соединен со входом стробирования чтения ББП2 и со входом стробирования чтения УУ, информационный вход ПРД является вторым информационным выходом устройства,

блок приемника содержит блок приема сигналов, буферный регистр, выходной регистр, схему выделения байта «маркер», схему выделения байта «конец сообщения», схему сравнения адресов, триггер разрешения сравнения адресов, триггер приема информации, счетчик байтов, первый, второй и третий элементы задержки, первый, второй и третий элементы И, перший и второй элементы ИЛИ, блок элементов И, информационный вход ИРМ, вход кода «конец сообщения» ПРМ, вход кода адреса ПРМ, информационный выход ПРМ, выход стробирования записи ПРМ, выход «маркер» ПРМ, причем вход блока приема сигналов является информационным входом ПРМ, первый выход которого соединен со входом буферного регистра, выход которого соединен с первым входом схемы выделения байта «маркер», с первым входом схемы выделения байта «конец сообщения», с первым входом схемы сравнения адресов и с первым входом блока элементов И, выход которого соединен со входом выходного регистра, выход которого является информационным выходом ПРМ, второй выход блока приема сигналов соединен со входом первого элемента задержки, выход которого соединен с третьим входом схемы выделения байта «конец сообщения», с третьим входом схемы сравнения адресов, с первым входом первого элемента И и с третьим входом схемы выделения байта «маркер», выход которого является выходом «маркер» ПРМ и соединен с первым входом первого элемента ИЛИ, выход которого соединен со вторым входом триггера разрешения сравнения адресов, выход которого соединен со вторым входом первого элемента И и с четвертым входом схемы сравнения адресов, выход которого соединен со вторым входом триггера приема информации, выход которого соединен с первым входом второго элемента И, выход которого соединен со входом третьего элемента задержки, с третьим входом блока элементов И и со входом счетчика байтов, первый выход которого соединен со вторым входом блока элементов И, второй выход счетчика байтов соединен с первым входом третьего элемента И, выход которого является выходом стробирования записи ПРМ, третий выход блока приема сигналов соединен с первым входом второго элемента ИЛИ, выход которого соединен с первым входом триггера разрешения сравнения адресов, второй вход схемы выделения байта «маркер» является входом кода «маркер» ПРМ, второй вход схемы сравнения адресов является входом кода адреса ПРМ, второй вход схемы выделения байта «конец сообщения» является входом кода «конец сообщения» ПРМ, первый выход схемы выделения байта «конец сообщения» соединен со вторым входом первого элемента ИЛИ и с первым входом триггера приема информации, второй выход схемы выделения байта «конец сообщения» соединен со входом второго элемента задержки, выход которого соединен со вторым входом второго элемента И, выход третьего элемента задержки соединен со вторым входом третьего элемента И, выход первого элемента И соединен со вторым входом второго элемента ИЛИ,

блок передатчика содержит блок формирования манчестерского кода, счетчик байтов, регистр приема информации, триггер, формирующий управляющий сигнал передачи сообщения, триггер, формирующий сигнал маркера, триггер, формирующий сигнал конца сообщения буферный, триггер, формирующий сигнал конца сообщения, триггер, формирующий сигнал конца передачи, блок элементов И-ИЛИ, одиннадцать элементов И, четыре элемента ИЛИ, два элемента НЕ, шесть элементов задержки, информационный вход ПРД, вход кода «конец сообщения» ПРД, вход кода «маркер» ПРД, вход ТИ ПРД, вход «запуск» ПРД, вход «передать маркер» ПРД, вход «0 таймера» ПРД, вход «0 счетчика слов» ПРД, информационный выход ПРД, выход стробирования чтения ПРД, причем вход регистра приема информации является информационным входом ПРД, выход регистра приема информации соединен с первым входом блока элементов И-ИЛИ, выход которого соединен с первым входом блока формирования манчестерского кода, первый выход которого является информационным выходом ПРД, второй вход блока формирования манчестерского кода является входом ТИ ПРД, третий вход блока формирования манчестерского кода является входом кода «маркер» ПРД, четвертый вход блока формирования манчестерского кода является входом кода «конец сообщения» ПРД, второй выход блока формирования манчестерского кода соединен с третьим входом седьмого элемента И, со вторым входом восьмого элемента И, с первым входом девятого элемента И, с первым входом одиннадцатого элемента И, со вторым входом шестого элемента И, с четвертым входом первого элемента И и с четвертым входом третьего элемента И, выход которого соединен с первым входом второго элемента ИЛИ, выход которого является выходом стробирования чтения ПРД и соединен со входом четвертого элемента задержки, выход которого соединен с третьим входом четвертого элемента И, выход которого соединен с первым входом триггера конца сообщения буферного, первый выход которого соединен с первым входом пятого элемента И, второй выход триггера конца сообщения буферного соединен с первым входом четвертого элемента И и со вторым входом второго элемента И, выход которого соединен со вторым входом второго элемента ИЛИ, вход первого элемента задержки является входом «запуск» ПРД, выход первого элемента задержки соединен с первым входом первого элемента ИЛИ, выход которого соединен с четвертым входом блока элементов И-ИЛИ и со входом второго элемента задержки, выход которого соединен со входом счетчика байтов, с первым входом десятого элемента И и со входом шестого элемента задержки, выход которого соединен с третьим входом второго элемента И и со вторым входом пятого элемента И, выход которого соединен с первым входом триггера конца сообщения, первый выход которого соединен с третьим входом третьего элемента И, со вторым входом седьмого элемента И, с третьим входом девятого элемента И, с седьмым входом блока формирования манчестерского кода и с первым входом шестого элемента И, выход которого соединен со вторым входом триггера конца сообщения буферного и со входом пятого элемента задержки, выход которого соединен со вторым входом триггера конца сообщения, второй выход которого соединен с первым входом первого элемента И, выход которого соединен со вторым входом первого элемента ИЛИ, первый вход четвертого элемента ИЛИ является входом «передать маркер» ПРД, выход которого соединен со входом третьего элемента задержки, выход которого соединен с первым входом триггера маркера, выход которого соединен с пятым входом блока формирования манчестерского кода и со вторым входом одиннадцатого элемента И, выход которого соединен со вторым входом триггера маркера, вход первого элемента НЕ является входом «0 таймера» ПРД и соединен с первым входом седьмого элемента И, выход которого соединен со вторым входом третьего элемента ИЛИ, выход которого соединен со вторым входом триггера, формирующего сигнал конца передачи, первый выход которого соединен с первым входом восьмого элемента И, выход которого соединен со вторым входом триггера, формирующего сигнал передачи сообщения, со вторым входом четвертого элемента ИЛИ и с первым входом триггера, формирующего сигнал конца передачи, второй выход которого соединен с третьим входом первого элемента И, выход первого элемента НЕ соединен с первым входом третьего элемента И, вход второго элемента НЕ является входом «0 счетчика слов» ПРД и соединен со вторым входом четвертого элемента И и со вторым входом девятого элемента И, выход которого соединен с первым входом третьего элемента ИЛИ, выход второго элемента НЕ соединен со вторым входом третьего элемента И, выход десятого элемента И соединен с первым входом триггера, формирующий сигнал передачи сообщения, второй выход которого соединен со вторым входом десятого элемента И, первый выход соединен с шестым входом блока формирования манчестерского кода и со вторым входом первого элемента И, первый выход счетчика байтов соединен со вторым входом блока элементов И-ИЛИ, второй выход счетчика байтов соединен с третьим входом блока элементов И-ИЛИ, третий выход счетчика байтов соединен с первым входом второго элемента И и с третьим входом пятого элемента И,

управляющий блок содержит генератор тактовых импульсов, шесть элементов И, счетчик слов, счетчик, определяющего очередность подключения устройства к общей шине, счетчик, определяющий длительность интервала времени, элемент задержки, вход кода длины сообщения УУ, вход «код интервала» УУ, вход «маркер» УУ, вход стробирования чтения УУ, выход «сообщение передано» УУ, выход «восстановить таймер» УУ, выход «0 счетчика слов» УУ, выход ТИ УУ, выход «запуск» УУ, выход «передать маркер» УУ, выход «0 таймера» УУ, причем первый вход счетчика слов является входом кода длины сообщения УУ, второй вход счетчика слов является входом стробирования чтения УУ, второй выход счетчика слов соединен с первым входом четвертого элемента И, первый выход счетчика слов соединен с первым входом пятого элемента И, с первым входом третьего элемента И и является выходом «0 счетчика слов» УУ, первый вход счетчика, определяющего длительность интервала времени является входом кода интервала УУ, первый выход счетчика, определяющего длительность интервала времени соединен с первым входом первого элемента И и со вторым входом третьего элемента И, выход которого является выходом «сообщение передано» УУ, вход шестого элемента И является входом «маркер» УУ и соединен со входом элемента задержки и со входом счетчика, определяющего очередность подключения устройства к общей шине, первый выход которого соединен с третьим входом пятого элемента И, с третьим входом четвертого элемента И, со вторым входом первого элемента И и со вторым входом шестого элемента И, выход которого соединен с третьим входом счетчика, определяющего длительность интервала времени, второй выход которого является выходом «0 таймера» УУ и соединен со вторым входом второго элемента И, выход которого является выходом «восстановить таймер» УУ, выход элемента задержки соединен со вторым входом четвертого элемента И и со вторым входом пятого элемента И, выход которого является выходом «передать маркер» УУ, выход четвертого элемента И является выходом «запуск» УУ, второй выход счетчика, определяющего очередность подключения устройства к общей шине соединен с первым входом второго элемента И, выход генератора тактовых импульсов является выходом ТИ УУ и соединен с третьим входом первого элемента И, выход которого соединен со вторым входом счетчика, определяющего длительность интервала времени.

Сравнительный анализ показал, что заявленное изобретение отличается наличием четырех дополнительных блоков, расположенных в такой последовательности, которая приводит к техническому результату.

Анализ патентной литературы показал, что до даты подачи отсутствовали устройства с указанной совокупностью существенных признаков, что говорит о новизне заявляемого технического решения.

Поиск технических решений в смежных областях техники не позволил выявить отличительные признаки заявляемого технического решения, что соответствует критерию «изобретательский уровень».

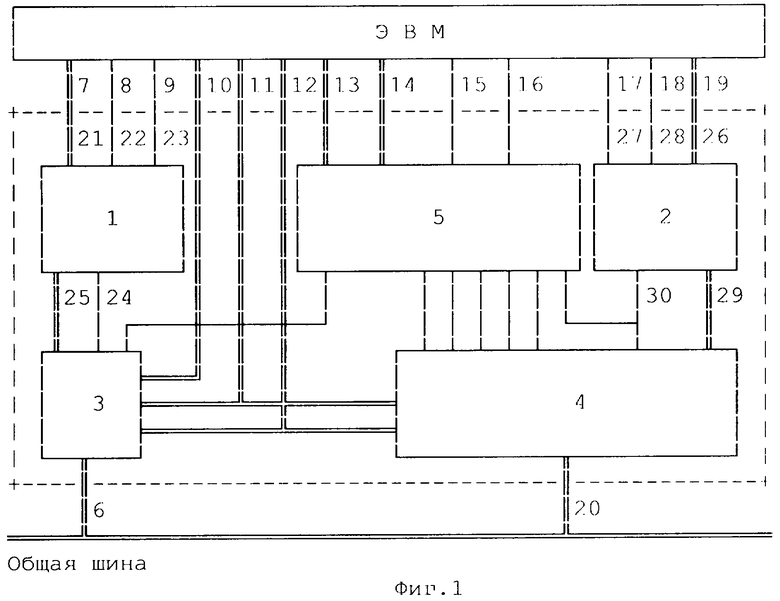

На фиг.1 представлена функциональная схема устройства для сопряжения источника и приемника информации, на фиг.2 - функциональная схема блока приемника, на фиг.3 - функциональная схема блока передатчика, на фиг.4 - функциональная схема управляющего блока.

Устройство для сопряжения источника и приемника информации (фиг.1-4) содержит первый блок буферной памяти (ББП1) 1, второй блок буферной памяти (ББП2) 2, блок приемника (ПРМ) 3, блок передатчика (ПРД) 4, управляющий блок (УУ) 5, первый информационный вход 6 устройства, первый информационный выход 7 устройства, вход стробирования чтения 8 устройства, первый вход начальной установки 9 устройства, вход кода адреса 10 устройства, вход кода маркера 11 устройства, вход кода конца сообщения 12 устройства, вход кода длины сообщения 13 устройства, вход кода интервала 14 устройства, выход «сообщение передано» 15 устройства, выход «восстановить таймер» 16 устройства, вход стробирования записи 17 устройства, второй вход начальной установки 18 устройства, второй информационный вход 19 устройства, второй информационный выход 20 устройства, причем информационный вход ПРМ является первым информационным входом 6 устройства, вход кода «конец сообщения» ПРМ соединен со входом кода «конец сообщения» ПРД и является входом кода конца сообщения 12 устройства, вход кода «маркер» ПРМ соединен с входом кода «маркер» ПРД и является входом кода маркера 11 устройства, вход кода адреса ПРМ является входом кода адреса 10 устройства, информационный выход ПРМ соединен с информационным входом 25 ББП1, выход стробирования записи ПРМ соединен со входом стробирования записи 24 ББП1, выход «маркер» ПРМ соединен со входом «маркер» УУ, вход стробирования чтения 22 ББП1 является входом стробирования чтения 8 устройства, вход начальной установки 23 ББП1 является первым входом начальной установки 9 устройства, информационный выход 21 ББГП является первым информационным выходом 7 устройства, вход кода длины сообщения УУ является входом кода длины сообщения 13 устройства, вход «код интервала» УУ является входом кода интервала 14 устройства, выход «сообщение передано» УУ является выходом 15 устройства «сообщение передано», выход «восстановить таймер» УУ является выходом 16 устройства «восстановить таймер», выход «0 счетчика слов» УУ соединен со входом «0 счетчика слов» ПРД, выход ТИ УУ соединен со входом ТИ ПРД, выход «запуск» УУ соединен со входом «запуск» ПРД, выход «передать маркер» УУ соединен со входом «передать маркер» ПРД, выход «0 таймера» УУ соединен со входом «0 таймера» ПРД, информационный вход 26 ББП2 является вторым информационным входом 19 устройства, вход стробирования записи 27 ББП2 является входом стробирования записи 17 устройства, вход начальной установки 28 ББП2 является вторым входом начальной установки 18 устройства, информационный выход 29 ББП2 соединен с информационным входом ПРД, выход стробирования чтения которого соединен со входом стробирования чтения 30 ББП2 и со входом стробирования чтения УУ, информационный выход ПРД является вторым информационным выходом 20 устройства, блок приемника содержит блок приема сигналов 31, буферный регистр 32, выходной регистр 33, схему выделения байта «маркер» 34, схему выделения байта «конец сообщения» 35, схему сравнения адресов 36, триггер разрешения сравнения адресов 37, триггер приема информации 38, счетчик байтов 39, элементы задержки 40, 41, 42, элементы И 43, 44, 45, элементы ИЛИ 46, 47, блок элементов И 48, информационный вход 49 ПРМ, вход кода «конец сообщения» 50 ПРМ, вход кода адреса 52 ПРМ, вход кода маркера 51 ПРМ, информационный выход 53 ПРМ, выход стробирования записи 54 ПРМ, выход «маркер» 55 ПРМ, причем вход блока приема сигналов 31 является информационным входом 49 ПРМ, первый выход которого соединен со входом буферного регистра 32, выход которого соединен с первым входом схемы выделения байта «маркер» 34, с первым входом схемы выделения байта «конец сообщения» 35, с первым входом схемы сравнения адресов 36 и с первым входом блока элементов И 48, выход которого соединен со входом выходного регистра 33, выход которого является информационным выходом 53 ПРМ, второй выход блока приема сигналов соединен со входом элемента задержки 40, выход которого соединен с третьим входом схемы выделения байта «конец сообщения» 35, с третьим входом схемы сравнения адресов 36, с первым входом элемента И 43 и с третьим входом схемы выделения байта «маркер» 34, выход которого является выходом «маркер» 55 ПРМ и соединен с первым входом элемента ИЛИ 46, выход которого соединен со вторым входом триггера разрешения сравнения адресов 37, выход которого соединен со вторым входом элемента И 43 и с четвертым входом схемы сравнения адресов 36, выход которого соединен со вторым входом триггера приема информации 38, выход которого соединен с первым входом элемента И 44, выход которого соединен со входом элемента задержки 42, с третьим входом блока элементов И 48 и со входом счетчика байтов 39, первый выход которого соединен со вторым входом блока элементов И 48, второй выход счетчика байтов 39 соединен с первым входом элемента И 45, выход которого является выходом стробирования записи 54 ПРМ, третий выход блока приема сигналов соединен с первым входом элемента ИЛИ 47, выход которого соединен с первым входом триггера разрешения сравнения адресов 37, выход элемента И 43 соединен со вторым входом элемента ИЛИ 47, второй вход схемы выделения байта «маркер» 34 является входом кода «маркер» 51 ПРМ, второй вход схемы сравнения адресов 36 является входом кода адреса 52 ПРМ, второй вход схемы выделения байта «конец сообщения» 35 является входом кода «конец сообщения» 50 ПРМ, первый выход схемы выделения байта «конец сообщения» 35 соединен со вторым входом элемента ИЛИ 46 и с первым входом триггера приема информации 38, второй выход схемы выделения байта «конец сообщения» 35 соединен со входом элемента задержки 41, выход которого соединен со вторым входом элемента И 44, выход элемента задержки 42 соединен со вторым входом элемента И 45, выход элемента И 43 соединен со вторым входом элемента ИЛИ 47, блок передатчика содержит блок формирования манчестерского кода 83, счетчик байтов 84, регистр приема информации 85, триггер передачи 86, триггер маркера 87, триггер конца сообщения буферный 56, триггер конца сообщения 57, триггер конца передачи 58, блок элементов И-ИЛИ 59, элементы И 60, 61, 62, 63, 64, 65, 66, 67, 68, 69 и 70, элементы ИЛИ 71, 72, 73 и 74, элементы НЕ 75 и 76, элементы задержки 77, 78, 79, 80, 81 и 82, информационный вход 93 ПРД, вход кода «конец сообщения» 97 ПРД, вход кода «маркер» 96 ПРД, вход ТИ 95 ПРД, вход «запуск» 94 ПРД, вход «передать маркер» 89 ПРД, вход «0 таймера» 90 ПРД, вход «0 счетчика слов» 91 ПРД, информационный выход 88 ПРД, выход стробирования чтения 92 ПРД, причем вход регистра приема информации 85 является информационным входом 93 ПРД, выход регистра приема информации 85 соединен с первым входом блока элементов И-ИЛИ 59, выход которого соединен с первым входом блока формирования манчестерского кода 83, первый выход которого является информационным выходом 88 ПРД, второй вход блока формирования манчестерского кода 83 является входом ТИ 95 ПРД, третий вход блока формирования манчестерского кода 83 является входом кода «маркер» 96 ПРД, четвертый вход блока формирования манчестерского кода 83 является входом кода «конец сообщения» 97 ПРД, второй выход блока формирования манчестерского кода 83 соединен с третьим входом элемента И 66, со вторым входом элемента И 67, с первым входом элемента И 68, с первым входом элемента И 70, со вторым входом элемента И 65, с четвертым входом элемента И 60 и с четвертым входом элемента И 62, выход которого соединен с первым входом элемента ИЛИ 72, выход которого является выходом стробирования чтения 92 ПРД и соединен со входом элемента задержки 80, выход которого соединен с третьим входом элемента И 73, выход которого соединен с первым входом триггера конца сообщения буферного 56, первый выход которого соединен с первым входом элемента И 64, второй выход триггера конца сообщения буферного 56 соединен с первым входом элемента И 63 и со вторым входом элемента И 61, выход которого соединен со вторым входом элемента ИЛИ 72, вход элемента задержки 77 является входом «запуск» 87 ПРД, выход элемента задержки 77 соединен с первым входом элемента ИЛИ 71, выход которого соединен с четвертым входом блока элементов И-ИЛИ 59 и со входом элемента задержки 78, выход которого соединен со входом счетчика байтов 84, с первым входом элемента И 69 и со входом элемента задержки 82, выход которого соединен с третьим входом элемента И 61 и со вторым входом элемента И 64, выход которого соединен с первым входом триггера конца сообщения 57, первый выход которого соединен с третьим входом элемента И 62, со вторым входом элемента И 66, с третьим входом элемента И 68, с седьмым входом блока формирования манчестерского кода 83 и с первым входом элемента И 65, выход которого соединен со вторым входом триггера конца сообщения буферного 56 и со входом элемента задержки 81, выход которого соединен со вторым входом триггера конца сообщения 57, второй выход которого соединен с первым входом элемента И 60, выход которого соединен со вторым входом элемента ИЛИ 71, первый вход элемента ИЛИ 74 является входом «передать маркер» 89 ПРД, выход которого соединен со входом элемента задержки 79, выход которого соединен с первым входом триггера маркера 87, выход которого соединен с пятым входом блока формирования манчестерского кода 83 и со вторым входом элемента И 70, выход которого соединен со вторым входом триггера маркера 87, вход элемента НE 75 является входом «0 таймера» 90 ПРД и соединен с первым входом элемента И 66, выход которого соединен со вторым входом элемента ИЛИ 73, выход которого соединен со вторым входом триггера конца передачи 58, первый выход которого соединен с первым входом элемента И 67, выход которого соединен со вторым входом триггера передачи 86, со вторым входом элемента ИЛИ 74, и с первым входом триггера конца передачи 58, второй выход которого соединен с третьим входом элемента И 60, выход элемента НЕ 75 соединен с первым входом элемента И 62, вход элемента НЕ 76 является входом «0 счетчика слов» 91 ПРД и соединен со вторым входом элемента И 63 и со вторым входом элемента И 68, выход которого соединен с первым входом элемента ИЛИ 73, выход элемента НЕ 76 соединен со вторым входом элемента И 62, выход элемента И 69 соединен с первым входом триггера передачи 86, второй выход которого соединен со вторым входом элемента И 69, первый выход соединен с шестым входом блока формирования манчестерского кода 83 и со вторым входом элемента И 60, первый выход счетчика байтов 84 соединен со вторым входом блока элементов И-ИЛИ 59, второй выход счетчика байтов 84 соединен с третьим входом блока элементов И-ИЛИ 59, третий выход счетчика байтов 84 соединен с первым входом элемента И 61 и с третьим входом элемента И 64, управляющий блок содержит генератор тактовых импульсов 101, элементы И 102, 103, 104, 105, 106, 108, счетчик слов 107, счетчик, определяющий очередность подключения устройства к общей шине 98, счетчик, определяющий длительность интервала времени 99, элемент задержки 100, вход кода длины сообщения 109 УУ, вход «код интервала» 119 УУ, вход «маркер» 110 УУ, вход стробирования чтения 111 УУ, выход «сообщение передано» 112 УУ, выход «восстановить таймер» 113 УУ, выход «0 счетчика слов» 114 УУ, выход ТИ 115 УУ, выход «запуск» 116 УУ, выход «передать маркер» 117 УУ, выход «0 таймера» 118 УУ, причем первый вход счетчика слов 107 является входом кода длины сообщения 109 УУ, второй вход счетчика слов 107 является входом стробирования чтения 111 УУ, второй выход счетчика слов 107 соединен с первым входом элемента И 105, первый выход счетчика слов 107 соединен с первым входом элемента И 106, с первым входом элемента И 104 и является выходом «0 счетчика слов» 114 УУ, первый вход счетчика, определяющего длительность интервала времени 99, является входом кода интервала 119 УУ, первый выход счетчика, определяющего длительность интервала времени 99, соединен с первым входом элемента И 102 и со вторым входом элемента И 104, выход которого является выходом «сообщение передано» 112 УУ, вход элемента И 108 является входом «маркер» 110 УУ и соединен со входом элемента задержки 100 и со входом счетчика, определяющего очередность подключения устройства к общей шине 98, первый выход которого соединен с третьим входом элемента И 106, с третьим входом элемента И 105, со вторым входом элемента И 102 и со вторым входом элемента И 108, выход которого соединен с третьим входом счетчика, определяющего длительность интервала времени 99, второй выход которого является выходом «0 таймера» 118 УУ и соединен со вторым входом элемента И 103, выход которого является выходом «восстановить таймер» 113 УУ, выход элемента задержки 100 соединен со вторым входом элемента И 105 и со вторым входом элемента И 106, выход которого является выходом «передать маркер» 117 УУ, выход элемента И 105 является выходом «запуск» 116 УУ, второй выход счетчика, определяющего очередность подключения устройства к общей шине 98, соединен с первым входом элемента И 103, выход генератора тактовых импульсов 101 является выходом ТИ 115 УУ и соединен с третьим входом элемента И 102, выход которого соединен со вторым входом счетчика, определяющего длительность интервала времени 99.

Устройство работает следующим образом (фиг.1).

Существует два режима работы устройства - режим приема и режим передачи. Режиму приема соответствует направление передачи информации от первого информационного входа 6 устройства к первому информационному выходу 7 устройства. Режиму передачи соответствует направление передачи информации от второго информационного входа 19 устройства ко второму информационному выходу 20 устройства.

Работа устройства в режиме приема обеспечивается блоками приемника (ПРМ), первой буферной памяти (ББП1) и управления (УУ). Работа устройства в режиме передачи обеспечивается блоками передатчика (ПРД), второй буферной памяти (ББП2) и управления (УУ).

Исходное состояние ПРМ (фиг.2) в момент приема маркера из общей шины следующее. Состояние двухразрядного счетчика байтов 39 - «00»; триггер разрешения сравнения адресов 37 и триггер приема информации 38 сброшены в нулевое состояние. ПРМ работает следующим образом. Блок приема сигналов 31 преобразует информацию, поступающую из общей шины в виде манчестерского кода, в двоичные байтовые комбинации и формирует последовательность управляющих сигналов «байт принят». По каждому сигналу «байт принят» байт информации, декодированный в блоке 31, поступает в буферный регистр 32. Этот же сигнал через элемент задержки 40 (время задержки выбирается из условия надежного приема информации в регистр 32) поступает па управляющий вход схем 34, 35, 36 и элемента И 43. Схема выделения байта «маркер» 34 используется для выделения из потока информации сетевого байта «маркер» путем сравнения кода «маркер» с информацией, содержащейся в регистре 32. Схема выделения байта «конец сообщения» 35 используется для выделения из потока информации сетевого байта «конец сообщения» путем сравнения кода «конец сообщения» с информацией, содержащейся в регистре 32. Схема сравнения адресов используется только в случае нахождения в единичном состоянии триггера разрешения сравнения адресов 37. В этом случае код «адрес» сравнивается с содержимым регистра 32. Импульсные сигналы, отражающие результат сравнения, появляются на выходах схем 34, 35 и 36 только по сигналу на управляющем входе.

При приеме маркера по сигналу «байт принят», сформированному на выходе элемента задержки 40, на выходе схемы 34 появляется сигнал «маркер», который поступает на вход 44 УУ устройства. Одновременно данный сигнал через элемент ИЛИ 46 устанавливает в единичное состояние триггер 37.

Если в течение интервала времени Т1 за маркером не последует информация (шина «молчит»), то блоком приема сигналов 31 формируется сигнал, который через элемент ИЛИ 47 сбрасывает триггер 37 (данная ситуация имеет место в том случае, если устройство, которому переданы полномочия, не имеет информации для передачи, следовательно, следующим байтом информации снова будет маркер). В противном случае очередной сигнал «байт принят» обязательно сопровождает байт, несущий информацию о том, кому адресовано сообщение.

Так как триггер 37 установлен в единичное состояние, то на выходе схемы 36 по сигналу «байт принят» появится результат сравнения (импульсный сигнал в случае, если сравниваемые байты адреса совпадают). Одновременно триггер 37 через элемент И 43 и элемент ИЛИ 47 устанавливается в нулевое состояние, запрещая тем самым появление сигналов на выходе схемы 36 при приеме информационных байтов.

Сигнал с выхода схемы 36 (в случае совпадения адресов) устанавливает в единичное состояние триггер приема информации 38. Единичное состояние триггера 38 свидетельствует о том, что принимаемое сообщение адресуется данному устройству. Схема выделения байта «конец сообщения» 35 имеет два выхода. При поступлении на управляющий вход данной схемы сигнала «байт принят» на первом выходе формируется сигнал «конец сообщения», если очередной байт - служебный байт «конец сообщения»; на втором выходе формируется сигнал «конец сообщения» в противном случае.

Сигнал «конец сообщения» через элемент задержки 41 (время задержки выбирается из условия надежной установки в единичное состояние триггера 38) поступает на вход элемента И 44. Если триггер 38 установлен в единичное состояние, то по очередному сигналу с выхода элемента задержки 41 на выходе элемента И 44 формируется сигнал, по которому содержимое буферного регистра 32 через блок элементов И 48 переписывается в соответствующие разряды выходного регистра 33 (содержимое счетчика байтов 39 определяет в какие разряды 4-х байтного регистра 33 переписывается информация; так как в нашем случае состояние счетчика 39 «00», то информация записывается в разряды с 31 по 24, если же состояние будет, например, «11», то информация будет записана в разряды с 7 по 0). Одновременно содержимое счетчика 39 изменяется на единицу (в нашем случае счетчик из состояния «00» переходит в состояние «01»). Сигнал с выхода элемента И 44 через элемент задержки 42 (время задержки выбирается из условия надежного перехода счетчика 39 в следующее состояние) поступает на вход элемента И 45. Если счетчик 39 к этому моменту находится в состоянии «00» (в регистре 33 накоплены 4 байта), то на выходе элемента И 45 формируется сигнал «стробирование записи», который поступает на вход 24 ББП1 и управляет записью в него содержимого регистра 33.

Прием любого сообщения (независимо от того, адресуется оно данному устройству или нет) завершается следующим образом. По сигналу «байт принят» в момент времени, когда очередной байт является служебным байтом «конец сообщения», на выходе схемы 35 появляется сигнал «конец сообщения». Данный сигнал сбрасывает триггер 38 и устанавливает в единичное состояние триггер 37, тем самым подготавливая условия для анализа адреса следующего сообщения. Если принятое сообщение последнее, то есть в течение интервала времени Т1 общая шина «молчит», то блок приема сигналов 31 формирует сигнал, который через элемент ИЛИ 47 сбрасывает триггер 37.

На фиг.5 и 6 показаны временные диаграммы функционирования ПРМ. Синхронизация осуществляется синхросигналами ТИ1, принимаемыми из общей шины.

Исходное состояние ПРД (фиг.3) следующее. Счетчик 84, регистр 85 и все триггеры сброшены.

ПРД работает следующим образом. Возможны два варианта начала работы.

1. Из УУ, выход 117, поступает сигнал «передать маркер», который через элемент ИЛИ 74 и элемент задержки 79 устанавливает триггер маркера 87 в единичное состояние. Время задержки (Т1) выбирается из условия надежной идентификации состояния «шина молчит». В результате установки триггера 87 блок 83 выдаст в общую шину код маркера. По окончании передачи маркера блок 83 формирует сигнал «байт передан», по которому через элемент И 70 триггер 87 сбрасывается. Отметим, что ПРМ данного устройства также принимает этот маркер из общей шины и в УУ изменяется состояние счетчика, определяющего очередность подключения устройства к общей шине, в результате чего происходит восстановление таймера. На фиг.7 показана временная диаграмма функционирования ПРД.

2. Из УУ, выход 116, поступает сигнал «запуск», который через элемент задержки 77 (время задержки выбирается из условия надежного приема информации из ББП2 в регистр 85 по сигналу «запуск») и элемент ИЛИ 71 поступает в блок элементов И-ИЛИ 59 и обеспечивает передачу в блок 83 одного из байтов слова, записанного в регистр 85. Номер байта определяется состоянием счетчика 84 и в нашем случае будет передан байт 0.

Сигнал с выхода элемента ИЛИ 71 поступает также через элемент задержки 78 на счетчик 84 (время задержки выбирается из условия надежной передачи информации из регистра 85 в блок 83) и изменяет его состояние (в рассматриваемом случае оно станет «01»), подготавливая тем самым к передаче в блок 83 следующий байт слова, записанного в регистре 85. Одновременно по данному сигналу через элемент И 69 устанавливается в единичное состояние триггер передачи 86. Триггер 86 находится в единичном состоянии весь интервал времени, пока передаются сообщения. Блок формирования манчестерского кода 83 начинает передачу информации в общую шину одновременно с приходом на его вход единичного потенциала с триггера 86. Для этих целей он использует тактовые импульсы (ТИ), поступающие из УУ, выход 115. В момент окончания передачи очередного байта (в нашем случае байта 0) блок 83 формирует сигнал «байт передан». Данный сигнал через элемент И 60 (он открыт, так как триггер 86 в единичном состоянии & триггер 67 в нулевом состоянии & триггер 58 в нулевом состоянии) и элемент ИЛИ 71 поступает на блок элементов И-ИЛИ 59 и организует передачу в блок 83 очередного байта слова, записанного в регистре 85 (в нашем случае байта 1). Сигнал с выхода элемента ИЛИ 71 через элемент задержки 78 изменяет состояние счетчика 84, подготавливая тем самым к передаче в блок 83 следующий байт слова.

Сигнал с выхода элемента задержки 78 поступает каждый раз через элемент задержки 82 (время задержки выбирается из условия надежного изменения состояния счетчика 84) на вход элемента 61, но проходит только при выполнении условия: нулевое состояние счетчика 84 & нулевое состояние триггера 56. Если это условие выполняется (означает, что очередное слово из регистра 85 полностью передано в блок 83 и это не последнее слово сообщения), то сигнал с выхода элемента И 61 через элемент ИЛИ 72 поступает на вход 30 ББП2 и на вход 111 УУ как сигнал «стробирование чтения». В результате из ББП2, выход 29, в регистр 85 поступает следующее слово, а содержимое счетчика слов в УУ уменьшается на единицу. На фиг.8 и 9 показаны временные диаграммы функционирования ПРД при передаче сообщения.

Сигнал «стробирование чтения» через элемент задержки 80 (время задержки выбирается из условия надежного переключения состояния счетчика слов) каждый раз поступает на вход элемента И 63, но проходит только при выполнении условия: нулевое состояние триггера 56 & нулевое состояние счетчика слов. Если это условие выполняется (сообщение полностью поступило из ББП2 в ПРД), то сигнал с выхода элемента И 63 устанавливает в единичное состояние триггер 56.

Сигнал с выхода элемента задержки 82 каждый раз поступает на вход элемента И 64, но проходит только при выполнении условия: единичное состояние триггера 56 & нулевое состояние счетчика 84.

Если это условие выполняется (означает, что последний байт последнего слова сообщения передан в блок 83), то сигнал с выхода элемента И 64 устанавливает в единичное состояние триггер конца сообщения 57, сигнализируя блоку 83, что следующим байтом должен быть передан байт «конец сообщения». Напомним, что в данном случае сигнал с выхода элемента задержки 82 через элемент И 61 в виде сигнала «стробирование чтения» не пройдет (триггер 56 в единичном состоянии).

Передав последний байт сообщения, блок 83 сформирует сигнал «байт передан» и начнет передавать код байта «конец сообщения». Сигнал «байт передан» через элемент И 60 не пройдет (триггер 57 в единичном состоянии) и состояние счетчика 84 не изменится. В то же время, если в счетчик слов загружена длина нового сообщения, данный сигнал пройдет через элемент И 62, так как выполняется следующее условие: таймер не в нулевом состоянии & счетчик слов не в нулевом состоянии & триггер 57 в единичном состоянии. Сигнал с выхода элемента И 62 через элемент ИЛИ 72 поступает на вход 30 ББП2 и на вход 111 УУ как сигнал «стробирование чтения». В результате из ББП2, выход 29, в регистр 85 загружается первое слово нового сообщения, а содержимое счетчика слов уменьшается на единицу. Сигнал «байт передан» одновременно через элемент И 65 (триггер 57 в единичном состоянии) сбрасывает триггер 56 и через элемент задержки 81 (время задержки выбирается из условия надежной установки, если возникает такая ситуация, триггера 58) сбрасывает триггер 57.

После передачи байта «конец сообщения» формируется сигнал «байт передан», который проходит через элемент И 60 и организует передачу в блок 83 байта 0 из регистра 85. Дальнейшие действия выполняются аналогично вышеописанному. На фиг.9 показана временная диаграмма функционирования ПРД при передаче байта «конец сообщения».

Возможны два варианта окончания передачи сообщений.

A. Интервал времени, отведенный для передачи сообщений, не истек, а очередь сообщений пуста.

Сигнал «байт передан» каждый раз поступает на вход элемента И 68, но проходит только при выполнении условия: единичное состояние триггера 57 & счетчик слов в нулевом состоянии. Если это условие выполняется, то сигнал с выхода элемента И 68 через элемент ИЛИ 73 устанавливает в единичное состояние триггер конца передачи 58. Тогда сигнал «байт передан», сформированный блоком 83 после передачи байта «конец сообщения», через элемент И 60 не пройдет (триггер 58 в единичном состоянии) и передача информации из регистра 85 осуществлена не будет. Не пройдет данный сигнал и через элемент И 62 (счетчик слов в нулевом состоянии), то есть сигнал «стробирование чтения» сформирован не будет. Зато сигнал «байт передан» через элемент И 67 сбросит триггер 58 и триггер 86, а сигнал с выхода элемента И 67 через элемент ИЛИ 74 и элемент задержки 79 установит в единичное состояние триггер маркера 87. В результате через Т1 блок 83 выдаст в общую шину байт «маркер». На фиг.10 показана временная диаграмма функционирования ПРД при завершении передачи по условию «очередь сообщений пуста».

B. Очередь сообщений не пуста, а интервал времени, отведенный для передачи, истек.

Сигнал «байт передан» каждый раз поступает на вход элемента И 66, но проходит только при выполнении условия: единичное состояние триггера 57 & нулевое состояние таймера. Если это условие выполняется, то сигнал с выхода элемента И 66 через элемент ИЛИ 73 устанавливает в единичное состояние триггер конца передачи 58.

Дальнейшие действия аналогичны описанным в варианте А. На фиг.11 показана временная диаграмма функционирования ПРД при завершении передачи по условию «нулевое состояние таймера».

Исходное состояние УУ (фиг.4) следующее. В счетчик, определяющий длительность интервала времени 99, загружен двоичный код, определяющий длительность интервала времени, выделенного устройству на передачу сообщений. В счетчик, определяющий очередность подключения устройства к общей шине, загружен номер устройства, определяющий очередность подключения устройства к общей шине для передачи сообщений по ней. Состояние счетчика слов 107 определяется состоянием очереди сообщений к общей шине. Если счетчик содержит нулевой код, то очередь сообщений пуста. В противном случае содержимое счетчика определяет длину сообщения (количество слов), стоящего первым в очереди.

УУ работает следующим образом. Каждый сигнал «маркер», поступающий из выхода 55 ПРМ, увеличивает содержимое счетчика 98 на единицу, тем самым приближая момент подключения станции к общей шине. Одновременно данный сигнал через элемент задержки 100 (время задержки выбирается из условия надежного изменения состояния счетчика 98) поступает на элементы И 105 и 106. Элемент И 105 формирует сигнал «запуск». Условием появления данного сигнала является нулевое состояние счетчика, определяющего очередность подключения устройства к общей шине 98 (устройство получило полномочия на передачу) и ненулевое состояние счетчика слов 107 (очередь сообщений не пустая). Элемент И 106 формирует сигнал «передать маркер». Условием появления данного сигнала является нулевое состояние счетчика 98 и нулевое состояние счетчика 107 (очередь сообщений пуста).

Как только счетчик 98 установится в нулевое состояние (при условии, что счетчик, определяющий длительность интервала времени 99, не в нулевом состоянии), тактовые импульсы с генератора 101 через элемент И 102 начинают поступать в счетчик 99, уменьшая его содержимое. Установка счетчика 99 в нулевое состояние свидетельствует, что интервал времени, отведенный на передачу данному устройству, истек. Элемент И 103 формирует сигнал прерывания «восстановить таймер». Условие появления данного сигнала: нулевое состояние счетчика 99 и ненулевое состояние счетчика 98 (полномочия устройства истекли). Отметим, что в случае, если устройство передало полномочия до истечения отведенного ему интервала времени, то счетчик 99 сбрасывается в нулевое состояние через элемент И 108 очередным сигналом «маркер». Результатом обработки ЭВМ данного прерывания является загрузка в счетчик 99 соответствующего двоичного кода.

Элемент И 104 формирует сигнал «сообщение передано». Условие появления данного сигнала: ненулевое состояние счетчика 99 и нулевое состояние счетчика 107. Результатом обработки ЭВМ данного прерывания является загрузка в счетчик 107, если это необходимо, кода, определяющего длину сообщения. В ходе передачи сообщения содержимое счетчика 107 уменьшается по сигналам «стробирование чтения», поступающим из выхода 92 ПРД.

УУ выдает в ПРД следующие управляющие потенциалы: «0 счетчика слов» (счетчик 107 находится в нулевом состоянии), «0 таймера» (счетчик 99 находится в нулевом состоянии). В ПРД выдаются также импульс «запуск» или «передать маркер» и тактовые импульсы с выхода генератора 101. Управление УУ осуществляется сигналом «маркер», поступающим из выхода 55 ПРМ.

Источники информации

1. US N 1488815, кл. G06F 13/00, 11/28, 1987.

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ДЛЯ СОПРЯЖЕНИЯ ИСТОЧНИКА И ПРИЕМНИКА ИНФОРМАЦИИ | 2010 |

|

RU2428737C1 |

| УСТРОЙСТВО ДЛЯ КОНТРОЛЯ НЕСАНКЦИОНИРОВАННОГО ДОСТУПА | 2002 |

|

RU2221270C2 |

| Устройство для сопряжения между абонентами | 1988 |

|

SU1594550A1 |

| Устройство для сбора данных о работе ЭВМ | 1982 |

|

SU1121679A1 |

| Устройство для сопряжения вычислительной машины с каналами связи | 1987 |

|

SU1472913A1 |

| Система отладки микропроцессорных устройств | 1989 |

|

SU1700559A1 |

| Устройство для контроля и диагностики логических узлов | 1980 |

|

SU960825A1 |

| СПОСОБ ОБРАБОТКИ СИГНАЛОВ СВЯЗИ В АБОНЕНТСКОМ ПУНКТЕ БЕСПРОВОДНОЙ СИСТЕМЫ ЭЛЕКТРОСВЯЗИ | 1990 |

|

RU2159007C2 |

| Устройство для сопряжения ЦВМ с внешними устройствами | 1989 |

|

SU1784840A1 |

| Устройство для обмена информацией | 1985 |

|

SU1334151A1 |

Изобретение относится к автоматике и вычислительной технике и может быть использовано в локальных вычислительных сетях (ЛВС) для реализации интервально-маркерного метода доступа к общей шине с динамически меняющимся интервалом передачи. Техническим результатом изобретения является расширение функциональных возможностей устройства для сопряжения источника и приемника информации. Этот результат достигается за счет того, что в устройство дополнительно введены второй блок буферной памяти (ББП2), блок приемника (ПРМ), блок передатчика (ПРД) и управляющий блок (УУ). Принципы работы заявленного изобретения сводятся к реализации алгоритма интервально-маркерного метода доступа к общей шине с динамически меняющимся интервалом передачи. 11 ил.

Устройство для сопряжения источника и приемника информации, содержащее входной регистр, блок элементов И, первый, второй и третий элементы задержки, первый и второй элементы ИЛИ, схему сравнения, первый и второй счетчики адреса, триггер, первый и второй элементы И, блок памяти (БП), содержащий первый и второй дешифраторы, блок элементов ИЛИ, N информационных регистров, N блоков элементов И первой группы, N блоков элементов И второй группы, информационный вход устройства, вход стробирования записи устройства, вход стробирования чтения устройства, вход начальной установки устройства, информационный выход устройства, выход «готовность записи» устройства и выход «готовность чтения» устройства, причем первый вход первого элемента ИЛИ является входом начальной установки устройства, выход первого элемента ИЛИ соединен со входами установки первого счетчика адреса, триггера и с установочными входами N информационных регистров, первый вход блока элементов И является информационным входом устройства, второй вход блока элементов И соединен со входом первого элемента задержки и является входом стробирования записи устройства, выход блока элемента И соединен с информационным входом входного регистра, выход которого соединен с соответствующими информационными входами N блоков элементов И первой группы, выходы которых соединены с входами данных N информационных регистров, выходы которых соединены с информационными входами N блоков элементов И второй группы, выходы которых соединены с соответствующими входами блока элементов ИЛИ, выход которого является информационным выходом устройства, выходы первого счетчика адреса соединены со входами первого дешифратора, выходы которого соединены с соответствующими стробирующими входами N блоков элементов И второй группы, выход первого элемента задержки соединен с первым входом первого элемента И, выход которого соединен с соответствующими первыми стробирующими входами N блоков элементов И первой группы и с входом второго элемента задержки, выход которого соединен со счетным входом второго счетчика адреса, выход переполнения которого соединен с единичным входом триггера, прямой и инверсный выходы которого соединены соответственно с первым входом второго элемента ИЛИ и вторым входом первого элемента И, инверсный выход триггера является выходом готовности записи устройства, выход второго элемента ИЛИ соединен с первым входом второго элемента И, второй вход которого является входом стробирования чтения устройства, а выход второго элемента ИЛИ является выходом готовности чтения устройства, выход второго элемента И соединен с вторыми стробирующими входами N блоков элементов И второй группы и с входом третьего элемента задержки, выход которого соединен со счетным входом первого счетчика адреса, выход переполнения которого соединен со вторым входом первого элемента ИЛИ, выход которого соединен с установочным входом второго счетчика адреса, информационные выходы которого соединены с входами второго дешифратора адреса и с первой группой входов схемы сравнения, вторая группа входов которой соединена с информационными выходами первого счетчика адреса, выход схемы сравнения соединен с вторым входом второго элемента ИЛИ, выходы второго дешифратора соединены с соответствующими вторыми стробирующими входами N блоков элементов И первой группы, отличающееся тем, что в устройство введены:

второй блок буферной памяти, выполненный идентично первому (ББП2), блок приемника (ПРМ), блок передатчика (ПРД) и управляющий блок (УУ), первый информационный вход устройства, первый информационный выход устройства, вход стробирования чтения устройства, первый вход начальной установки устройства, вход кода адреса устройства, вход кода «маркер» устройства, вход кода «конец сообщения» устройства, вход кода длины сообщения устройства, вход «кода интервала времени передачи сообщений» устройства, выход «сообщение передано» устройства, выход «восстановить таймер» устройства, второй информационный вход устройства, вход стробирования записи устройства, второй вход начальной установки устройства, второй информационный выход устройства, причем информационный вход ПРМ является первым информационным входом устройства, вход кода «конец сообщения» ПРМ соединен со входом кода «конец сообщения» ПРД и является входом кода конца сообщения устройства, вход кода «маркер» ПРМ соединен с входом кода «маркер» ПРД и является входом кода маркера устройства, вход кода адреса ПРМ является входом кода адреса устройства, информационный выход ПРМ соединен с информационным входом ББП1, выход стробирования записи ПРМ соединен со входом стробирования записи ББП1, выход «маркер» ПРМ соединен со входом «маркер» УУ, вход стробирования чтения ББП1 является входом стробирования чтения устройства, вход начальной установки ББП1 является первым входом начальной установки устройства, информационный выход ББП1 является первым информационным выходом устройства, вход кода длины сообщения УУ является входом кода длины сообщения устройства, вход «код интервала» УУ является входом кода интервала устройства, выход «сообщение передано» УУ является выходом устройства «сообщение передано», выход «восстановить таймер» УУ является выходом устройства «восстановить таймер», выход «0 счетчика слов» УУ соединен со входом «0 счетчика слов» ПРД, выход ТИ УУ соединен со входом ТИ ПРД, выход «запуск» УУ соединен со входом «запуск» ПРД, выход «передать маркер» УУ соединен со входом «передать маркер» ПРД, выход «0 таймера» УУ соединен со входом «0 таймера» ПРД, информационный вход ББП2 является вторым информационным входом устройства, вход стробирования записи ББП2 является входом стробирования записи устройства, вход начальной установки ББП2 является вторым входом начальной установки устройства, информационный выход ББП2 соединен с информационным входом ПРД, выход стробирования чтения которого соединен со входом стробирования чтения ББП2 и со входом стробирования чтения УУ, информационный выход ПРД является вторым информационным выходом устройства, причем

блок приемника содержит блок приема сигналов, буферный регистр, выходной регистр, схему выделения байта «маркер», схему выделения байта «конец сообщения», схему сравнения адресов, триггер разрешения сравнения адресов, триггер приема информации, счетчик байтов, первый, второй и третий элементы задержки, первый, второй и третий элементы И, первый и второй элементы ИЛИ, блок элементов И, информационный вход ПРМ, вход кода «конец сообщения» ПРМ, вход кода адреса ПРМ, информационный выход ПРМ, выход стробирования записи ПРМ, выход «маркер» ПРМ, причем вход блока приема сигналов является информационным входом ПРМ, первый выход которого соединен со входом буферного регистра, выход которого соединен с первым входом схемы выделения байта «маркер», с первым входом схемы выделения байта «конец сообщения», с первым входом схемы сравнения адресов и с первым входом блока элементов И, выход которого соединен со входом выходного регистра, выход которого является информационным выходом ПРМ, второй выход блока приема сигналов соединен со входом первого элемента задержки, выход которого соединен с третьим входом схемы выделения байта «конец сообщения», с третьим входом схемы сравнения адресов, с первым входом первого элемента И и с третьим входом схемы выделения байта «маркер», выход которого является выходом «маркер» ПРМ и соединен с первым входом первого элемента ИЛИ, выход которого соединен со вторым входом триггера разрешения сравнения адресов, выход которого соединен со вторым входом первого элемента И и с четвертым входом схемы сравнения адресов, выход которого соединен со вторым входом триггера приема информации, выход которого соединен с первым входом второго элемента И, выход которого соединен со входом третьего элемента задержки, с третьим входом блока элементов И и со входом счетчика байтов, первый выход которого соединен со вторым входом блока элементов И, второй выход счетчика байтов соединен с первым входом третьего элемента И, выход которого является выходом стробирования записи ПРМ, третий выход блока приема сигналов соединен с первым входом второго элемента ИЛИ, выход которого соединен с первым входом триггера разрешения сравнения адресов, выход первого элемента И соединен со вторым входом второго элемента ИЛИ, второй вход схемы выделения байта «маркер» является входом кода «маркер» ПРМ, второй вход схемы сравнения адресов является входом кода адреса ПРМ, второй вход схемы выделения байта «конец сообщения» является входом кода «конец сообщения» ПРМ, первый выход схемы выделения байта «конец сообщения» соединен со вторым входом первого элемента ИЛИ и с первым входом триггера приема информации, второй выход схемы выделения байта «конец сообщения» соединен со входом второго элемента задержки, выход которого соединен со вторым входом второго элемента И, выход третьего элемента задержки соединен со вторым входом третьего элемента И, выход первого элемента И соединен со вторым входом второго элемента ИЛИ, а

блок передатчика содержит блок формирования манчестерского кода, счетчик байтов, регистр приема информации, триггер, формирующий управляющий сигнал передачи сообщения, триггер, формирующий управляющий сигнал передачи маркера, триггер, формирующий управляющий сигнал конца сообщения буферный, триггер, формирующий управляющий сигнал конца сообщения, триггер, формирующий управляющий сигнал передачи конца передачи, блок элементов И-ИЛИ, одиннадцать элементов И, четыре элемента ИЛИ, два элемента НЕ, шесть элементов задержки, информационный вход ПРД, вход кода «конец сообщения» ПРД, вход кода «маркер» ПРД, вход ТИ ПРД, вход «запуск» ПРД, вход «передать маркер» ПРД, вход «0 таймера» ПРД, вход «0 счетчика слов» ПРД, информационный выход ПРД, выход стробирования чтения ПРД, причем вход регистра приема информации является информационным входом ПРД, выход регистра приема информации соединен с первым входом блока элементов И-ИЛИ, выход которого соединен с первым входом блока формирования манчестерского кода, первый выход которого является информационным выходом ПРД, второй вход блока формирования манчестерского кода является входом ТИ ПРД, третий вход блока формирования манчестерского кода является входом кода «маркер» ПРД, четвертый вход блока формирования манчестерского кода является входом кода «конец сообщения» ПРД, второй выход блока формирования манчестерского кода соединен с третьим входом седьмого элемента И, со вторым входом восьмого элемента И, с первым входом девятого элемента И, с первым входом одиннадцатого элемента И, со вторым входом шестого элемента И, с четвертым входом первого элемента И и с четвертым входом третьего элемента И, выход которого соединен с первым входом второго элемента ИЛИ, выход которого является выходом стробирования чтения ПРД и соединен со входом четвертого элемента задержки, выход которого соединен с третьим входом четвертого элемента И, выход которого соединен с первым входом триггера конца сообщения буферного, первый выход которого соединен с первым входом пятого элемента И, второй выход триггера конца сообщения буферного соединен с первым входом четвертого элемента И и со вторым входом второго элемента И, выход которого соединен со вторым входом второго элемента ИЛИ, вход первого элемента задержки является входом «запуск» ПРД, выход первого элемента задержки соединен с первым входом первого элемента ИЛИ, выход которого соединен с четвертым входом блока элементов И-ИЛИ и со входом второго элемента задержки, выход которого соединен со входом счетчика байтов, с первым входом десятого элемента И и со входом шестого элемента задержки, выход которого соединен с третьим входом второго элемента И и со вторым входом пятого элемента И, выход которого соединен с первым входом триггера конца сообщения, первый выход которого соединен с третьим входом третьего элемента И, со вторым входом седьмого элемента И, с третьим входом девятого элемента И, с седьмым входом блока формирования манчестерского кода и с первым входом шестого элемента И, выход которого соединен со вторым входом триггера конца сообщения буферного и со входом пятого элемента задержки, выход которого соединен со вторым входом триггера конца сообщения, второй выход которого соединен с первым входом первого элемента И, выход которого соединен со вторым входом первого элемента ИЛИ, первый вход четвертого элемента ИЛИ является входом «передать маркер» ПРД, выход которого соединен со входом третьего элемента задержки, выход которого соединен с первым входом триггера маркера, выход которого соединен с пятым входом блока формирования манчестерского кода и со вторым входом одиннадцатого элемента И, выход которого соединен со вторым входом триггера маркера, вход первого элемента НЕ является входом «0 таймера» ПРД и соединен с первым входом седьмого элемента И, выход которого соединен со вторым входом третьего элемента ИЛИ, выход которого соединен со вторым входом триггера конца передачи, первый выход которого соединен с первым входом восьмого элемента И, выход которого соединен со вторым входом триггера передачи, со вторым входом четвертого элемента ИЛИ и с первым входом триггера конца передачи, второй выход которого соединен с третьим входом первого элемента И, выход первого элемента НЕ соединен с первым входом третьего элемента И, вход второго элемента НЕ является входом «0 счетчика слов» ПРД и соединен со вторым входом четвертого элемента И и со вторым входом девятого элемента И, выход которого соединен с первым входом третьего элемента ИЛИ, выход второго элемента НЕ соединен со вторым входом третьего элемента И, выход десятого элемента И соединен с первым входом триггера передачи, второй выход которого соединен со вторым входом десятого элемента И, первый выход соединен с шестым входом блока формирования манчестерского кода и со вторым входом первого элемента И, первый выход счетчика байтов соединен со вторым входом блока элементов И-ИЛИ, второй выход счетчика байтов соединен с третьим входом блока элементов И-ИЛИ, третий выход счетчика байтов соединен с первым входом второго элемента И и с третьим входом пятого элемента И, а

управляющий блок содержит генератор тактовых импульсов, шесть элементов И, счетчик слов, счетчик, определяющего очередность подключения устройства к общей шине, счетчик, определяющего длительность интервала времени, элемент задержки, вход кода длины сообщения УУ, вход «код интервала» УУ, вход «маркер» УУ, вход стробирования чтения УУ, выход «сообщение передано» УУ, выход «восстановить таймер» УУ, выход «0 счетчика слов» УУ, выход ТИ УУ, выход «запуск» УУ, выход «передать маркер» УУ, выход «0 таймера» УУ, причем первый вход счетчика слов является входом кода длины сообщения УУ, второй вход счетчика слов является входом стробирования чтения УУ, второй выход счетчика слов соединен с первым входом четвертого элемента И, первый выход счетчика слов соединен с первым входом пятого элемента И, с первым входом третьего элемента И и является выходом «0 счетчика слов» УУ, первый вход счетчика, определяющего длительность интервала времени является входом кода интервала УУ, первый выход счетчика, определяющего длительность интервала времени соединен с первым входом первого элемента И и со вторым входом третьего элемента И, выход которого является выходом «сообщение передано» УУ, вход шестого элемента И является входом «маркер» УУ и соединен со входом элемента задержки и со входом счетчика, определяющего очередность подключения устройства к общей шине, первый выход которого соединен с третьим входом пятого элемента И, с третьим входом четвертого элемента И, со вторым входом первого элемента И и со вторым входом шестого элемента И, выход которого соединен с третьим входом счетчика, определяющего длительность интервала времени, второй выход которого является выходом «0 таймера» УУ и соединен со вторым входом второго элемента И, выход которого является выходом «восстановить таймер» УУ, выход элемента задержки соединен со вторым входом четвертого элемента И и со вторым входом пятого элемента И, выход которого является выходом «передать маркер» УУ, выход четвертого элемента И является выходом «запуск» УУ, второй выход счетчика, определяющего очередность подключения устройства к общей шине соединен с первым входом второго элемента И, выход генератора тактовых импульсов является выходом ТИ УУ и соединен с третьим входом первого элемента И, выход которого соединен со вторым входом счетчика, определяющего длительность интервала времени.

| SU 1488815 A1, 23.06.1989 | |||

| RU 2058584 C1, 20.04.1996 | |||

| WO 9302423 A1, 04.02.1993 | |||

| Устройство для передачи информации | 1985 |

|

SU1251148A1 |

Авторы

Даты

2009-08-20—Публикация

2008-04-09—Подача