Изобретение относится к вычислительной технике, в частности к устройствам сопряжения абонентов в еистеме кольцевой структуры, и может быть использовано для приема и передачи информации в системах, использующих для обмена бит-ориентированные

протоколы синхронной СВЯЗИо

Целью из.обретения является расширение функщюнальных возможностей устройства за счет обеспечения дву- стороннего обмена данными между любыми абонентами кольцевой системы.

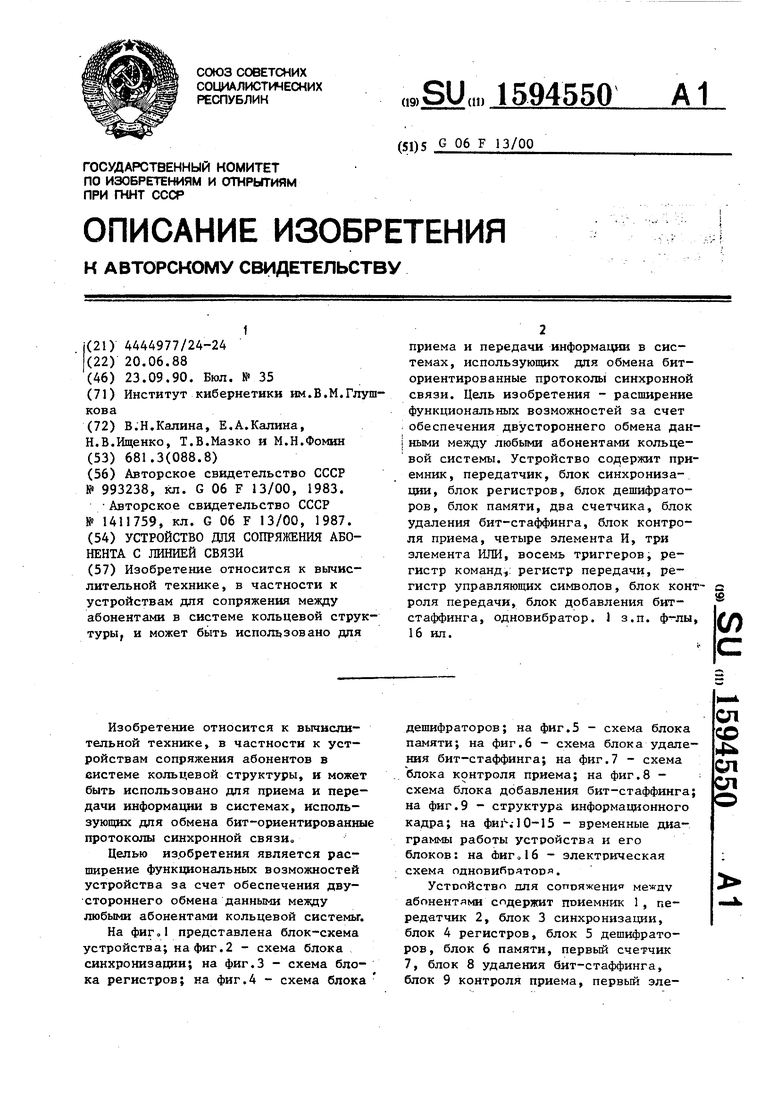

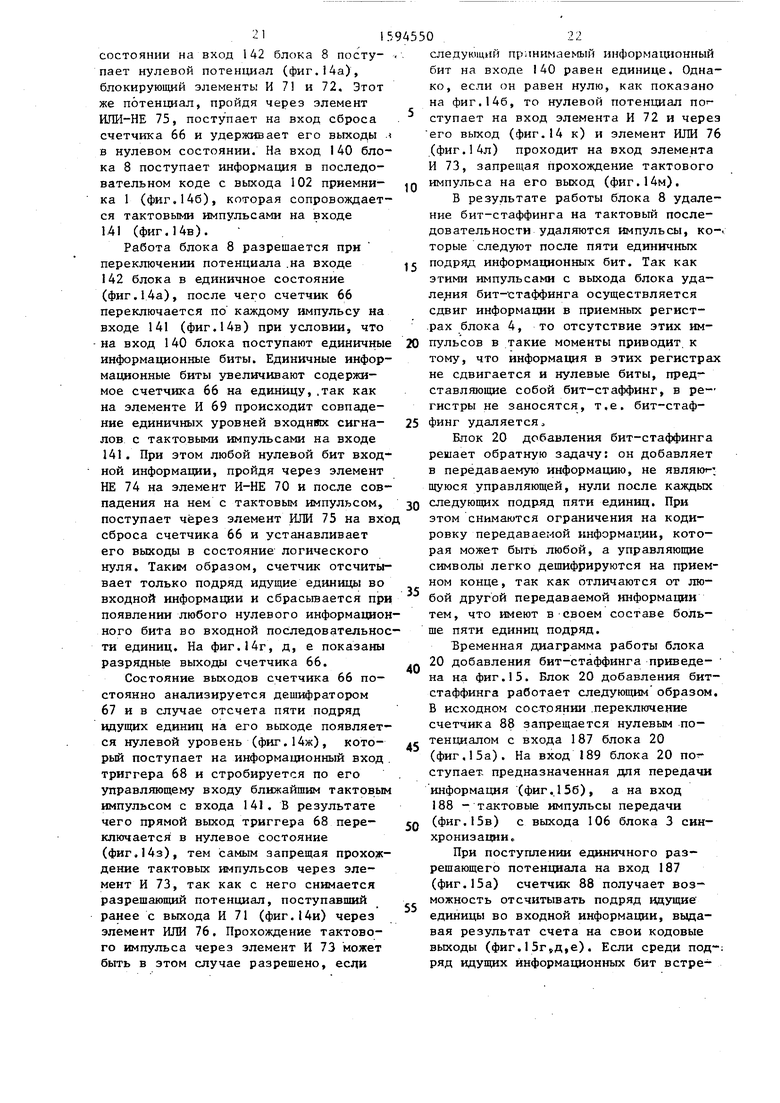

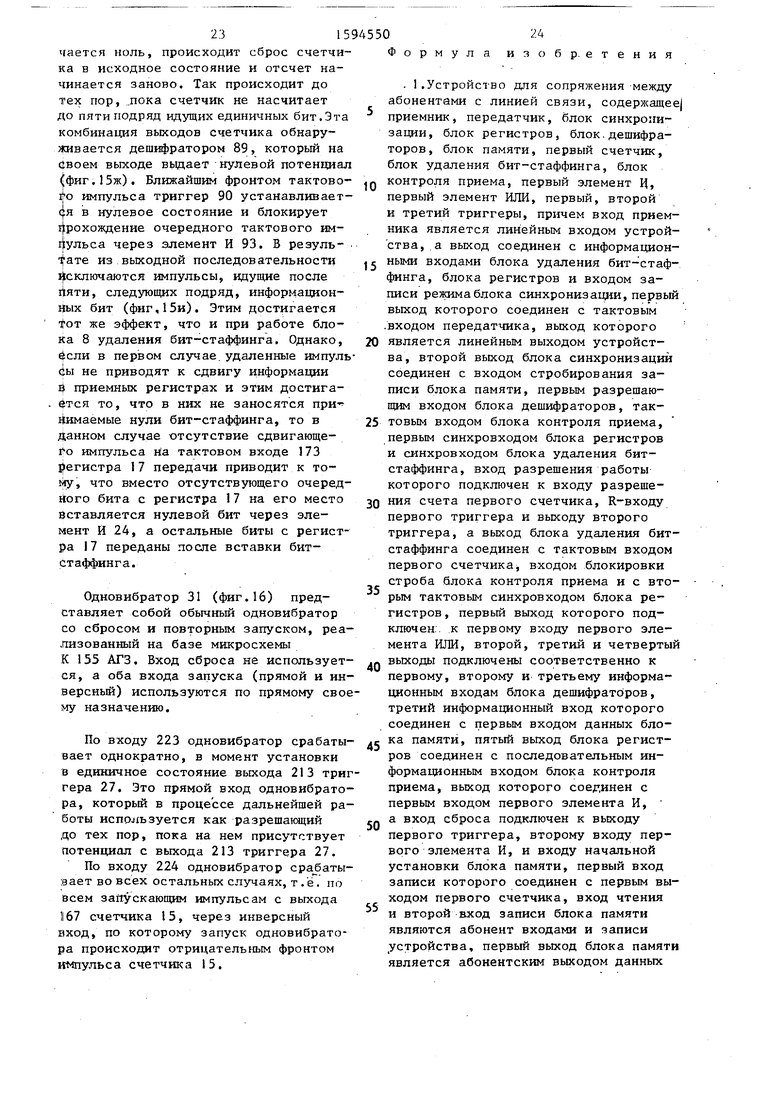

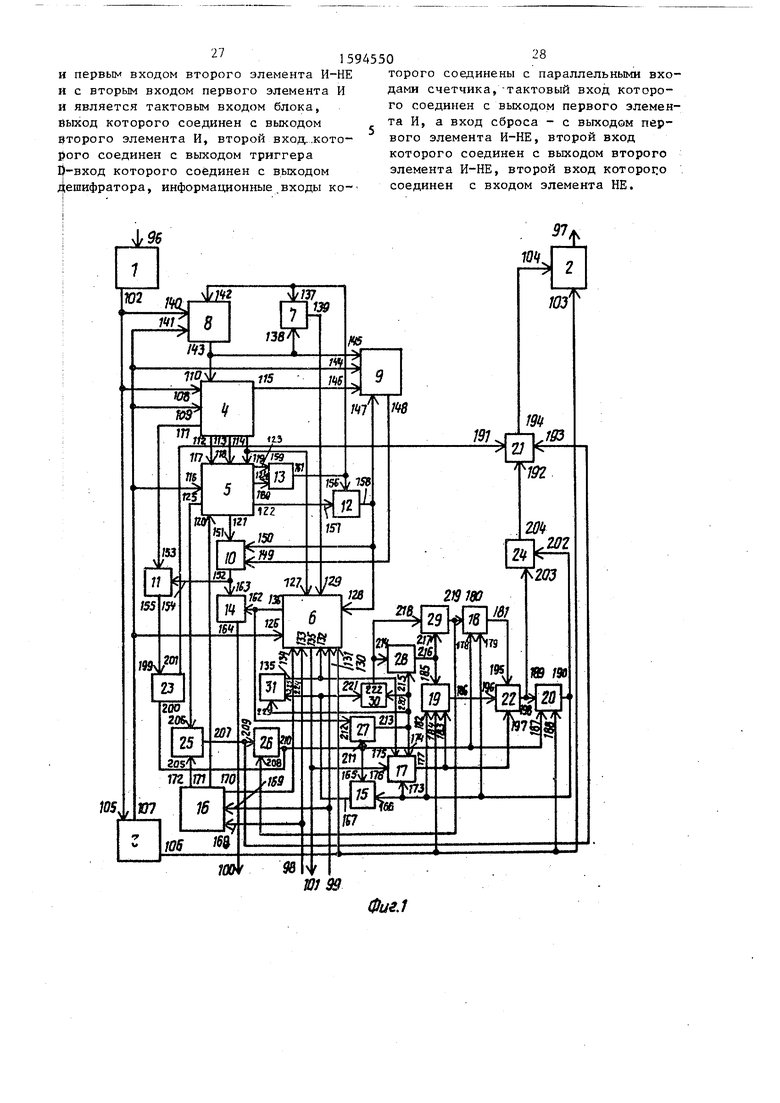

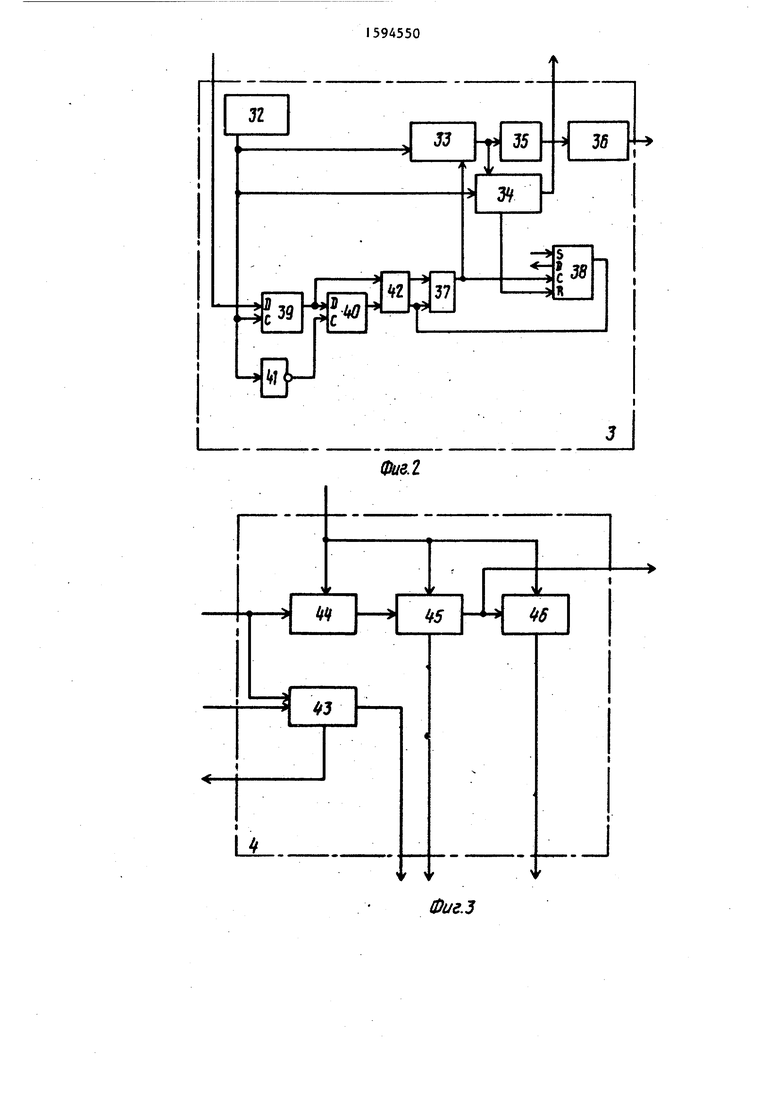

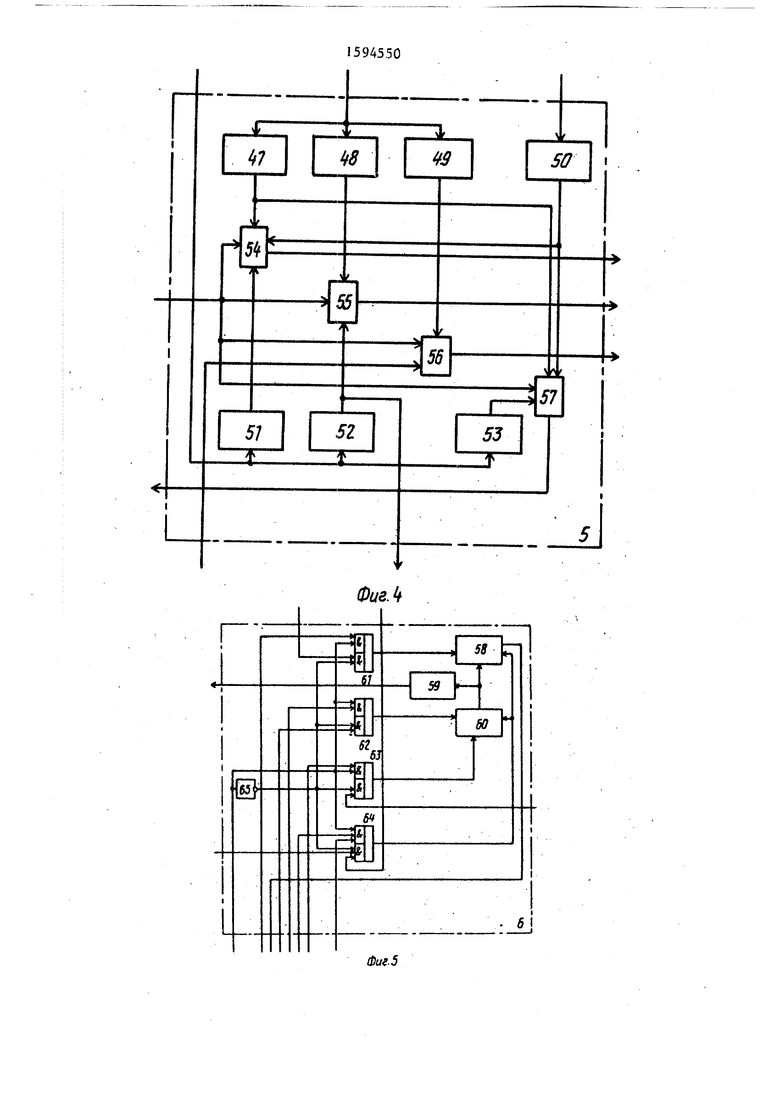

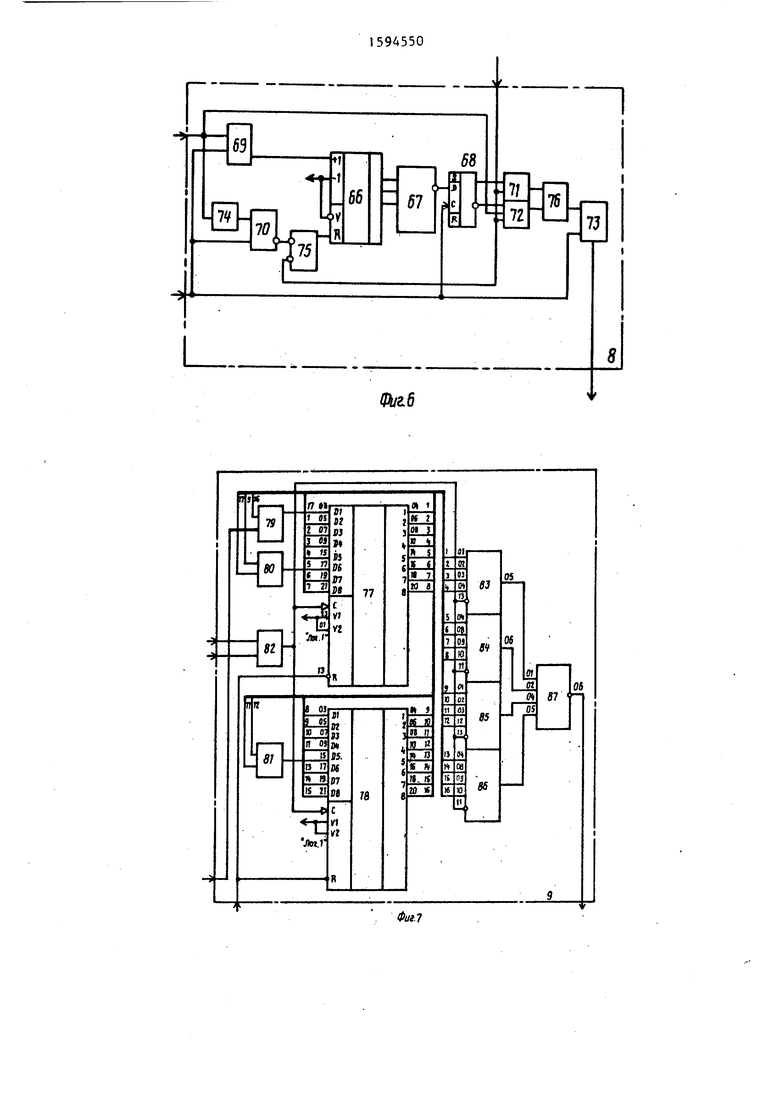

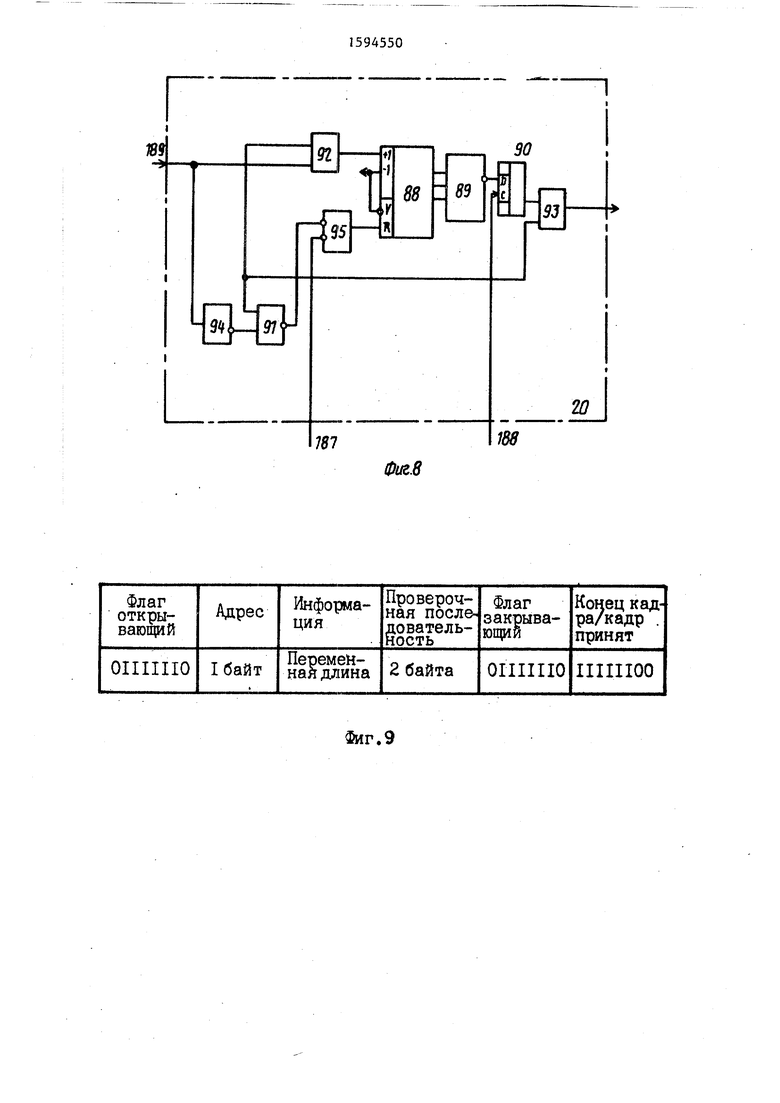

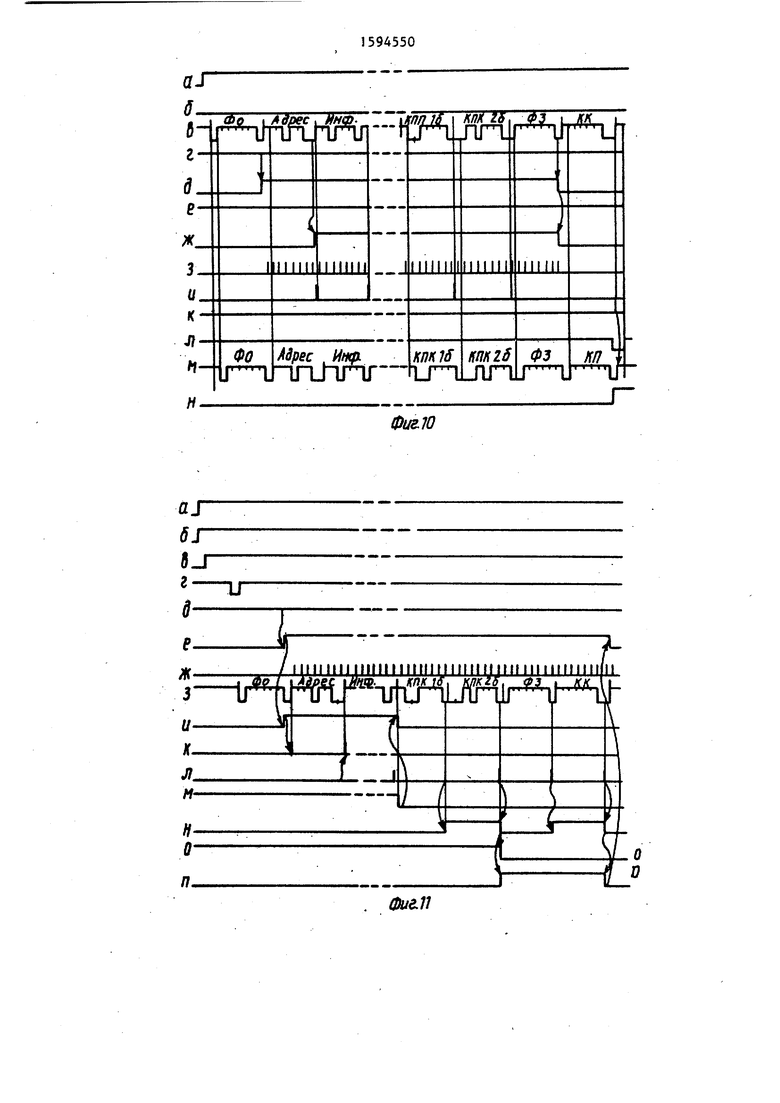

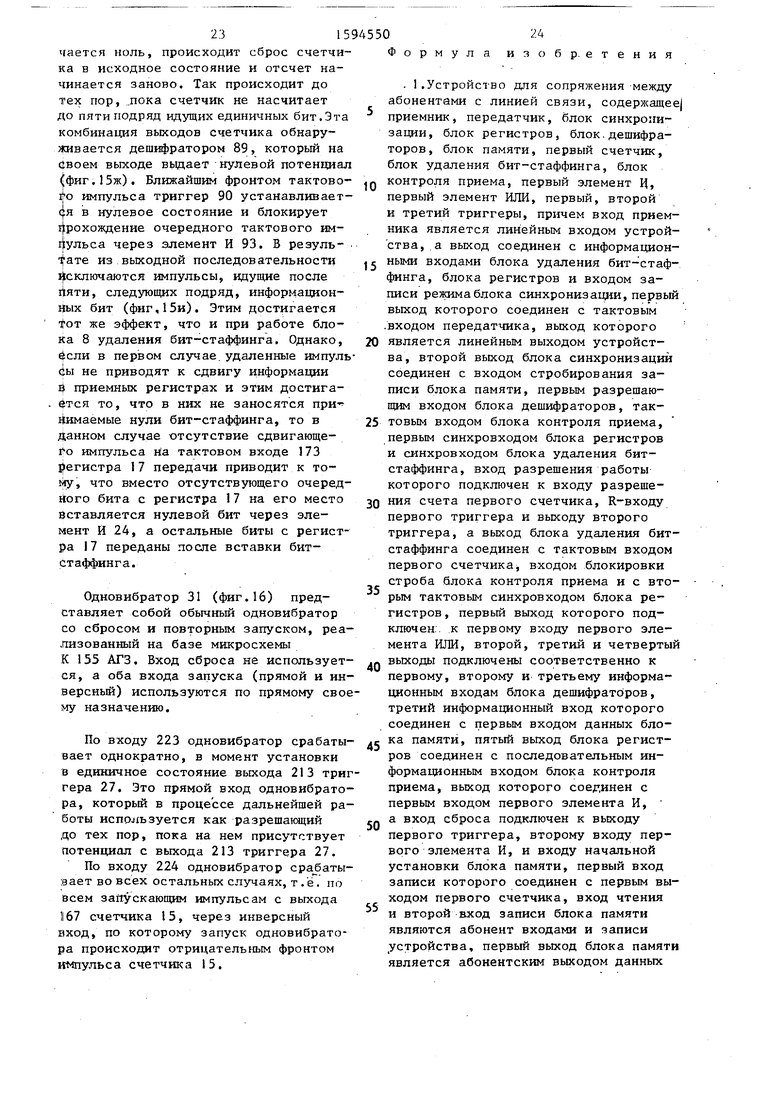

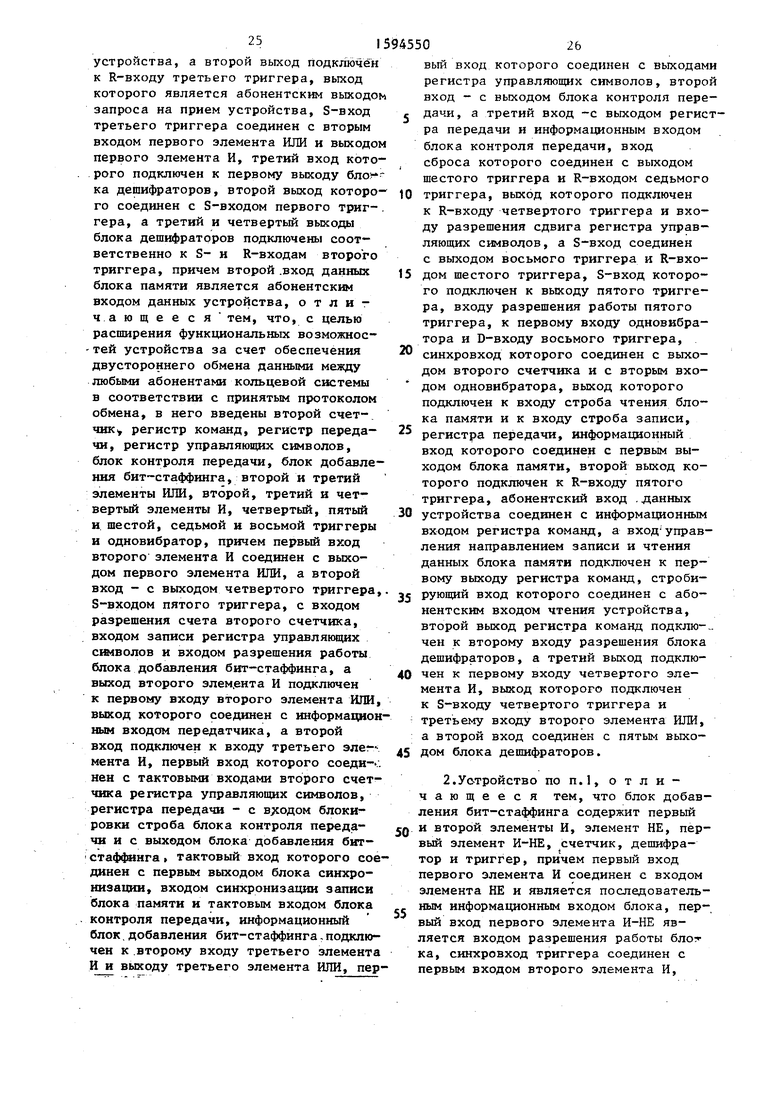

На фиг,1 представлена блок-схема устройства; на фиг.2 - схема блока синхронизации; на фиг.З - схема блока регистров; на фиг.4 - схема блока

дешифраторов; на фиг.5 - схема блока памяти; на фиг.6 - схема блока удаления бит-стаффинга; на фиг.7 - схема блока контроля приема; на фиг.8 - схема блока добавления бит-стаффинга; на фиг.9 - структура информационного кадра; на фиг.-10-15 - временные диаграммы работы устройства и его блоков: на Фиг,16 - электрическая схема одновибоятовя.

УСТООЙСТВГ) для СОТТОЯжеНИ МВ ЖДУ

абонентями содержит поиемник 1, передатчик 2, блок 3 синхронизации, блок 4 регистров, блок 5 дешифраторов, блок 6 памяти, первый счетчик 7, блок 8 удаления бит-стаффинга, блок 9 контроля приема, первый элеел

со

4

сл

С71

мент И 10, первый элемент ИЛИ 11, первьш 12, второй 13 и третий 14 триггеры, второй счетчик 15, регистр 16 команд, регистр 17 передачи, регистр 18 управляющих символов, блок 19 контроля передачи, блок 20 добавления бит-стаффинга, второй 21 и третий 22 элементы ИЛИ, второй 23, третий 24 и четвертый 25 элементы И, четвертый 26, пятый 27, шестой 28, седьмой 29 и восьмой 30 триггеры и одновибратор 31.

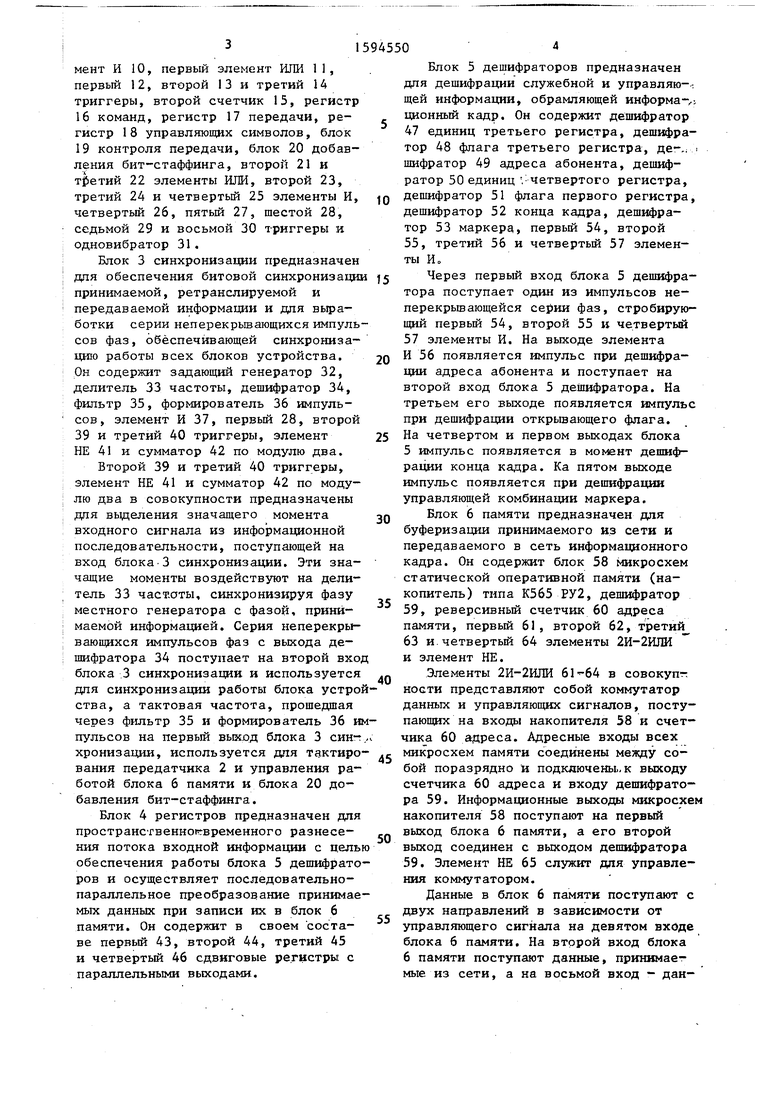

Блок 3 синхронизации предназначен дпя обеспечения битовой синхронизации принимаемой, ретранслируемой и передаваемой информации и дпя выработки серии неперекрывающихся импульсов фаз, обеспечивающей синхронизацию работы всех блоков устройства. Он содержит задающий генератор 32, делитель 33 частоты, дешифратор 34, фильтр 35, формирователь 36 импульсов, элемент И 37, первьй 28, второй 39 и третий 40 триггеры, элемент НЕ 41 и сумматор 42 по модулю два.

Второй 39 и третий 40 триггеры, элемент НЕ 41 и сумматор 42 по модулю два в совокупности предназначены дпя выделения значащего момента входного сигнала из информационной последовательности, поступающей на вход блока-3 синхронизации. Эти значащие моменты воздействуют на делитель 33 част.аты, синхронизируя фазу местного генератора с фазой, принимаемой информацией. Серия неперекрывающихся импульсов фаз с выхода дешифратора 34 поступает на второй вхо блока 3 синхронизации и используется дпя синхронизации работы блока устроства, а тактовая частота, прошедшая через фильтр 35 и формирователь 36 ипульсов на первый выход блока 3 синхронизадии, используется дпя тактирования передатчика 2 и управления работой блока 6 памяти и блока 20 добавления бит-стаффинга.

Блок 4 регистров предназначен для пространственноргвременного разнесения потока входной информации с цель обеспечения работы блока 5 дешифраторов и осуществляет последовательно- параллельное преобразование принимаемых данных при записи их в блок 6 памяти. Он содержит в своем составе первый 43, второй 44, третий 45 и четвертьй 46 сдвиговые регистры с параллельными выходами.

10

20

25

15 ,- 5945504

Блок 5 дешифраторов предназначен дпя дешифрации служебной и управляю-: щей информации, обрамляющей информа-,; ционный кадр. Он содержит дешифратор 47 единиц третьего регистра, дешифратор 48 флага третьего регистра, де-,: шифратор 49 адреса абонента, дешифратор 50 единиц .-четвертого регистра, дешифратор 51 флага первого регистра, дешифратор 52 конца кадра, дешифратор 53 маркера, первый 54, второй 55, третий 56 и четвертый 57 элементы Но

Через первый вход блока 5 дешифратора поступает один из импульсов не- перекрьшающейся серии фаз, стробирую- щий первый 54, второй 55 и четвертый 57 элементы И. На выходе элемента И 56 появляется импульс при дешифрации адреса абонента и поступает на второй вход блока 5 дешифратора. На третьем его выходе появляется импульс при дешифрации открьшающего флага. На четвертом и первом выходах блока

5импульс появляется в момент дешифрации конца кадра. Ка пятом выходе импульс появляется при дешифрации управляющей комбинации маркера.

Блок 6 памяти предназначен для буферизации принимаемого из сети и передаваемого в сеть информационного кадра. Он содержит блок 58 микросхем статической оперативной памяти (накопитель) типа К565 РУ2, дешифратор 59, реверсивный счетчик 60 адреса памяти, первый 61, второй 62, третий 63 и. четвертый 64 элементы 2И-2ИШ и элемент НЕ.

Элементы 2И-2ШШ 61 64 в совокупности представляют собой коммутатор данных и управляющих сигналов, поступающих на входы накопителя 58 и счетчика 60 адреса. Адресные входы всех микросхем памяти соединены между собой поразрядно и подключены,, к выходу счетчика 60 адреса и входу дешифратора 59. Информационные выходы микросхем накопителя 58 поступают на первый выход блока 6 памяти, а его второй выход соединен с выходом дешифратора 59. Элемент НЕ 65 служит для управления коммутатором.

Данные в блок 6 памяти поступают с двух направлений в зависимости от управляющего сигнала на девятом входе блока 6 памяти. На второй вход блока

6памяти поступают данные, принимаемые из сети, а на восьмой вход - дан30

35

40

45

50

55

ые от абонента, предназначенные для ередачи в сеть. Выход второго элемена 2И-2ИЛИ 62 соединен с вычитающим I ходом счетчика 60 адреса, а его сумирующий вход соединен с выходом четертого элемента 2И-2ИЛИ 64, Сигнал с выхода третьего элемента 2И-2ИШ1 63 поступают на вход сброса счетчика 60 адреса

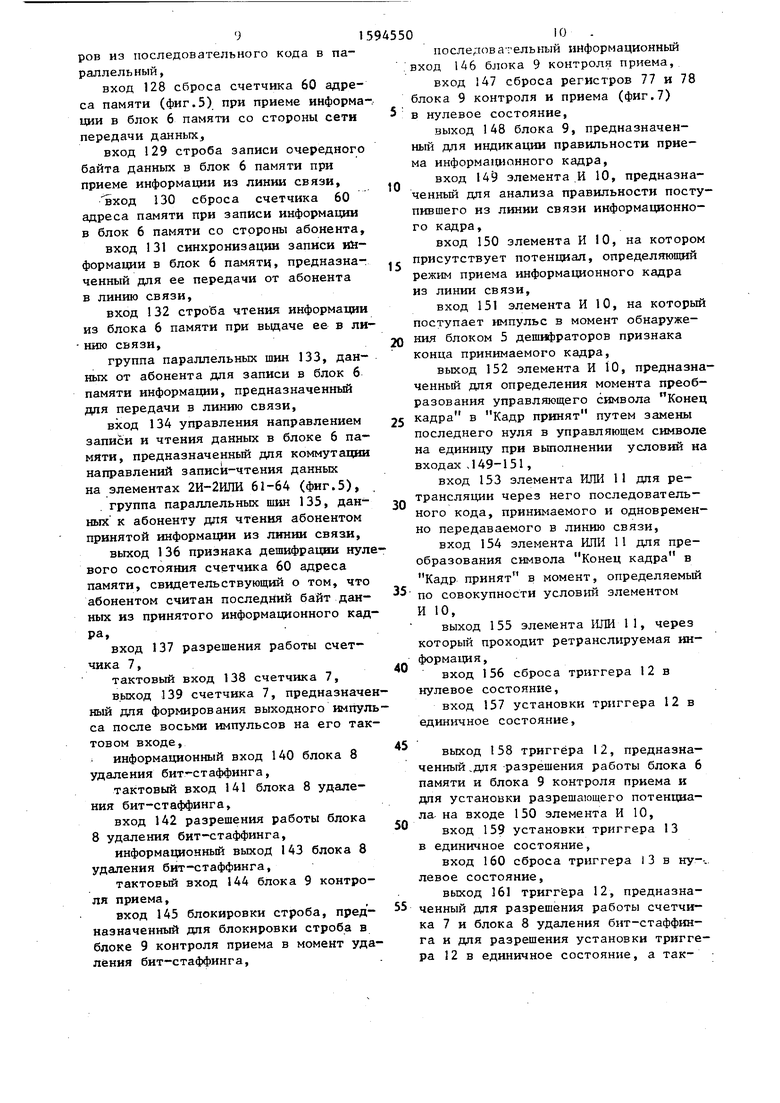

Блок 8 удаления бит-стаффинга предназначен для удаления из принимаемой информации нулей, которые добавляются в информационную часть при передаче дпя отделения управляющих символов от информационной части передаваемого по кольцу пакета. Он содержит счетчик 66, дешифратор 67, триггер 68, первый 69, второй 70, третий 71, четвертьш 72 и пятый 73 элементы И, элемент НЕ 74, первый 75 и второй 76 элементы ИЛИ.

Информация, передаваемая по коль-., цу, через первый вход блока 8 поступает на элементы И 69 и 72, а также через элемент НЕ 74 - на вход элемента И 70. Через второй вход на первый 69, второй 70 и пятый 73 элементы И поступает одна из тактовых серий блока 3 синхронизации. Третий вход является управляющим и предназначен дпя разрешения работы блока 8. Нулевой уровень сигнала через элемент ИЛИ 75 запрещает переключение счетчика 66 и блокирует элементы И 71 и 72.

Блок 8 удаления бит-стаффинга работает следующим образом.После прихода разрешающего потенциала на третий вход блока 8 счетчика 66 переключается в следующее состояние только по приходу подряд не- .. скольких единиц. Если в принимаемой информации меньше пяти единиц подряд появляется нуль, он сбрасьтает счетчик 66 в исходное состояние. Если счетчик 66 насчитьшает подряд пять единиц, на выходе дешифратора 67 появится нулевой потенциал, устанавливающий в нулевое состояние триггер 68. После этого, если на первом входе блока 8 появится следующим нулевой бит информации, элемент И 72 окажется заблокированным, что приведет к блокировке выработки выходного импульса блока 8, являющегося стробом блока 4 приемных регистров.

Блок 9 контроля приема предназначен для подсчета контрольной последо

5

вательности кадра информации и проверки правильности приема поступающей информации. Он содержит первый 77 и второй 78 регистры, первый 79, второй 80 и третий 81 сумматоры по модулю два, первый 82, второй 83, третий 84, четвертый 85, пятый 86 и шестой 87 элементы И.

Регистры 77 и 78 и сумматоры 79-81 по модулю два в совокупности представляют собой схему подсчета контрольной последовательности кода с использованием образующего полинома 1. Элементы И 830

5

0

5

87 представляют собой дешифратор нуля.

Суть работы блока 9 сводится к ...л подсчету контрольной суммы по образующему полиному и сложению ее с контрольной Если искажения информации в канале связи не бьто,то результатом проверки является нулевое состояние регистров блока 9 и на его выходе появится сигнал, свидетельствующий о правильности приема информации.

Регистр 16 команд предназначен для управления режимами работы устройства и представляет собой, три триггера с возможностью их установки и сброса.абонентом. Первый выход задает направление записи информации в блоке 6 памяти со стороны линии связи или от абонента. Второй выход является выходом готовности работы устройства в составе кольцевой системы передачи данных. Третий выход определяет режим приема или передачи информации.

Блок 19 контроля передачи предназначен дпя формирования контрольной последовательности кадра с использованием образующего; полинома X + Х + + Х + 1. Эта контрольная последовательность длиной два байта прифор- мировьшается к концу информационной части сообщения и служит для ....л- контроля правильности передачи в приемных точках кольцевой системы. Блок 19 контроля передачи построен аналогично блоку 9 контроля приема, показанному на фиг.7, и отличается от него отсутствием схемы дешифрации нуля, т.е элементов И 83-87 Вы- ходом блока 19 в этом случае является выход ста ршего разряда сдвигового регистра 78, с которого контрольная последовательность под управлением так-

0

5

0

товьгх импульсов с первого выхода блока 3 синхронизации поступает на второй вход третьего элемента, отсутствует импульс сдвига передающих регистров, в результате чего в информацию, передаваемую в линию связи, . добавится нулевой бит. Если в пере- да аемой информации содержится подряд

первый синхровход 109 блока 4 регистров для сдвига информации без удаления бит-стаффинга,

второй синхровход ПО блока 4 для сдвига ин формации с удалением бит- стаффинга,

последовательный информационный выход блока 4 для регистрации

.--. ,-,fj. --r i -I -- - .. -г vi A jTi 1 оаипмъ

меньше пяти единиц, ближайший нулевой ,Q информации соседнему устройству коль- бит каждый паз пооияиопит г(;плп .n- тюппл гт тлатт, „««

20

25

30

j бит каждый раз производит сброс счет- I чика 88 в нулевое состояние и он на- i чинает заново отсчет следующих подряд i единиц о Таким образом обеспечивается

; прозрачность передаваемо, информации.. }5 : Блок добавления бит-стаффинга со-J держит счетчик 88, дешифратор 89, триггер 90, второй элемент И-НЕ 911, : : первьш 92 и второй 93 элементы И, : элемент НЕ 94 .и первый элемент : И-НЕ 95о

; Связи, представленные на фкг.1: ; информационный вход 96 устройст- : ва, подключаемый к двухпроводной ; входной линии связи,

информационный выход 97 устройства, подключаемый к двухпроводной выходной линии связи,

: группа шин 98 данных от абонента, по которым передается информащш в параллельном коде,

шина 99 управлений от абонента, по которой передаются стробирующие сигналы, сопровождающие информацию на шинах 98 данных от абонента,

выход 100, признак состояния, свидетельствующий о необходимости пере- дачи абоненту принятого сообщения, устанавливается при получении информационного кадра на локальной сети, сбрасьшается после передачи информационного кадра абоненту,

группа шин 101 данных от устройства, по которым передается информация в параллельном коде к абоненту,

информационный выход 102 приемника. 1 ,

тактовьй вход 103 передатчика 2, информационный последовательный вхрд 104 передатчика 2, вход 105 задания режима блока 3 синхронизации,

тактовый вход 106 блока 3 синхронизации для синхронизации передачи данных в локальную сеть,

35

40

45

50

цевой локальной сети,

параллельные информационные выхо- ды 112-114 блока 4 для организации дешифрации управляющих символов кадра в блоке 5 дешифраторов,

последовательный информационный выход 115 блока 4 для организации работы блока 9 контроля приема,

первый разрешающий вход 116 блока 5 дешифраторов, через который осуществляется стробирование элементов И 54-57 (фиг,4) при дешифрации управ- .ляющих символов,

параллельные информационные вхо-. ды 117-119 блока 5 дешифраторов, через которые поступают разнесенные во времени принимаемые кодовые комбинации,

второй разрешающий вход 120, на который поступает потенциал с второго выхода регистра 16 команд, разрешающий устройству осуществлять дешифрацию адреса, поступающего из сети передачи данных,

выход 121 признака дешифрации конца кадра в принимаемом .сообщении, вькод 122 признака дешифрации адреса устройства, который.возникает при обращении к устройству со стороны других абонентов сети в момент ,. опознования (дешифрации) данным устройством собственного адреса,

выход 123 признака дешифрации флага, открьтающего в принимаемом сообщении,

выход 124 признака дешифрации фла га, закрывающего в принимаемом сообг; щении,

выход 125 признака дешифрации маркера ,

тактовый вход 126 блока 6 памяти, через который осуществляемся стробирование записи в блок принимаемой

тактовый выход 107 блока 3 синхро- ,, сети передачи данных информации.

низации для синхронизации приема дан ных из линии связи,

последовательный информационный вход 108 блоков 4 регистра.

параллельный вход 127 блока 6 па-.: мяти, на который поступает принимаемая из сети передачи данных информации, преобразованная блоком 4 регист

45508

первый синхровход 109 блока 4 регистров для сдвига информации без удаления бит-стаффинга,

второй синхровход ПО блока 4 для сдвига ин формации с удалением бит- стаффинга,

последовательный информационный выход блока 4 для регистрации

-I -- - .. -г vi A jTi 1 оаипмъ

Q информации соседнему устройству коль- тюппл гт тлатт, „««

,Q информации соседнему устройству коль- тюппл гт тлатт, „««

20

25

30

}5

35

0

5

0

цевой локальной сети,

параллельные информационные выхо- ды 112-114 блока 4 для организации дешифрации управляющих символов кадра в блоке 5 дешифраторов,

последовательный информационный выход 115 блока 4 для организации работы блока 9 контроля приема,

первый разрешающий вход 116 блока 5 дешифраторов, через который осуществляется стробирование элементов И 54-57 (фиг,4) при дешифрации управ- .ляющих символов,

параллельные информационные вхо-. ды 117-119 блока 5 дешифраторов, через которые поступают разнесенные во времени принимаемые кодовые комбинации,

второй разрешающий вход 120, на который поступает потенциал с второго выхода регистра 16 команд, разрешающий устройству осуществлять дешифрацию адреса, поступающего из сети передачи данных,

выход 121 признака дешифрации конца кадра в принимаемом .сообщении, вькод 122 признака дешифрации адреса устройства, который.возникает при обращении к устройству со стороны других абонентов сети в момент ,. опознования (дешифрации) данным устройством собственного адреса,

выход 123 признака дешифрации флага, открьтающего в принимаемом сообщении,

выход 124 признака дешифрации фла га, закрывающего в принимаемом сообг; щении,

выход 125 признака дешифрации маркера ,

тактовый вход 126 блока 6 памяти, через который осуществляемся стробирование записи в блок принимаемой

, сети передачи данных информации.

сети передачи данных информации.

параллельный вход 127 блока 6 па-.: мяти, на который поступает принимаемая из сети передачи данных информации, преобразованная блоком 4 регист9

ров из последовательного кода в параллельный ,

вход 128 сброса счетчика 60 адреса памяти (фиг.5) при приеме информации в блок 6 памяти со стороны сети передачи данных,

вход 129 строба записи очередного байта данных в блок 6 памяти при приеме информации из линии связи,

Таход 130 сброса счетчика 60 адреса памяти при записи информации в блок 6 памяти со стороны абонента, вход 131 синхронизации записи иИ- формации в блок 6 памяти, предназначенный для ее передачи от абонента в линию связи,

вход 132 стро ба чтения информации из блока 6 памяти при выдаче ее в ли- нию связи,

группа параллельных шин 133, данных от абонента для записи в блок 6 памяти информации, предназначенный для передачи в линию связи,

вход 134 управления направлением записи и чтения данных в блоке 6 памяти, предназначенный для коммутации направлений записи-чтения данных на элементах 2И-2ИЛИ 61-64 (фиг.5), группа параллельных шин 135, данных к абоненту для чтения абонентом принятой информации из линии связи,

выход 136 признака дешифрации нулвого состояния счетчика 60 адреса памяти, свидетельствующий о том, что абонентом считан последний байт данных из принятого информационного кадра,

вход 137 разрешения работы счетчика 7,

тактовый вход 138 счетчика 7, в.ыход 139 счетчика 7, предназначеный для формирования выходного импулса после восьми импульсов на его тактовом входе,

информационный вход 140 блока 8 удаления бит-стаффинга,

тактовый вход 141 блока 8 удаления бит-стаффинга,

вход 142 разрешения работы блока 8 удаления бит-стаффинга,

информационный выход 143 блока 8 удаления бит-стаФФинга,

тактовый вход 144 блока 9 контроля приема,

вход 145 блокировки строба, предназначенный для блокировки строба в блоке 9 контроля приема в момент удаления бит-стаффинга.

94550

10

.

нь

10

15

20

25

30

35

40

45

50

55

последова-г ельный информационный вход 146 блока 9 контроля приема,

вход 147 сброса регистров 77 и 78 блока 9 контроля и приема (фиг.7) в нулевое состояние,

выход 148 блока 9, предназначенный для индикации правильности приема информационного кадра,

вход 149 элемента,И 10, предназначенный для анализа правильности поступившего из линии связи информационного кадра,

вход 150 элемента И 10, на котором присутствует потенциал, определяющий режим приема информационного кадра из линии связи,

вход 151 элемента И 10, на который поступает импульс в момент обнаружения блоком 5 дешифраторов признака конца принимаемого кадра,

выход 152 элемента И 10, предназначенный для определения момента преобразования управляющего символа Конец кадра в Кадр принят путем замены последнего нуля в управляющем символе на единицу при вьтолнении условий на входах Л 49-151,

вход 153 элемента ИЛИ 11 для ретрансляции через него последовательного кода, принимаемого и одновременно передаваемого в линию связи,

вход 154 элемента ИЛИ 11 для преобразования символа Конец кадра в Кадр принят в момент, определяемый по совокупности условий элементом

И 10,

выход 155 элемента ИЛИ 11, через который проходит ретранслируемая информация,

вход 156 сброса триггера 12 в нулевое состояние,

вход 157 установки триггера 12 в единичное состояние,

выход 158 триггера 12, предназначенный .для разрешения работы блока 6 памяти и блока 9 контроля приема и для установки разрешающего потенциала- на входе 150 элемента И 10,

вход 159 установки триггера 13 в единичное состояние,

вход 160 сброса триггера 13 в ну--., левое состояние,

выход 161 тригг ера 12, предназначенный для разрешения работы счетчика 7 и блока 8 удаления бит-стаффинга и для разрешения установки триггера 12 в единичное состояние, а так- ;

же для сброса его в нулевое состояние ,

вход 162 сброса триггера 14 в нулевое состояние,

вход 163 установки триггера 14 в единичное состояние, , выход 164 триггера 14 для передачи сигнала Внимание абоненту, предназначенный для сообщения абоненту о том, что в блок 6 памяти принято сообщение из кольцевой сети,

вход 165 разрешения работы счетчика 15,

счетный вход 166 счетчика 15,

выход 167 счетчика 15, на котором появляется сигнал после отсчета вось ми тактовых сигналов на счетном де, т„е. после передачи в линию связи одного байта информаизш из блока 6 памяти,

группа информационных входов 168 регистра команд для записи кода команды в регистр 16,

управляющий (.стробирующий) вход 169 регистра 16 команд,

первый выход 170 регистра 16 команд, предназначенный для задания направления передачи данных в блоке 6 памяти (при равенстве нулю разряд устанавливает режим записи данных со стороны линии связи, а при равенстве единице задается режим записи данных в блок 6 со стороны абонента)

второй выход 171 регистра 16 ко- манд, предназначенный для разрешения работы устройства в составе сети передачи данных (состояние логического нуля запрещает работу в составе сети, а состояние логической единицы разрешает такую работу),

третий выход 172 регистра 16 команд является признаком конца записи массива информации в блок 6 памяти со стороны абонента, установкой данного разряда в состояние логической единицы абонент переводит устройство в режим поиска управляющей комбинации Маркер с последующей передачей записанного массива в кольцевую систему при обнаружении такой комбинации.

тактовый вход 173 регистра 17 пе-

редачи, на который поступают сдвигающие тактовые импульсы,

вход 174 разрешения работы регистра 17 передачи.

10

15

0

5

0

5

0

5

тактовый вход 175 параллельный записи байта данных в регистр 17 передачи (вход строба),

группа параллельных информационных входов 176 регистра 17,

последовательный информационный выход 177 регистра 17 передачи,

тактовый вход 178 параллельного занесения в регистр 18 кодов управляющих символов Флаг закрьшающий и Конец кадра, набранных перемычками в виде комбинаций логических уровней нулей и единиц на его входах (не показаны), так как не имеют функциональной связи с остальной частью схемы,

тактовый вход 179 регистра 18, предназначенный для подачи сдвигающих импульсов,

вход 180 разрешения сдвига информации в регистре 18,

последовательный информационный выход 181 регистра 18,

вход 182 блокировки строба в блоке 19 контроля передачи в момент добавления бит-стаффинга,

последовательный информационный вход 183 блока 19,

тактовьй вход 184 блока 19, вход 185 сброса регистров, пред- . назначенный для разрешения работы блока 19,

последовательный информационный выход 186 блока 19 контроля передачи,

вход 187 разрешения работы блока 20 добавления бит-стаффинга,

тактовый вход 188 блока 20 добавления бит-стаффинга,

последовательный информационный вход 189 блока 20,

выход 190 блока 20, вход: 191 элемента ИЛИ 21, предназначенный для передачи ретранслируемой информации,

вход Л 92 элемента ИЛИ 21, предназначенный для передачи информации от данного абонента в кольцевую систему,

вход 193 элемента ИЛИ 21, предназначенный для преобразования управляющей комбинации Маркер в комбинацию Флаг открывающий, выход 194 элемента ИЛИ 21, вход 195 элемента ИЛИ 22, предназначенный для передачи уиравляющих символов,

вход 196 элемента ИЛИ 22, предназначенный для передачи контроль. 1

ной последовательности кадра, сформированной блоком 19 контроля передачи,

вход 197 элемента ИЛИ 22, предназначенный для передачи информационной части кадра,

выход 198 элемента ИЛИ 22,

последовательный информационный вход 199 элемента И 23, предназначенный для передачи информации в режиме ретрансляции,

вход 200 блокировки элемента И 23, предназначенный для запрета ретрансля цин во время передачи информации ст данного абонента в кольцевую систему,

выход 201 элемента И 23,

вход 202 элемента И 24, предназначенный для добавления бит-стаффинга в передаваемую информацию,

вход 203 элемента И 24, предназначенный для передачи сформированного для передачи в кольцевую систему кадра,

выход 204 элемента И 24,

вход 205 элемента И 25, предназначенный для разрешения устройству реа- гироцать на управляющую комбинацию Маркер после записи абонентом предназначаемой для передачи информации в буферную память блока 6,

вход 206 элемента И 25, на который поступает признак дешифрации управляющей комбинации Маркер,

выход 207 элемента И 25,

вход 208 сброса триггера 26 в исходное состояние,

вход 209 установки триггера 26,

выход 210 триггера 26, предназначенный для разрешения работы регистра 18 управляющих символов блока 20 добавления бит-стаффинга и счетчика 15 установки в единицу триггера 27 и запрещения прохождения информации через элемент И 23 в режиме передачи- (триггер передачи),

вход 211 установки в единицу триггера 27,

вход 212 сброса в нуль триггера

27.

выход 213 триггера 27, предназначенный для-разрешения работы регистра 17 передачи и одновибратора 31 и- разрешения переключения триггеров. 28 и 30 (триггер разрешения вьщачи информации) ,

вход 214 сброса триггера 28, вход 215 установки триггера 28, выход 216 триггера 28, предназна

435014

ченный для разрешения работы блока 19 контроля и сброса триггера 29,

вход 217 сброса триггера 29, , вход 218 установки триггера 29, выход 219 триггера 29, предназначенный для разрешения сдвига информации в регистре 18 управляющих символов и сброса в исходное состояние 10 триггера 26,

вход 220 данных счетного триггера 30,

счетный вход 221 триггера 30,

выход 222 триггера 30, преднаэна- J5 ченный для управления переключением триггеров 28 и 29,

вход 223 запуска и разрешения работы одновибратора 31 во время вьща- чи информации из буферной памяти бло- 20 ка 6 в линию связи,

вход 224 запуска одновибратора 31«

выход 225 одновибратора 31, предназначенный для вьфаботки импульсов чтения информации из блока 6 памяти 25 и записи этой информации в регистр 17 передачи.

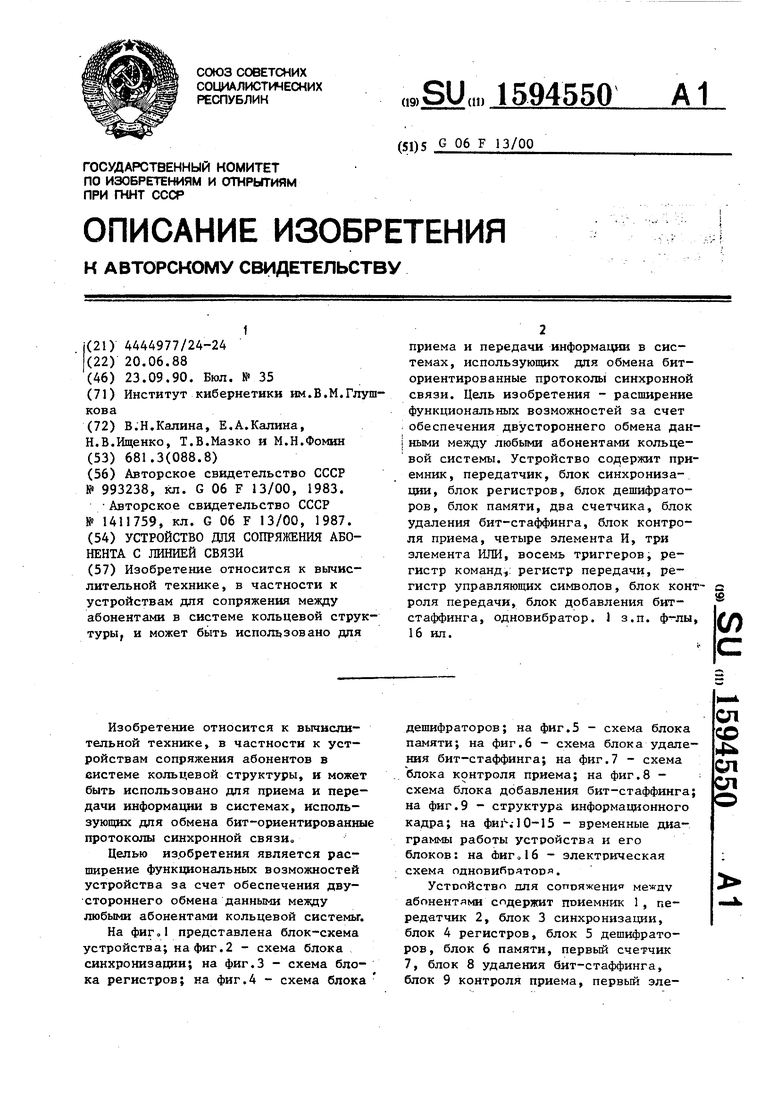

В режиме приема информации из линии связи (фиг о 10) перед началом работы устройства выход 171.регистра 30 16 команд должен быть установлен абонентом в состояние логической единицы (фиг.Юа) с целью разрешения работы устройства в составе кольцевой се-т ти. передачи данных Этот сигнал через вход 120 блока 5 дешифраторов поступает на элемент И 56 блока 5 и разрешает устройству реагировать при опознавании собственного адреса. Выход 170 регистра 16 команд должен быть установлен в состояние логичес-. кого нуля () с целью задания соответствующего направления записи и чтения информации в блоке 6 памяти (фиг.5).

де Находясь в режиме приема, устройство осуществляет ретрансляцию принимаемой информации. При этом информация на выходе 97 устройства в точности соответствует информации на его входе 96 с задержкой из-за ретрансля г ции на один бит. На фиг Л О показана информация на выходе 102 приемника 1 ((}мг.10в) и на входе 104 передат йнка 2 (фиг.10м).

При появлении управляющего символа Флаг открывающий (фиг.Юв) блок 5 дешифраторов производит его опозно- вание и выдает на своем выходе 123 (фиг.Юг) импульс, устанавливающий

35

40

50

15

Флага начинает работу блок 8

выход 161 триггера 13 (фиг.Юд) в состояние логической единицы Этим г, производится подготовка к установке в состояние логической единицы вьжо- да 157 триггера 12, что произойдет в том случае, если передаваемый в этот момент по кольцевой сети кгщр предназначен для данного абонента., В таком случае-, после дешифрации Флага открывающего на выходе 122 блока 5 дешифраторов появится импульс (фиг.Юе), свидетельствующий о том, что адрес данного устройства опознан fe блоке 5. Этот импульс уста- ; навливает выход 158 триггера 12 I (фигЛОж) в состояние логической ; единицы.

; С момента опознава 1ия : открьшающего

: удаления бит-стаффинга, на выходе 143 I которого формируются; тактовые импуль- i сы (фиг.Юз), управляющие работой ; блока 4 регистров, блока 9 контроля : приема и счетчика 7. Последний от- I считав восемь сдвиговых импульсов : на своем входе, вьщает на своем выхо- ; де 139 импульс (фиг.Юи), свидетель- ствующий о том, что в сдщиговом стре 46 блока 4 регистров (фиг,3) ; накоплен байт информации для записи в блок 6 памяти. Данные с выхода 114 блока 4 регистров поступают в паргш- лельном коде на входу 127 блока б памяти и стробируются этим импульсом по входу 129 блока 6. Этим же импульсом в блоке 6 памяти осуществляется : переключение следующего адреса ячейки памяти.

Если адрес устройства опознан (фиг.1Ое), последовательно-параллельное преобразование поступающей информации и запись ее в паййть блока 6 продолжается. Так как сдвиг информа,

ции в регистрах производится тактовьг-

ми импульсами с выхода 143 блока 8 удаления бит-стаффинга, в блок 6 памяти производится запись информал; ,. дни, освобожденный от бит-стаффинга. Ретрансляция же информации происходит с выхода 11I блока 4 регистров под действием тактовых импульсов на его синхровходе Ю9, поступающкк непосредственно с выхода 107 блока 3 синхронизации, поэтому она не освобождена от бит-стаффинга, а передается в неизменном виде (фиг.10м). После дешифрации управляющего симво- ла Флаг закрьшающий (фиг.Юв) про

4550 . It)

исходит сброс триггера 13 (фиг.Юд)

и триггера I 2(Фиг . 10ж) . При этом

прекращается запись информации в блок 6 памяти.

В момент прохождения последнего управляющего символа в данном сообщении Конец кадра на выходе 121 блока 5 дешифраторов формируется соответствующий импульс (фиг.Юк), которым стробируется потенциал, поступающий , с выхода 148 блока 9 контроля приема (фиг.10л). Нулевой уровень потенциа-. ла свидетельствует о совпадении контрольных последовательностей, т.е. нормальном заверщении приема информации из линии связи. Импульс с выхода 121 блока 5, пройдя через элемент ИЛИ 11, заменяет последний нуль в управляющем символе Конец кадра на единицу, тем самым преобразуя его в .

10

15

20

символ Кадр принят (фиг.10м). Од5

0

5

новременно импульс с выхода 152 п ерво- го элемента И 10 устанавливает выход 164 триггера 14 в единичное состояние, сообщая абоненту о наличии для него в блоке 6 памяти принятого сообщения. На этом процедура приема кадра информации из кольцевой сети заканчивается.

В режиме передачи информации в кольцевую сеть (фиг.11) перед началом работы в этом режиме выход 17 регистра 16 команд (фиг.Г1 а) и выход 170 регистра 16 (фиг.11 б) должны быть установлены в состояние логической единицы с целью обеспечения работы устройства в составе кольцевой сети в режиме передачи данных от абонен- д та. Затем абонент записьшает информацию, предназначенную для передачи, в блок 6 буферной памяти и устанавливает выход 172 регистра 16 команд в состояние логической единицы

(фиг.Пв).

После этого блок 5 дешифраторов анализирует циркулирующую информацию на предмет наличия управляющей комбинации маркера (фиг.11 г). При обнаружении такой комбинации на выходе 125 блока 5 появляется импульс (фиг.Ид), устанавливающий выход 210 триггера 26 в состояние логической единицы (фиг.lie). Этим разрешается

работа блока 20 добавления бит-стаф-т финга (фиг.Пж) и регистра 18 управляющих символов, формирующих управляющие символы в передаваемой иа вход 103 передатчика 2 (фиг.Пв) последовательности, а также устанавливается в единицу выход 213 триггера 27 (фиг.11 и). В момент установки триггера 27 потенциал с его выхода 210 поступает на вход 200 элемента И 23 и запрещает прохождение через него . информации на вход 191 второго элемента ИЛИ 21. Импульс с выхода 125 . блока 5 дешифратора проходит также через элемента И 25 на зход 193 элемента ИЛИ 21. Это приводит к замене в управляющей комбинации маркера последней единицы на нуль, что эквивалентно замене управляющего символа Маркер на Флаг открьшающий (фиг. Из).

Сигналом с выхода 213 триггера 27 (фиг. Пи) производится запуск вибратора 31 по входу 223. В результате чего на выходе 225 одновибрато- ра 31 вырабатывается импульс (фиг.Пк). Этим импульсом производится чтение информации из блока 6 памяти с последующим переключением в нем счетчика 60 адреса и запись считанного байта в регистр 17 передачи. После этого поступающие с блока 20 до-Л бавления бит-стаффинга тактовые импульсы (фиг.Пж) производят сдвиг информации в регистре 17 передачи, осуществляя параллельно-последовательное преобразование. Сдвиг осуществляется так, что при необходимости в передаваемую информацию добавляется бит-стаффинг.

После отсчета восы-ш переданных бит счетчиком 15 на его ввкоде 167 появляется импульс (фиг.Пл), которьй поступает на вход 22Д одновибратора 31. В результате на выходе одновибратора вырабатывается очередной импульс (фиг.Пк), по которому произ-. водится чтение очередного байта информации из блока 6 памяти и запись ее в регистр 17 передачи. Затем путем подачи сдвигающих импульсов на вход Л 73 регистра 17 осуществляется параллельно последовательное преобразование и передача в линию связи через вход 104 передатчика 2 (фиг. Из) следующего байта данных.

Описанные процессы повторяются до полной передачи всего массива из буферной памяти блока 6 в линию свя- . зи. После завершения передачи всего массива содер 1а мое счетчика 60 адреса памяти уменьшается до нуля, что фиксируется дешифратором 59 блока 6.

5

0

5

0

5

0

5

0

5

В результате на выходе 136 блока 6 устанавливается нулевой потенциал (фиг.I1м), по которому происходит переключение выхода 213 триггера 27 в нулевое состояние (фиг.11 и), при этом запрещается работа регистра 17 передачи и формирователя импульсов и разрешается переключение триггеров 30 и 28 (фиг.11н,о).

Далее под действием сдвиговых импульсов, поступающих на вход 183 блока контроля передачи, происходит выдача контрольной последовательности кадра (фиг.Пз). После передачи перт-- вых восьми бит контрольной последовательности счетчик 15 на выходе 167 формирует сигнал (фиг.Пл)., который переключает счетный триггер 30 (фиг.Пн). Далее блок контроля передачи выдает на передатчик 2 второй байт контрольной последовательности, после чего импульс с выхода второго счетчика 15 (фиг.Пл) производит повторное переключение триггера 30. По фронту этого переключения сбрасывается триггер 28 (фиг.11 о),запрещая работу блока 19 контроля и устанавливается седьмой триггер 29 (фиГоПп), разрешая сдвиг информации в регистре 18 управляющих символов. Под действием сдвигающих импульсов происходит -. их последовательная передача в линию связи. После каждых восьми бит счет- чик 15 производит переключение тригт гера 30 (фиг.11л,н). После выдачи символа Конец кадра (фиг.11 в) происходит повторное переключение триггера 30 (фиг.Пн), что приводит к переключению триггера 29 (фиг.Пп), которое запрещает работу регистра 18 управляющих символов и приводит к сбросу триггера 26 (фиг.lie) в исходное состояние. На этом процедура передачи кадра в кольцевую сеть заканчив ается.

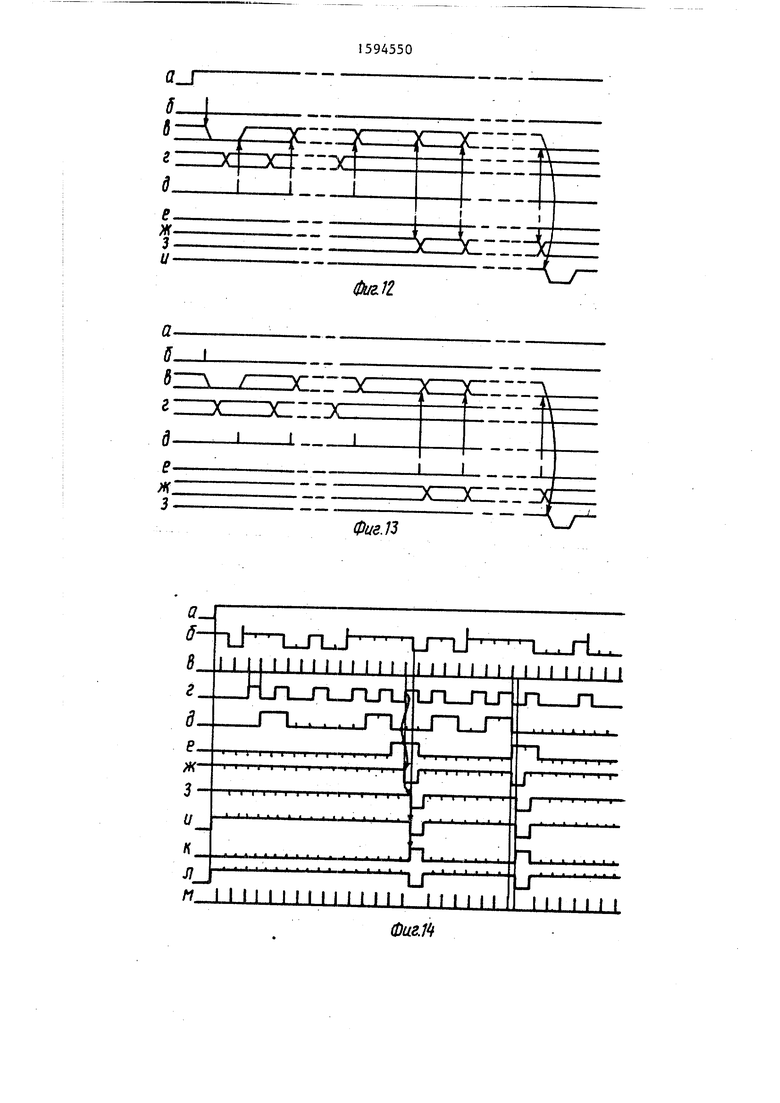

Временная диаграмма работы блока 6 памяти при передаче информации в линию связи приведена на фиг.12. Временная диаграмма работы блока 6 памяти при приеме информации из линии связи - на фиг.13.

В режиме передачи информации в лИ :-. кию связи на входе 134 блока 6 памяти (фиг.5) должен быть установлен абонентом уровень логической единицы (фиг.12а) - дпя задания соответствующего направления передачи .информации в блоке 6 памяти. И этот уровень должен удерживаться на все время передачи. Перед началом работы на один из входов 130 абонентом подается импульс сброса, устанавливающий счетчик ;60 адреса памяти в исходное состояние (фиг.12б).Выходы счетчика 60 при ЗТ0М сбрасываются в куль (фиг,12в). После этого блок б памяти I готон к приему информации от абоиен- I та.

.I Данные от абонента поступают на ВХОДЫ 133 блока б и сопровождаются I стробом на входе 130 (фиг.12г,д). |По стробу происходит запись байта ;данных в накопитель 58 блока б и пе- |реключение.счетчика 60 адреса. Затем :абонент устанавливает на входы 133 ;следующий байт данных и сопровождает ;его стробом ка входе 130 (фиг.12г,д). IДалее эта процедура повторяется и ;продолжается до тех пор, пока абонент не запишет в блок 6 весь необходимый :ДГ1Я передачи массив данных. После : этого абонент дает устройству команду на передачу записанного массива в кольцевую систему путем установки в состояние логической единицы выхо- |да 172 регистра 16 команд (фиг.Пв). Получив команду. Устройство осуществляет режим передачи как показано на фиг.П. Причем выходные импульсы формирователя 36 (фиг.И к) посту-, пают на вход 132 блока 6 памяти (фиг.12е) и является стробами чтения информации из блока 6. По зтим стробам осуществляется вьщача информации с вьпсодов 135 блока 6 (фиг. 1 За) и записи ее в регистр 17 передачи. По

ключение счетчика 60 адреса памяти в обратном направлении после каждого считанного и переданного в линию связи байта (фиг.12в). После завершения передачи всего массива даинызс выходы счетчика 60 устанавливаются в нулевое состояние (фиг.12в), что определяется дешифратором 59, который на своем выходе 136 формирует сигнал (фиг.12и) сбрасьшающий триггер 27 в нулевое состояние и тем самым запрещает работу формирователя 36. На этом цикл передачи кадра информации через блок б в линию связи заканчивается

10

15

На входе 134 блока 6 устанавли- ; вается уровень логического нуля, который должен сохраняться в течение всего времени работы устройства в режиме приема (фиг.1 За). Счетчик 60 перед началом работы должен быть установлен в нулевое состояние, если он в нем не находится, сигналом на входе 130 блока 6 (фиг.136). После сброса счетчика 60 в нуль (фиг.13в) блок б готов к приему информации из линии связи.

При поступлении из линии связи i .и байта информации в соответствии с диаграммой на фиг.10 данные устанавливаются на входах 127 блока б (фиг.1Зг) и сопровождаются стробом записи на входе 129 блока 6 (фиг.Пд). Этим стробом осуществляется запись информации в накопитель 58 и переключение счетчика 60 адреса памяти. За пись информации и переключение счетчика в прямом направлении происходя до тех пор, пока из линии связи не принят весь информащюнный кадр. О чем свидетельствует сигнал на выходе 164 триггера 14 (фиг.Юн), который поступает к абоненту.

Абонент, приняв сигнал о наличии для него в блоке 6 поступившегося согч общения, подачей сигналов строба чтения на вход 130 блока б (фиг.13е) j осуществляет считывание принятых в блок 6 байтов данных, которые посту- лают на вход 135 блока 6 (фиг.13ж). : Импульсы чтения осуществляют переключение счетчика 60 адреса в обратном .направлении после каждого очередного этим же импульсам происходит пере- до прочитанного байта. Это происходит

20

25

30

35

до тех пор, пока счетчик 60 не исчерпывается до нуля (фиг.Пв), т.е. пока не считан весь массив данных из блока 6. Нулевое состояние счетчика

45 определяется дешифратором 59 блока 6, который вьщает нулевой сигнал на выход 136 блока 6 (фиг.13з).Этот сигнал приводит к сбросу триггера 14, что извещает абонента о завершении

5Q цикла приема данных из кольцевой cei-.- ти. На этом работа блока б по приему из сети и передаче абоненту текущего информационного кадра заканчивается. Временная диаграмма работы блока

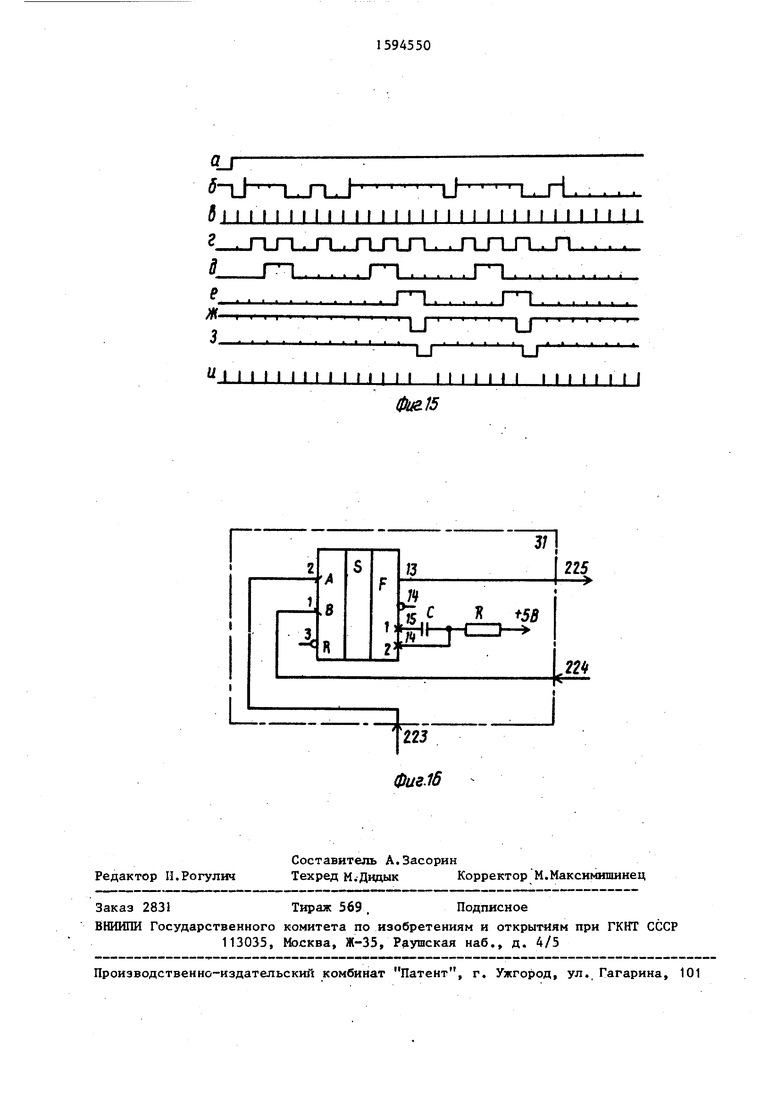

55 8 удаления бит-стаффинга показана на фиг.14, а сам блок 8 приведен на

В режиме приема информации нз линии связи блок 6 памяти работает следующим образом.

Абонент, приняв сигнал о наличии для него в блоке 6 поступившегося согч общения, подачей сигналов строба чтения на вход 130 блока б (фиг.13е) j осуществляет считывание принятых в блок 6 байтов данных, которые посту- лают на вход 135 блока 6 (фиг.13ж). : Импульсы чтения осуществляют переключение счетчика 60 адреса в обратном .направлении после каждого очередного до прочитанного байта. Это происходит

до тех пор, пока счетчик 60 не исчерпывается до нуля (фиг.Пв), т.е. пока не считан весь массив данных из блока 6. Нулевое состояние счетчика

45 определяется дешифратором 59 блока 6, который вьщает нулевой сигнал на выход 136 блока 6 (фиг.13з).Этот сигнал приводит к сбросу триггера 14, что извещает абонента о завершении

Q цикла приема данных из кольцевой cei-.- ти. На этом работа блока б по приему из сети и передаче абоненту текущего информационного кадра заканчивается. Временная диаграмма работы блока

5 8 удаления бит-стаффинга показана на фиг.14, а сам блок 8 приведен на

|ФИГ . б .

Блок удаления бит-стаффинга работает следующим образом. В исходном

состоянии на вход 142 блока 8 посту- пает нулевой потенциал (фиг.14а), блокирующий элементы И 7 и 72. Этот же потенциал, пройдя через элемент ИЛИ-НЕ 75, поступает на вход сброса счетчика 66 и удерживает его выходы в нулевом состоянии. На вход 140 блока 8 поступает информация в последовательном коде с выхода 102 приемника 1 (фиг.146), которая сопровождается тактовыми импульсами на входе 1Л1 (фиг.14в).

Работа блока 8 разрешается при переключении потенциала .на входе 142 блока в единичное состояние (фиг.14а), после чего счетчик 66 переключается по каждому импульсу на входе 141 (фиг.14в) при условии, что на вход 140 блока поступают единичные информационные биты. Единичные информационные биты увеличивают содержимое счетчика 66 на единицу,.так как на элементе И 69 происходит совпадение единичных уровней входник сигналов с тактовыми импульсами на входе 141 . При этом любой нулевой бит входной информации, пройдя через элемент НЕ 74 на элемент И-НЕ 70 и после совпадения на нем с тактовым импульсом, поступает через элемент ИЛИ 75 на вхо сброса счетчика 66 и устанавливает его выходы в состояние логического нуля. Таким образом, счетчик отсчитывает только подряд идущие единицы во входной информации и сбрасьшается при появлении любого нулевого информационного бита во входной последовательности единиц. На фиг.14г, д, е показаны разрядные выходы счетчика 66.

Состояние выходов счетчика 66 постоянно анализируется дешифратором 67 и в случае отсчета пяти подряд идущих единиц на его выходе появляется нулевой уровень (фиг.14ж), который поступает на информационный вход триггера 68 и стробируется по его управляющему входу ближайшим тактовым импульсом с входа 141. В результате чего прямой выход триггера 68 переключается в нулевое состояние (фиг.14з), тем самым запрещая прохождение тактовых импульсов через элемент И 73, так как с него снимается разрешающий потенциал, поступавший ранее с выхода И 71 (фиг.14и) через элемент ИЛИ 76. Прохождение тактового импульса через элемент И 73 может быть в этом случае разрешено, если

0

5

0

5

0

5

0

5

0

5

следующий принимаемый информационный бит на входе 140 равен единице. Однако, если он равен нулю, как показано на фиг.14б, то нулевой потенциал пог- ступает на вход элемента И 72 я через его выход (фиг.14 к) и элемент ИЛИ 76 (фиг.14л) проходит на вход элемента И 73, запрещая прохождение тактового импульса на его выход (фиг.14м).

В результате работы блока 8 удаление бит-стаффинга на тактовый последовательности удаляются импульсы, ко-. торые следуют после пяти единичных подряд информационных бит. Так как этими импульсами с выхода блока удаления бит-стаффинга осуществляется сдвиг информации в приемных регист- .рах блока 4, то отсутствие этих импульсов в такие моменты приводит, к тому, что информация в этих регистрах не сдвигается и нулевые биты, представляющие собой бит-стаффинг, в регистры не заносятся, т.е. бит-стаф- финг удаляется

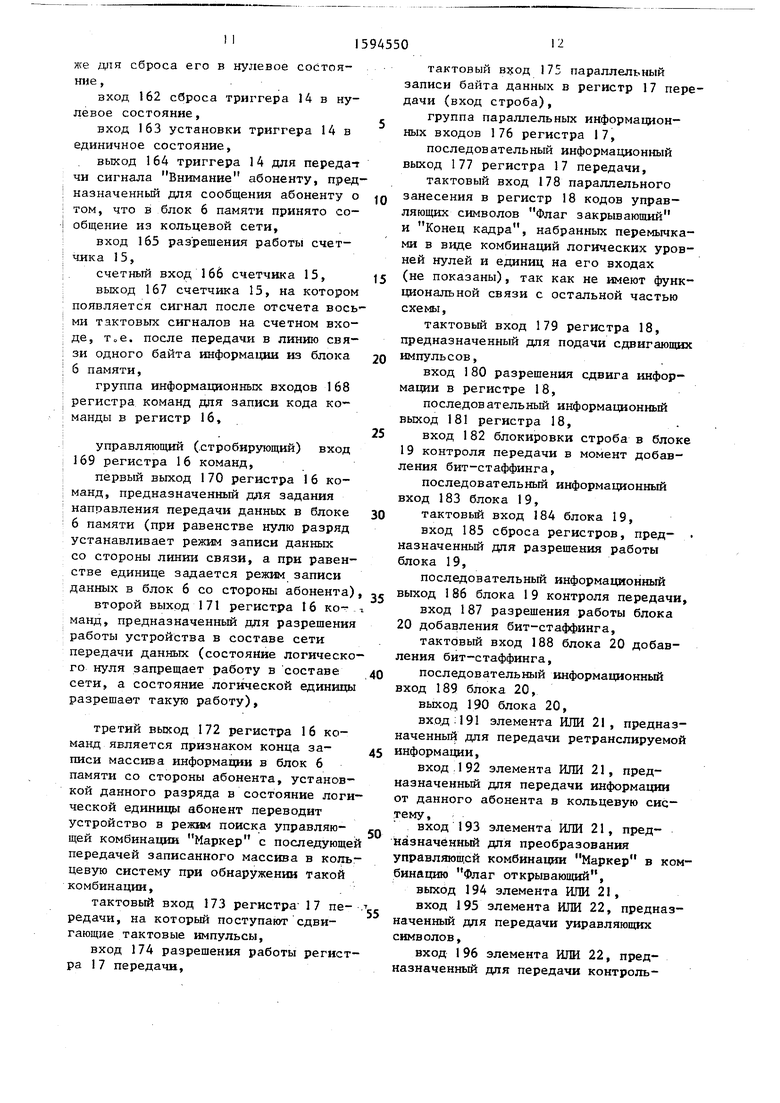

Блок 20 добавления бит-стаффинга решает обратную задачу: он добавляет в передаваемую информацию, не являют- щуюся управляющей, нули после каждых следующих подряд пяти единиц. При этом снимаются ограничения на кодировку передаваемой информации, которая может быть любой, а управляющие символы легко дешифрируются на приемном конце, так как отличаются от любой другой передаваемой информации тем, что имеют в Своем составе больше пяти единиц подряд.

Временная диаграмма работы блока 20 добавления бит-стаффинга приведе- на на фиг.15. Блок 20 добавления бит- стаффинга работает следующим образом. В исходном состоянии .переключение счетчика 88 запрещается нулевым потенциалом с входа 187 блока 20 (фиг.15а). На вход 189 блока 20 пот- ступает. предназначенная для передачи информация (фиг.156), а на вход 188 - тактовые импульсы передачи (фиг.15в) с выхода 106 блока 3 синхронизации.

При поступлении единичного разрешающего потенциала на вход 187 (фиг.15а) счетчик 88 получает возможность отсчитывать подряд вдущие единицы во входной информации, выдавая результат счета на свои кодовые выходы (фиг.,е). Если среди под-: ряд идущих информационных бит ветре23

594550

чается ноль, происходит сброс счетчика в исходное состояние и отсчет начинается заново. Так происходит до тех пор, .пока счетчик не насчитает до пяти подряд идущих единичных бит.Эта комбинация выходов счетчика обнаруживается дешифратором 89, который на Своем выходе вьвдает нулевой потенциал (;фиг.15ж). Ближайшим фронтом тактово- ij-o импульса триггер 90 устанавливает- 4я в нулевое состояние и блокирует Прохождение очередного тактового им- г ульса через элемент И 93. В резуль- из выходной последовательности 1 сключаются импульсы, идущие после йяти, следующих подряд, информационных бит (фиг,15и). Этим достигается toT же эффект, что и при работе блока 8 удаления бит-стаффинга. Однако, 4сли в первом случае, удаленные импуль- йы не приводят к сдвигу информации 5 приемных регистрах и этим достигается то, что в них не заносятся при- йимаемые нули бит-стаффинга, то в данном случае отсутствие сдвигающе- импульса на тактовом входе 173 1 егистра 1 7 передачи приводит к то- иу, что вместо отсутствующего очередного бита с регистра 17 на его место йставляется нулевой бит через элемент И 24, а остальные биты с регистра 17 переданы после вставки бит- стаффинга.

Одновибратор 31 (фиг.16) представляет собой обычный Одновибратор со сбросом и повторным запуском, реализованный на базе микросхемы К 155 АГЗ. Вход сброса не используется, а оба входа запуска (прямой и ин- версньй) используются по прямому своему назначению.

Формул а

24 зоб

р. е т е н и я

10

30

. 1.Устройство для сопряжения между абонентами с линией связи, содержащее приемник, передатчик, блок синхронизации, блок регистров, блок.дешифраторов, блок памяти, первый счетчик, блок удаления бит-стаффинга, блок контроля приема, первый элемент Д, первый элемент ИЛИ, первый, второй и третий триггеры, причем вход приемника является линейным входом устройства, а выход соединен с информацион 5 ными входами блока удаления бит-стаффинга, блока регистров и входом записи режима блока синхронизации, первый выход которого соединен с тактовым .входом передатчика, выход которого

20 является линейным выходом устройства, второй выход блока синхронизации соединен с входом стробирования записи блока памяти, первым разрешающим входом блока дешифраторов, так25 товым входом блока контроля приема, первым синхровходом блока регистров и синхровходом блока удаления бит- стаффинга, вход разрешения работы которого подключен к входу разрешения счета первого счетчика, R-входу первого триггера и выходу второго триггера, а выход блока удаления бит- стаффинга соединен с тактовым входом первого счетчика, входом блокировки строба блока контроля приема и с вторым тактовым синхровходом блока регистров , первьш выход которого подключен:, к первому входу первого элемента ИЛИ, второй, третий и четвертый выходы подключены соответственно к первому, второму и третьему информационным входам &лока дешифраторов, третий информационный вход которого соединен с первым входом данных блоПо входу 223 Одновибратор срабаты- дс памяти, пятый выход блока регистров соединен с последовательным информационным входом блока контроля приема, выход которого соединен с первым входом первого элемента И, а вход сброса подключен к выходу первого триггера, второму входу первого элемента И, и входу начальной установки блока памяти, первый вход записи которого соединен с первым выходом первого счетчика, вход чтения и второй вход записи блока памяти являются абонент входами и записи устройства, первый выход блока памяти является абонентским выходом данных

35

40

вает однократно, в момент установки в единичное состояние выхода 213 триггера 27. Это прямой вход одновибрато- ра, который в процессе дальнейшей работы иcпoJXЬзyeтcя как разрешающий до тех пор, пока на нем присутствует потенциал с выхода 213 триггера 27.

По входу 224 Одновибратор срабатывает во всех остальных случаях, т .ё. по всем запускающим импульсам с выхода 167 счетчика 15, через инверсный вход, по которому запуск одновибрато- ра происходит отрицательШ)1м фронтом импульса счетчика 15.

50

55

ормул а

24 зоб

р. е т е н и я

10

15

20

25

251594550

устройства, а второй выход подключен к R-входу третьего триггера, выход которого является абонентским выходом запроса на прием устройства, S-вход третьего триггера соединен с вторым входом первого элемента ШШ и выходом первого элемента И, третий вход которого подключен к первому выходу бло ка дешифраторов, второй выход которо- го соединен с S-входом первого триг-. гера, а третий и четвертый выходы блока дешифраторов подключены соответственно к S- и R-входам второго триггера, причем второй .вход данных блока памяти является абонентским входом данных устройства, отличающееся тем, что, с целью расширения функциональных возможностей устройства за счет обеспечения двустороннего обмена данными между любыми абонентами кольцевой системы в соответствии с принятым протоколом обмена, в него введены второй счет-, чику регистр команд, регистр передачи, регистр управляющих символов, блок контроля передачи, блок добавления бит-стаффиига, второй и третий элементы ИЛИ, второй, третий и четвертый элементы И, четвертый, пятый и шестой, седьмой и восьмой триггеры и одновибратор, причем первый вход второго элемента И соединен с выходом первого элемента ИЛИ, а второй вход - с выходом четвертого триггера,. S-входом пятого триггера, с входом разрешения счета второго счетчика, входом записи регистра управляющих С1е4волов и входом разрешения работы блока добавления бит-стаффинга, а выход второго элем.ента И подключен к первому входу второго элемента ИЛИ, выход которого соединен с информационным входом передатчика, а второй вход подключен к входу третьего эле-- мента И, первый вход которого соеди--.. ней с тактовыми входами второго счетчика регистра управляющих символов, егистра передачи - с в;1содом блокиовки строба блока контроля передаи и с выходом блока добавления биттаффинга, тактовый вход которого соеинен с первым выходом блока синхроизации, входом синхронизации записи лока памяти и тактовым входом блока онтроля передачи, информационный лок.добавления бит-стаффинга,подклюен к .второму входу третьего элемента и выходу третьего элемента ИЛИ, пер30

35

40

45

в в ш т к д л с д г тр то си до до по ка ре вх хо то тр ус вх ле да во ру не вт че де че ме к тр а до

50

55

ч ле и вы то пе эл ны вы ля ка пе

10

15

20

25

4550

30

35

0

5

26

вый вход которого соединен с выходами регистра управляющих символов, второй вход - с выходом блока контроля передачи, а третий вход -с выходом регистра передачи и информационным входом блока контроля передачи, вход сброса которого соединен с выходом шестого триггера и R-входом седьмого триггера, выход которого подключен к R-входу четвертого триггера и входу разрешения сдвига регистра управляющих символов, а S-вход соединен с выходом восьмого триггера и R-входом шестого триггера, S-вход которого подключен к выходу пятого триггера, входу разрешения работы пятого триггера, к первому входу одновибра- тора и D-входу восьмого триггера, синхровход которого соединен с выходом второго счетчика и с вторым входом одновибратора, выход которого подключен к входу строба чтения блока памяти и к входу строба записи, регистра передачи, информационный вход которого соединен с первым выходом блока памяти, второй выход которого подключен к R-входу пятого триггера, абонентский вход .данных устройства соединен с информационным входом регистра команд, а вход управления направлением записи и чтения данных блока памяти подключен к первому выходу регистра команд, строби- рующий вход которого соединен с абонентским входом чтения устройства, второй выход регистра команд подклю-- чен к второму входу разрешения блока дешифраторов, а третий вькод подключен к первому входу четвертого элемента И, выход которого подключен к S-входу четвертого триггера и третьему входу второго элемента ИЛИ, а второй вход соединен с пятым выходом блока дешифраторов.

0

5

2.Устройство по п.1, отличающееся тем, что блок добавления бит-стаффинга содержит первый и второй элементы И, элемент НЕ, первый элемент И-НЕ, счетчик, дешифратор и триггер, причем первый вход первого элемента И соединен с входом элемента НЕ и является последовательным информационным входом блока, первый вход первого элемента И-НЕ является входом разрешения работы блот ка, синхровход триггера соединен с первым входом второго элемента И,

и первым входом второго элемента И-НЕ и с вторым входом первого элемента И и является тактовьм входом блока, йыход которого соединен с выходом второго элемента И, второй вход,.кото- рого соединен с выходом триггера 1)-вход которого соединен с выходом дешифратора, информационные,входы ко-торого соединены с параллельными входами счетчика, -тактовый вход которого соединен с выходом первого элемента И, а вход сброса - с выходом первого элемента И-НЕ, второй вход которого соединен с выходом второго элемента И-НЕ, второй вход которог:о соединен с входом элемента НЕ.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для сопряжения между абонентами | 1987 |

|

SU1411759A1 |

| Устройство для сопряжения ЭВМ с абонентом | 1990 |

|

SU1702380A1 |

| УСТРОЙСТВО УПРАВЛЕНИЯ СОПРЯЖЕНИЕМ АБОНЕНТОВ | 1993 |

|

RU2037196C1 |

| Устройство для отображения информации | 1986 |

|

SU1441450A1 |

| УСТРОЙСТВО ПРИЕМА И ОБРАБОТКИ ИНФОРМАЦИИ | 2002 |

|

RU2213424C1 |

| УСТРОЙСТВО ДЛЯ СОПРЯЖЕНИЯ АБОНЕНТОВ С ЦВМ | 1991 |

|

RU2018942C1 |

| МОДУЛЬ УПЛОТНЕНИЯ РЕЧЕВЫХ СООБЩЕНИЙ ПАКЕТАМИ ДАННЫХ | 1995 |

|

RU2103825C1 |

| Устройство для обмена данными между электронно-вычислительной машиной и абонентами | 1985 |

|

SU1277125A1 |

| Устройство для отображения графической информации на экране телевизионного индикатора | 1987 |

|

SU1439672A1 |

| Устройство для отображения информации на экране телевизионного индикатора | 1985 |

|

SU1437907A1 |

Изобретение относится к вычислительной технике, в частности к устройствам для сопряжения между абонентами в системе кольцевой структуры, и может быть использовано для приема и передачи информации в системах, использующих для обмена бит-ориентированные протоколы синхронной связи. Цель изобретения - расширение функциональных возможностей за счет обеспечения двухстороннего обмена данными между любыми абонентами кольцевой системы. Устройство содержит приемник, передатчик, блок синхронизации, блок регистров, блок дешифраторов, блок памяти, два счетчика, блок удаления бит-стаффинга, блок контроля приема, четыре элемента И, три элемента ИЛИ, восемь триггеров, регистр команд, регистр передачи, регистр управляющих символов, блок контроля передачи, блок добавления бит-стаффинга, одновибратор. 1 з.п.ф-лы, 16 ил.

96

97,

и.

Фиг.З

Г

47

8

55

57

51

9

50

t

5J

г/гЧ

Фиг.6

п

95

-9

91

787

Фиг.9

30

1

89

71 rtc

t

..Е

188

aS Jж

j

аг 6Г

б-Г г

(

ж

(/ К

Л. МЛ.

Фиг. 70

о о

. Фие.11

Й

1 e,

Ж- 3uJCIII

ФигЛг

Фие.1

I M M t

Фи.г.11

ojT

-п . п . h

Д I Mi м I I I I И I I И Г I I I ММ м м I м I

ж- 3,

i I 1 I и и I и и иi I 1 м I м м м г I

Фиа/5

Т.Н.:...

LT

| Двухканальное устройство сопряжения | 1981 |

|

SU993238A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для сопряжения между абонентами | 1987 |

|

SU1411759A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1990-09-23—Публикация

1988-06-20—Подача