(S) УСТРОЙСТВО для КОНТРОЛЯ и ДИАГНОСТИКИ

1

Изобретение относится к вычислительной технике и предназначено для тестового контроля и диагностики логических блоков, узлов, приборов.

Известно устройство для испытания логических блоков, содержащее генератор тактов, генератор случайных кодов, эталонный и логический блоки, блоки сравнения и управления, дешифратор, сумматор по модулю два, коммутатор т 3Однако для проверки логического блока в этом устройстве необходимо иметь такой же, но эталонный (т. е. заведомо исправный) логический блок, который не всегда имеется в наличии. Кроме того, проверка блоков производится случайными кодами, что снижает полноту контроля и увеличивает время проверки блоков.

Известно также устройство для контроля логических блоков, содержащее проверяемый логический блок, коммутатор, блок усилителей и нормализаЛОГИЧЕСКИХ УЗЛОВ

торов, магистральную шину, временной и амплитудный дискриминаторы, блоки ввода-вывода, ввода и печати, пульт управления, блоки проверки стандартных ячеек, состоящие из блоков уставок, компараторов, блоков управления уставками, регистрации и управления, схему ИЛИ, генератор тестов 23Недостатком этого устройства является то, что генератор тестов переби10рает все возможные комбинации входных сигналов. Это приводит к избыточности теста и увеличивает время проверки блоков. Кроме того, устройство может проверять только отдельные

15 стандартные ячейки, для каждого типа которых в устройстве имеется отдельный блок проверки. Это ограничивает область применения устройства.

Наиболее близким по технической

20 сущности к предлагаемому является устройство для тестового контроля цифровых узлов цифровой вычислительной машины, содержащее блок памяти, предназначенный для хранения тестовой программы, блок ввода, через который передается информация из блока памяти в регисгр тестов или регистр управления, дешифраторы, управляющие рабо- j той переключателей, которые служат для подключения напряжений, вырабатываемых блоком опорных напряжений, к схемам сравнения, формирователи входных сигналов и индикаторы. Выходы фор-ю мирователеи входных сигналов соедине ны с входами-выходами контролируемого блока. Информация о тесте с блока памяти через блок ввода поступает в регистры, а затем в виде стимулирующих сигналов подается на контролируемый блок. Ответные реакции контролируемого блока сравненияС эталоннь1 значениями, записанными в регистрах, и результаты контроля отображаются на индикаторах, (загорается лампочка в том канале, где произошло несравне ответных сигналов с эталонными). Опе ратор отмечает какие индикаторы светятся и делает соответствующие выводы о возможной неисправности в контр лируемом блоке. Затем вводится очередной тест информации, и контроль продолжается З. Для того, чтобы формировать очередной тест стимулирующих сигналов, в известном устройстве необходимо пе редать из блока памяти количество разрядов информации, равное числу входов-выходов контролируемого блока. А так как устройство ввода (например, фотосчитывающие механизмы) передают информацию побайтно со скоростью не выше 2000 байт/с, то, например, для формирования ОДНОГО тест для контролируемого блока с 200 входами-выходами потребуется 12,5 мс и максимальная частота подачи стимулирующих сигналов 80 Гц. Кроме того, оператору необходимо время, чтобы оценить какие индикаторы в каждом кадре загораются. Следовательно, известное устройство не может, быть при менено для контроля блоков, на которые необходимо подавать стимулирующие сигналы с высокой частотой, например десятки и сотни килогерц. Недостатком известного устройства является также невозможность подачи на его входы циклических последовательностей сигналов, чтобы наблюдать ответные реакции контролируемого бло ка с целью диагностики, например, на экране осциллографа, так как в уст960824 ройстве нет блока, обеспечивающего циклическое формирование стимулирующих сигналов с достаточно высокой час тотой. Кроме того, с помощью известного устройства невозможно проводить диагностику до элемента в контролируемом блоке, так как оператор получает только информацию о том, на каких выходах получено несравнение ответных сигналов с эталонными. Все перечисленные недостатки снижают функциональные возможности известного устройства. Целью изобретения является увеличение точности локализации неисправностей. Поставленная цель достигается тем, что в устройство для контроля и диа|- ностики логических узлов, содержащее блок терминалов, блок ввода-вывода, три регистра, блок опорных напряжений, каналы по числу контактов проверяемого узла, каждый канал содержит дешифратор, переключатель, узел сравнения, формирователь импульса, причем выход блока терминалов соединен с первым входом блока ввода-вывода, первый выход которого соединен с входом блока терминов, второй вход блока ввода-вывода соединен с первым выходом первого регистра, второй выход блока ввода-вывода - с входом второго регистра и вторым входом первого регистра, выходы третьего регистра - соответственно с управляющими входами дешифраторов, выходы которых соединены соответственно с первыми входами переключателей, вторые входы которых соединены с выходом блока опорных напряжений, первые выходы переключателей соединены соответственно с первыми информационными входами узлов сравнения, вторые информационные входы которых соединены соответственно с выходными контактами проверяе 5ого узла, входные контакты которого соединены соответственно с выходами формирователей, входы которых соединены соответственно с вторыми выходами переключателей, введен элемент И-ИЛИ, регистр сдвига, блок управления, преобразователь импульсного сигнала в сигнатуру, два блока памяти, причем управляющий вход регистра сдзига соединен с первым выходом блока управления, второй выход которого соединен с управляющими входами узлов сравнения, первая группа выходов блока управления соединена с управляющими входами первого и второго блока памяти, выходы первого блока памяти соединены соответственно с информационными входами дешифраторов, выходы второго блока памяти с группой информационных входов ре-гистра сдвига,выходы которого соединены с входами третьего регистра и с инфор мационными входами первого блока памяти, информационный вход регистра сдвига соединен с выходом элемента И-ИЛИ, первый вход которого соединен с первым входом блока преобразования импульсного сигнала в сигнатуру и является входом устройства, второй вход элемента И-ИЛИ соединен с вторым выходом первого регистра, первый вход которого соединен с выходом регистра сдвига, второй вход первого регистра соединен с выходом блока преобразования кода импульсного сигнала в сигнатуру, выход второго регистра - с первым входом блока управления, третий выход которого соединен с вторым входом элемента И-ИЛИ, третий вход блока ввода-вывода - с второй группой выходов блока управления, третья груп па выходов которого соединена с вторым входом блока преобразования кода второй вход блока управления соединен с выходом второго регистра. Кроме того, блок управления содержит три узла сравнения, пять счетчиков, три коммутатора, два элемента ИЛИ, два дешифратора, узел памяти, три регистра, элемент И, два триггера элемент задержки, генератор импульсов, причем первый вход блока соединен с управляющим входом элемента задержки, с первым входом первого узла сравнения и с первым информационным -входом первого коммутатора, первый управляющий вход которого соединен с выходом первого узла сравнения, второй вход которого соединен с выходом первого счетчика, с информационным входом первого регистра, с первым входом второго узла сравнения, второй вход которого является первым информа ционным выходом первой группы выходо блока, второй вход которого соединен с вторым информационным входом перво го коммутатора и со счетным входом второго счетчика, выход которого сое динен свторым управляющим входом первого коммутатора, третий информационный вход которого соединен с выходом третьего счетчика, с первым вхо ДОМ первого дешифратора, с первым информационным входом второго коммутатора, с первым входом второго дешифратора, с информационным входом узла памяти, управляющий вход которого соединен с выходом первого элемента ИЛИ, первый вход которого соединен с первым информационным входом третьего коммутатора, с первым входом элемента И, с первым управляющим входом второго регистра, с выходом второго дешифратора, с информационным входом элемента задержки, выход которого является вторым выходом блока, первый выход которого соединен с выходом четвертого счетчика, управляющий вход которого соединен с установочным входом первого триггера, со счетным входом пятого счетчика, с управляющим входом третьего регистра, с управляющим входом первого регистра, со счетным входом первого счетчика, с установочным входом второго триггера, с выходом первого дешифратора, с вторым входом первого элемента ИЛИ, с вторым управляющим входом второго регистра и является первым выходом второй группы выходов блока, второй выход второй группы выходов блока соединен с выходом элемента И, второй вход которого соединен с первым выходом узла памяти, с первыминформационным входом второго регистра, с вторым информационным входом третьего коммутатора, выход которого соединен с первым управляющим входом третьего счетчика, второй управляющий вход которого соединен с выходом второго элемен та ИЛИ, первый вход которого соединен с вторым входом первого дешифратора и с первым выходом первого комкутатора, второй выход которого соединен с третьим входом первого элемента ИЛИ, выход пятого счетчика соединен с информационным входом третьего регистра, с первым входом третьего узла сравнения, с четвертым информационным входом первого коммутатора, третий управляющий вход которого соединен с вторым входом второго элемента ИЛИ и с первым выходом второго регистра, второй выход которого соединен с вторым информационным входом второго коммутатора, выход которого соединен с вторым входом второго дешифратора, второй информационный вход второго регистра соединен с вторым выходом узла памяти, с информационнъ1м входом третьего счетчика и является третьим

выходом второй группы выходов блока, третий выход которого соединен с выходом второго триггера, выход первого триггера является первым выходом третьей.группы выходов блока, второй выход третьей группы выходов которого соединен с синхровходом четвёртого счетчика, с выходом генератора импульсов, с синхровходом третьего счетчика, выход второго узла сравнения соединен с четвертым управляющим входом первого коммутатора, пятый управляющий вход которого соединен с выходом третьего узла сравнения, второй йход которого соединен с выходом третьего регистра, выход первого регистра соединен с вторым входом второго узла сравнения.

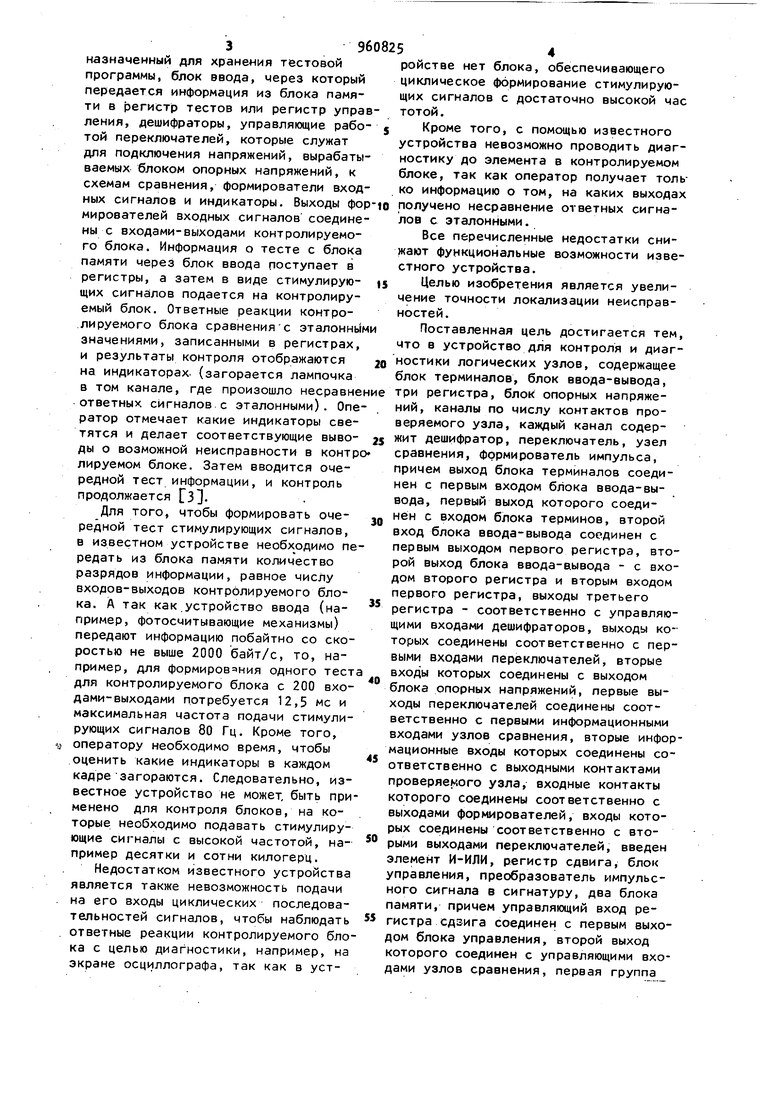

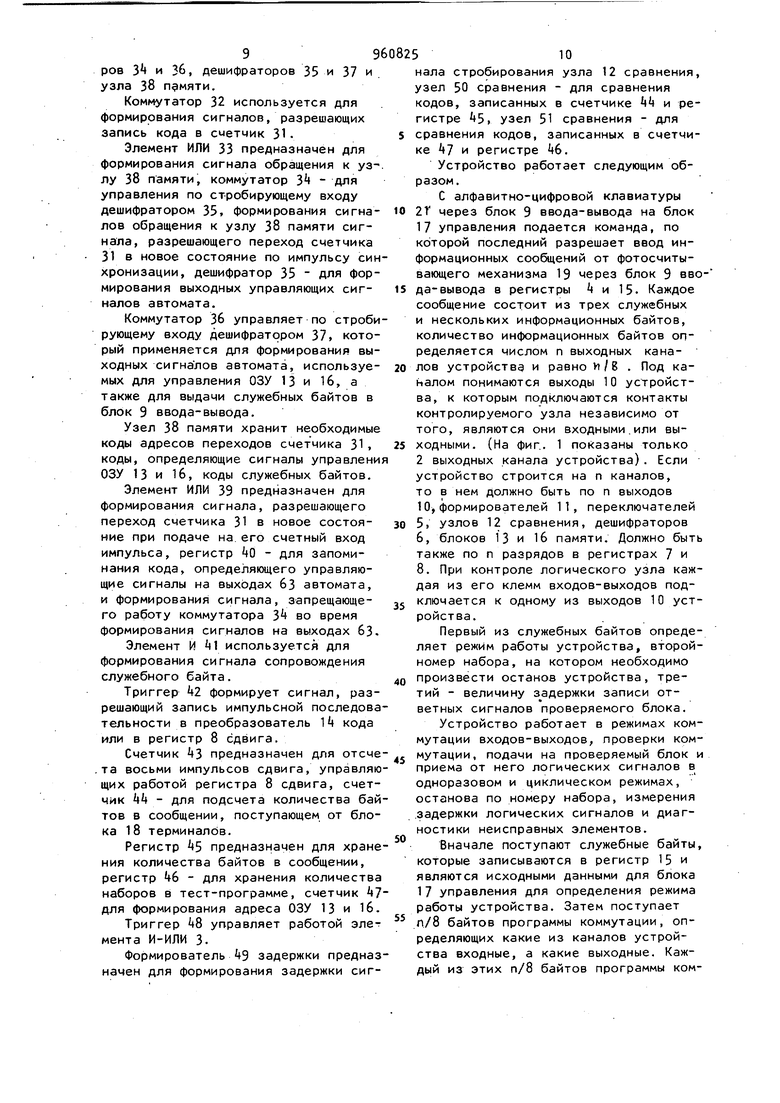

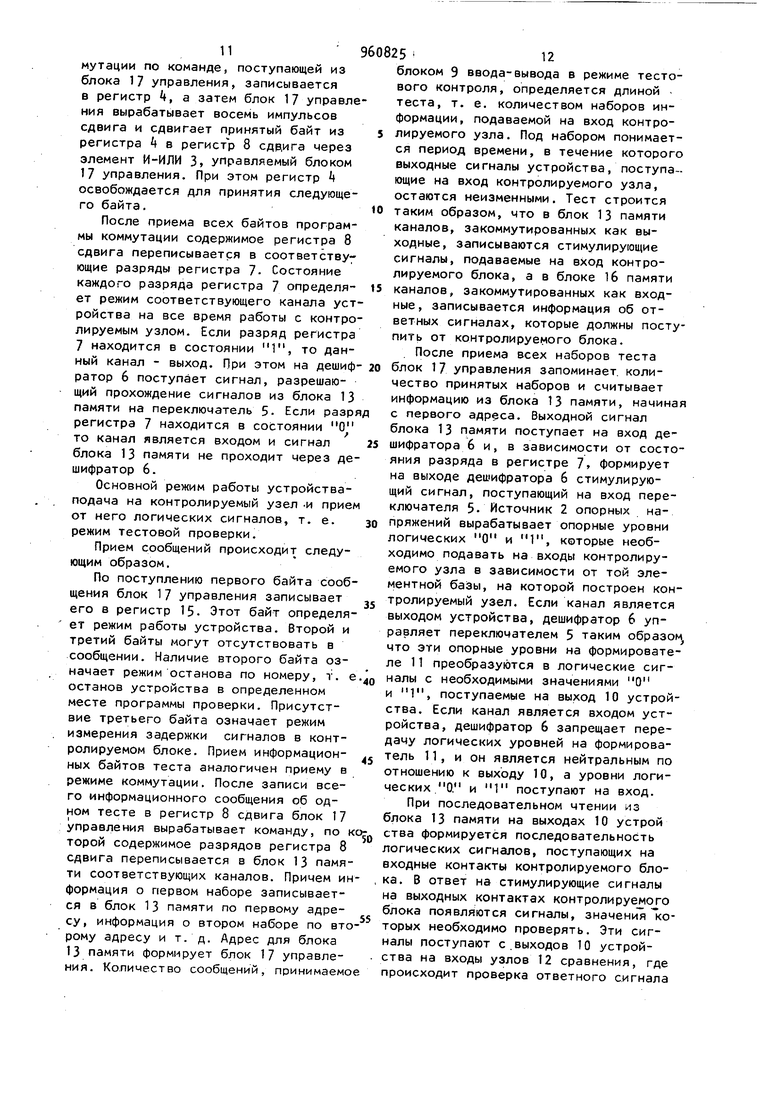

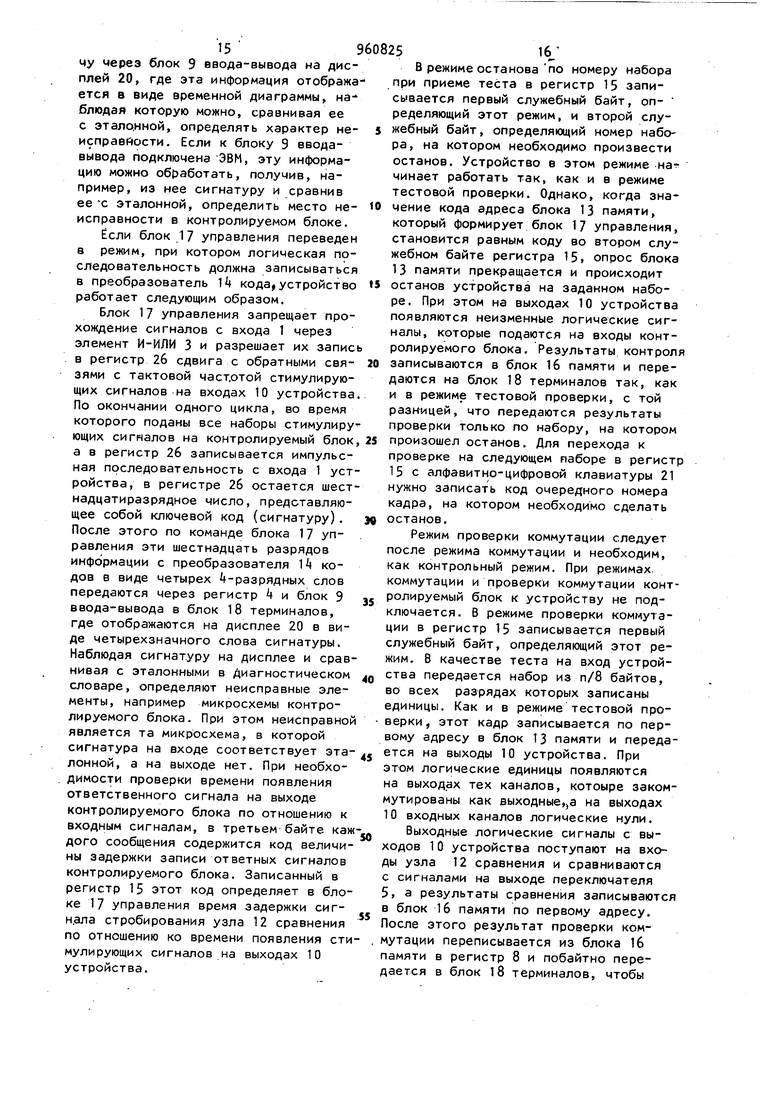

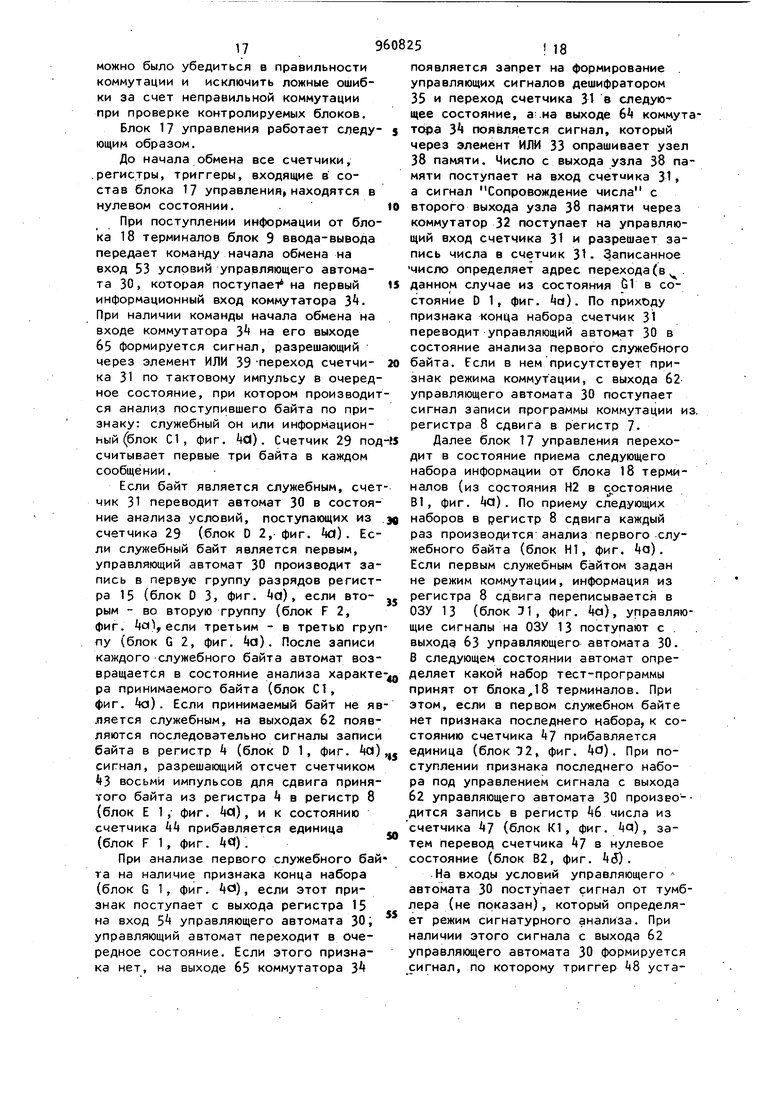

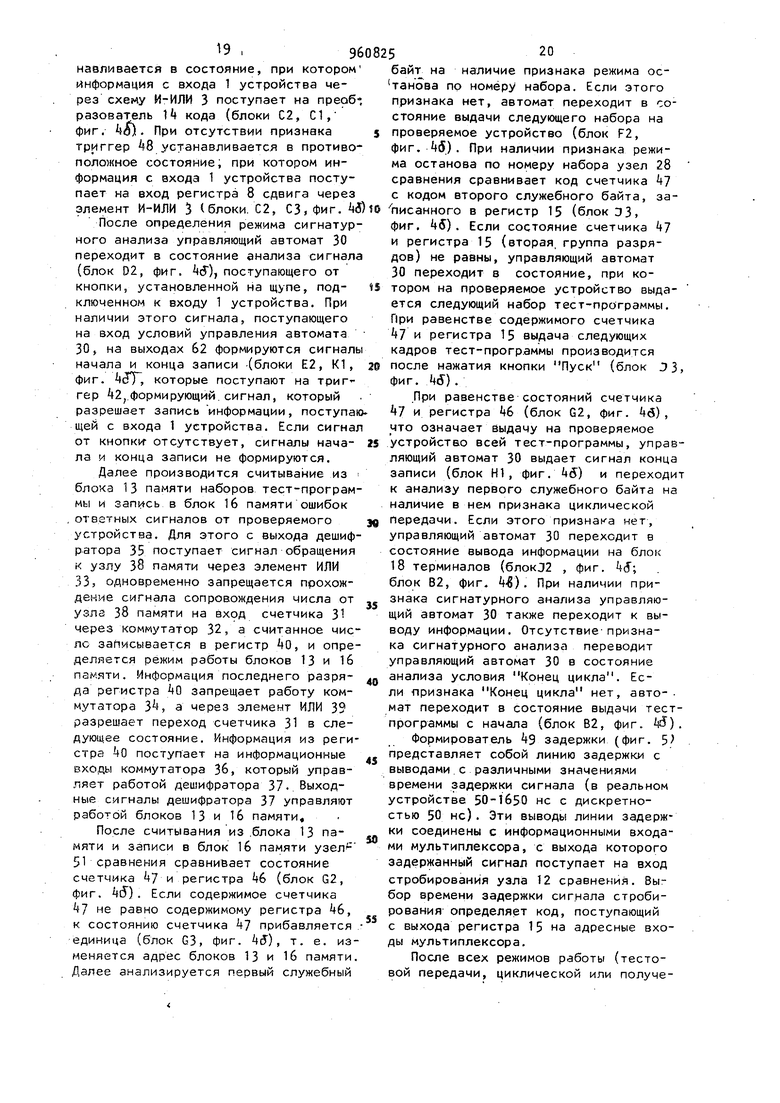

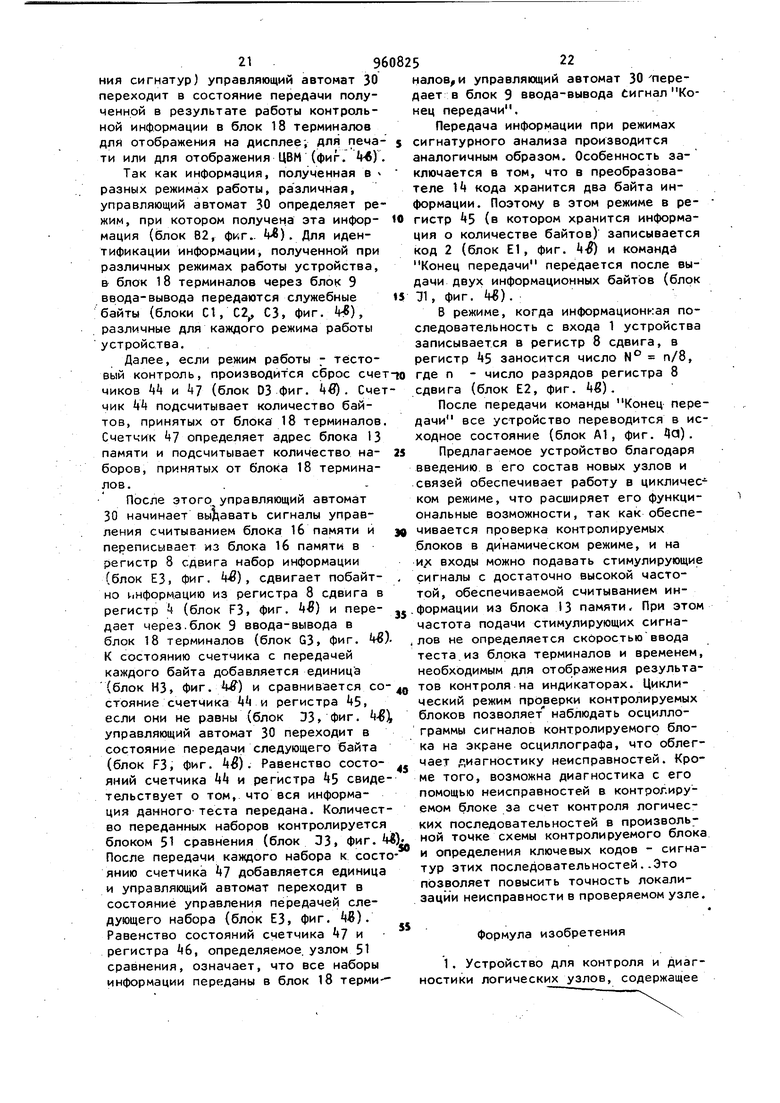

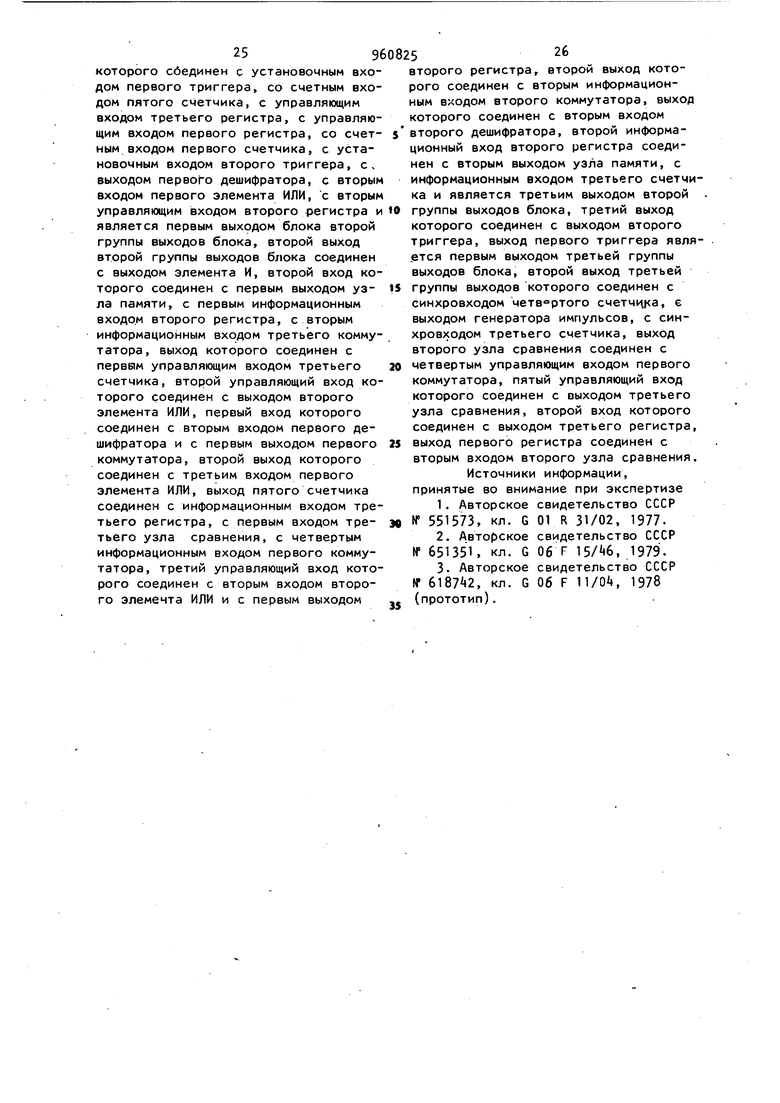

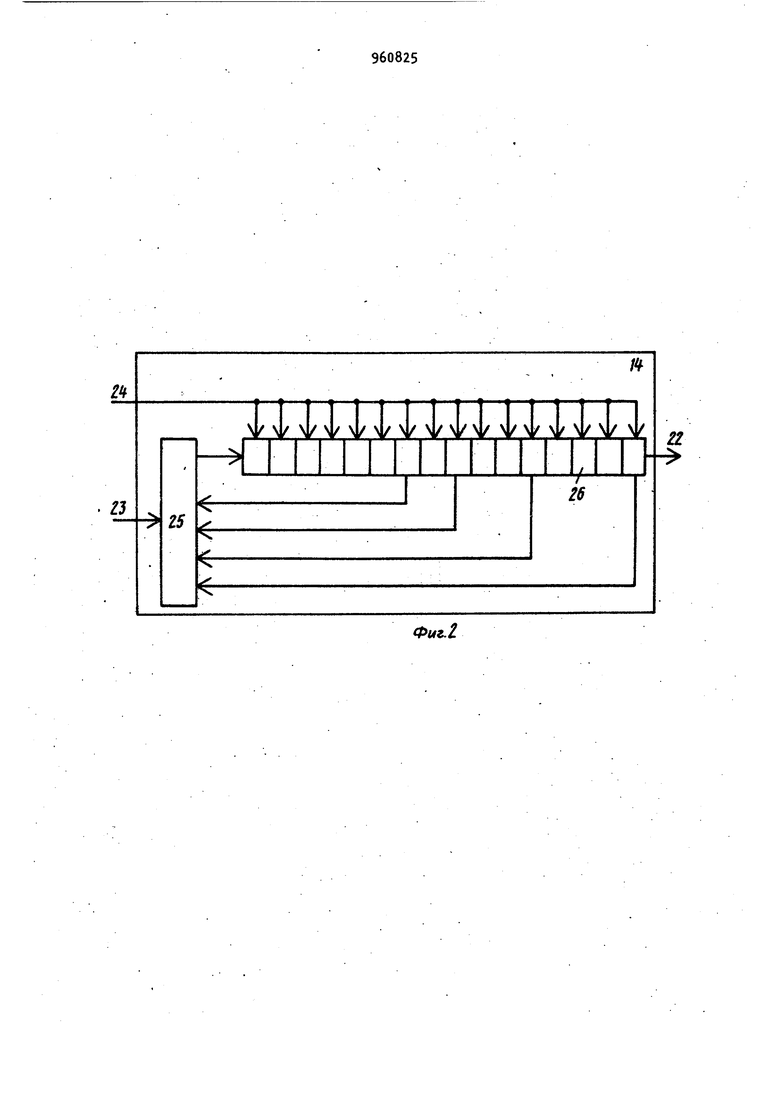

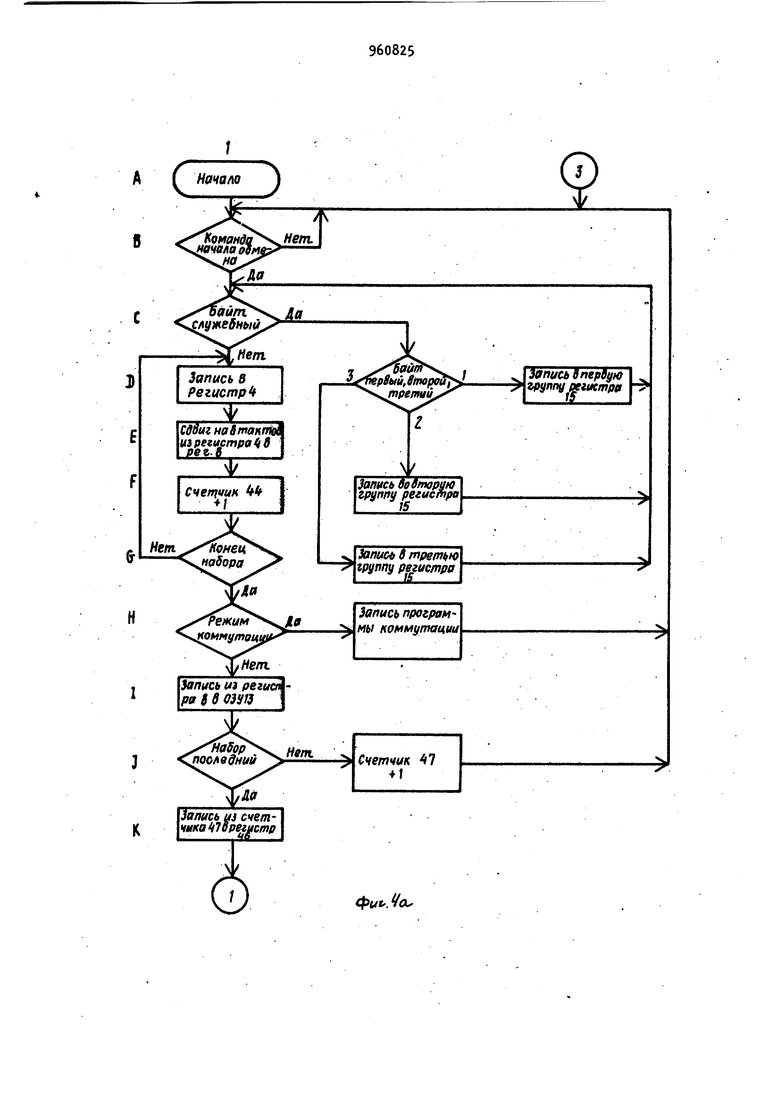

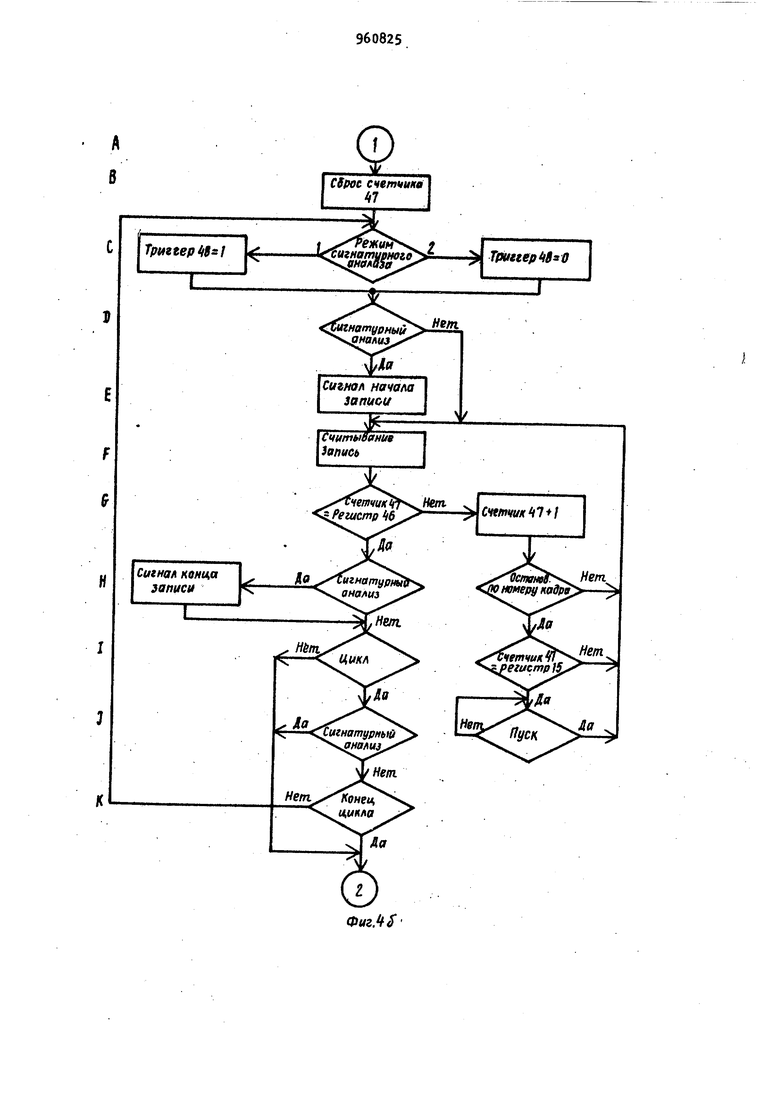

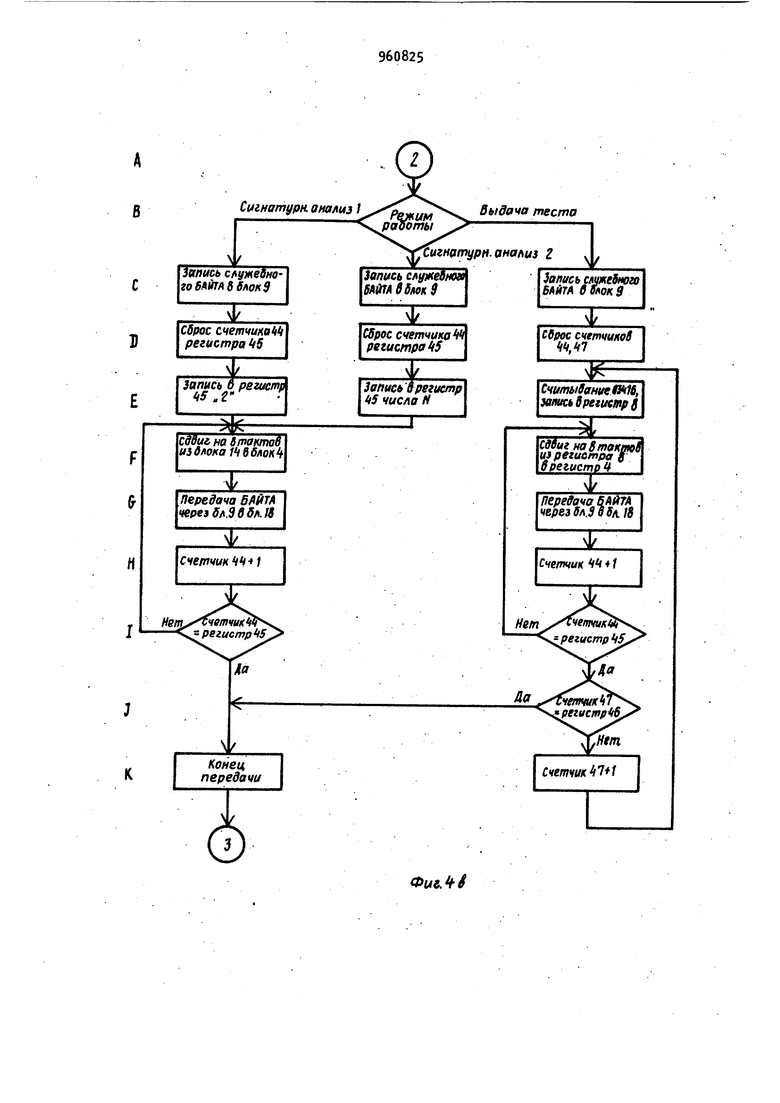

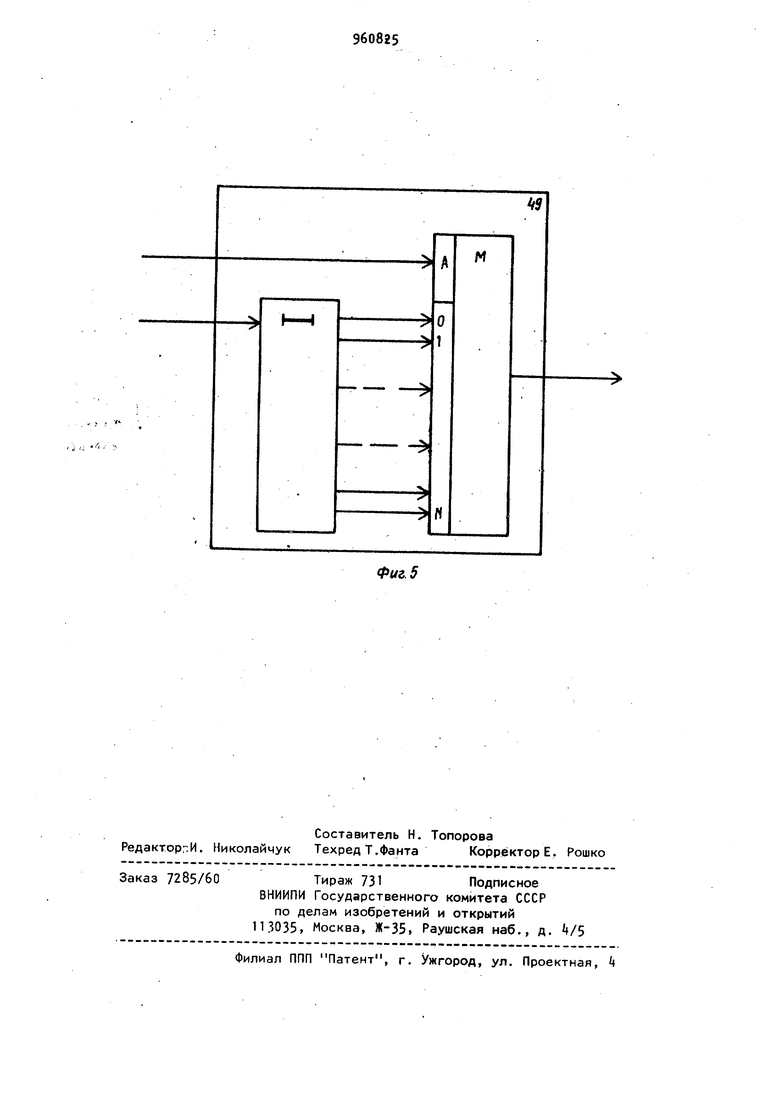

На фиг. 1 показана структурная схема предлагаемого устройства; на фиг. 2 - вариант построения преобразователя кода; на фиг. 3 блок управления; на фиг. а,б,в - блок-схема алгоритма работы блока управления на фиг. 5 - формирователь задержки,

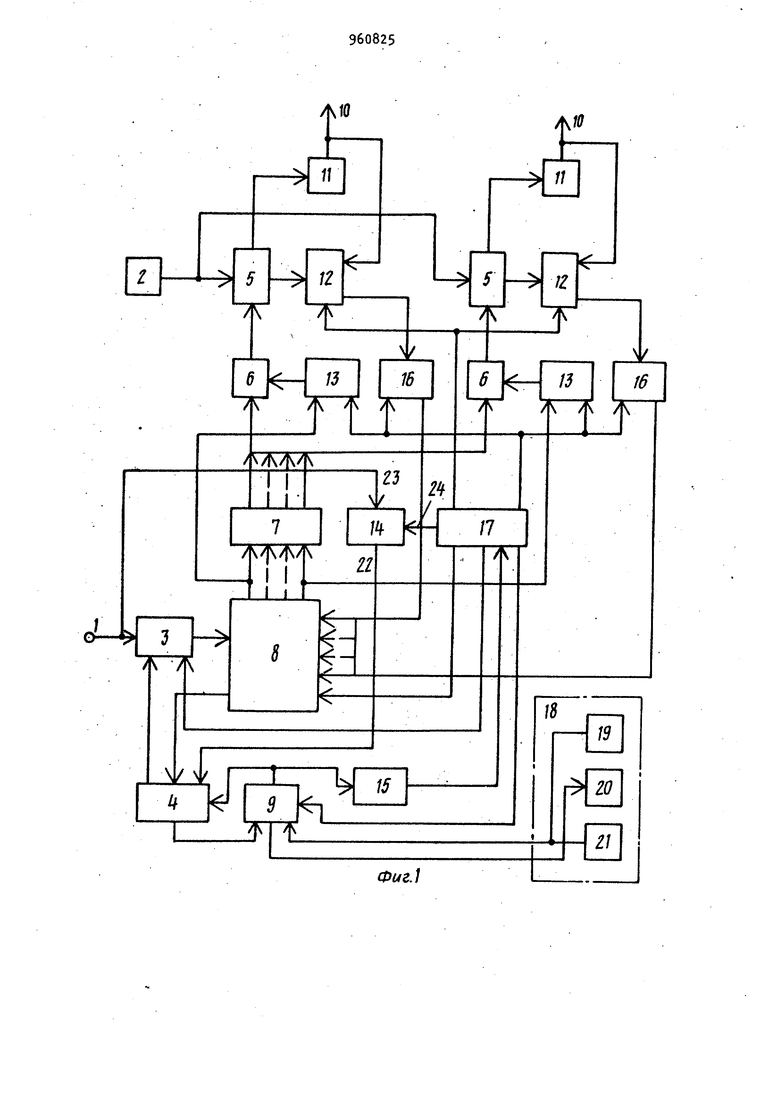

Устройство содержит вход 1, блок 2 опорных напряжений, элемент И-ИЛИ 3 первый регистр , переключатель 5 дешифратор 6, третий регистр 7, регистр 8 сдвига, блок 9 ввода-вывода, выход 10 устройства, формирователь 11 импульса, узел 12 сравнения, первый блок 13 памяти, преобразователь 1 кода, второй регистр 15, второй блок 16 памяти, блок 17 управления, блок 18 терминалов, фотосчитывающий механизм 19, дисплей 20, алфавитноцифровую клавиатуру 21, вывод 22 преобразователя кода, первый 23 и второй 2k входы преобразователя кода, сумматор 25 по модулю два, шестнадцатиразрядный регистр 26 сдвига с обратными связями, генератор 27 тактовых импульсов, узел 28 сравнения, счетчик 29, управляющий автомат 30, счетчик 31, коммутатор 32, элемент ИЛИ 33, коммутатор 3, дешифратор 35 коммутатор 36, дешифратор 37, узел 3 памяти, элемент ИЛИ 39, регистр 40, элемент И 1, триггер 2, счетчики 3 и 44, регистры 45 и 46, счетчик 47, триггер 48, формирователь 49 задержки, узлы 50 и 51 сравнения, входы -52-54 условий управляющего автомата, выход 55 числа управляющего автомата, выход 56 импульса сопровождения, вход 57 импульсов синхронизации входы 53-61 условий управляющего автомата, управляющие выходы Ь2 и 63, выходы 64 и б5.

Блок 2 опорных напряжений предназначен для формирования уровней выходных сигналов, элемент И-ИЛИ 3 - для коммутации информации, поступающей со входа 1 устройства или из регистра 4, который Используется как буферный .

Переключатели 5 коммутируют опорное напряжение или на формирователь 11, или на схему 12 сравнения.

Дешифраторы 6 предназначены для управления работой переключателей 5, регистр 7 - для хранения информации о распределении каналов на входные и выходные. Регистр 8 сдвига используется для запоминания информации, поступающей со входа 1 устройства, для записи программы проверки в блок 13 памяти и считывания результатов контроля из блока 16 памяти, блок 9 ввода-вывода - для сопряжения с блоком 18 терминалов.

Формирователи 11 предназначены для усиления по мощности выходных сигналов устройства, узел 12 сравнения - для сравнения уровней входных сигналов с уровнем опорного напряжения, блок 13 памяти - для хранения программы проверки.

Преобразователь 14 кода предназначен для преобразования импульсной последовательности, поступающей со входа 1 устройства, в ключевые коды (сигнатуры).

Регистр 15 используется для хранения команд управления.

Блок 16.памяти предназначен для хранения ответных сигналов, поступающих от проверяемого блока, блок 17 управления - для организации управления режимами работы устройства, блок 18 терминалов - для отображения информации и ввода исходных данных в устройство.

Генератор 27 тактовых импульсов предназначен для формирования импуль сов синхронизации.

Узел 28 сравнения предназначен для сравнения кодов, поступающих со счетчика 47 и из регистра 15, счетчик 29 - для подсчета первых трех байтов в сообщении, управляющий автомат 30 - для выработки сигналов, управляющих работой устройств счетчик 31 для определения состояния автомата и формирования кодов адресов на адресные входы коммутаторов 3 и 36, дешифраторов 35 и 37 и узла 38 памяти. Коммутатор 32 используется для формирования сигналов, разрешающих запись кода в счетчик 31. Элемент ИЛИ 33 предназначен для формирования сигнала обращения к уз лу 38 памяти, коммутатор З для управления по стробирующему входу дешифратором 35, формирования сигналов обращения к узлу 38 памяти сигнала, разрешающего переход счетчика 31 в новое состояние по импульсу син хронизации, дешифратор 35 - для формирования выходных управляющих сигналов автомата. Коммутатор 36 управляет по строби рующему входу дешифратором 37, который применяется для формирования выходных сигналов автомата, используемых для управления ОЗУ 13 и 16, а также для выдачи служебных байтов в блок 9 ввода-вывода. Узел 38 памяти хранит необходимые коды адресов переходов счетчика 31 , коды, определяющие сигналы управлени ОЗУ 13 и 16, коды служебных байтов. Элемент ИЛИ 39 предназначен для формирования сигнала, разрешающего переход счетчика 31 в новое состояние при подаче на. его счетный вход импульса, регистр kO - для запоминания кода, определяющего управляющие сигналы на выходах 63 автомата, и формирования сигнала, запрещающего работу коммутатора 3 во время формирования сигналов на выходах 63. Элемент И 1 используется для формирования сигнала сопровождения служебного байта. Триггер k2 формирует сигнал, разрешающий запись импульсной последова тельности в преобразователь Ц кода или в регистр 8 сдвига. Счетчик 3 предназначен для отсче .та восьми импульсов сдвига, управляю щих работой регистра 8 сдвига, счетчик ЦЦ - для подсчета количества бай тов в сообщении, поступающем от блока 18 терминалов. Регистр 5 предназначен для хране ния количества байтов в сообщении, регистр k6 - для хранения количества наборов в тест-программе, счетчик 7 для формирования адреса ОЗУ 13 и 16. Триггер 48 управляет работой элемента И-ИЛИ 3. Формирователь 9 задержки предназ начен для формирования задержки сигнала стробирования узла 12 сравнения, узел 50 сравнения - для сравнения кодов, записанных в счетчике k и регистре 5, узел 51 сравнения - для сравнения кодов, записанных в счетчике 7 и регистре . Устройство работает следующим образом. С алфавитно-цифровой клавиатуры 2Т через блок 9 ввода-вывода на блок 17 управления подается команда, по которой последний разрешает ввод информационных сообщений от фотосчитывающего механизма 19 через блок 9 ввода-вывода в регистры 4 и 15. Каждое сообщение состоит из трех служебных и нескольких информационных байтов, количество информационных байтов определяется числом п выходных каналов устройства и равно И/В . Под каналом понимаются выходы 10 устройства, к которым подключаются контакты контролируемого узла независимо от того, являются они входными.или выходными. (На фиг,. 1 показаны только 2 выходных канала устройства). Если устройство строится на п каналов, то в нем должно быть по п выходов 10, формирователей 11, переключателей 5,узлов 12 сравнения, дешифраторов 6,блоков 13 и 16 памяти. Должно быть также по п разрядов в регистрах 7 и 8. При контроле логического узла каждая из его клемм входов-выходов подключается к одному из выходов 10 устройства. Первый из служебных байтов определяет режим работы устройства, второйномер набора, на котором необходимо произвести останов устройства, третий - величину задержки записи ответных сигналов проверяемого блока. Устройство работает в режимах коммутации входов-выходов, проверки коммутации, подачи на проверяемый блок и приема от него логических сигналов в одноразовом и циклическом режимах, останова по номеру набора, измерения .задержки логических сигналов и диагностики неисправных элементов. Вначале поступают служебные байты, которые записываются в регистр 15 и являются исходными данными для блока 17 управления для определения режима работы устройства. Затем поступает п/8 байтов программы коммутации, определяющих какие из каналов устройства входные, а какие выходные. Каждый из этих п/8 байтов программы коммутации по команде, поступающей из блока 17 управления, записывается в регистр Ц, а затем блок 17 управле ния вырабатывает восемь импульсов сдвига и сдвигает принятый байт из регистра 4 в регистр 8 сдвига через элемент И-ИЛИ 3 управляемый блоком 17 управления. При этом регистр h освобождается для принятия следующего байта. После приема всех байтов программы коммутации содержимое регистра 8 сдвига переписывается в соответству-;ющие разряды регистра 7. Состояние каждого разряда регистра 7 определяет режим соответствующего канала уст ройства на все время работы с контро лируемым узлом. Если разряд регистра 7 находится в состоянии 1, то данный канал - выход. При этом на дешиф ратор 6 поступает сигнал, разрешающий прохождение сигналов из блока 13 памяти на переключатель 5- Если разря регистра 7 находится в соЬтоянии 0 то канал является входом и сигнал блока 13 памяти не проходит через дешифратор 6. Основной режим работы устройстваподача на контролируемый узел -и прием от него логических сигналов, т. е. режим тестовой проверки. Прием сообщений происходит следующим образом. По поступлению первого байта сообщения блок 17 управления записывает его в регистр 15. Этот байт определяет режим работы устройства. Второй и третий байты могут отсутствовать в сообщении. Наличие второго байта означает режим останова по номеру, т. е останов устройства в определенном месте программы проверки. Присутствие третьего байта означает режим измерения задержки сигналов в контролируемом блоке. Прием информационных байтов теста аналогичен приему в режиме коммутации. После записи всего информационного сообщения об одном тесте в регистр 8 сдвига блок 17 управления вырабатывает команду, по торой содержимое разрядов регистра 8 сдвига переписывается в блок 13 памя ти соответствующих каналов. Причем и формация о первом наборе записывается в блок 13 памяти по первому адресу, информация о втором наборе по вт рому адресу и т. д. Адрес для блока 13 памяти формирует блок 17 управления. Количество сообщений, принимаемо 9 5 12 блоком 9 ввода-вывода в режиме тестового контроля, определяется длиной теста, т. е. количеством наборов информации, подаваемой на вход контролируемого узла. Под набором понимается период времени, в течение которого выходные сигналы устройства, поступающие на вход контролируемого узла, остаются неизменными. Тест строится таким образом, что в блок 13 памяти каналов, закоммутированных как выходные, записываются стимулирующие сигналы, подаваемые на вход контролируемого блока, а в блоке 16 памяти каналов, закоммутированных как входные, записывается информация об ответных сигналах, которые должны поступить от контролируемого блока. После приема всех наборов теста блок 17 управления запоминает, количество принятых наборов и считывает информацию из блока 13 памяти, начиная с первого адреса. Выходной сигнал блока 13 памяти поступает на вход дешифратора 6 и, в зависимости от состояния разряда в регистре 7, формирует на выходе дешифратора 6 стимулирующий сигнал, поступающий на вход переключателя 5- Источник 2 опорных напряжений вырабатывает опорные уровни М, которые необлогических О ходимо подавать на входы контролируемого узла в зависимости от той элементной базы, на которой построен контролируемый узел. Если канал является выходом устройства, дешифратор 6 управляет переключателем 5 таким образом что эти опорные уровни на формирователе 11 преобразуются в логические си1- налы с необходимыми значениями О и 1, поступаемые на выход 10 устройства. Если канал является входом устройства, дешифратор 6 запрещает передачу логических уровней на формирователь 11, и он является нейтральным по отношению к выходу 10, а уровни логических.0. и 1 поступают на вход. При последовательном чтении из блока 13 памяти на выходах 10 устрой ства формируется последовательность логических сигналов, поступающих на входные контакты контролируемого блока. В ответ на стимулирующие сигналы на выходных контактах контролируемого блока появляются сигналы, значения которых необходимо проверять. Эти сигналы поступают с,выходов 10 устройства на входы узлов 12 сравнения, где происходит проверка ответного сигнала с уровнем логической 1 или О в зависимости от ожидаемого значения ответного сигнала, записанного в бло 13 памяти. При несоответствии ответн сигналов заданным уровням логической 1 или О, а также при их неравенстве ответным сигналам, записанным в блоке 13 памяти, узел 12 Сравнения вырабатывает сигнал ошибки, который записывается в блок 16 памяти по том же адресу, по которому происходит сч тывание стимулирующих сигналов из блока 13 памяти. Адрес обоих блоков памяти определяется блоком 17 управления . После чтения блоком 13 по последнему адресу, величина которого равна количеству принятых кадров информаци блок 17 управления в зависимости от служебного байта или прекращает чтение блока 13 памяти, или, если задан циклический режим, начинает чтение его с первого адреса, чем обеспечива ется формирование очередного цикла подачи стимулирующих сигналов. Если служебным байтом устройству задана одноразовая проверка, то после прохождения одного цикла устройство переходит к передаче результатов проверки на дисплей 20 блока 18 терминалов. При этом блок 17 управления начинает чтение блока 1б памяти с первого адреса. Выходные чис ла блока 1б памяти переписываются в регистр 8 сдвига, а затем по команде блока 17 управления сдвигаются из него побайтно в регистр Ц и через блок 9 ввода-вывода поступают для отображения на дисплее 20. Вместо дисплея 20 может быть подключено печатающее устройство, для распечатки результатов контроля или ЭВМ для распечатки результатов контроля или ЭВМ для дальнейшей их обработки. Если при проверке в контролирую емом блоке обнаружены несоответствия ответных сигналов заданным, в блок 16 памяти записываются ошибки в соответствующих адресах. Эти ошибки отображаются на дисплее с указанием номера набора и канала, что дает возмож ность, пользуясь диагностическими словарями, определять характер неис правности. Одноразовая проверка используется если необходимо определить исправен или не исправен контролируемый блок и выявить ошибки в сигналах на его выходных контактах. Циклический режим применяется, если необходимо произвести диагностику контролируемого блока. Для локализации неисправности, т. е. определения вышедшего из строя элемента, например микросхемы, используется вход 1 устройства. Этот вход, а точнее щуп, имеющийся в реальном устройстве, можно подключить к любой точке схемы контро-лируемого блока. На вход 1 устройства с проверяемого блока поступает последовательность логических сигналов, которая в режиме диагностики может записываться в регистр 8 сдвига или в преобразователь 1А кода. Информационные сигналы поступают на вход 23 преобразователя кода, а импульсы сдвига - на вход . С выходов седьмого, девятого, двенадцатого и шестнадцатого разрядов регистра 26 на входы сумматора 25 по модулю два заводятся обратные связи. За счет этого в сумматоре 25 происходит сложение по модулю два информационной последовательности) поступающей на вход 23 преобра.зователя It, и чисел, записанных в этих разрядах. Так как регистр 8 сдвига является более быстродействующим, чем регистр 2б сдвига с обратными связями, то при записи логических сигналов с входа 1 с частотой, равной тактовой частоте стимулирующих сигналов на выходах 10, используется преобразователь кода, а при записи с более высокой частотой - регистр 8. Выбор осуществляет блок 17 управления за счет перевода его в соответствующий режим внешними переключателями (на фиг. 1 не показаны). Если выбрана запись в регистр 8 сдвига, то при нажатии кнопки на щупе, подключаемом к входу 1 устройства, на блок 17 управления поступает команда, по которой он разрешает запись логических сигналов с входа 1 устройства через элемент И-ИЛИ 3 в регистр 8 сдвига..Период, в течение которого информация записывается в регистр 8 сдвига, выбирается в промежутке между подачей первого и последнего набора стимулирующих сигналов, т. е. во время, когда в контролируемом узле формируются ответные сигналы не только на его выходах, но и в других точках схемы. После выдачи последнего набора теста блок 17 управления начинает побайтно переписывать принятую информацию из регист ра 8 сдвига в реги.стр t и ее передаl5 9 чу через блок 9 ввода-вывода на дисплей 20, где эта информация отобража ется в виде временной диаграммы, наблюдая которую можно, сравнивая ее с эталонной, определять характер неисправности. Если к блоку 9 вводавывода подключена ЭВМ, эту информацию можно обработать, получив, например, из нее сигнатуру и сравнив ее С эталонной, определить место неисправности в контролируемом блоке. Если блок 17 управления переведен в режим, при котором логическая последовательность должна записываться в преобразователь k кода,устройство работает следующим образом. Блок 17 управления запрещает прохождение сигналов с входа 1 через элемент И-ИЛИ 3 и разрешает их запис в регистр 26 сдвига с обратными связями с тактовой частотой стимулирующих сигналов на входах 10 устройства По окончании одного цикла, во время которого поданы все наборы стимулиру ющих сигналов на контролируемый блок а в регистр 26 записывается импульсная последовательность с входа 1 уст ройства, в регистре 26 остается шест надцатиразрядное число, представляющее собой ключевой код (сигнатуру). После этого по команде блока 17 управления эти шестнадцать разрядов информации с преобразователя 1A кодов в виде четырех -разрядных слов передаются через регистр k и блок 9 ввода-вывода в блок 18 терминалов, где отображаются на дисплее 20 в виде четырехзначного слова сигнатуры. Наблюдая сигнатуру на дисплее и срав нивая с эталонными в диагностическом словаре, определяют неисправные элементы, например микросхемы контролируемого блока. При этом неисправно является та микросхема, в которой сигнатура на входе соответствует эта лонной, а на выходе нет. При необходимости проверки времени появления ответственного сигнала на выходе контролируемого блока по отношению к входным сигналам, в третьем байте ка дого сообщения содержится код величи ны задержки записи ответных сигналов контролируемого блока. Записанный в регистр 15 этот код определяет в бло ке 17 управления время задержки сигн.ала стробирования узла 12 сравнения по отношению ко времени появления ст мулирующих сигналов на выходах 10 устройства. 5 В режиме остановапо номеру набора при приеме теста в регистр 15 записывается первый служебный байт, определяющий этот режим, и второй служебный байт, определяющий номер набора, на котором необходимо произвести останов. Устройство в этом режиме на чинает работать так, как и в режиме тестовой проверки. Однако, когда значение кода адреса блока 13 памяти, который формирует блок 17 управления, становится равным коду во втором служебном байте регистра 15, опрос блока 13 памяти прекращается и происходит останов устройства на заданном наборе. При этом на выходах 10 устройства появляются неизменные логические сигналы, которые подаются на входы контролируемого блока. Результаты контроля записываются в блок 16 памяти и передаются на блок 18 терминалов так, как и в режиме тестовой проверки, с той разницей, что передаются результаты проверки только по набору, на котором произошел останов. Для перехода к проверке на следующем наборе в регистр 15 с алфавитно-цифровой клавиатуры 21 нужно записать код очередного номера кадра, на котором необходимо сделать останов. Режим проверки коммутации следует после режима коммутации и необходим, как контрольный режим. При режимах, коммутации и проверки коммутации контролируемый блок к устройству не подключается. В режиме проверки коммутации в регистр 15 записывается первый служебный байт, определяющий этот режим. В качестве теста на вход устройства передается набор из п/8 байтов, во всех разрядах которых записаны единицы. Как и в режиме тестовой проверки , этот кадр записывается по первому адресу в блок 13 памяти и передается на выходы 10 устройства. При этом логические единицы появляются на выходах тех каналов, котоыре закоммутированы как выходные,,а на выходах 10 входных каналов логические нули. Выходные логические сигналы с выходов 10 устройства поступают на входы узла 12 сравнения и сравниваются с сигналами на выходе переключателя 5, а результаты сравнения записываются в блок 16 памяти по первому адресу. После этого результат проверки коммутации переписывается из блока 16 памяти в регистр 8 и побайтно передается в блок 18 терминалов, чтобы 179 можно было убедиться в правильности коммутации и исключить ложные ошибки за счет неправильной коммутации при проверке контролируемых блоков. Блок 17 управления работает следующим образом. До начала обмена все счетчики, .регистры, триггеры, входящие в состав блока 17 управления находятся в нулевом состоянии. При поступлении информации от блока 18 терминалов блок 9 ввода-вывода передает команду начала обмена на вход 53 условий управляющего автомата 30, которая поступает на первый информационный вход коммутатора З. При наличии команды начала обмена на входе коммутатора 3 на его выходе б5 формируется сигнал, разрешающий через элемент ИЛИ 39переход счетчика 31 по тактовому импульсу в очередное состояние, при котором производит ся анализ поступившего байта по признаку: служебный он или информационный (блок С1 , фиг. 4с1). Счетчик 29 под считывает первые три байта в каждом сообщении. Если байт является служебным, счет чик 31 переводит автомат 30 в состояние анализа УС.ЛОВИЙ, поступающих из счетчика 29 (блок D 2,-фиг. ku) . Если служебный байт является первым, управляющий автомат 30 производит запись в первую группу разрядов регистра 15 (блок D 3, фиг. id), если вторым во вторую группу (блок F 2, фиг. ita), если третьим - в третью груп пу (блок G 2, фиг. 4а). После записи каждого -служебного байта автомат возвращается в состояние анализа характе ра принимаемого байта (блок С1, фиг. ю). Если принимаемый байт не яв ляется служебным, на выходах 62 появляются последовательно сигналы записи байта в регистр k (блок D 1, фиг. ) сигнал, разрешающий отсчет счетчиком 3 восьми импульсов для сдвига принятого байта из регистра 4 в регистр 8 (блок Е 1, фиг. ko), и к состоянию счетчика прибавляется единица (блок F 1, фиг. ijC) . При анализе первого служебного бай та на наличие признака конца набора (блок G 1, фиг. ), если этот признак поступает с выхода регистра 15 на вход 5 управляющего автомата 30 i управляющий автомат переходит в очередное состояние. Если этого признака нет, на выходе 65 коммутатора 3 5 появляется запрет на формирование управляющих сигналов дешифратором 35 и переход счетчика 31 в следующее состояние, а-.на выходе 6 коммутатбра З появляется сигнал, который через элемент ИЛИ 33 опрашивает узел 38 памяти. Число с выхода узла 38 памяти поступает на вход счетчика 31, а сигнал Сопровождение числа с второго выхода узла 38 памяти через коммутатор 32 поступает на управляющий вход счетчика 31 и разрешает запись числа в счетчик 31- Записанное ЧИСЛО определяет адрес перехода (в . данном случае из состояния б1 в состояние D 1, фиг. id). По приходу признака конца набора счетчик 31 переводит управляющий автомат 30 в состояние анализа первого служебного байта. Рели в нем присутствует признак режима коммутации, с выхода б2 управляющего автомата 30 поступает сигнал записи программы коммутации из. регистра 8 сдвига в регистр 7. Далее блок 17 управления переходит в состояние приема следующего набора информации от блока 18 терминалов (из состояния Н2 в состояние В1, фиг. а). По приему следующих наборов в регистр 8 сдвига каждый раз производится:анализ первого служебного байта (блок HI, фиг. о). Если первым служебным байтом задан не режим коммутации, информация из регистра 8 сдвига переписывается в ОЗУ 13 (блок 31, фиг. ka}, управляющие сигналы на ОЗУ 13 поступают с , выходу 63 управляющего автомата 30. В следующем состоянии автомат определяет какой набор тест-программы принят от блока,18 терминалов. При ЭТОМ, если в первом служебном байте нет признака последнего набора, к состоянию счетЧика 7 прибавляется единица (блок 52, фиг. ko), При поступлении признака последнего набора под управлением сигнала с выхода 62 управляющего автомата 30 произво- дится запись в регистр числа из счетчика 7 (блок К1, фиг. k), затем перевод счетчика 7 в нулевое состояние (блок 82, фиг. S}. На входы условий управляющего автомата 30 поступает сигнал от тумблера (не показан), который определяет режим сигнатурного анализа. При наличии этого сигнала с выхода 62 управляющего автомата 30 формируется сигнал, по которому триггер 48 устанавяивается в состояние, при котором информация с входа 1 устройства через схему И-ИЛИ 3 поступает на преобразователь 1 кода (блоки С2, С1, фиг, k. При отсутствии признака триггер 8 устанавливается в противоположное состояние, при котором информация с входа 1 устройства поступает на вход регистра 8 сдвига через элемент И-ИЛИ 5 Яблоки. С2, С35фиг. 43) После определения режима сигнатурного анализа управляющий автомат 30 переходит в состояние анализа сигнала (блок D2, фиг. (5), поступающего от кнопки, установленной на щупе, подключенном к входу 1 устройства. При наличии этого сигнала, поступающего на вход условий управления автомата 30, на выходах 62 формируются сигналы начала и конца записи -(блоки Е2, К1, фиг. с), которые поступают на триггер 2.формирующий, сигнал, который разрешает запись информации, поступаю щей с входа 1 устройства. Если сигнал от кнопки- отсутствует, сигналы нача- 25 ла и конца записи не формируются. Далее производится считывание из блока 13 памяти наборов тест-программы и запись в блок 16 памяти ошибок ответных сигналов от проверяемого устройства. Для этого с выхода дешифратора 35 поступает сигнал обращения к узлу 38 памяти через элемент ИЛИ 33, одновременно запрещается прохождение сигнала сопровождения числа от узла 38 памяти на вход счетчика 31 через коммутатор 32, а считанное число записывается в регистр 40, и определяется режим работы блоков 13 и 16 памяти. Информация последнего разряда регистра 40 запрещает работу коммутатора 3, а через элемент ИЛИ 39 разрешает переход счетчика 31 в следующее состояние. Информация из регистра 40 поступает на информационные входы коммутатора 36, который управляет работой дешифратора 37. Выходные сигналы дешифратора 37 управляют работой блоков 13 и 16 памяти. После считывания из .блока 13 памяти и записи в блок 16 памяти узел 51 сравнения сравнивает состояние счетчика 47 и регистра 46 (блок G2, фиг. kS . Если содержимое счетчика 7 не равно содержимому регистра k6, к состоянию счетчика kj прибавляется единица (блок G3, фиг. AJ), т. е. изменяется адрес блоков 13 и 16 памяти. Далее анализируется первый служебный байт на наличие признака режима останова по номеру набора. Если этого признака нет, автомат переходит в состояние выдачи следующего набора на проверяемое устройство (блок F2, фиг. 5). При наличии признака режима останова по номеру набора узел 28 сравнения сравнивает код счетчика 7 с кодом второго служебного байта, заОписанного в регистр 15 (блокЭЗ, фиг, kS) . Если состояние счетчика 7 и регистра 15 (вторая, группа разрядов) не равны, управляющий автомат 30 переходит в состояние, при котором на проверяемое устройство выдается следующий набор тест-программы. При равенстве содержимого счетчика kj и регистра 15 выдача следующих кадров тест-программы производится после нажатия кнопки Пуск (блок J3, фиг. MS}. .При равенстве состояний счетчика 7 и регистра tS (блок G2, фиг. 6), что означает выдачу на проверяемое устройство всей тест-программы, управляющий автомат 30 выдает сигнал конца записи (блок HI, фиг. «d) и переходит к анализу первого служебного байта на наличие в нем признака циклической Передачи. Если этого признака нет, управляющий автомат 30 переходит в состояние вывода информации на блок 18 терминалов (блокЭ2 , фиг, kS; блок В2, фиг. t) . При наличии признака сигнатурного анализа управляющий автомат 30 также переходит к выводу информации. Отсутствиепризнака сигнатурного анализа переводит управляющий автомат 30 в состояние анализа условия Конец цикла. Если лризнака Конец цикла нет, авто- мат переходит в состояние выдачи тестпрограммы с начала (блок 82, фиг. ). Формирователь kS задержки (фиг. 5 представляет собой линию задержки с выводами.с различными значениями времени задержки сигнала (в реальном устройстве 50-Т650 не с дискретностью 50 не). Эти выводы линии задержки соединены с информационными входами мультиплексора, с выхода которого задержанный сигнал поступает на вход стробирования узла 12 сравнения. Выбор времени задержки сиг.нала стробирования определяет код, поступающий с выхода регистра 15 на адресные входы мультиплексора. После всех режимов работы (тестовой передачи, циклической или получе219ния сигнатур) управляющий автомат 30 переходит в состояние передачи полученной в результате работы контрольной информации в блок 18 терминалов для отображения на дисплее; для печати или для отображения ЦВМ (фиг. W) Так как информация, полученная в v разных режимах работы, различная, управляющий автомат 30 определяет режим, при котором получена эта информация (блок В2, 0kir.. W). Для идентификации информации, полученной при различных режимах работы устройства, & блок 18 терминалов через блок 9 ввода-вывода передаются служебные байты (блоки С1, С2 СЗ, фиг. k), различные для каждого режима работы устройства. Далее, если режим работы - тёстовый контроль, производится сброс сче чиков i и 47 (блок 03 фиг. kS). Счет чик kk подсчитывает количество байтов, принятых от блока 18 терминалов Счетчик kj определяет адрес блока 13 памяти и подсчитывает количество наборов, принятых от блока 18 терминалов. После этогр управляющий автомат 30 начинает выдавать сигналы управления считыванием блока 16 памяти и переписывает из блока 16 памяти в регистр 8 сдвига набор информации (блок E3i фиг. k), сдвигает побайтно информацию из регистра 8 сдвига в регистр 4 (блок F3, фиг. S) и передает через.блок 9 ввода-вывода в блок 18 терминалов (блок G3, фиг. К состоянию счетчика с передачей каждого байта добавляется единица (блок НЗ, фиг. 4) и сравнивается со стояние счетчика i и регистра kS, если они не равны (блок 33, фиг. k-S управляющий автомат 30 переходит в состояние передачи следующего байта (блок F3, фиг. kS). Равенство состояний счетчика kk и регистра kS свиде тельствует о том, что вся информация данного теста передана. Количест во переданных наборов контролируется блоком 51 сравнения (блок 33, фиг. 4 После передачи каждого набора к сост янию счетчика добавляется единица и управляющий автомат переходит в состояние управления передачей следующего набора (блок ЕЗ Фиг. ЦВ}. Равенство состояний счетчика и регистра 6, определяемое, узлом 51 сравнения, означает, что все наборы информации переданы в блок 18 терми-522налов,и управляющий автомат 30передает в блок 9 ввода-вывода Сигнал Конец передачи. Передача информации при режимах сигнатурного анализа производится аналогичным образом. Особенность заключается в том, что в преобразователе I кода хранится два байта информации. Поэтому в этом режиме в регистр 45 (в котором хранится информация о количестве байтов) записывается код 2 (блок Е1, фиг. 4- и командй Конец передачи передается после выдачи двух информационных байтов (блок :П, фиг. if8). : В режиме, когда информационная последовательность с входа 1 устройства записывается в регистр 8 сдвига, в регистр 5 заносится число № п/8. где п - число разрядов регистра 8 сдвига (блок Е2, фиг. в). После передачи команды Конец передачи все устройство переводится в исходное состояние (блок А1, фиг. Да). Предлагаемое устройство благодаря введению в его состав новых узлов и связей обеспечивает работу в циклическом режиме, что расширяет его функциональные возможности, так как обеспечивается проверка контролируемых блоков в динамическом режиме, и на и входы можно подавать стимулирующие сигналы с достаточно высокой частотой, обеспечиваемой считыванием информации из блока 13 памяти. При этом частота подачи стимулирующих сигналов не определяется скоростью ввода теста,из блока терминалов и временем, необходимым для отображения результатов контроля на индикаторах. Циклический режим проверки контролируемых блоков позволяет наблюдать осциллограммы сигналов контролируемого блока на экране осциллографа, что облегчает диагностику неисправностей. Кроме того, возможна диагностика с его помощью неисправностей в контролируемом блоке за счет контроля логических последовательностей в произвольной точке схемы контролируемого блока и определения ключевых кодов - сигнатур этих последовательностей..Это позволяет повысить точность локализации неисправности в проверяемом узле. Формула изобретения 1. Устройство для контроля и диа|- ностики логических узлов, содержащее блок териииэлов, блок ввода-вывода, три pernctpa, блок опорных напряжений каналы по числу контактов проверяемого узла, каждый канал содержит дешифратор, переключатель, .узел сравнения формирователь импульса, причем выход блока терминалов соединен с первым входом блока ввода-вывода, первый выход которого соединен с входом блок терминалов, второй вход блока вводавывода соединен с первым выходом первого регистра, второй выход блока ввода-вывода - с входом второго регистра и вторым входом первого регистра, выходы третьего регистра - соответственно с управляющими входами дешифраторов, выходы которых соединены соответственно с первыми входами переключателей вторые входы которых соединены с выходом блока опорных напряжений, первые выходы переключателей соединены соответственно с первыми информационными входами узлов Сравнения, вторые информационные входы которых соединены соответственно с выходными контактами проверяемого узла, входные контакты которого соединены соответственно с выходами формирователей, входы которых, соединены соответственно с вторыми выходам.и переключателей, отличающееся тем, что, с целью увеличения точности локализации неисправностей, в него введен элемент И-ИЛИ, регистр сдвига, блок управления, преобразователь импульсного сигнала в сигнатуру, ; два блока памяти причем управляющий вход регистра сдвига соединен с первым выходом блока управления, второй выход которого соедине с управляющими входами узлов сравнения, первая группа выходов блока управления соединена с управляющими входами первого и второго блока памя ти, выходы первого блока памяти соединены соответственно, с и.нформационными входами дешифраторов, выходы второго блока памяти - с группой информационных входов регистра сдвига, выходы которого соединены с входами третьего регистра и с информационными входами первого блока памяти, информационный вход регистра сдвига со единен с выходом элемента И-ИЛИ., пер вый вход которого соединен с первым входом блока преобразования импульсного сигнала в сигнатуру и является входом устройства, второй вход элемента .И-ИЛИ соединен с вторым выхо дом.первого регистра, первый вход которого соединён с выходом регистра сдвига, второй вход первого регистра соединен с выходом блока преобразования импульсного сигнала в сигнатуру, выход второго регистра - с первым входом блока управления, третий выход которого соединен с вторым входом элемента И-ИЛИ, третий вход блока ввода-вывода - с второй группой выходов блока управления, третья группа выходов которого соединена с вторым входом блока преобразования кода, второй вход блока управления соединен с выходом второго регистра. 2. Устройство по п. 1, отличающееся тем, что блок управления содержит три узла сравнения, пять счетчиков, три коммутатора, два элемента ИЛИ, два дешифратора, узел памяти, три регистра, элемент И, два триггера, элемент задержки, генератор импульсов, причем первый вход блока соединен с управляющим входом элемента задержки, с первым входом первого. узла сравнения и с первым информационным входом первого коммутатора, первый управляющий вход которого соединен с выходом первого узла сравнения, второй вход которого соединен с выходом первого счетчика, с .информационным входом первого регистра, с первым входом второго узла сравнения, второй, вход которого является первым информационным выходом первой группы выходов блока, второй вход которого соединен с вторым информационным входом первого коммутатора и со счетным входом второго счетчика, выход которого соединен с втчэрым управляющим входом первого коммутатора, третий информационный вход которого соединен с выходом третьего счетчика, с первым входом первого дешифратора, с первым информационным входом второго коммутатора, с первым входом второго дешифратора, с информационным входом узла памяти, управляющий вход которого соединен с выходом первого элемента ИЛИ, первый вход которого соединен с первым информационным входом третьего коммутатора, с первым входом элемента И, с первым управляющим входом второго регистра, с выходом второго дешифра1тора, с информационным входом элемента задержки, вь1ход которого является вторым выходом блока, первый выход которого соединен с выходом четвертого счетчика, управляющий вход

которого сбединен с установочным входом первого триггера, со счетным входом пятого счетчика, с управляющим входом третьего регистра, с управляющим входом первого регистра, со счетным входом первого счетчика, с установочным входом второго триггера, с выходом первого дешифратора, с вторым входом первого элемента ИЛИ, с вторым управляющим входом второго регистра и является первым выхрдом блока второй группы выходов блока, второй выход второй группы выходов блока соединен с выходом элемента И, второй вход которого соединен с первым выходом узла памяти, с первым информационным входом второго регистра, с вторым информационным входом третьего коммутатора, выход которого соединен с первам управляющим входом третьего счетчика, второй управляющий вход которого соединен с выходом второго элемента ИЛИ, первый вход которого соединен с вторым входом первого дешифратора и с первым выходом первого коммутатора, второй выход которого соединен с третьим входом первого элемента ИЛИ, выход пятого счетчика соединен с информационным входом третьего регистра, с первым входом третьего узла сравнения, с четвертым информационным входом первого коммутатора, третий управляющий вход которого соединен с вторым входом второго элемента ИЛИ и с первым выходом

второго регистра, второй выход которого соединен с вторым информационным входом второго коммутатора, выход которого соединен с вторым входом второго дешифратора, второй информационный вход второго регистра соединен с вторым выходом узла памяти, с информационным входом третьего счетчика и является третьим выходом второй группы выходов блока, третий выход которого соединен с выходом второго триггера, выход первого триггера явля.ется первым выходом третьей группы выходов блока, второй выход третьей группы выходов которого соединен с синхровходом четвертого счетчц| а, е выходом генератора импульсов, с синхровходом третьего счетчика, выход второго узла сравнения соединен с четвертым управляющим входом первого коммутатора, пятый управляющий вход которого соединен с выходом третьего узла сравнения, второй вход которого соединен с выходом третьего регистра выход первого регистра соединен с вторым входом второго узла сравнения

Источники информации, принятые во внимание при экспертизе

1.Авторское свидетельство СССР № 551573, кл. G 01 R 31/02, 1977.

2.Авторское свидетельство СССР № 651351, кл. G 06 Г , 1979.

3.Авторское свидетельство СССР № 6187А2, кл. G Об F 11/ОА, 1978 (прототип).

AtO

П

11

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для сопряжения вычислительной машины с каналами связи | 1980 |

|

SU918944A1 |

| Устройство для отображения информации на газоразрядной индикаторной панели | 1983 |

|

SU1119065A1 |

| Устройство тестового контроля цифровых блоков | 1985 |

|

SU1315982A1 |

| Устройство для контроля и диагностики цифровых узлов | 1987 |

|

SU1587513A1 |

| Устройство для сопряжения процессора с каналами связи | 1978 |

|

SU763882A1 |

| Имитатор канала | 1987 |

|

SU1425675A2 |

| Устройство для контроля и диагностики логических блоков | 1984 |

|

SU1295401A1 |

| Устройство для сопряжения внешних устройств с накопителем на магнитной ленте | 1984 |

|

SU1348842A1 |

| ОТКАЗОУСТОЙЧИВЫЙ ПРОЦЕССОР С КОРРЕКЦИЕЙ ОШИБОК В БАЙТЕ ИНФОРМАЦИИ | 2021 |

|

RU2758065C1 |

| ОТКАЗОУСТОЙЧИВЫЙ ПРОЦЕССОР С КОРРЕКЦИЕЙ ОШИБОК В ДВУХ БАЙТАХ ИНФОРМАЦИИ | 2021 |

|

RU2758410C1 |

т

/

S

11

/

/к/ь/

I I 1 1

II. I i

3 fTvl

8

ч

/ /

2t

/

/7

/

Фиг.

Фиг.З

А 6

Cfpoc счетчика Сигнал конца запаси 47 Сигнал начала запиои

А В

Сигнатурн. анализ

Выдача теста

Сброс счетчица регистра г5

i

Гбя

Запись о регистр

cSBui на в/пактов из блока в блок

Передача В/ШТА черезУА.9вбА.№

±

Счетчикtt l

Запись слугкеЯт) бАИГА вбмк 9

±

счетчиков f,«7

Ж

СчитыОаниеО П, заяисьбрегиея у

а

Свбиг HagmaKt из регистра

в регистр Ч

передача БАЙТА через 9л.$в SA. )8

Ж

Счетчик 1

Счетчик 7

Фиг. 5

Авторы

Даты

1982-09-23—Публикация

1980-03-11—Подача