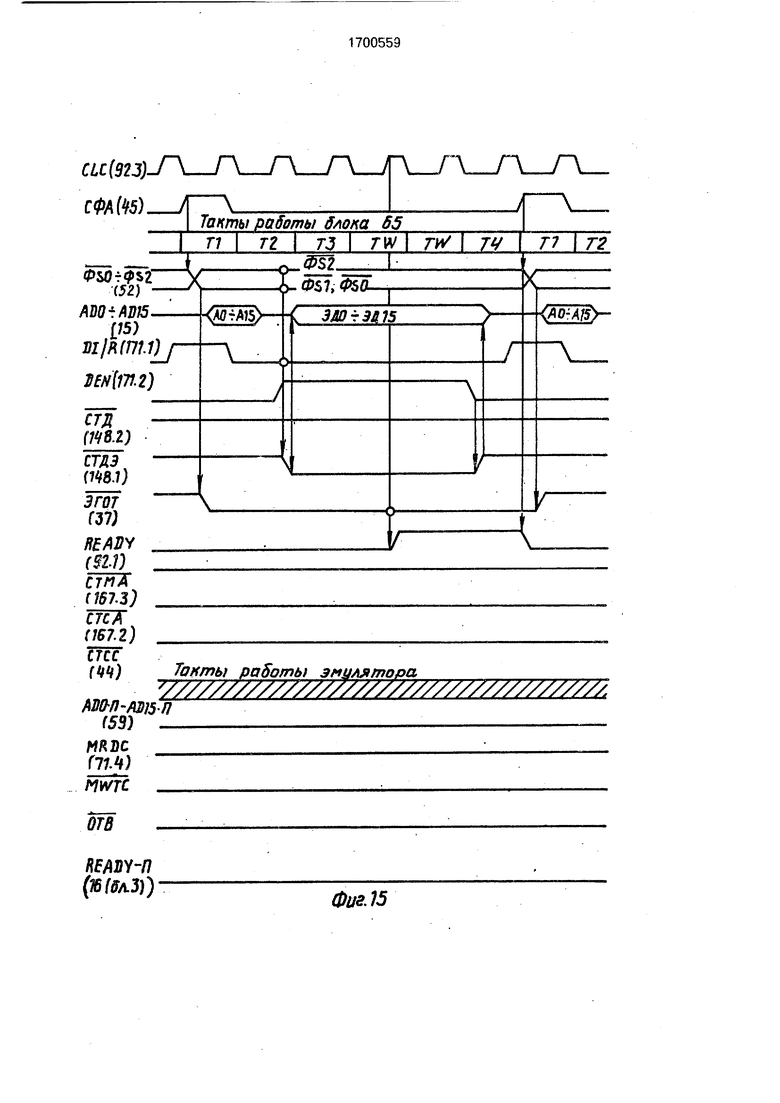

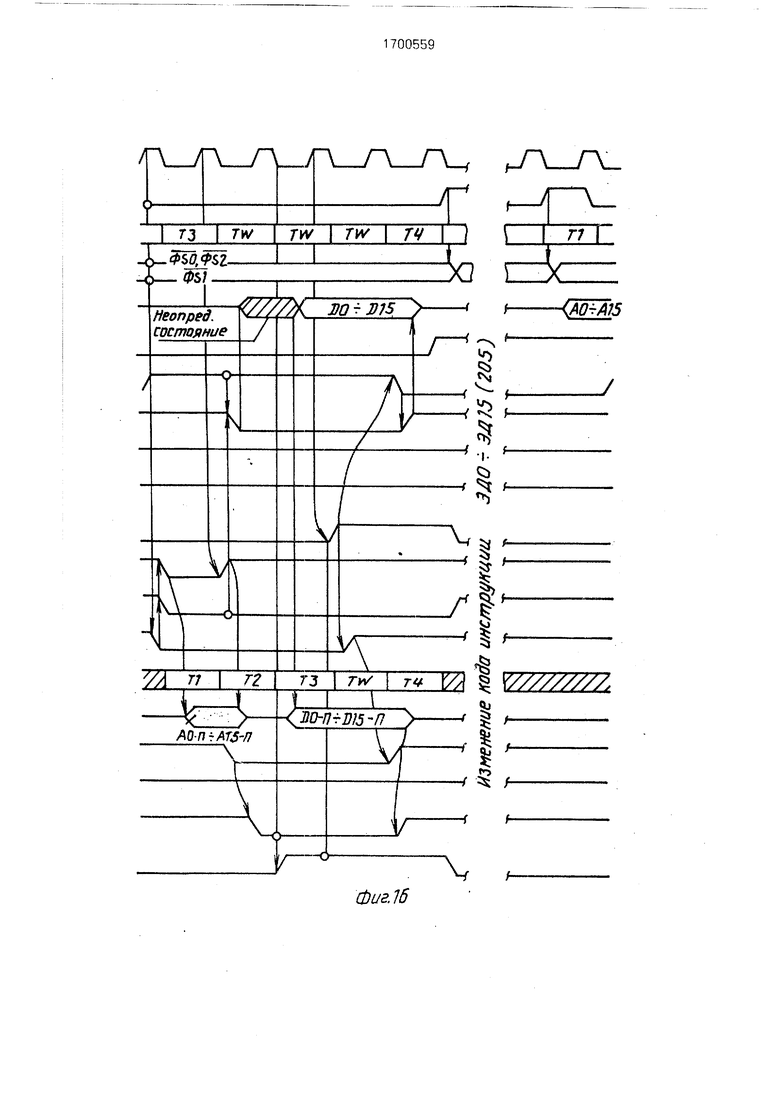

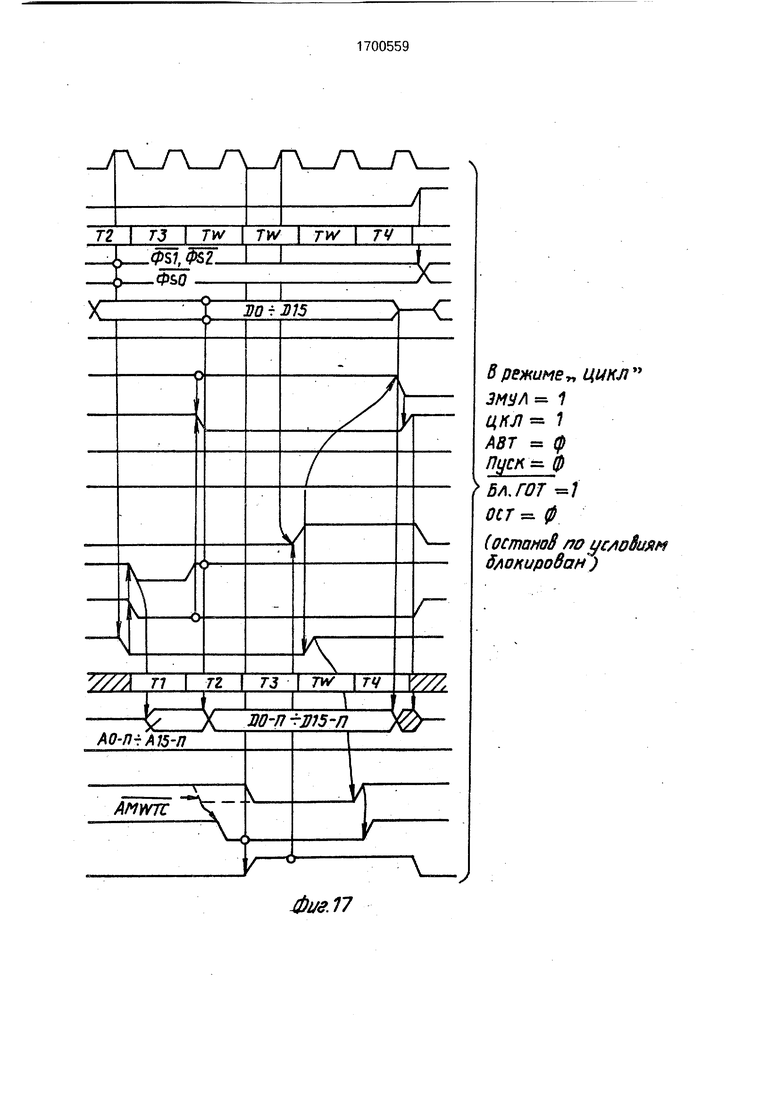

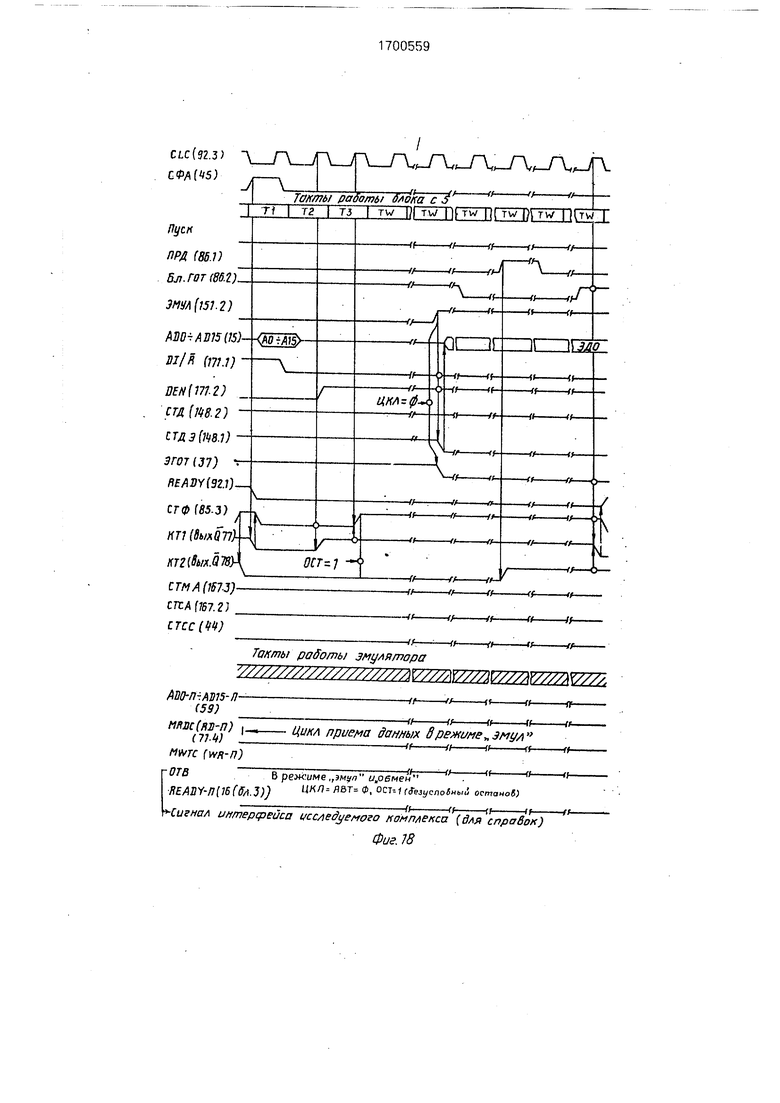

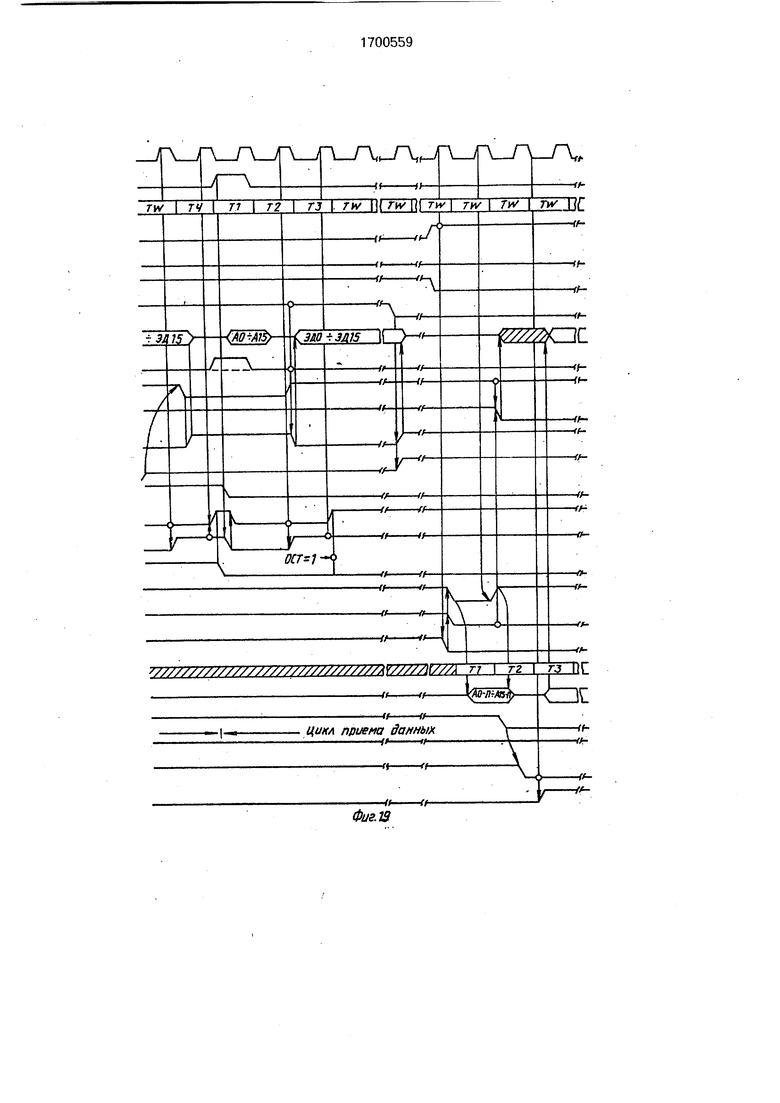

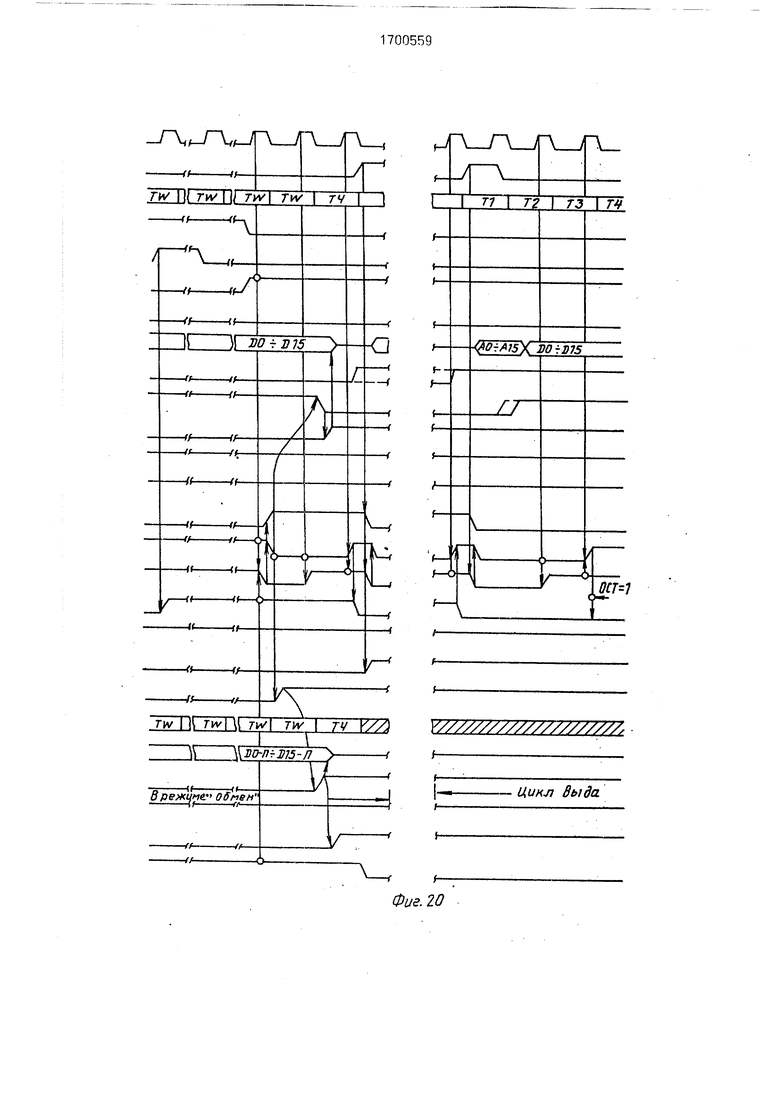

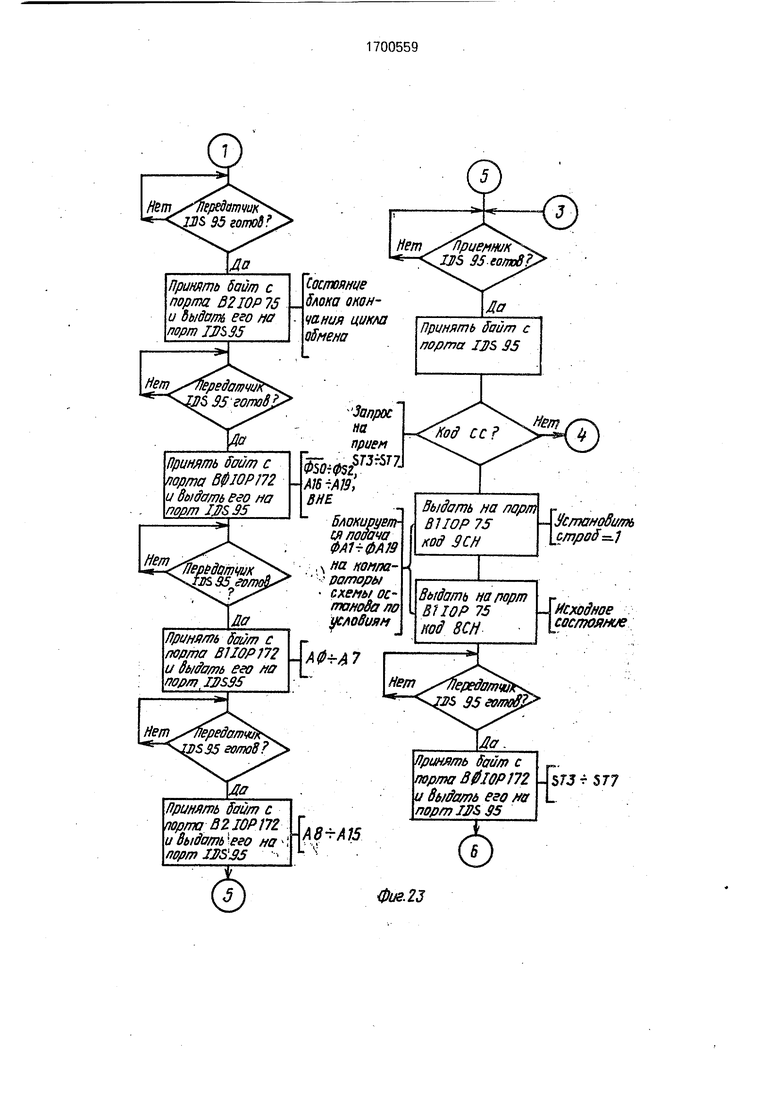

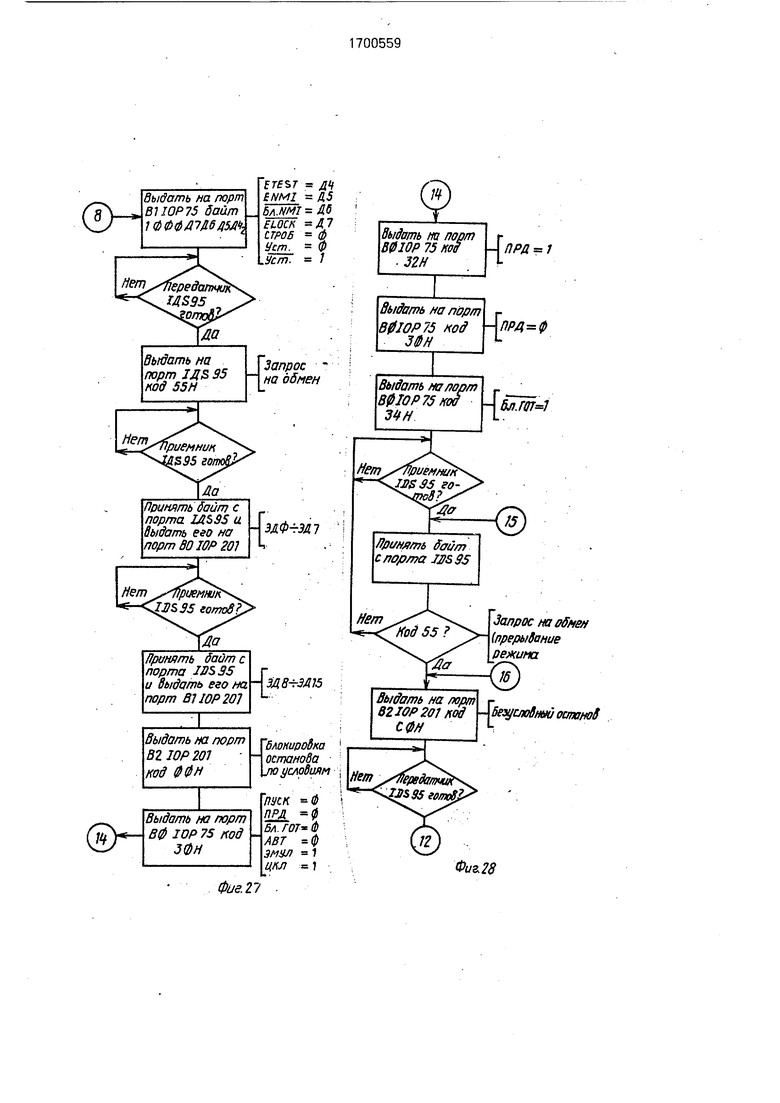

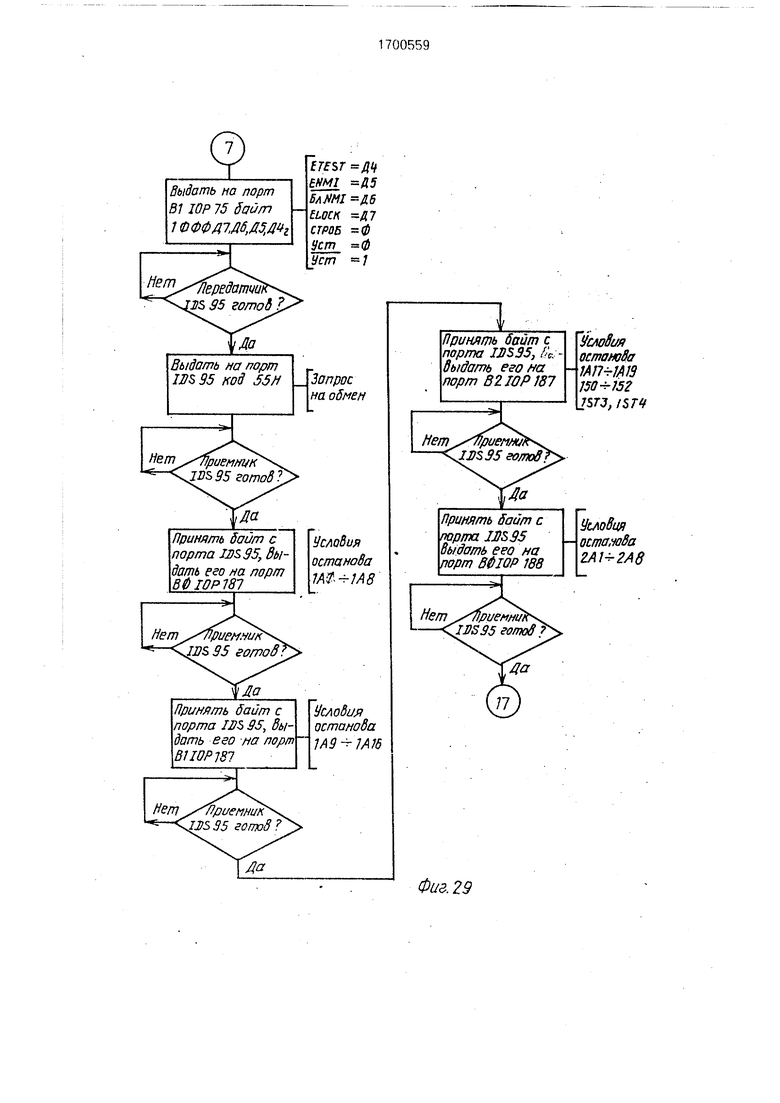

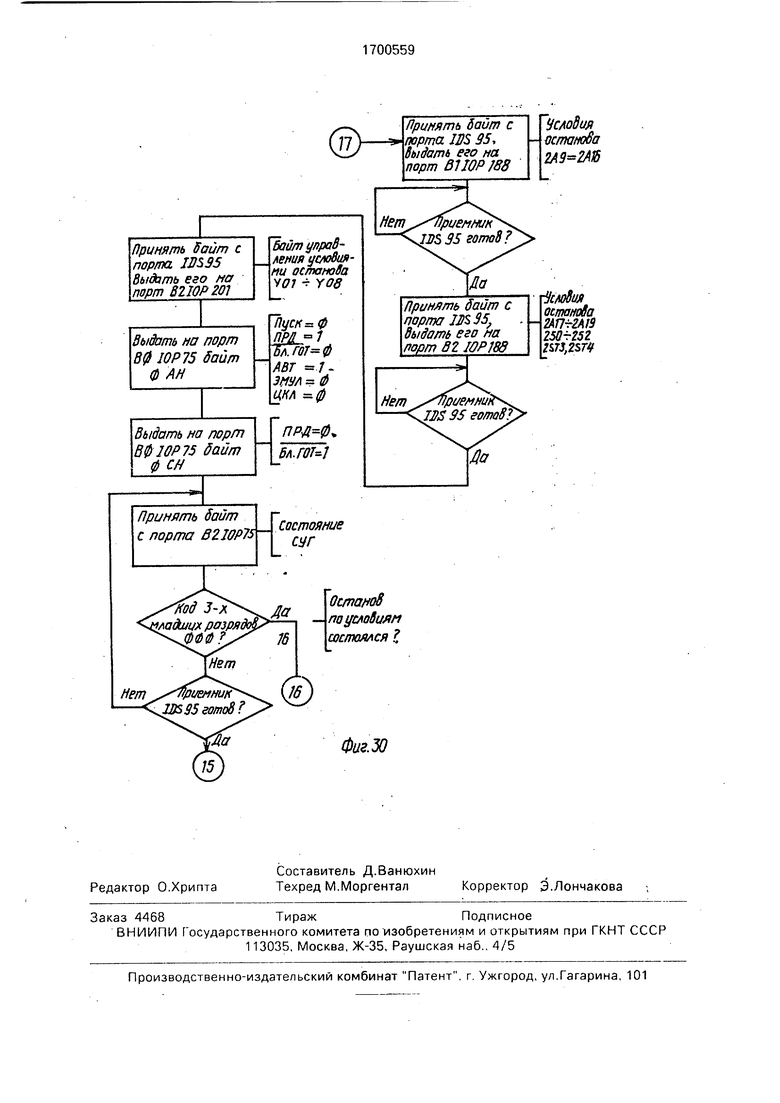

блока коммутации данных; на фиг 15-17 - временные диаграммы функционирования системы в режиме на фиг. 18-21 - то же, в режимах Эмуляция и Обмен ; на фиг, 22-30 - схемы алгоритмов функционирования системы во всех указанных режимах.

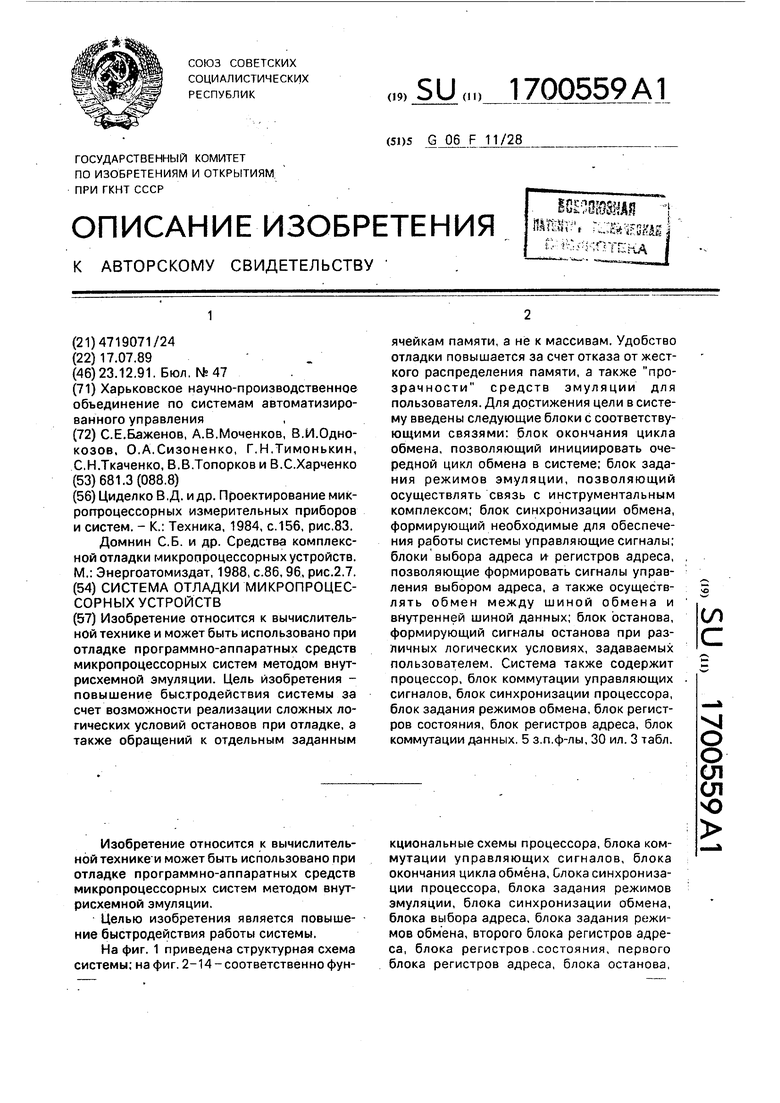

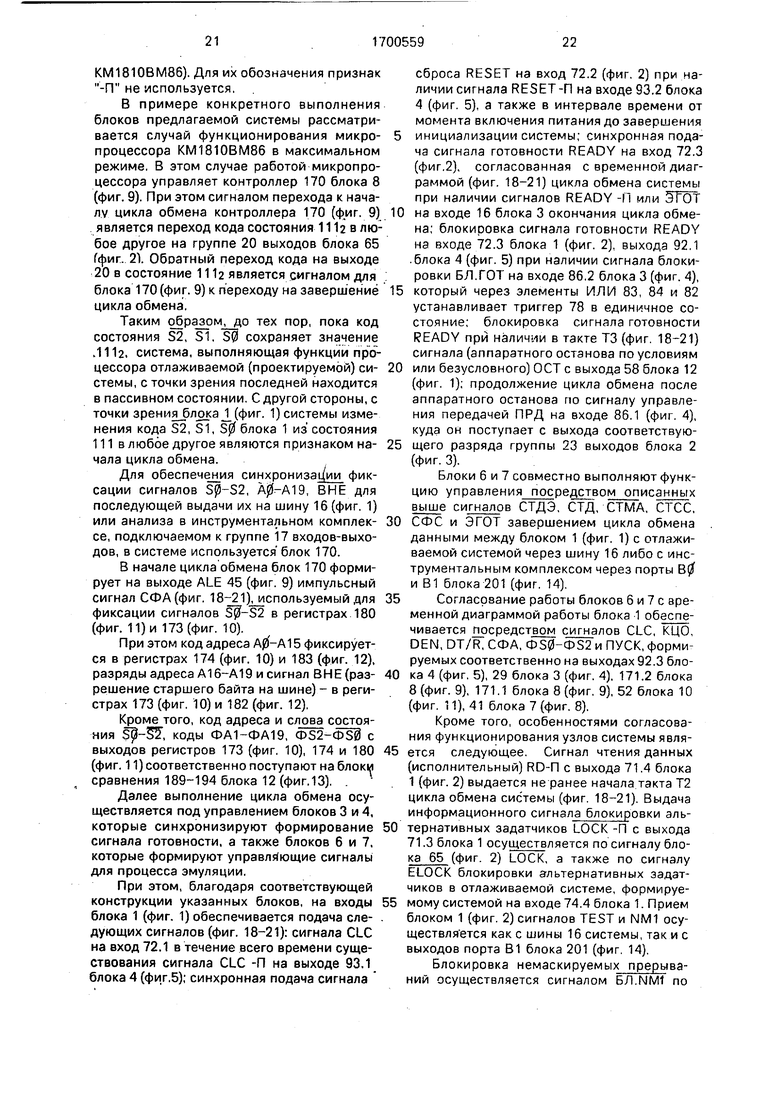

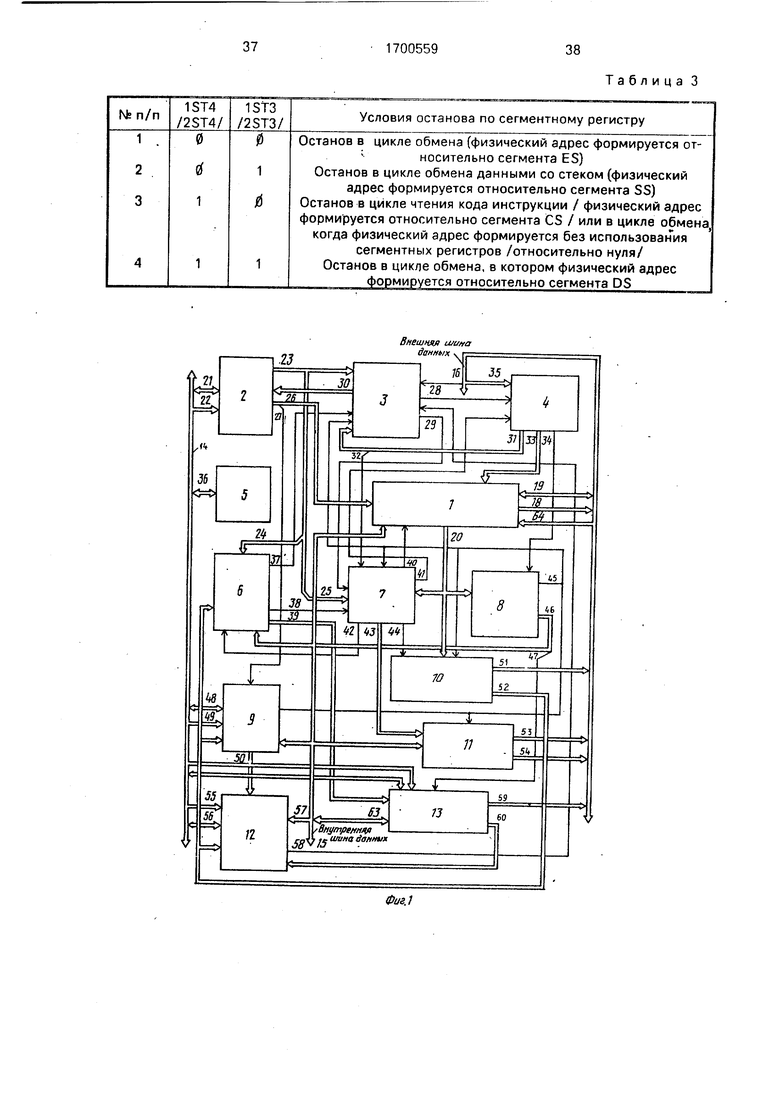

Система для отладки (фиг, 1} содержит процессор 1, блок 2 коммутации управляющих сигналов, блок 3 окончания цикла обмена, блок 4 синхронизации процессора, блок 5 задания режимов эмуляции, блок 6 синхронизации обмена, блок 7 выбора адреса, блок 8 задания режимов обмена, второй блок 9 регистров адреса, блок 10 регистров состояния, первый блок 11 регистров адреса, блок 12 останова, блок 13 коммутации данных , шину Т4 обмена, внутреннюю шину 15 данных, внешнюю шину 16 данных, группу 17 входов-выходов системы, входы-выходы 18-64 блоков системы.

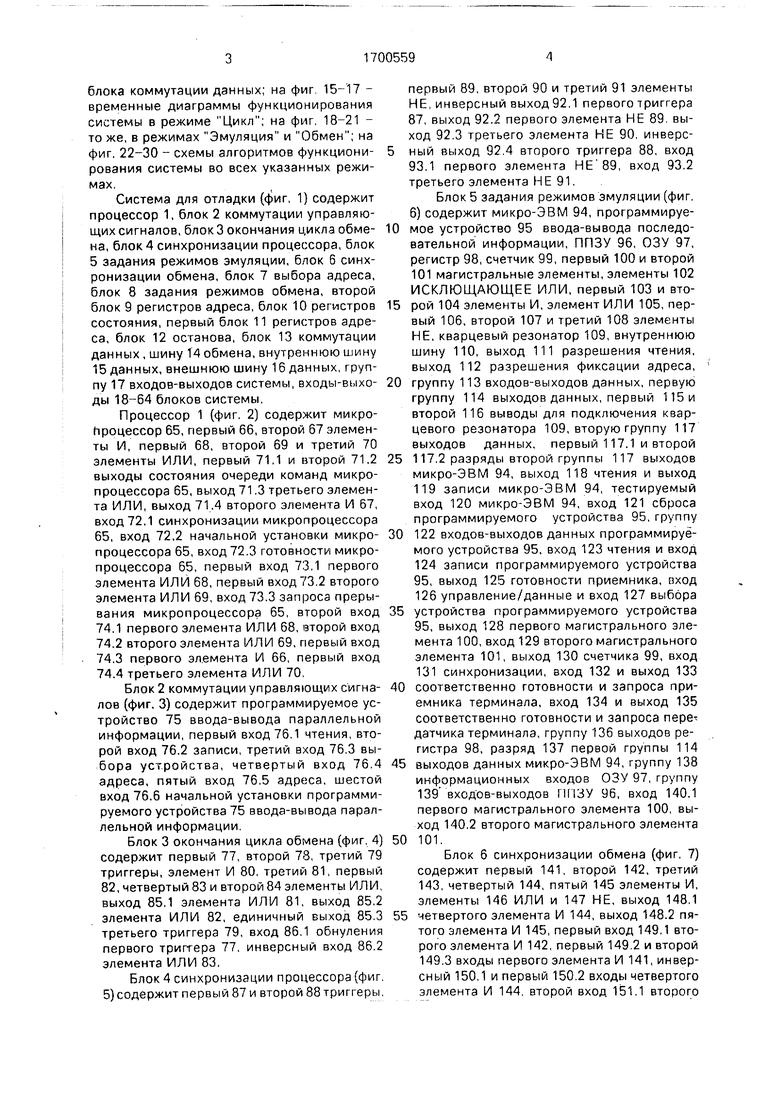

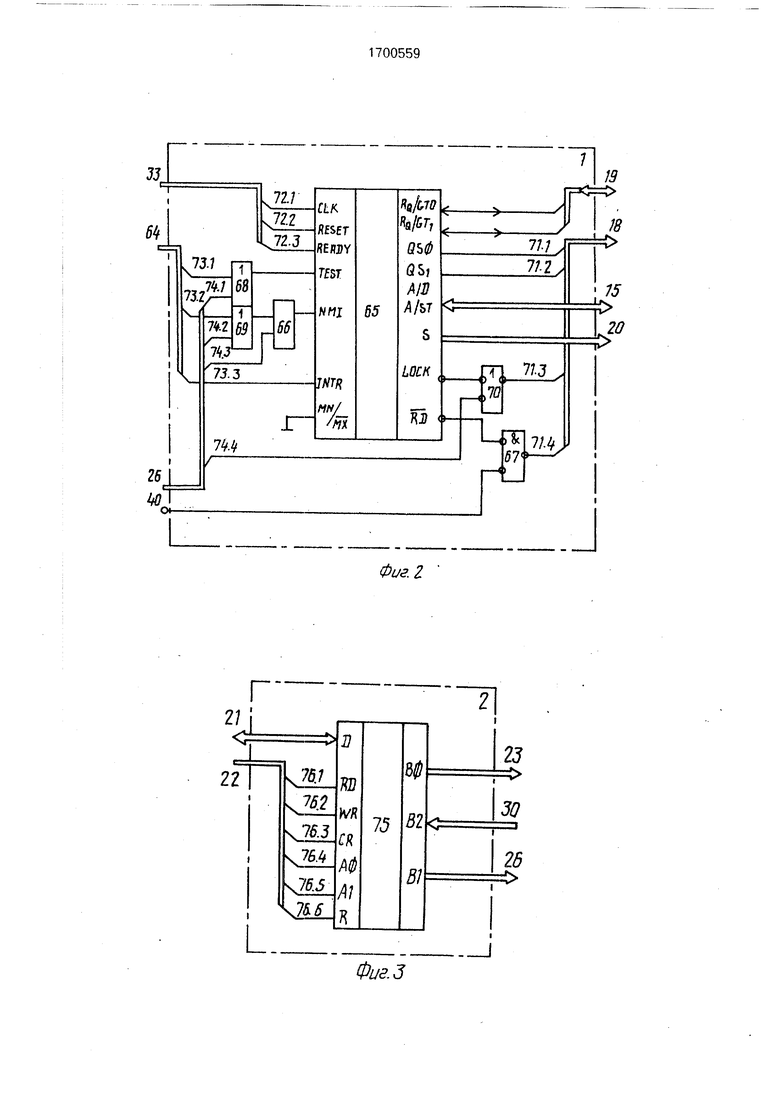

Процессор 1 (фиг, 2) содержит микро- гфоцессор 65, первый 66, второй 67 элементы И, первый 68, второй 69 и третий 70 элементы ИЛИ, первый 71,1 и второй 71.2 выходы состояния очереди команд микропроцессора 65, выход 71.3 третьего элемента ИЛИ, выход 71.4 второго элемента И 67, вход 72.1 синхронизации микропроцессора 65, вход 72.2 начальной установки микропроцессора 65, вход 72.3 готовности микропроцессора 65, первый вход 73.1 первого элемента ИЛИ 68, первый вход 73.2 второго элемента ИЛИ 69, вход 73.3 запроса прерывания микропроцессора 65, второй вход

74.1первого элемента ИЛИ 68, второй вход

74.2второго элемента ИЛИ 69, первый вход

74.3первого элемента И 66, первый вход

74.4третьего элемента ИЛИ 70.

Блок 2 коммутации управляющих сигналов (фиг. 3) содержит программируемое устройство 75 ввода-вывода параллельной информации, первый вход 76.1 чтения, второй вход 76.2 записи, третий вход 76.3 выбора устройства, четвертый вход 76.4 адреса, пятый вход 76.5 адреса, шестой вход 76.6 начальной установки программируемого устройства 75 ввода-вывода параллельной информации

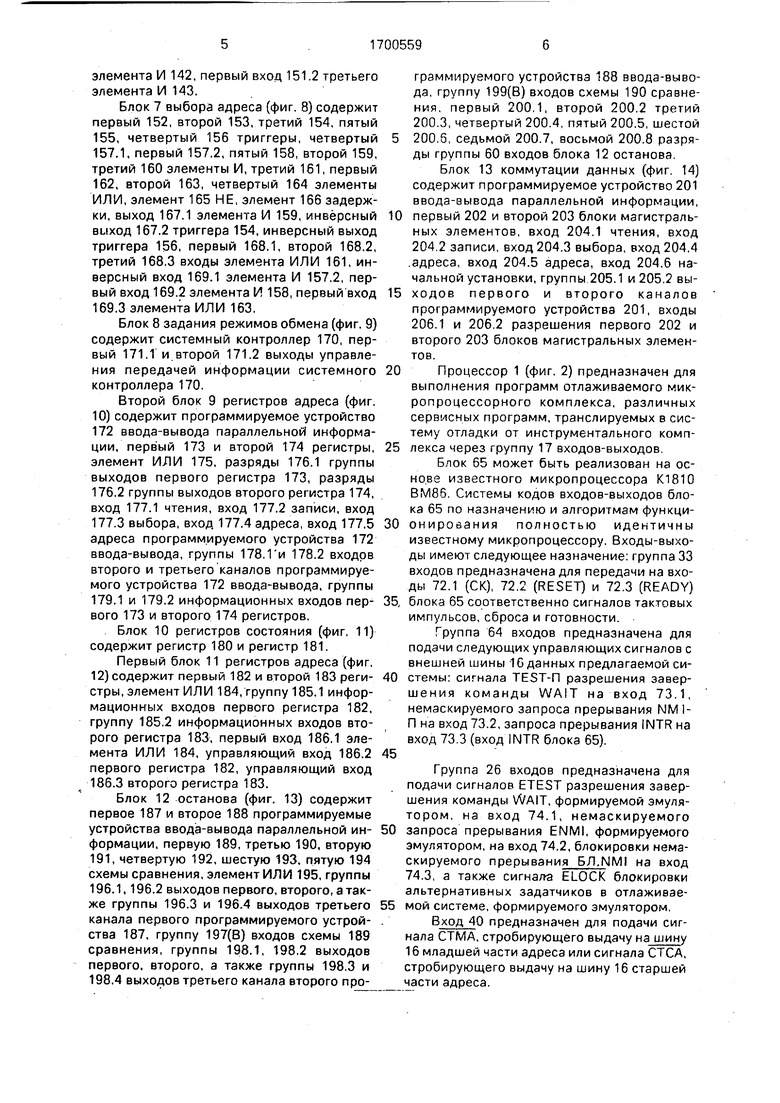

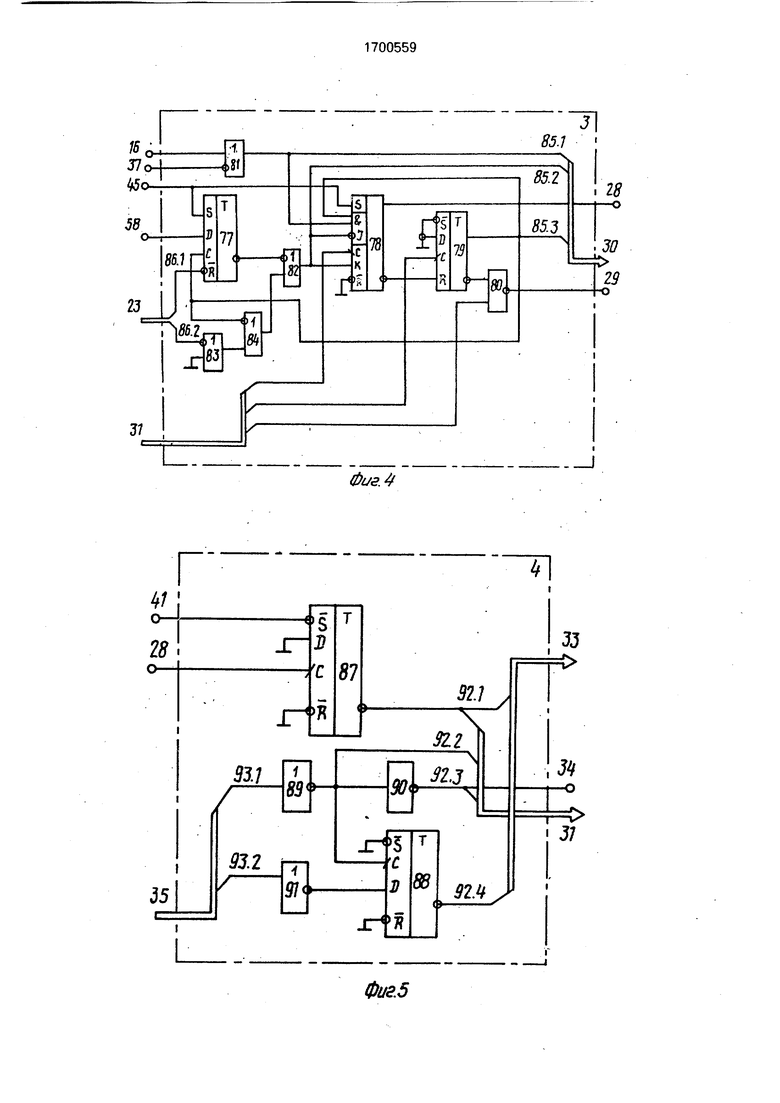

Блок 3 окончания цикла обмена (фиг, 4) содержит первый 77, второй 78, третий 79 триггеры, элемент И 80, третий 81, первый 82, четвертый 83 и второй 84 элементы ИЛИ, выход 85.1 элемента ИЛИ 81, выход 85,2 элемента ИЛИ 82, единичный выход 85.3 третьего триггера 79, вход 86.1 обнуления первого триггера 77, инверсный вход 86.2 элемента ИЛИ 83.

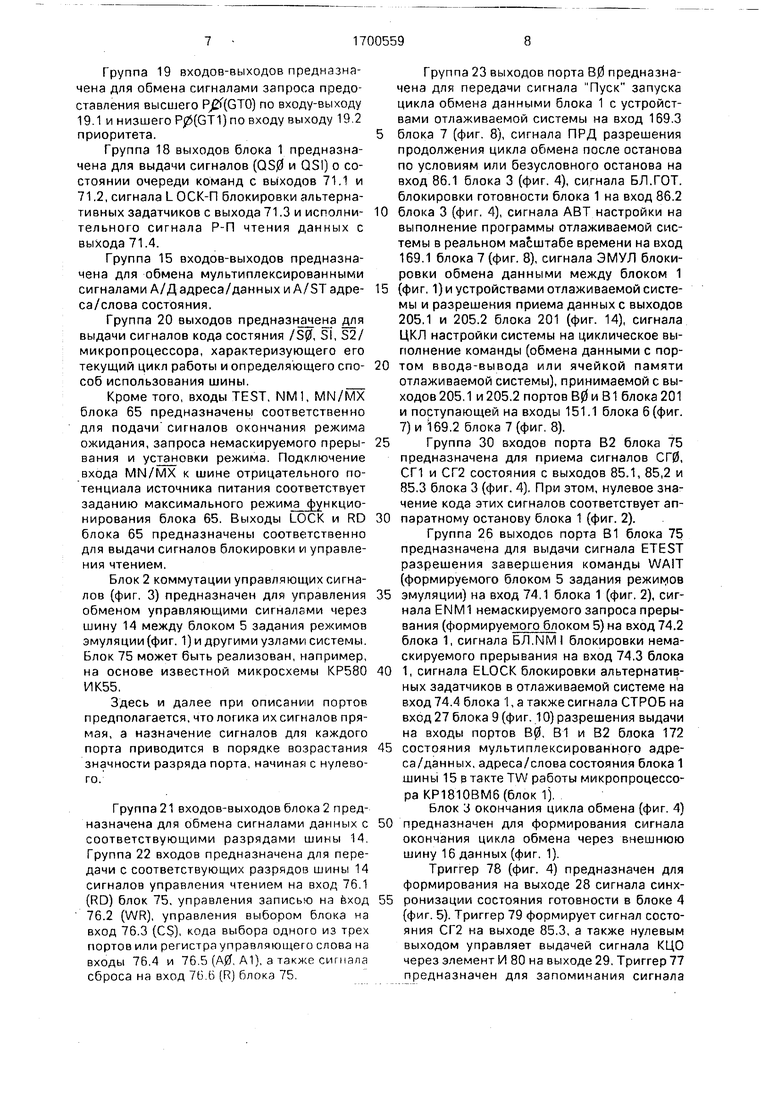

Блок 4 синхронизации процессора (фиг 5) содержит первый 87 и второй 88 триггеры

первый 89, второй 90 и третий 91 элементы НЕ, инверсный выход 92.1 первого триггера 87, выход 92.2 первого элемента НЕ 89 выход 92.3 третьего элемента НЕ 90, инверсный выход 92 4 второго триггера 88, вход 93.1 первого элемента НЕ 89, вход 93.2 третьего элемента НЕ 91.

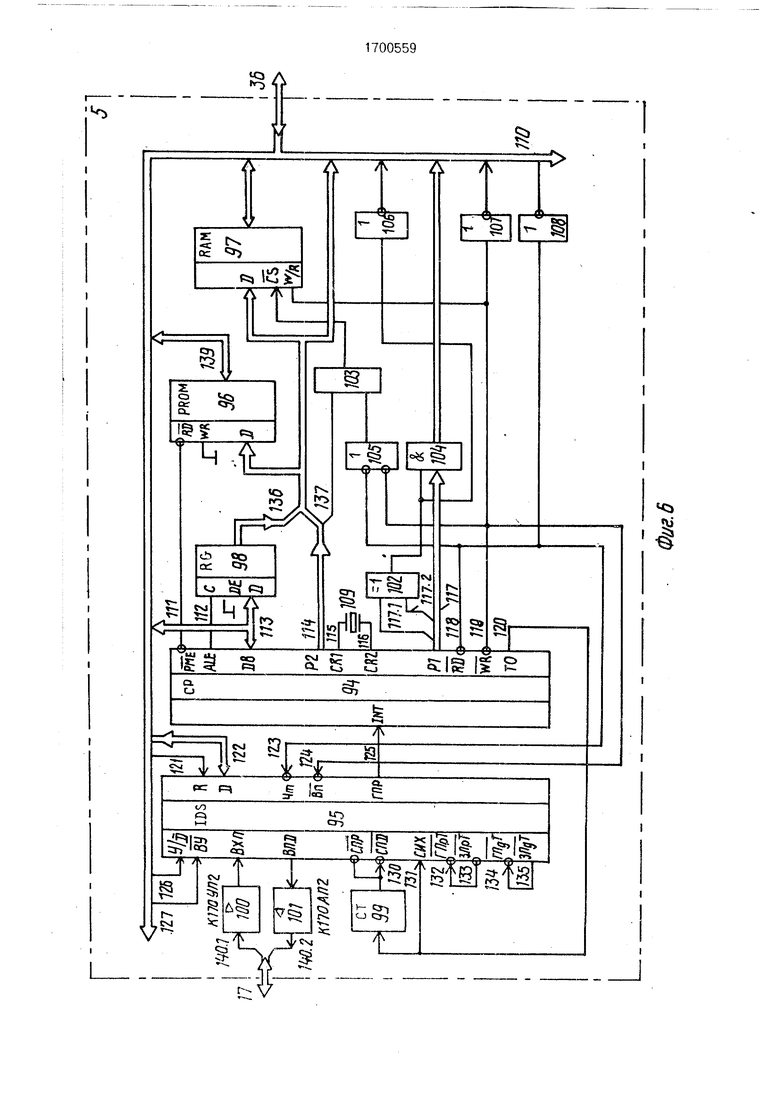

Блок 5 задания режимов эмуляции (фиг. 6) содержит микро-ЭВМ 94, программируе0 мое устройство 95 ввода-вывода последовательной информации, ППЗУ 96, ОЗУ 97, регистр 98, счетчик 99, первый 100 и второй 101 магистральные элементы, элементы 102 ИСКЛЮЩАЮЩЕЕ ИЛИ, первый 103 и вто5 рой 104 элементы И, элемент ИЛИ 105, первый 106, второй 107 и третий 108 элементы НЕ, кварцевый резонатор 109, внутреннюю шину 110, выход 111 разрешения чтения, выход 112 разрешения фиксации адреса,

0 группу 113 входов-выходов данных, первую группу 114 выходов данных, первый 115 и второй 116 выводы для подключения кварцевого резонатора 109, вторую группу 117 выходов данных, первый 117.1 и второй

5 117.2 разряды второй группы 117 выходов микро-ЭВМ 94, выход 118 чтения и выход 119 записи микро-ЭВМ 94, тестируемый вход 120 микро-ЭВМ 94, вход 121 сброса программируемого устройства 95, группу

0 122 входов-выходов данных программируемого устройства 95, вход 123 чтения и вход 124 записи программируемого устройства 95, выход 125 готовности приемника, вход 126 управление/данные и вход 127 выбора

5 устройства программируемого устройства 95, выход 128 первого магистрального элемента 100, вход 129 второго магистрального элемента 101, выход 130 счетчика 99, вход 131 синхронизации, вход 132 и выход 133

0 соответственно готовности и запроса приемника терминала, вход 134 и выход 135 соответственно готовности и запроса пере датчика терминала, группу 136 выходов регистра 98, разряд 137 первой группы 114

5 выходов данных микро-ЭВМ 94, группу 138 информационных входов ОЗУ 97, группу 139 входов-выходов МПЗУ 96, вход 140.1 первого магистрального элемента 100, выход 140.2 второго магистрального элемента

0 101.

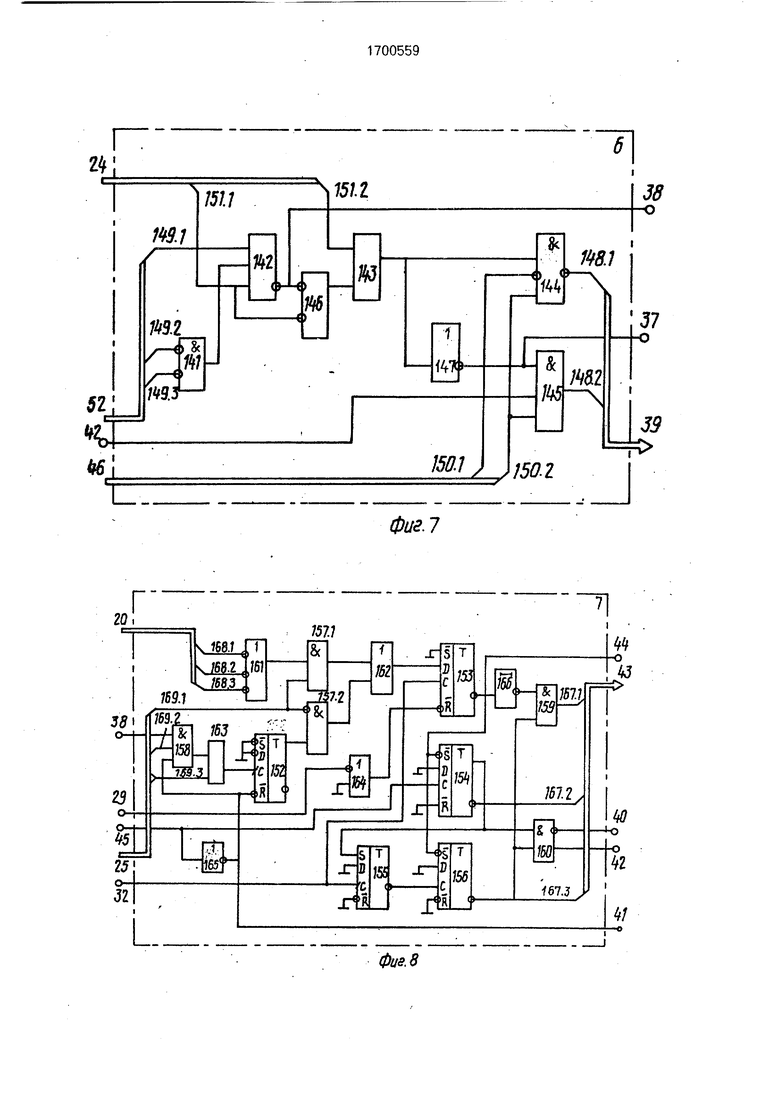

Блок 6 синхронизации обмена (фиг. 7) содержит первый 141, второй 142, третий 143, четвертый 144, пятый 145 элементы И, элементы 146 ИЛИ и 147 НЕ, выход 148.1

5 четвертого элемента И 144, выход 148.2 пятого элемента И 145, первый вход 149.1 второго элемента И 142, первый 149 2 и второй 149.3 входы первого элемента И 141, инверсный 150.1 и первый 150 2 входы четвертого элемента И 144, второй вход 151.1 второго

элемента И 142, первый вход 151.2 третьего элемента И 143.

Блок 7 выбора адреса (фиг. 8) содержит первый 152, второй 153,третий 154, пятый 155, четвертый 156 триггеры, четвертый 157.1, первый 157.2, пятый 158, второй 159, третий 160 элементы И, третий 161, первый 162, второй 163, четвертый 164 элементы ИЛИ, элемент 165 НЕ, элемент 166 задержки, выход 167.1 элемента И 159, инверсный выход 167.2 триггера 154, инверсный выход триггера 156, первый 168.1, второй 168.2, третий 168.3 входы элемента ИЛИ 161, инверсный вход 169.1 элемента И 157.2, первый вход 169.2 элемента И 158, первый вход 169.3 элемента ИЛИ 163.

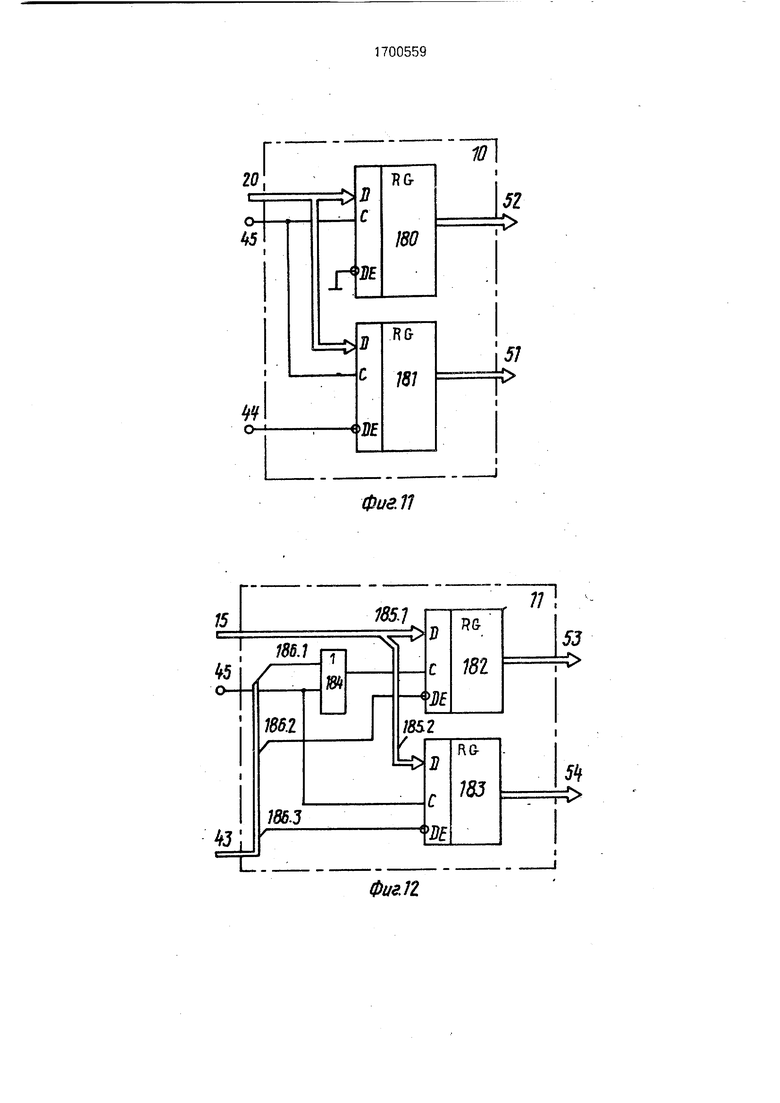

Блок 8 задания режимов обмена (фиг. 9) содержит системный контроллер 170, первый 171.Т и второй 171.2 выходы управления передачей информации системного контроллера 170.

Второй блок 9 регистров адреса (фиг. 10) содержит программируемое устройство 172 ввода-вывода параллельной информации, первый 173 и второй 174 регистры, элемент ИЛИ 175, разряды 176.1 группы выходов первого регистра 173, разряды

176.2группы выходов второго регистра 174, вход 177.1 чтения, вход 177.2 записи, вход

177.3выбора, вход. 177.4 адреса, вход 177,5 адреса программируемого устройства 172 ввода-вывода, группы 178.1 и 178.2 входов второго и третьего каналов программируемого устройства 172 ввода-вывода, группы 179.1 и 179.2 информационных входов пер- вого 173 и второго 174 регистров.

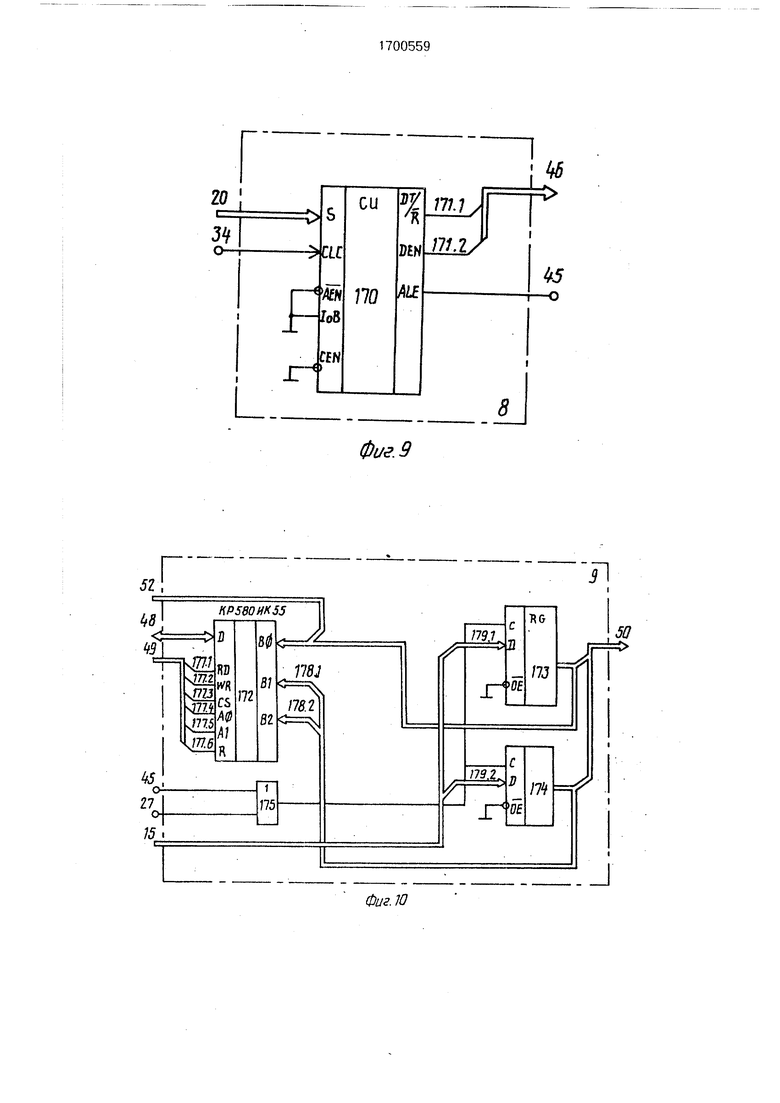

Блок 10 регистров состояния (фиг. 11) содержит регистр 180 и регистр 181.

Первый блок 11 регистров адреса (фиг. 12) содержит первый 182 и второй 183 реги- стры, элемент ИЛИ 184, группу 185.1 информационных входов первого регистра 182, группу 185.2 информационных входов второго регистра 183, первый вход 186.1 элемента ИЛИ 184, управляющий вход 186.2 первого регистра 182, управляющий вход

186.3второго регистра 183.

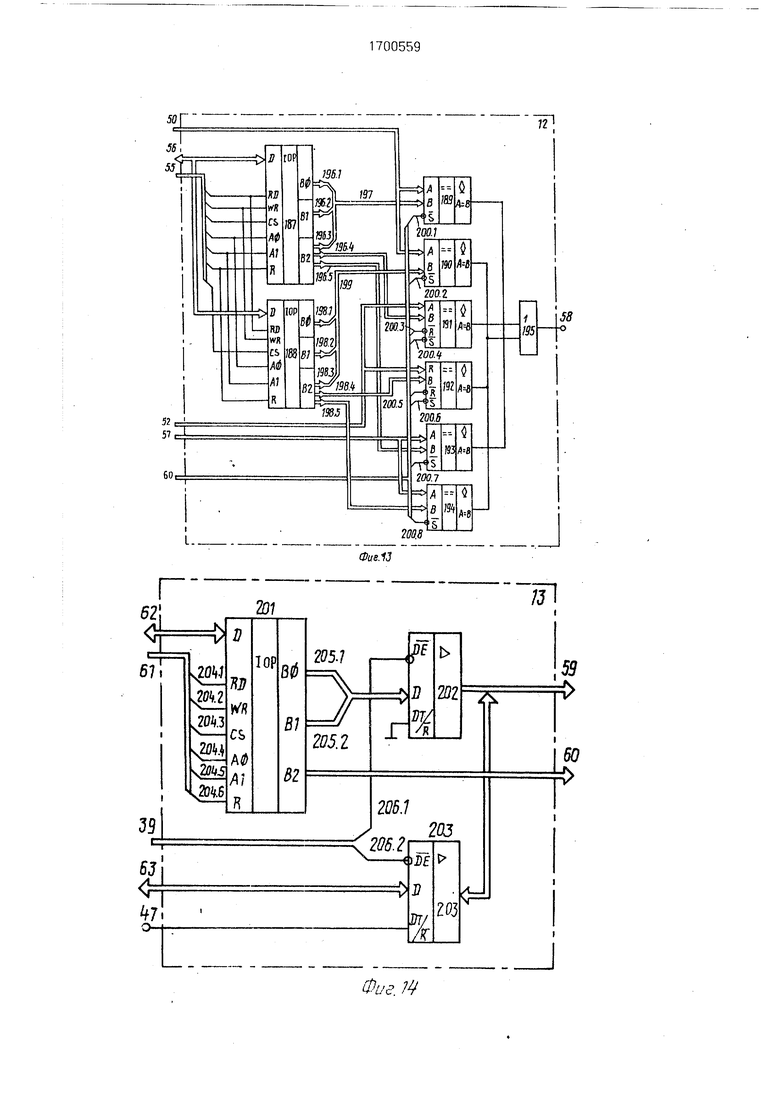

Блок 12 останова (фиг. 13) содержит первое 187 и второе 188 программируемые устройства ввода-вывода параллельной ин- формации, первую 189, третью 190, вторую 191, четвертую 192, шестую 193, пятую 194 схемы сравнения, элемент ИЛИ 195, группы 196.1,196.2 выходов первого, второго, а также группы 196.3 и 196.4 выходов третьего канала первого программируемого устрой- ства 187, группу 197(8) входов схемы 189 сравнения, группы 198.1, 198,2 выходов первого, второго, а также группы 198.3 и

198.4выходов третьего канала второго программируемого устройства 188 ввода-вывода, группу 199(В) входов схемы 190 сравнения, первый 200.1, второй 200.2 третий 200.3, четвертый 200.4, пятый 200.5, шестой 200.5, седьмой 200.7, восьмой 200.8 разряды группы 60 входов блока 12 останова.

Блок 13 коммутации данных (фиг. 14) содержит программируемое устройство 201 ввода-вывода параллельной информации, первый 202 и второй 203 блоки магистральных элементов, вход 204.1 чтения, вход 204.2 записи, вход 204.3 выбора, вход 204.4 .адреса, вход 204.5 адреса, вход 204.6 начальной установки, группы 205.1 и 205,2 выходов первого и второго каналов программируемого устройства 201, входы 206.1 и 206.2 разрешения первого 202 и второго 203 блоков магистральных элементов.

Процессор 1 (фиг. 2) предназначен для выполнения программ отлаживаемого микропроцессорного комплекса, различных сервисных программ, транслируемых в систему отладки от инструментального комплекса через группу 17 входов-выходов.

Блок 65 может быть реализован на основе известного микропроцессора К1810 ВМ86. Системы кодов входов-выходов блока 65 по назначению и алгоритмам функционирования полностью идентичны известному микропроцессору. Входы-выходы имеют следующее назначение: группа 33 входов предназначена для передачи на входы 72.1 (СК), 72.2 (RESET) и 72.3 (READY) блока 65 соответственно сигналов тактовых импульсов, сброса и готовности.

Группа 64 входов предназначена для подачи следующих управляющих сигналов с внешней шины 16 данных предлагаемой системы: сигнала TEST-П разрешения завершения команды WAIT на вход 73.1, немаскируемого запроса прерывания NM1- П на вход 73.2, запроса прерывания INTR на вход 73.3 (вход INTR блока 65).

Группа 26 входов предназначена для подачи сигналов ETEST разрешения завершения команды WAIT, формируемой эмулятором, на вход 74.1, немаскируемого запроса прерывания ENMI, формируемого эмулятором, на вход 74.2, блокировки немаскируемого прерывания БЛ.ММ на вход 74.3, а также сигнала ELOCK блокировки альтернативных задатчиков в отлаживаемой системе, формируемого эмулятором.

Вход 40 предназначен для подачи сигнала СТМА, стробирующего выдачу на шину 16 младшей части адреса или сигнала СТСА, стробирующего выдачу на шину 16 старшей части адреса.

Группа 19 входов-выходов предназначена для обмена сигналами запроса предоставления высшего PjЈf(GTO) по входу-выходу 19.1 и низшего P0(GT1)no входу выходу 19 2 приоритета.

Группа 18 выходов блока 1 предназначена для выдачи сигналов (QS0 и QSI) о состоянии очереди команд с выходов 71.1 и 71.2, сигнала L ОСК-П блокировки альтернативных задатчиков с выхода 71.3 и исполнительного сигнала Р-П чтения данных с выхода 71.4.

Группа 15 входов-выходов предназначена для обмена мультиплексированными сигналами А/Д адреса/данных и A/ST адреса/слова состояния.

Группа 20 выходов предназначена для выдачи сигналов кода состяния /S0, SI, S2/ микропроцессора, характеризующего его текущий цикл работы и определяющего способ использования шины.

Кроме того, входы TEST, NM1, MN/MX блока 65 предназначены соответственно для подачи сигналов окончания режима ожидания, запроса немаскируемого прерывания и установки режима. Подключение входа MN/MX к шине отрицательного потенциала источника питания соответствует заданию максимального режима функцио- нирования блока 65. Выходы LOCK и RD блока 65 предназначены соответственно для выдачи сигналов блокировки и управления чтением.

Блок 2 коммутации управляющих сигналов (фиг. 3) предназначен для управления обменом управляющими сигналами через шину 14 между блоком 5 задания режимов эмуляции (фиг. 1) и другими узлами системы. Блок 75 может быть реализован, например, на основе известной микросхемы КР580 ИК55.

Здесь и далее при описании портов предполагается, что логика их сигналов прямая, а назначение сигналов для каждого порта приводится в порядке возрастания значности разряда порта, начиная с нулевого.

Группа 21 входов-выходов блока 2 предназначена для обмена сигналами данных с соответствующими разрядами шины 14. Группа 22 входов предназначена для передачи с соответствующих разрядов шины 14 сигналов управления чтением на вход 76.1 (RD) блок 75, управления записью на вход 76.2 (WR), управления выбором блока на вход 76.3 (CS), кода выбора одного из трех портов или регистра управляющего слова на входы 76.4 и 76 5 (А0, А1), а также сигнала сброса на вход 76 6 (R) блока 75.

Группа 23 выходов порта В0 предназначена для передачи сигнала Пуск запуска цикла обмена данными блока 1 с устройствами отлаживаемой системы на вход 169.3

блока 7 (фиг. 8), сигнала ПРД разрешения продолжения цикла обмена после останова по условиям или безусловного останова на вход 86.1 блока 3 (фиг, 4), сигнала БЛ.ГОТ. блокировки готовности блока 1 на вход 86.2

0 блока 3 (фиг. 4), сигнала АВТ настройки на выполнение программы отлаживаемой системы в реальном масштабе времени на вход 169.1 блока 7 (фиг. 8), сигнала ЭМУЛ блокировки обмена данными между блоком 1

5 (фиг, 1) и устройствами отлаживаемой системы и разрешения приема данных с выходов 205.1 и 205.2 блока 201 (фиг. 14), сигнала ЦКЛ настройки системы на циклическое выполнение команды (обмена данными с пор0 том ввода-вывода или ячейкой памяти отлаживаемой системы), принимаемой с выходов 205.1 и 205.2 портов В0 и В1 блока 201 и поступающей на входы 151.1 блока 6 (фиг. 7) и 169.2 блока 7 (фиг, 8).

5Группа 30 входов порта В2 блока 75

предназначена для приема сигналов СГ0, СП и СГ2 состояния с выходов 85.1, 85,2 и 85.3 блока 3 (фиг. А. При этом, нулевое значение кода этих сигналов соответствует ап0 паратному останову блока 1 (фиг. 2).

Группа 26 выходов порта В1 блока 75 предназначена для выдачи сигнала ETEST разрешения завершения команды WAIT (формируемого блоком 5 задания режимов

5 эмуляции) на вход 74.1 блока 1 (фиг. 2), сигнала ENM1 немаскируемого запроса прерывания (формируемого блоком 5) на вход 74.2 блока 1, сигнала БЛ.ЫМ I блокировки немаскируемого прерывания на вход 74.3 блока

0 1, сигнала ELOCK блокировки альтернативных задатчиков в отлаживаемой системе на вход 74.4 блока 1, а также сигнала СТРОБ на вход 27 блока 9 (фиг. 10) разрешения выдачи на входы портов В0, В1 и В2 блока 172

5 состояния мультиплексированного адреса/данных, адреса/слова состояния блока 1 шины 15 в такте TW работы микропроцессора КР1810ВМ6(блок 1).

Блок 3 окончания цикла обмена (фиг. 4)

0 предназначен для формирования сигнала окончания цикла обмена через внешнюю шину 16 данных (фиг. 1).

Триггер 78 (фиг. 4) предназначен для формирования на выходе 28 сигнала синх5 ронизации состояния готовности в блоке 4 (фиг. 5). Триггер 79 формирует сигнал состояния СГ2 на выходе 85.3, а также нулевым выходом управляет выдачей сигнала КЦО через элемент И 80 на выходе 29. Триггер 77 предназначен для запоминания сигнала

ОСТ останова, поступающего на вход 58 блока 3 с одноименного выхода блока 12 останова (фиг. 1).

Вход 16 блока 3 предназначен для подачи с соответствующего разряда шины 16 сигнала READY-П готовности, разрешающего завершения цикла обмена, вход 37 - для подачи сигнала ЭТОТ готовности блока 1 (фиг. 1), формируемого системой при обмене данными между блоком 1 и портами В0и В1 блока 201 (фиг. 14), вход 45 - для подачи сигнала СФА строба фиксации адреса, вход 31 -для подачи сигналов READY готовности на вход 31.3, а также сигналов состояния блока 4 на входы 31.2 и 31.1.

Блок 4 синхронизации процессора (фиг.

5)предназначен для формирования известных сигналов READY готовности, СК тактовых импульсов и RESET сброса для синхронизации микропроцессора типа К1810ВМ86, а также управления работой блока 3 (фиг. 4), Триггеры 87 и 88 предназначены для формирования соответственно сигналов готовности READY1 и сброса

.

Блок 41 предназначен для подачи сигнала стробирования фиксации адреса СФА, входы 93.1 и 93.2 - для подачи с интерфейсной шины 16 соответственно сигналов тактовой частоты CLC-П и сброса начального пуска микропроцессора RESET-П.

Выходы 92.1, 92.2, 92.3 и 92.4 блока 4 предназначены для выдачи сигналов готовности READY управления блоком 3 и сброса RESET, которые поступают соответственно на входы 72.3 блока 65 (фиг. 2)31.2. блока 3) (фиг.4) 31.1 блока 3 (фиг.4),31,2 блока 3 (фиг. 4), 72.1 блока 65 (фиг. 2), 72.2 блока 65 (фиг. 2).

Блок 5 задания режимов эмуляции (фиг.

6)предназначен для осуществления приема по интерфейсу ИРПС от инструментального комплекса отладки через группу 17 входов- выходов системы (фиг. 1) управляющих слов, передачи сигналов управления работой предлагаемой системы в заданном режиме, сбора информации о состоянии микропро- цессора и передачи этой информации по интерфейсу ИРПС в инструментальный комплекс.

Блок 5 может быть выполнен, например, на основе известной однокристальной микро-ЭВМ (ОМ ЭВМ)типа КР1816ВЕ35, которая представлена блоком 94, алгоритмы функционирования и режимы использова- ния блока 94 полностью идентичны известным.

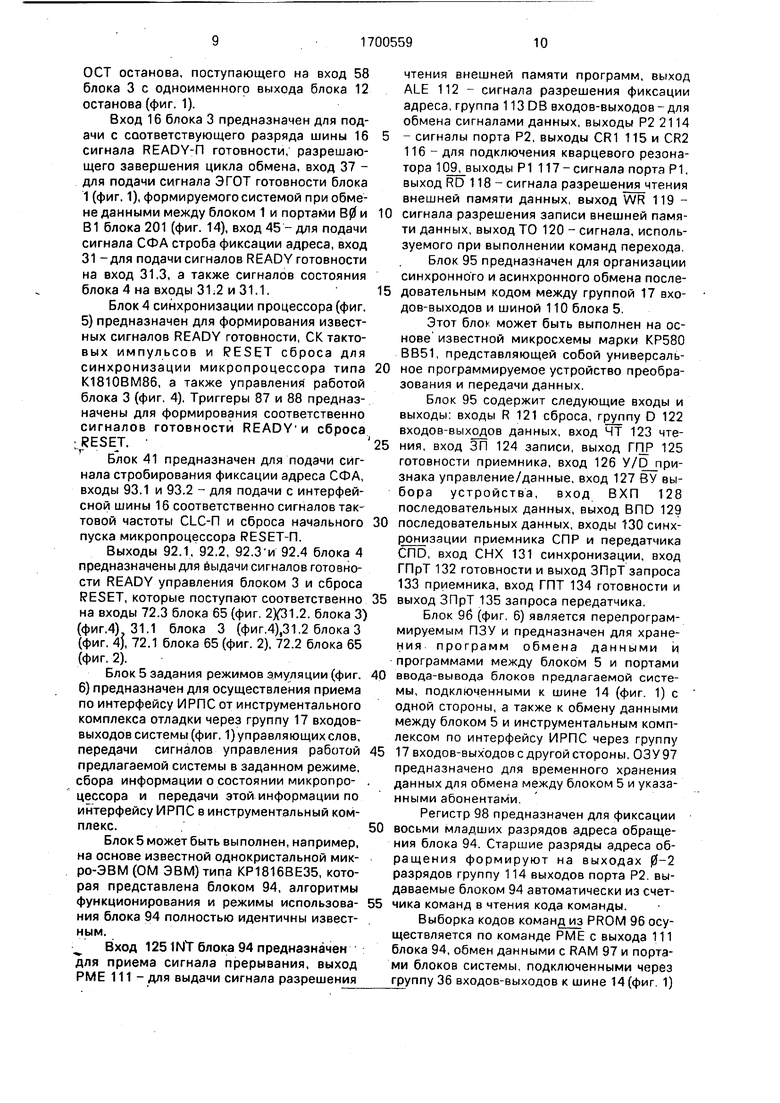

Вход 125 INt блока 94 предназначен для приема сигнала прерывания, выход РМЕ 111 - для выдачи сигнала разрешения

чтения внешней памяти программ, выход ALE 112 - сигнала разрешения фиксации адреса, группа 113 DB входов-выходов-для обмена сигналами данных, выходы Р2 2114 - сигналы порта Р2, выходы CR1 115 и CR2 116 - для подключения кварцевого резонатора 109. выходы Р1 117 - сигнала порта Р1, выход RD 118 - сигнала разрешения чтения внешней памяти данных, выход WR 119 - сигнала разрешения записи внешней памяти данных, выход ТО 120 - сигнала, используемого при выполнении команд перехода

Блок 95 предназначен для организации синхронного и асинхронного обмена последовательным кодом между группой 17 входов-выходов и шиной 110 блока 5,

Этот блок может быть выполнен на основе известной микросхемы марки КР580 ВВ51, представляющей собой универсальное программируемое устройство преобразования и передачи данных.

Блок 95 содержит следующие входы и выходы- входы R 121 сброса, группу D 122 входов-выходов данных, вход ЧТ 123 чтения, вход ЗП 124 записи, выход ГПР 125 готовности приемника, вход 126 У/D при- знака управление/данные, вход 127 ВУ выбора устройства, вход ВХП 128 последовательных данных, выход ВПО 129 последовательных данных, входы t30 синх- рониззции приемника СПР и передатчика СПО, вход СНХ 131 синхронизации, вход ГПрТ 132 готовности и выход ЗПрТ запроса 133 приемника, вход ГПТ 134 готовности и выход ЗПрТ 135 запроса передатчика.

Блок 96 (фиг. 6) является перелрограм- мируемым ПЗУ и предназначен для хранения программ обмена данными и программами между блоком 5 и портами ввода-вывода блоков предлагаемой системы, подключенными к шине 14 (фиг. 1) с одной стороны, а также к обмену данными между блоком 5 и инструментальным комплексом по интерфейсу ИРПС через группу 17 входов-выходов с другой стороны. ОЗУ 97 предназначено для временного хранения данных для обмена между блоком 5 и указанными абонентами

Регистр 98 предназначен для фиксации восьми младших разрядов адреса обращения блока 94. Старшие разряды адреса обращения формируют на выходах 0-2 разрядов группу 114 выходов порта Р2 выдаваемые блоком 94 автоматически из счетчика команд в чтения кода команды.

Выборка кодов команд из PROM 96 осуществляется по команде РМЕ с выхода 111 блока 94, обмен данными с RAM 97 и портами блоков системы, подключенными через группу 36 входов-выходов к шине 14 (фиг 1)

- по сигналам чтения и записи с выходов 118 и 119 блока 94 соответственно.

В качестве старших разрядов адреса блока 97 RAM используются сигналы 2-6 разрядов порта Р2, поступающие с выходов 114 блока 94. Седьмой разряд порта Р2 (выход 137) используется для выборки блока 97. Разряды порта Р2 24-27 устанавливаются программно. Сигналы с выходов разрядов 10-15 порта Р1 через блок 104 элементов И, шину 110 и группу 36 входов-выходов используются для адресации как внутренних элементов блока 5 (фиг. 6), так и элементов, подключенных к шине 14 обмена системы. С момента включения питания системы и до установки на выходах 117.1 и 117.2 разрядов 17-16 порта Р1 кода 10 элементом НЕ 106 фиксируется сигнал СБРОС, который через соответствующий разряд шин 14 поступает на входы 76.6 блока 2 (фиг. 3), 55.6 блока 12 (фиг. 13), 204.6 блока 13 (фиг. 14), 177.6 блока 9 (фиг. 10),

Выход управления записью элемента НЕ 107 соединен через шину 14 с входами 76.2 блока 2 (фиг. 3), 177 2 блока 9 (фиг. 10). Выход управления чтелием элемента НЕ 108 соединен через шину 14 с входами 76.1 блока 2 (фиг. 3), 177,1 блока 9 (фиг. 10), 55.1 блока 12 (фиг. 13), 204.1 блока 13 (фиг. 14).

Кроме того, сигналами с соответствующих адресных разрядов шины 110 через шину 14 и входы 76.4, 76.5 и 76.6 блока 2 (фиг. 3), 177.4, 177.5 и 177.3 блока 172 (фиг. 20), 55.3, 55.4 и 55.5 блока 12 (фиг. 13), 204.4, 204.5 и 204.3 блока 13 (фиг. 14) осуществляется управление указанными блоками по входам А0, А1 (обращение к порту или регистру управляющего слова) и CS (разрешение работы блока) в соответствии с известным для схемы КР580ВВ55 алгоритмом.

Блок 99 является генератором синхронизации приемника и передатчика и осуществляет деление частоты приема-передачи, например, с коэффициентом 1/33 для получения на выходе стандартной частоты интерфейса ИРПС.

Блоки 100 и 101 предназначены для согласования сигналов с входов-выходов 128 и 129 с линией связи 17 Они могут быть реализованы на известных элементах типа К170АП2.

Блок 6 синхронизации обмена (фиг 7) предназначен для управления обменом через блок 13 коммутации данных а также формирования необходимых для этого управляющих сигналов

Группа 52 входов предназначена для подачи сигналов нулевою SO, первого S1 второго S2 разрядов кода состояния микропроцессора на ПХЭД1-1 - 149 3 и 149 1 (,

соответствующих выходов регистра 180 блока 10 (фиг. 11),

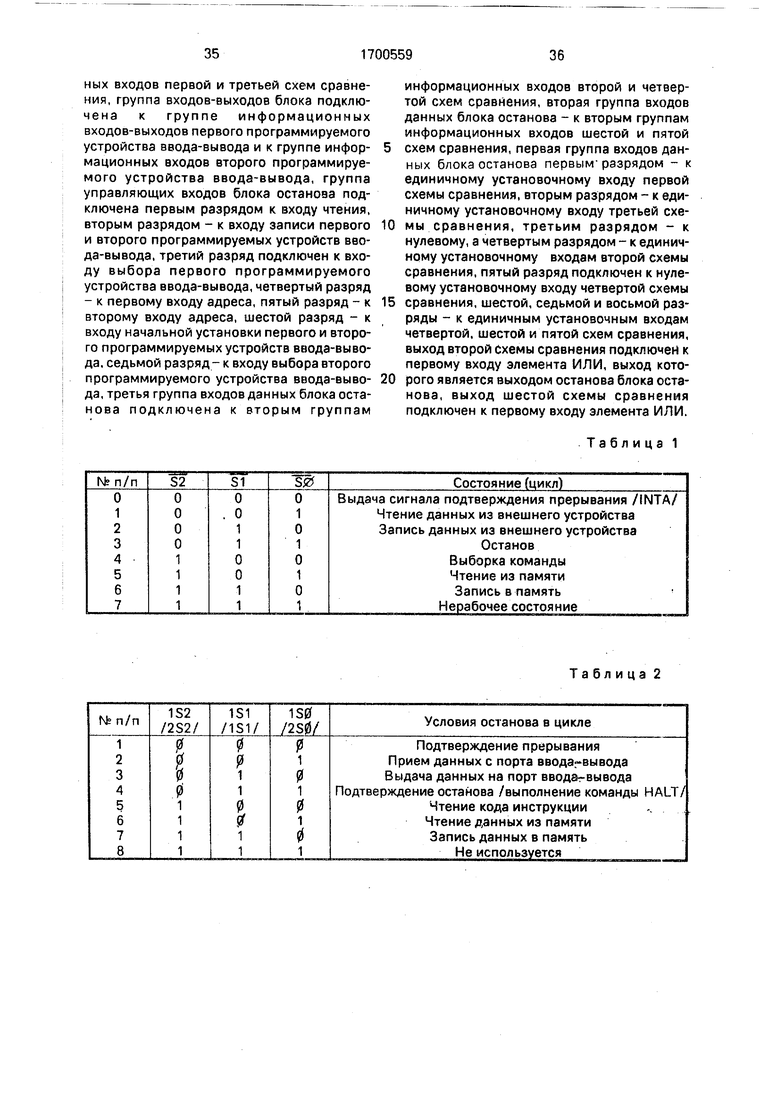

Код состояния микропроцессора характеризует текущий цикл работы в соответст- вии с табл. 1.

На входы 42, 150.1 и 150.2 блока 6 (фиг. 7) поступают сигналы выдачи кода адреса на шину 16 с выхода элемента И 160 блока 7 (фиг.8), признака передачи-приема данных 0 (ДТ/R) с выхода 171.1 контроллера 170 и разрешения передачи данных (DEN) с выхода 171.2 контроллера 170 блока 8 (фиг. 9).

Выход 38 блока 6 (фиг. 7) предназначен для формирования сигнала управления эле- 5 ментом И 158 блока 7 (фиг. 8), выход 37 - для выдачи сигнала готовности блока 1 (фиг. 1), формируемого системой при обмене данными блока 1 с портами В0 и В1 блока 201 (фиг. 14).

0 Группа 39 выходов предназначена для выдачи с выходов 148.1 и 148.2 соответствен но сигналов стробирования приема данных (СТДЭ) блоком 1 из портов В0, В1 блока 201 (фиг. 14) и стробирования обмена дан- 5 ными (СТД) блоком 1 через шину 16 (фиг. 1). Блок 7 выбора адреса (фиг. 8) предназначен для формирования сигналов управления выбором адреса при обмене данными в системе, а также некоторых других сигналов 0 управления обменом,

Триггер 152 предназначен для фикса- ции строба фиксации адреса в циклическом режиме работы системы. Триггеры 153-156 предназначены соответственно для форми- 5 рования на выходе 44 сигнала (СТСС) выдачи на шину 16 (фиг. 1) битов состояния (30-П-52-П) из регистра 181 блока 10 (фиг. 11), определяющего начало цикла обмена по шине 16. для формирования на выходе 167.2 0 сигнала СТСА выдачи на шину 16 старшей части адреса (А16-А19, ВНЕ, где ВНЕ - старший разряд мультиплексированной шины адреса/слова состояния микропроцессора), для формирования сигнала 5 синхронизации установки триггера 156 по С-входу, для формирования на выходе 167,3 сигнала (СТМА) управления выдачей на шину 16 младшей части адреса (А0-А15).

- Группа 20 входов блока 7 предназначе- 0 на для подачи сигнала состояния S0, S1 и S2 микропроцессора 65 блока 1 (фиг. 2) на входы 168.1, 168 2 и 1 68.3 соответственно.

Группа 25 входов предназначена для подачи на входы 169.1, 169.2 и 169.3 сигна- 5 лов АВТ, ЦКЛ и ПУСК соответственно с выходов одноименных разрядов порта В0 блока 75 (фиг. 3), как описано выше.

Входы 29, 45 и 32 предназначены для подачи сигналов окончания цикла обмена КЦО, строба фиксации адреса, СФА и тактовых импульсов соответственно, которые поступают с выходов элементов И 80 блока 3 (фиг. 4), выхода ALE блока 170 (фиг. 9) и выхода 92.3 (32) блока 4 (фиг. 5).

Выход 44 предназначен для выдачи сиг- нала СТСС, выходы 167.1, 167.2 и 167.3 - сигналов СФС строба фиксации слова состояния, СТСА стробирования выдачи на шину 16 (фиг. 1) старшей части адреса (А16- А19, ВНЕ), СТМА стробирования выдачи на шину 16 младшей части адреса соответственно, которые поступают на входы DE блока 181 (фиг. 11), 186.1 блока 11 (фиг. 12), 186.2 (DE) блока 182 (фиг. 12), 186.3 блока 183 (фиг. 12).

Выходы 40 и 42 блока 7 (фиг. 8) предназначены для выдачи прямого и инверсного сигналов стробирования выдачи на шину 16 (фиг. 1) младшей или старшей частей адреса, которые поступают соответственно на вхо- ды элемента И 67 блока 1 (фиг. 2) и элемента И 145 блока 6 (фиг. 7).

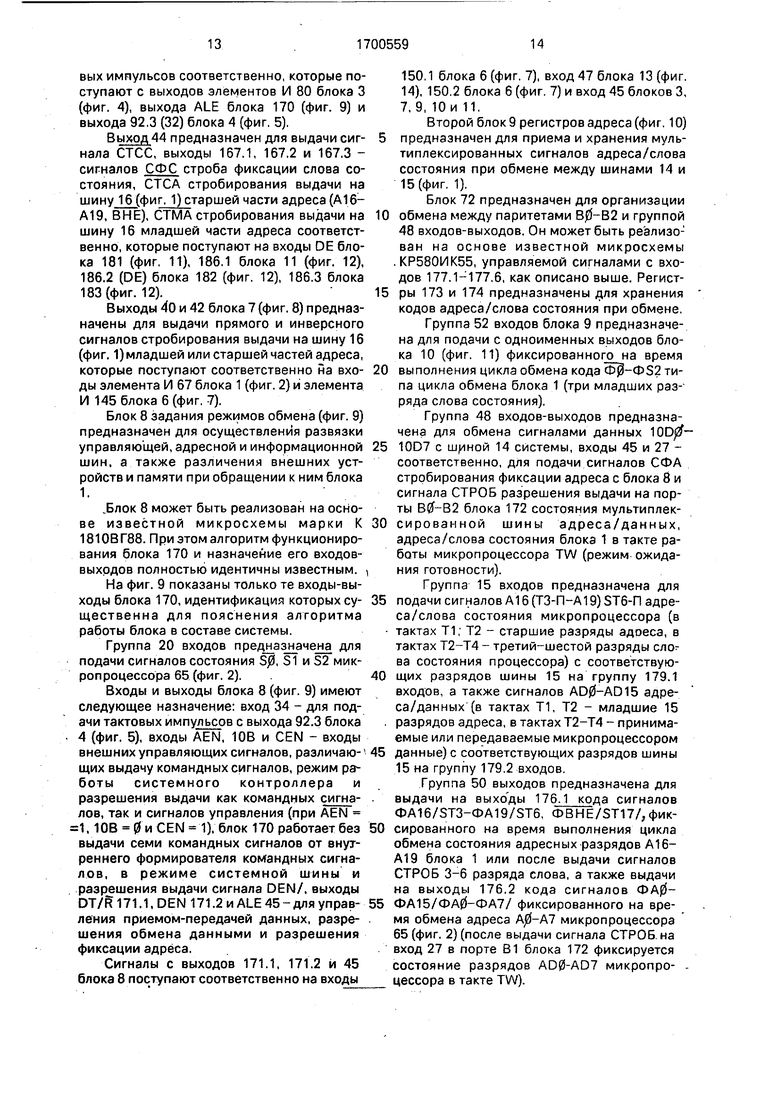

Блок 8 задания режимов обмена (фиг. 9) предназначен для осуществления развязки управляющей, адресной и информационной шин, а также различения внешних устройств и памяти при обращении к ним блока 1.

.Блок 8 может быть реализован на основе известной микросхемы марки К 1810ВГ88. При этом алгоритм функционирования блока 170 и назначение его входов- выходов полностью идентичны известным.

На фиг. 9 показаны только те входы-выходы блока 170, идентификация которых су- щественна для пояснения алгоритма работы блока в составе системы.

Группа 20 входов предназначен для подачи сигналов состояния Sfl, S1 и S2 микропроцессора 65 (фиг. 2).

Входы и выходы блока 8 (фиг. 9) имеют следующее назначение: вход 34 - для подачи тактовых импульсов с выхода 92.3 блока 4 (фиг. 5), входы AEN, 10В и CEN - входы внешних управляющих сигналов, различаю-1 щих выдачу командных сигналов, режим работы системного контроллера и разрешения выдачи как командных сигналов, так и сигналов управления (при AEN 1,10В 0 и CEN 1). блок 170 работает без выдачи семи командных сигналов от внутреннего формирователя командных сигналов, в режиме системной шины и разрешения выдачи сигнала DEN/, выходы ОТ/РМ71.1,ОЕМ171.2иА1.Е45-дляуправ- ления приемом-передачей данных, разрешения обмена данными и разрешения фиксации адреса.

Сигналы с выходов 171.1, 171.2 и 45 блока 8 поступают соответственно на входы

150.1 блока 6 (фиг. 7), вход 47 блока 13 (фиг 14), 150.2 блока 6 (фиг. 7) и вход 45 блоков 3 7,9, Юи 11.

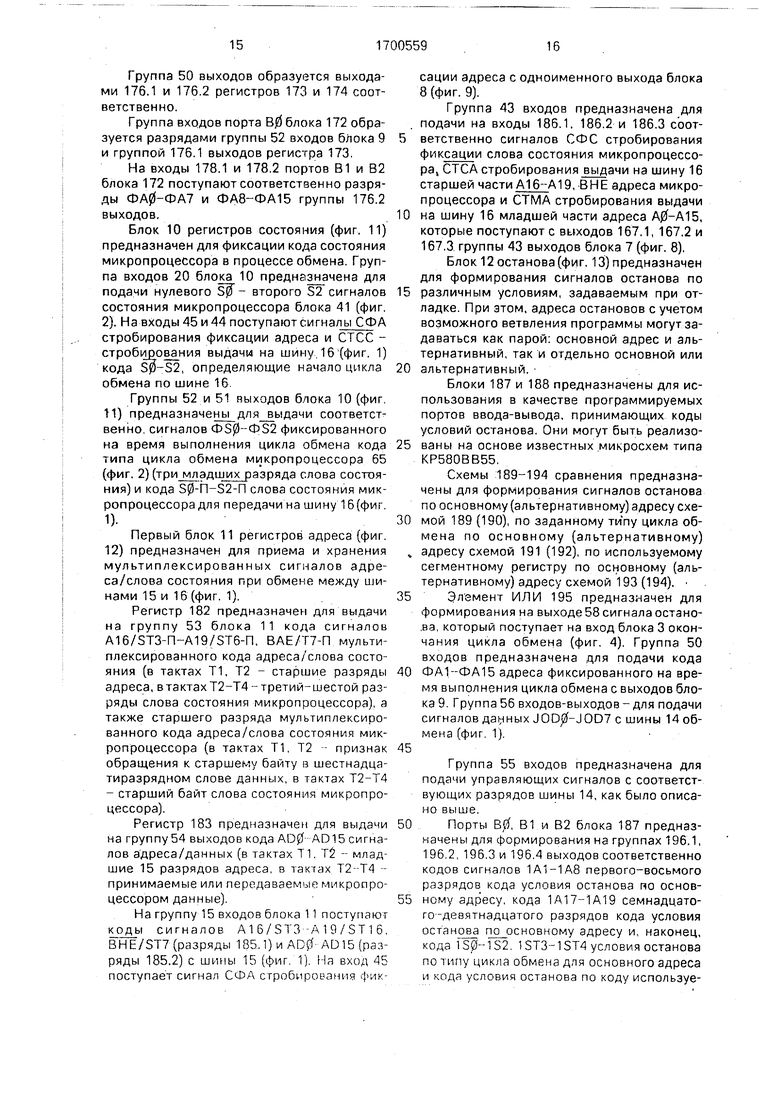

Второй блок 9 регистров адреса (фиг. 10) предназначен для приема и хранения мультиплексированных сигналов адреса/слова состояния при обмене между шинами 14 и 15 (фиг. 1).

Блок 72 предназначен для организации обмена между паритетами В0-В2 и группой 48 входов-выходов. Он может быть ре апизо- ван на основе известной микросхемы .КР580ИК55, управляемой сигналами с входов 177.1-177,6, как описано выше. Регистры 173 и 174 предназначены для хранения кодов адреса/слова состояния при обмене.

Группа 52 входов блока 9 предназначена для подачи с одноименных выходов блока 10 (фиг. 11) фиксированного на время выполнения цикла обмена кода Ф$-Ф52 типа цикла обмена блока 1 (три младших разряда слова состояния).

Группа 48 входов-выходов предназначена для обмена сигналами данных 10D)2f 10D7 с шиной 14 системы, входы 45 и 27 - соответственно, для подачи сигналов СФА стробирования фиксации адреса с блока 8 и сигнала СТРОБ разрешения выдачи на порты В0-В2 блока 172 состояния мультиплексированной шины адреса/данных, адреса/слова состояния блока 1 в такте работы микропроцессора TW (режим ожидания готовности).

Группа 15 входов предназначена для подачи сигналов А16 (ТЗ-П-А19) 5Т6-П адреса/слова состояния микропроцессора (в тактах Т1, Т2 - старшие разряды адоеса, в тактах Т2-Т4 - третий-шестой разряды слова состояния процессора) с соответствующих разрядов шины 15 на группу 179.1 входов, а также сигналов AD0-AD15 адреса/данных (в тактах Т1, Т2 - младшие 15 разрядов адреса, в тактах Т2-Т4 - принимаемые или передаваемые микропроцессором данные) с соответствующих разрядов шины 15 на группу 179.2 входов.

Группа 50 выходов предназначена для выдачи на выходы 176.1 кода сигналов ФА16/5ТЗ-ФА19/5Т6, ФВНЕ/5Т17/,фиксированного на время выполнения цикла обмена состояния адресных разрядов А16- А19 блока 1 или после выдачи сигналов СТРОБ 3-6 разряда слова, а также выдачи на выходы 176.2 кода сигналов ФА0- ФА15/ФА0-ФА7/ фиксированного на время обмена адреса Aj#-A7 микропроцессора 65 (фиг. 2) (после выдачи сигнала СТРОБ на вход 27 в порте 81 блока 172 фиксируется состояние разрядов AD0-AD7 микропро- цессора в такте TW).

Группа 50 выходов образуется выходами 176.1 и 176.2 регистров 173 и 174 соответственно.

Группа входов порта В0 блока 172 образуется разрядами группы 52 входов блока 9 и группой 176.1 выходов регистра 173.

На входы 178.1 и 178.2 портов В1 и В2 блока 172 поступают соответственно разряды ФА0-ФА7 и ФА8-ФА15 группы 176.2 выходов.

Блок 10 регистров состояния (фиг. 11) предназначен для фиксации кода состояния микропроцессора в процессе обмена. Группа входов 20 блока 10 предназначена для подачи нулевого второго S2 сигналов состояния микропроцессора блока 41 (фиг. 2). На входы 45 и 44 поступают сигналы СФА стробирования фиксации адреса и СТСС - стробирования выдачи на шину 16 (фиг. 1) кода S0-S2, определяющие начало цикла обмена по шине 16

Группы 52 и 51 выходов блока 10 (фиг

11)предназначены для выдачи соответственно сигналов Ф30-Ф52 фиксированного на время выполнения цикла обмена кода типа цикла обмена микропроцессора 65 (фиг. 2) (три младших разряда слова состояния) и кода 50-П-52-П слова состояния микропроцессора для передачи на шину 16(фиг

1).

Первый блок 11 регистров адреса (фиг.

12)предназначен для приема и хранения мультиплексированных сигналов адреса/слова состояния при обмене между шинами 15 и 16 (фиг. 1).

Регистр 182 предназначен для выдачи на группу 53 блока 11 кода сигналов А16/5ТЗ-П-А19/5Тб-П, ВАЕ/Т7-П мультиплексированного кода адреса/слова состояния (в тактах Т1, Т2 - старшие разряды адреса, втактахТ2-Т4-третий-шестой разряды слова состояния микропроцессора), а также старшего разряда мультиплексированного кода адреса/слова состояния микропроцессора (в тактах Т1, Т2 признак обращения к старшему байту в шестнадцатиразрядном слове данных, в тактах Т2-Т4 - старший байт слова состояния микропроцессора).

Регистр 183 предназначен для выдачи на группу 54 выходов кода AD0 AD15 сигналов адреса/данных (в тактах Т1. Т2 - младшие 15 разрядов адреса, в тактах Т2 Т4 принимаемые или передаваемые микропроцессором данные)

На группу 15 входов блока 11 поступают коды сигналов A16/S13 A19/ST16, ВRE/ST7 (разряды 185.1)иА00 AD15 (разряды 185.2) с шины 15 (фиг 1) На вход 45 поступает сигнал СФА сгробирования фик

сации адреса с одноименного выхода блока 8 (фиг. 9).

Группа 43 входов предназначена для подачи на входы 186.1, 186.2 и 186.3 соответственно сигналов СФС стробирования фиксации слова состояния микропроцессо- pas CTCA стробирования выдачи на шину 16 старшей части А16-А19, ВНЕ адреса микропроцессора и СТМА стробирования выдачи

0 на шину 16 младшей части адреса А0-А15, которые поступают с выходов 167.1, 167.2 и 167.3 группы 43 выходов блока 7 (фиг. 8).

Блок 12 останова (фиг. 13) предназначен для формирования сигналов останова по

5 различным условиям, задаваемым при отладке. При этом, адреса остановов с учетом возможного ветвления программы могут задаваться как парой: основной адрес и альтернативный, так и отдельно основной или

0 альтернативный.

Блоки 187 и 188 предназначены для использования в качестве программируемых портов ввода-вывода, принимающих коды условий останова. Они могут быть реализо5 ваны на основе известных микросхем типа КР580ВВ55.

Схемы 189-194 сравнения предназначены для формирования сигналов останова по основному (альтернативному) адресу схе0 мой 189 (190), по заданному типу цикла обмена по основному (альтернативному) „ адресу схемой 191 (192), по используемому сегментному регистру по основному (альтернативному) адресу схемой 193 (194).

5Элемент ИЛИ 195 предназначен для

формирования на выходе 58 сигнала останова, который поступает на вход блока 3 окончания цикла обмена (фиг. 4). Группа 50 входов предназначена для подачи кода

0 ФА1-ФА15 адреса фиксированного на время выполнения цикла обмена с выходов блока 9 Группа 56 входов-выходов - для подачи сигналов данных JOD -JOD7 с шины 14 обмена (фиг 1)

5

Группа 55 входов предназначена для подачи управляющих сигналов с соответствующих разрядов шины 14, как было описано выше.

0Порты В0, В1 и В2 блока 187 предназначены для формирования на группах 196.1, 196 2, 196.3 и 196.4 выходов соответственно кодов сигналов 1А1-1А8 первого-восьмого разрядов кода условия останова по основ5 ному адресу, кода 1А17-1А19 семнадцатого-девятнадцатого разрядов кода условия остано ва по основному адресу и, наконец, кода fS0-1S2 1ST3-1ST4 условия останова по типу цикла обмена для основного адреса и кода условия останова по коду используемого сегментного регистра для основного адреса.

Порты В0, В1 и В2 блока 188 предназначены для формирования на группах 198.1, 198.2, 198.3 и 198.4 выходов соответственно 5 кодов 2А1-2А8 первого-восьмого разрядов кода условия останова по альтернативному адресу, кода 2А9-2А16 девятого-шестнад- цатого разрядов кода условия останова по альтернативному адресу, кода 2А17-2А19 10 семнадцатого-девятнадцатого разрядов кода условия останова по альтернативному адресу, кода 2S$-2S2, 2ST3-2ST4 условия останова по типу цикла обмена по альтернативному адресу и условия останова по коду 15 используемого сегментного регистра при останове по альтернативному адресу.

Группа 52 входов блока 12 предназна- чена для подачи кода Ф50-Ф52 типа цикла обмена фиксированного на время выполне- 20 ния цикла обмена, группа 57 входов - для подачи кода A16/ST3-A17/ST4 шестнадцатого разряда адреса (третьего разряда слова состояния и семнадцатого разряда адреса) четвертого разряда слова состояния 25 с шины 15 (фиг. 1).

Группа 60 входов блока 12 предназначена для подачи управляющих сигналов условий останова У01-У08 на входы 200.1-200.8 блока 12 следующим образом: 30 вход 200.1 при У01 1/У01 0/ включает (исключает) адреса в условия останова по основному адресу; вход 200.2 при У02 1 /У02 0/ включает (исключает) адреса А1- А19 в условия останова по альтернативному 35 адресу; вход 200.3 при У07 1 /У07 0/ разрешает (запрещает) останов по условиям основного адреса; вход 200.4 при УОЗ 1/УОЗ 0/ включает (исключает) в условия останова пр основному адресу тип цикла 40 обмена /S0-S2/; вход 200.5 при У04 1 /У04 $/ включает (исключает) в условиях останова по альтернативному адресу тот цикл обмена /S0-S2/; вход 200.6 при У08 1 /У08 0/ разрешает (запрещает) останов 45 по условиям альтернативного адреса; вход 200.7 при У05 1 /У05 0/ включает (исключает) в условиях останова по основному адресу код используемого сегментного регистра (ST3, ST4); вход 200.8 при У06 1 50 /У06 0/ включает (исключает) в условиях останова по альтернативному адресу код используемого сегментного регистра (ST3, ST4).

Присутствие кода С016 на группе 60 входов инициирует безусловный останбв в каждом цикле обмена..

Формирование условий останова по типу цикла обмена в зависимости от сигналов

5 10 15

20 25

0 5 0 5 0

5

на выходах 196.4 (198.4) осуществляется в соответствии с табл.2.

Формирование условий останова по типу используемого сегментного регистра(CS. DS, SS, ES ) в зависимости от значений сигналов на выходах 196.5 (198.5) осуществляется в соответствии с табл. 3.

Схемы 189-194 срабатывают при совпадении условий останова. При этом на выходе блоков 189-194 формируется сигнал Лог. 1. Поскольку выходы блоков 189-194 объединены по монтажному ИЛИ, то сиг- .нал останова может быть сформирован только при наличии сигналов Лог. 1 на выходе схем сравнения, обслуживающих все типы остановов.

Для исключения возможности формирования какого-либо сигнала останова достаточно установить выход соответствующего блока в состояние Лог. 1. Принудительная установка в О любого из блоков, входящих в соответствующую группу (189, 191,193 или 190, 192, 194), приводит к тому, что соответствующая группа командоаппаратов не будет формировать сигнал останова. Установка в 1 всех блоков сравнения группы приводит к безусловному останову в каждом цикле обмена.

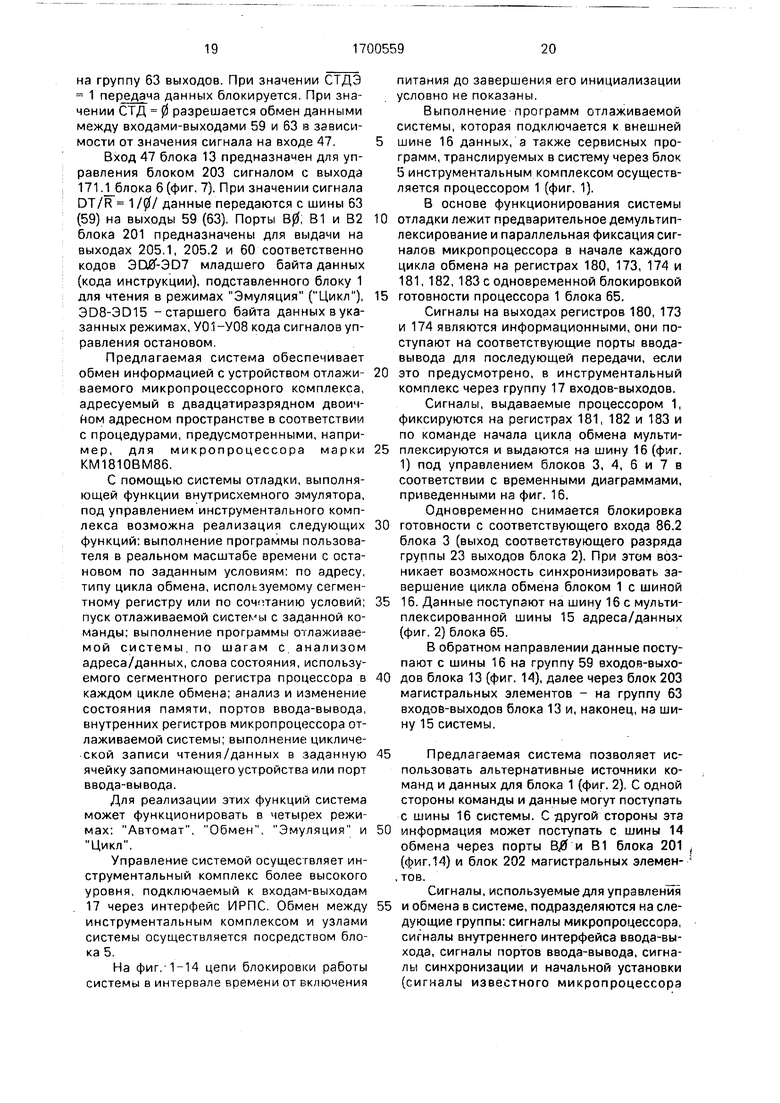

Блок 13 коммутации данных (фиг. 14) предназначен для коммутации потоков данных при обмене между шинами 15 и 16 (фиг. 1). Блок 201 является программируемым портом ввода-вывода, который может быть выполнен на известной микросхеме марки КР580ВВ55. Управление этим блоком по входам 204.1-204.6 осуществляется аналогично тому, как было описано выше. Блоки 202 и 203 являются магистральными эле-г ментами, коммутирующими потоки данных при обмене.

Группа 62 входов-выходов предназначена для обмена кодами 1D0-1D7 данных с шиной системы, группа 63 входов-выходов

-для обмена кодами адреса/данных AD0- AD15 (в тактах Т1, Т2 - младшие пятнадцать разрядов адреса, в тактах Т2-Т4 - принимаемые или передаваемые микропроцессором данные) с шиной 15 системы (фиг. 1).

Группа 59 входов-выходов блока 13 (фиг. 14) предназначена для обмена кодами адреса/данных АО0-П-АО15-П с шиной 16 системы, группа 39 входов - для подачи на входы 206.1 и 206.2 соответственно сигналов СТДЭ строба приема данных микропро- цессором с портов В0, В1 , блока 201 и СТД

-строба обмена данными микропроцессора по шинб 16, которые поступают с выходов 148.1 и 148.2 блока 6 (фиг. 7).

При значении сигнала СТДЭ 0 данные передаются с портов В0 и В1 через блок 202

на группу 63 выходов. При значении СТДЭ 1 передача данных блокируется. При значении СТД 0 разрешается обмен данными между входами-выходами 59 и 63 в зависимости от значения сигнала на входе 47.

Вход 47 блока 13 предназначен для управления блоком 203 сигналом с выхода 171 .Нэлока 6 (фиг, 7). При значении сигнала DT/R 1/0/ данные передаются с шины 63 (59) на выходы 59 (63). Порты В0, В1 и В2 блока 201 предназначены для выдачи на выходах 205,1, 205,2 и 60 соответственно кодов ЭОЈС-Э07 младшего байта данных (кода инструкции), подставленного блоку 1 для чтения в режимах Эмуляция (Цикл), Э08-Э015 -старшего байта данных в указанных режимах, У01-У08 кода сигналов управления остановом.

Предлагаемая система обеспечивает обмен информацией с устройством отлаживаемого микропроцессорного комплекса, адресуемый в двадцатиразрядном двоичном адресном пространстве в соответствии с процедурами, предусмотренными, например, для микропроцессора марки КМ1810ВМ86.

С помощью системы отладки, выполняющей функции внутрисхемного эмулятора, под управлением инструментального комплекса возможна реализация следующих функций: выполнение программы пользователя в реальном масштабе времени с остановом по заданным условиям: по адресу, типу цикла обмена, используемому сегментному регистру или по сочетанию условий; пуск отлаживаемой системы с заданной команды; выполнение программы отлаживаемой системы, по шагам с анализом адреса/данных, слова состояния, используемого сегментного регистра процессора в каждом цикле обмена; анализ и изменение состояния памяти, портов ввода-вывода, внутренних регистров микропроцессора отлаживаемой системы; выполнение циклической записи чтения/данных в заданную ячейку запоминающего устройства или порт ввода-вывода.

Для реализации этих функций система может функционировать в четырех режимах: Автомат, Обмен, Эмуляция и Цикл.

Управление системой осуществляет инструментальный комплекс более высокого уровня, подключаемый к входам-выходам 17 через интерфейс ИРПС. Обмен между инструментальным комплексом и узлами системы осуществляется посредством блока 5.

На фиг.-1-14 цепи блокировки работы системы в интервале времени от включения

питания до завершения его инициализации условно не показаны.

Выполнение программ отлаживаемой системы, которая подключается к внешней

шине 16 данных, а также сервисных программ, транслируемых в систему через блок 5 инструментальным комплексом осуществляется процессором 1 (фиг. 1).

В основе функционирования системы

0 отладки лежит предварительное демультиплексирование и параллельная фиксация сигналов микропроцессора в начале каждого цикла обмена на регистрах 180, 173, 174 и 181, 182, 183 с одновременной блокировкой

5 готовности процессора 1 блока 65.

Сигналы на выходах регистров 180, 173 и 174 являются информационными, они поступают на соответствующие порты ввода- вывода для последующей передачи, если

0 это предусмотрено, в инструментальный

комплекс через группу 17 входов-выходов.

Сигналы, выдаваемые процессором 1,

фиксируются на регистрах 181, 182 и 183 и

по команде начала цикла обмена мульти5 плексируются и выдаются на шину 16 (фиг. 1) под управлением блоков 3, 4, 6 и 7 в соответствии с временными диаграммами, приведенными на фиг. 16.

Одновременно снимается блокировка

0 готовности с соответствующего входа 86.2 блока 3 (выход соответствующего разряда группы 23 выходов блока 2). При этом возникает возможность синхронизировать завершение цикла обмена блоком 1 с шиной

5 16. Данные поступают на шину 16с мультиплексированной шины 15 адреса/данных (фиг. 2) блока 65.

В обратном направлении данные поступают с шины 16 на группу 59 входое-выхо0 дов блока 13 (фиг. 14), далее через блок 203 магистральных элементов - на группу 63 входов-выходов блока 13 и, наконец, на шину 15 системы.

5 Предлагаемая система позволяет использовать альтернативные источники команд и данных для блока 1 (фиг. 2). С одной стороны команды и данные могут поступать с шины 16 системы. С другой стороны эта

0 информация может поступать с шины 14 обмена через порты BJ3 и В1 блока 201 ( (фиг.14) и блок 202 магистральных элемен- :

, тов,

Сигналы, используемые для управления

5 и обмена в системе, подразделяются на следующие группы: сигналы микропроцессора, сигналы внутреннего интерфейса ввода-выхода, сигналы портов ввода-вывода, сигналы синхронизации и начальной установки (сигналы известного микропроцессора

КМ1810ВМ86). Для их обозначения признак -П не используется.

В примере конкретного выполнения блоков предлагаемой системы рассматривается случай функционирования микро- процессора КМ1810ВМ86 в максимальном режиме. В этом случае работой микропроцессора управляет контроллер 170 блока 8 (фиг. 9). При этом сигналом перехода к началу цикла обмена контроллера 170 (фиг. 9) является переход кода состояния 1112 в лю: бое другое на группе 20 выходов блока 65 (фиг. 21. Обратный переход кода на выходе 20 в состояние 1112 является сигналом для блока 170 (фиг. 9) к переходу на завершение цикла обмена.

Таким образрм о тех пор, пока код состояния S2, S1. S0 сохраняет значение Л12. система, выполняющая функции процессора отлаживаемой (проектируемой) си- стемы, с точки зрения последней находится в пассивном состоянии. С другой стороны, с точки зрения лежа J (фиг. 1) системы изменения кода S2, S1, S0 блока 1 из состояния 111 в любое другое являются признаком на- чала цикла обмена.

Для обеспечения синхронизации фиксации сигналов S{3-S2, A0-A19, ВНЕ для последующей выдачи их на шину 16 (фиг. 1) или анализа в инструментальном комплек- се, подключаемом к группе 17 входов-выходов, в системе используется блок 170.

В начале цикла обмена блок 170 формирует на выходе ALE 45 (фиг. 9) импульсный сигнал СФА (фиг. 18-21),используемый для фиксации сигналов в регистрах 180 (фиг. 11) и 173 (фиг. 10).

При этом код адреса А0-А15 фиксируется в регистрах 174 (фиг. 10) и 183 (фиг. 12), разряды адреса А16-А19 и сигнал ВНЕ (раз- решение старшего байта на шине) - в регистрах 173 (фиг. 10) и 182 (фиг. 12),

Кроме того, код адреса и слова состояния , коды ФА1-ФА19, Ф52-Ф50 с выходов регистров 173 (фиг. 10), 174 и 180 (фиг. 11) соответственно поступают на блоки сравнения 189-194 блока 12 (фиг. 13). .

Далее выполнение цикла обмена осуществляется под управлением блоков 3 и 4, которые синхронизируют формирование сигнала готовности, а также блоков 6 и 7, которые формируют управляющие сигналы для процесса эмуляции,

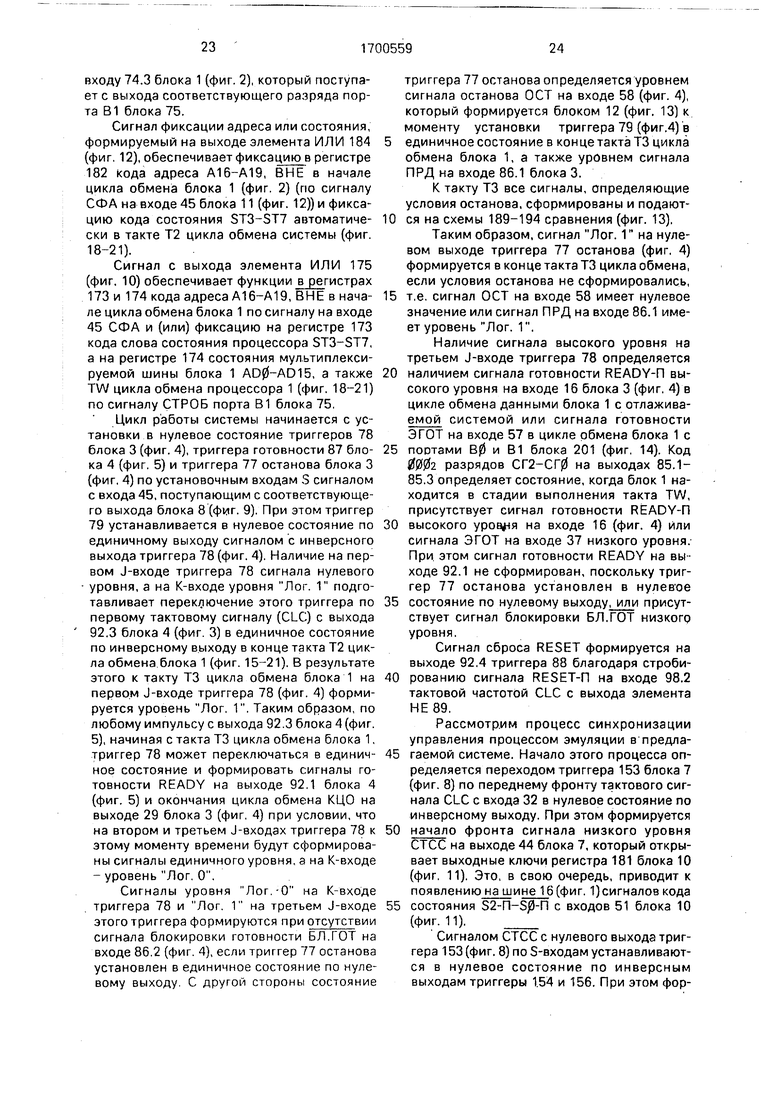

При этом, благодаря соответствующей конструкции указанных блоков, на входы блока 1 (фиг. 1) обеспечивается подача еле- дующих сигналов (фиг. 18-21): сигнала CLC на вход 72.1 в течение всего времени существования сигнала CLC -П на выходе 93.1 блока 4 (фиг.5); синхронная подача сигнала

сброса RESET на вход 72.2 (фиг. 2) при наличии сигнала RESET-П на входе 93.2 блока 4 (фиг. 5), а также в интервале времени от момента включения питания до завершения инициализации системы; синхронная подача сигнала готовности READY на вход 72.3 (фиг.2), согласованная с временной диаграммой (фиг. 18-21) цикла обмена системы при наличии сигналов READY -П или ЭТОТ на входе 16 блока 3 окончания цикла обмена; блокировка сигнала готовности READY на входе 72.3 блока 1 (фиг. 2), выхода 92.1 .блока 4 (фиг. 5) при наличии сигнала блокировки БЛ.ГОТ на входе 86.2 блока 3 (фиг. 4), который через элементы ИЛИ 83, 84 и 82 устанавливает триггер 78 в единичное состояние; блокировка сигнала готовности READY при наличии в такте ТЗ (фиг. 18-21) сигнала (аппаратного останова по условиям или безусловного) ОСТ с выхода 58 блока 12 (фиг. 1); продолжение цикла обмена после аппаратного останова по сигналу управления передачей ПРД на входе 86.1 (фиг. 4), куда он поступает с выхода соответствующего разряда группы 23 выходов блока 2 (фиг. 3).

Блоки 6 и 7 совместно выполняют функцию управления посредством описанных выше сигналов СТДЭ, СТД, США, СТСС. СФС и ЭТОТ завершением цикла обмена данными между блоком 1 (фиг. 1) с отлаживаемой системой через шину 16 либо с инструментальным комплексом через порты В$ и В1 блока 201 (фиг. 14).

Согласование работы блоков 6 и 7 с временной диаграммой работы блока 1 обеспечивается посредством сигналов CLC, КЦО, DEN, DT/R, СФА, Ф50-Ф52 и ПУСК, формируемых соответственно на выходах 92.3 блока 4 (фиг. 5), 29 блока 3 (фиг. 4), 171.2 блока 8 (фиг. 9), 171.1 блока 8 (фиг. 9), 52 блока 10 (фиг. 11), 41 блока 7 (фиг. 8).

Кроме того, особенностями согласования функционирования узлов системы является следующее. Сигнал чтения данных (исполнительный) RD-П с выхода 71.4 блока 1 (фиг. 2) выдается не ранее начала такта Т2 цикла обмена системы (фиг. 18-21). Выдача информационного сигнала блокировки альтернативных задатчиков LOCK -П с выхода 71.3 блока 1 осуществляется по сигналу бло- ка 65 (фиг. 2) LOCK, а также по сигналу ELOCK блокировки альтернативных задзт- чиков в отлаживаемой системе, формируемому системой на входе 74.4 блока 1. Прием блоком 1 (фиг. 2) сигналов TEST и NM1 осу- ществля ется как с шины 16 системы, так и с выходов порта В1 блока 201 (фиг. 14).

Блокировка немаскируемых прерыва- ний осуществляется сигналом БЛ.ЫМ1 по

входу 74.3 блока 1 (фиг. 2), который поступает с выхода соответствующего разряда порта В1 блока 75.

Сигнал фиксации адреса или состояния, формируемый на выходе элемента ИЛИ 184 (фиг. 12), обеспечивает фиксацию в регистре 182 кода адреса А16-А19, ВНЕ в начале цикла обмена блока 1 (фиг. 2) (по сигналу СФА на входе 45 блока 11 (фиг. 12)) и фиксацию кода состояния ST3-ST7 автоматиче- ски в такте Т2 цикла обмена системы (фиг. 18-21).

Сигнал с выхода элемента ИЛИ 175 (фиг. 10) обеспечивает функции в регистрах 173 и 174 кода адреса А16-А19, ВНЕ в нача- ле цикла обмена блока 1 по сигналу на входе 45 СФА и (или) фиксацию на регистре 173 кода слова состояния процессора ST3-ST7, а на регистре 174 состояния мультиплексируемой шины блока 1 AD0-AD15, а также TW цикла обмена процессора 1 (фиг. 18-21) по сигналу СТРОБ порта В1 блока 75.

Цикл работы системы начинается с установки в нулевое состояние триггеров 78 блока 3 (фиг. 4), триггера готовности 87 бло- ка 4 (фиг. 5) и триггера 77 останова блока 3 (фиг. 4) по установочным входам S сигналом с входа 45, поступающим с соответствующего выхода блока 8 (фиг. 9). При этом триггер 79 устанавливается в нулевое состояние по единичному выходу сигналом с инверсного выхода триггера 78 (фиг. 4). Наличие на первом J-входе триггера 78 сигнала нулевого уровня, а на К-входе уровня Лог. 1 подготавливает переключение этого триггера по первому тактовому сигналу (CLC) с выхода 92.3 блока 4 (фиг. 3) в единичное состояние по инверсному выходу в конце такта Т2 цикла обмена блока 1 (фиг. 15-21). В результате этого к такту ТЗ цикла обмена блока 1 на первом J-входе триггера 78 (фиг. 4) формируется уровень Лог, 1. Таким образом, по любому импульсу с выхода 92.3 блока 4 (фиг. 5), начиная с такта ТЗ цикла обмена блока 1, триггер 78 может переключаться в единич- ное состояние и формировать сигналы готовности READY на выходе 92.1 блока 4 (фиг. 5) и окончания цикла обмена КЦО на выходе 29 блока 3 (фиг. 4) при условии, что на втором и третьем J-входах триггера 78 к этому моменту времени будут сформированы сигналы единичного уровня, а на К-входе - уровень Лог. О.

Сигналы уровня Лог.-О на К-входе триггера 78 и Лог. 1 на третьем J-входе этого триггера формируются при отсутствии сигнала блокировки готовности БЛ.ГОТ на входе 86.2 (фиг. 4), если триггер 77 останова установлен в единичное состояние по нулевому выходу С другой стороны состояние

триггера 77 останова определяется уровнем сигнала останова ОСТ на входе 58 (фиг. 4), который формируется блоком 12 (фиг. 13) к моменту установки триггера 79 (фиг.4) в единичное состояние в конце такта ТЗ цикла обмена блока 1, а также уровнем сигнала ПРД на входе 86.1 блока 3.

К такту ТЗ все сигналы, определяющие условия останова, сформированы и подаются на схемы 189-194 сравнения (фиг. 13).

Таким образом, сигнал Лог. 1 на нулевом выходе триггера 77 останова (фиг. 4) формируется в конце такта ТЗ цикла обмена, если условия останова не сформировались, т.е. сигнал ОСТ на входе 58 имеет нулевое значение или сигнал ПРД на входе 86.1 имеет уровень Лог. 1.

Наличие сигнала высокого уровня на третьем J-входе триггера 78 определяется наличием сигнала готовности READY-П высокого уровня на входе 16 блока 3 (фиг, 4) в цикле обмена данными блока 1 с отлаживаемо системой или сигнала готовности ЭТОТ на входе 57 в цикле обмена блока 1 с постами В0 и В1 блока 201 (фиг. 14). Код 0002 разрядов СГ2-СГ0 на выходах 85.1- 85.3 определяет состояние, когда блок 1 находится в стадии выполнения такта TW, присутствует сигнал готовности READY-П высокого уровня на входе 16 (фиг. 4) или сигнала ЭТОТ на входе 37 низкого уровня. При этом сигнал готовности READY на выходе 92.1 не сформирован, поскольку триггер 77 останова установлен в нулевое состояние по нулевому выходу, или присутствует сигнал блокировки БЛ.ГОТ низкого уровня.

Сигнал сброса RESET формируется на выходе 92.4 триггера 88 благодаря строби- рованию сигнала RESET-П на входе 98.2 тактовой частотой CLC с выхода элемента НЕ 89.

Рассмотрим процесс синхронизации управления процессом эмуляции в предлагаемой системе. Начало этого процесса определяется переходом триггера 153 блока 7 (фиг. 8) по переднему фронту тактового сигнала CLC с входа 32 в нулевое состояние по инверсному выходу. При этом формируется начало фронта сигнала низкого уровня СТСС на выходе 44 блока 7, который открывает выходные ключи регистра 181 блока 10 (фиг. 11). Это, в свою очередь, приводит к появлению на шине 16 (фиг. 1)сигналов кода состояния 52-П-50-П с входов 51 блока 10 (фиг. 11).

Сигналом СТСС с нулевого выхода триггера 153 (фиг. 8) по S-входам устанавливаются в нулевое состояние по инверсным выходам триггеры 154 и 156. При этом формируется начало сигналов ОТСА и СТМА на выходах 167.2 и 167.3 соответственно, Указанными сигналами с входов 186.2 и 186.3 открываются выходные ключи регистров 182 и 183 соответственно, что приводит к выдаче на выходах 53 и 54 блока 11 адресных сигналов Ар-П-А19-П, ВНЕ-П.

По переднему фронту очередного импульса CLC с входа 32 блока 7 (фиг. 8) триггер 156 через триггер 155, выполняющий функцию задержки переднего фронта сигнала CLC, устанавливается в нулевое состо- яние. По заднему фронту сигнала СТМА с выхода 163.3 блока 7 закрываются выходные #лючи регистра 183, тем самым завер- шается выдача сигналов адреса А0-П-А15-П на шину 16 (фиг. 1).

В дальнейшем обмен данными между шиной 15 (фиг. 1) AD0-AD15 и шиной 16 системы осуществляется через магистраль- ный элемент 203 (фиг. 14), а обмен между шиной 15 и портами В0, В1 блока 201 осуществляется через блок 202 (фиг 14).

Окончание выдачи сигнала СТМА на выходе 167.3 приводит к формированию на выходе 167.1 переднего фронта сигнала фиксации состояния СФС, который поступает на вход 186.1 блока 11 (фиг. 12). Выходным сигналом высокого уровня с элемента ИЛИ 184 (фиг. 12) происходит фиксация в регистре 152 (при открытых сигналом с входа 186.2 выходных ключах Тблока 182) состояния шины 15 (фиг. 1) кодом A16/ST3- A19/ST6, BHE/ST7 блока 1 (фиг. 2).

Поскольку к рассматриваемому момен- ту времени на шине 15 блоком 1 устанавливается код слова состояния блока 1, то на шине Сформируется код состояния 5ТЗ-П- 5Т7-П. Одновременно с этим формируется сигнал СТМА V СТСА на выходе 40 блока 7 (фиг. 8), который поступает на одноименный вход элемента И 67 (фиг. 2) и разрешает выдачу на шину 16 (фиг. 1) сигнала чтения RD-П с выхода 71.4 группы 18 выходов блока 1 (фиг. 2). Кроме того, сигналом с выхода 42 блока 7 разрешается формирование эле- ментом И 145 блока 6 (фиг. 7) сигнала СТД на выходе 148.2 блока 6.

Завершение сигналов СТСС и СТС на выходах 44 и 167.1 блока 7 (фиг. 8) соответ- ственно определяется поступлением сигнала окончания цикла обмена КЦО на вход 29 блока 7, сформированного таким образом, чтобы переход сигналов процессора 1 (фиг. 2) S2-SЈ на выходах 20 в состояние 1112 и1 завершение сигнала СТСС на выходе 44 блока 7 (фиг. 8) произошли в одном такте цикла обмена. Это гарантирует синхронное завершение цикла обмена процессора и отлаживаемой системы.

Завершение сигналов СТСА на выходе 167.2 (СТМА V СТСА) на выходе 40 происходит по сигналу СФА с входа 45, формируемому в начале следующего цикла обмена блока 1 (фиг. 2) контроллером 170 (фиг, 9),

Начало цикла обмена данными блока 1 (фиг, 1) с отлаживаемой системой обеспечивается подачей на D-вход триггера 153 (фиг. 8) сигнала уровня Лог. 1. Изменение этого состояния D-входа триггера 153 на нулевое возможно лишь в последнем такте TW цикла обмена (фиг. 15-21). При этом подача сигна- ,ла высокого уровня на D-вход триггера 153 может осуществляться тремя способами: программной установкой единичного сигнала ПУСК на входе 169,3 (при нулевом значении сигнала АВТ с входа 169.1); изменением состояния S2-S0 на выходах 20 (фиг, 2) со значения 1112 на любое другое (при единичном значении сигнала АВТ); кодом типа цикла обмена Ф52-Ф50 на выходах регистра 180, сличающимся от кода 11 пассивное состояние) и от кода 1002 (код чтения команды) при наличии единичного сигнала ЦКЛ по, завершении сигнала СФА на выходе 41 бло- ка 7 (фиг. 8).

Сигнал ЭТОТ готовности формируется на выходе 37 блока 6 (фиг. 7) при наличии сигнала ЭМУЛ на входе 151.2 блока 6, нулевом значении сигнала ЦКЛ на входе 151.1, а также в любом цикле обмена, кроме цикла чтения кода команды, при единичном значении сигнала ЦКЛ. При этом же условии раэ- решается формирование сигнала СТДЭ на выходе 148.1 блока 6 (фиг. 7) и блокируется выдача сигнала СТД на выходе 148.2, Формирование сигналов СТД и СТДЭ стробиру- ется действующим единичным значением сигнала DEN с входа 150.2 блока 6, который формируется на выходе 171.2 блока 8 (фиг. 91

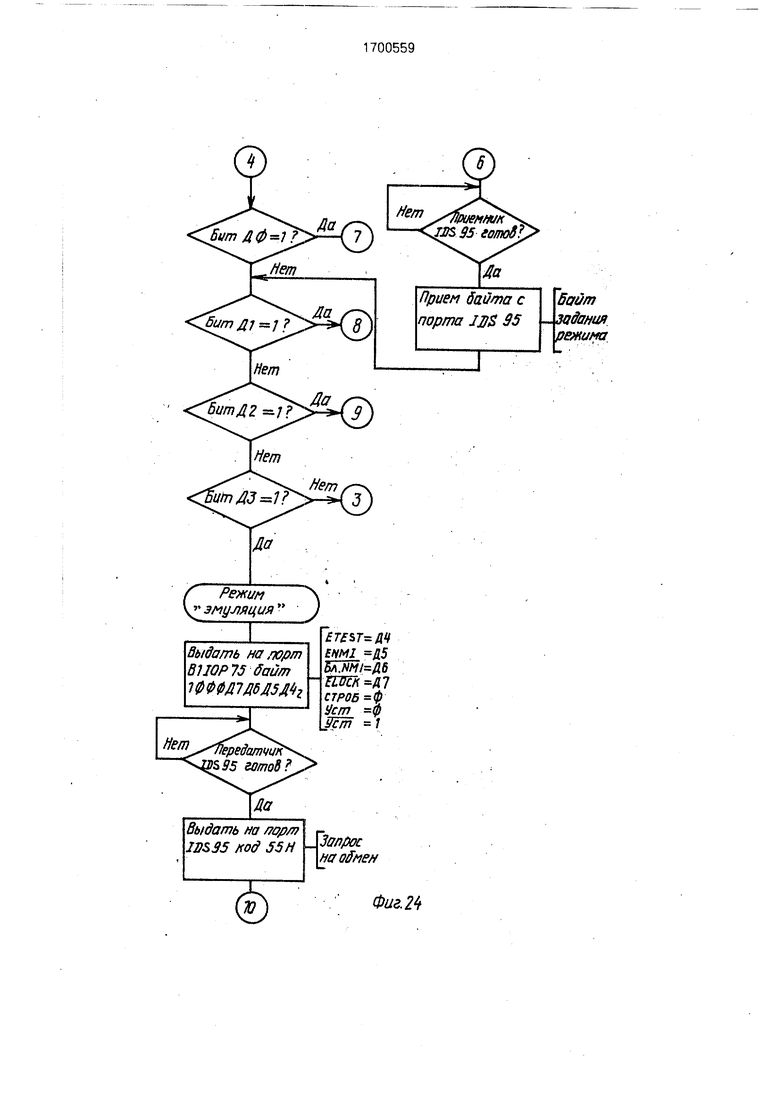

Дополнительным условием формирования сигнала СТДЭ является нулевое значение сигнала DT/R с выхода 171.1 блока 8, который поступает на вход 150.1 блока 6 (фиг.7). Условие формирования сигнала СТД определяется, кроме того, нулевым значением сигнала СТМА V СТСА на выходе 40 (фиг. 8). Это обусловлено необходимостью блокировки выдачи данных с портов В0, В1 на шину 15 (фиг. 1 и 2) блока 1 в циклах записи данных и необходимостью согласования момента приема (выдачи) данных отлаживаемого комплекса с временной диаграммой сигналов шины 16 (фиг. 15-21). Функционирование предлагаемой системы осуществляется в соответствии с алгоритмами, приведенными на фиг, 17. При этом отдельные этапы, составляющие алгоритмы режимов работы, выполняются в соответствии с временными диаграммами, приведенными на фиг. 15-21.

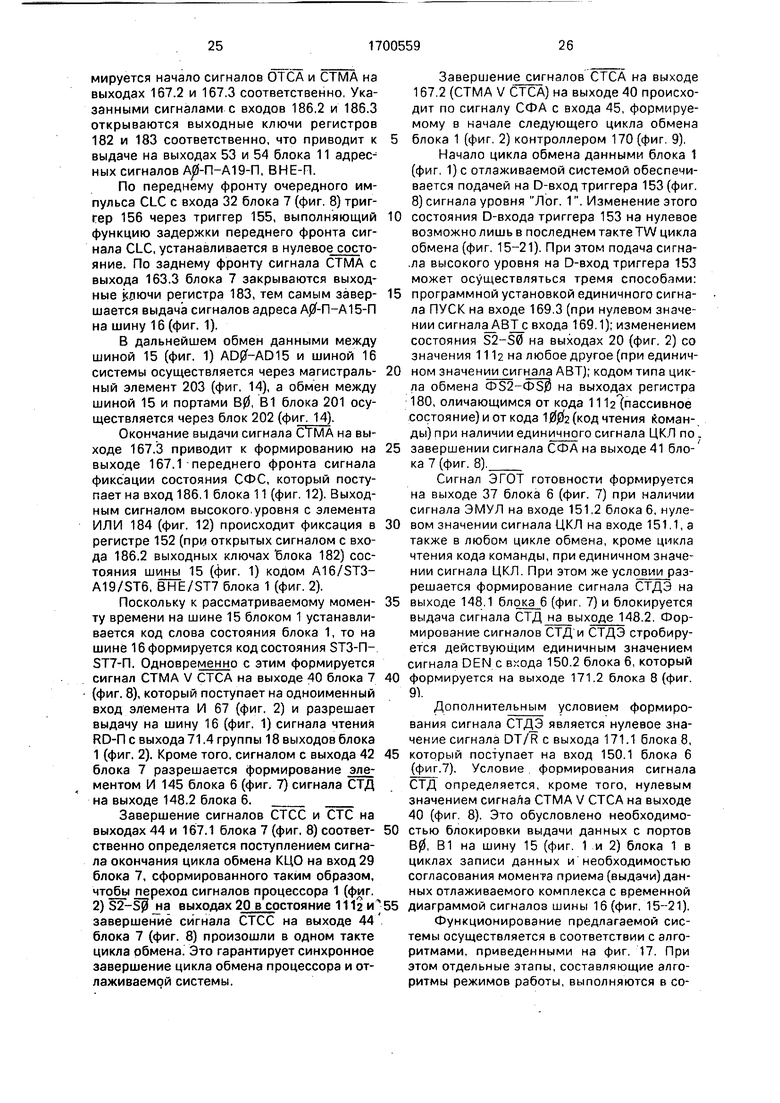

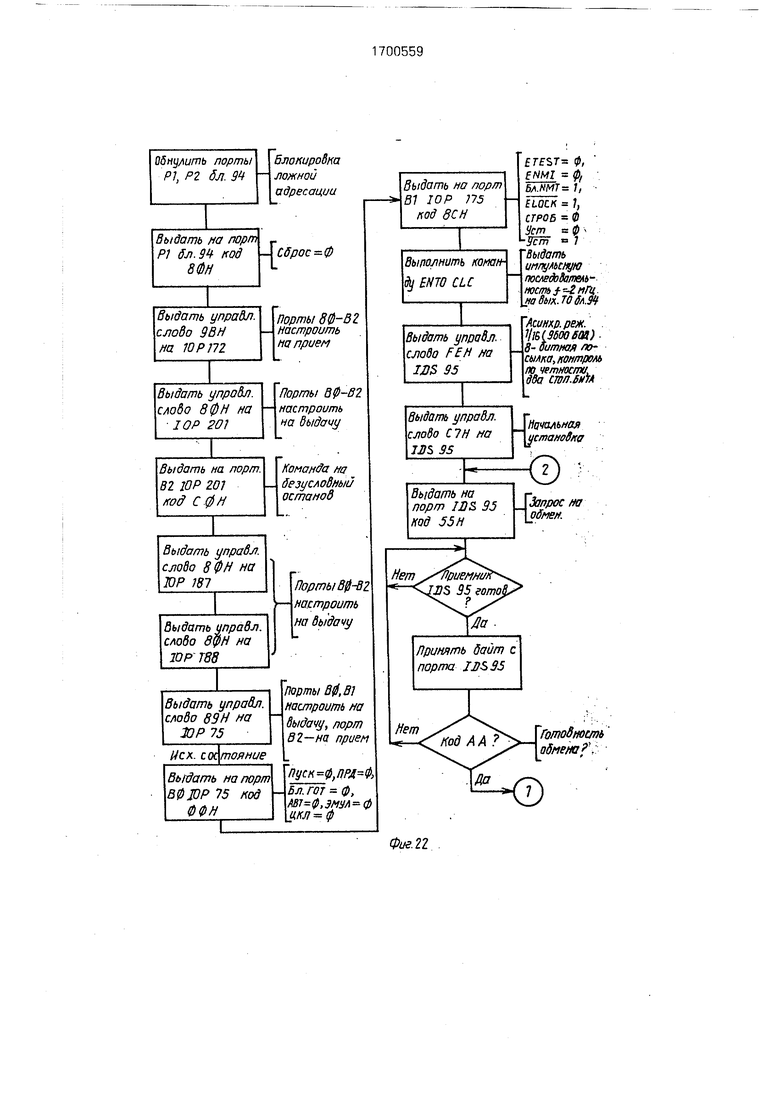

При включении питания блоком 5 (фиг. 6) по программе, записанной в блоке 96 памяти, осуществляется настройка блоков 75, 172, 201, 187 и 188. Устанавливаются коды, определяющие безусловный останов блока 1 (фиг. 2) в первом же цикле, и снимаются сигналы блокировки,

В результате этого, система переходит в исходное состояние, в котором блок 1 (фиг. 1) остановлен в такте Тп (по сигналу останова ОСТ на входе 58 блока 3 (фиг. 4) шина 16 сохраняет пассивное состояние, а обмен данными заблокирован).

В исходном состоянии производится передача информации, зафиксированной на регистрах 180, 173 и 174 (фиг. 11 и 10); в инструментальный комплекс через группу 17 входов-выходов.

На основании анализа этой информации из инструментального комплекса передается управляющее слово, которое определяет переход системы из исходного состояния в один из четырех режимов работы:

Эмуляция. Обмен. Цикл, Автомат.

Анализ управляющего слова осуществляется блоком 94 (фиг. 6) по заданной в блок 96 программе. Управляющее слово, кроме того, определяет, будет ли выполняться режим со следующими дополнительными функциями: формирование системой сигнала TEST на одноименный вход блока 65 (фиг. 2); формирование системой сигнала NMI на одноименный вход блока 65 (фиг. 2); формирование системой сигнала LOCK-П на выходе 71,3 блока 1 (фиг. 2); блокировка сигнала немаскируемого прерывания NMI.

Управление формированием этих сигналов осуществляется кодом с выходов порта В1 блока 75 (фиг. 3).

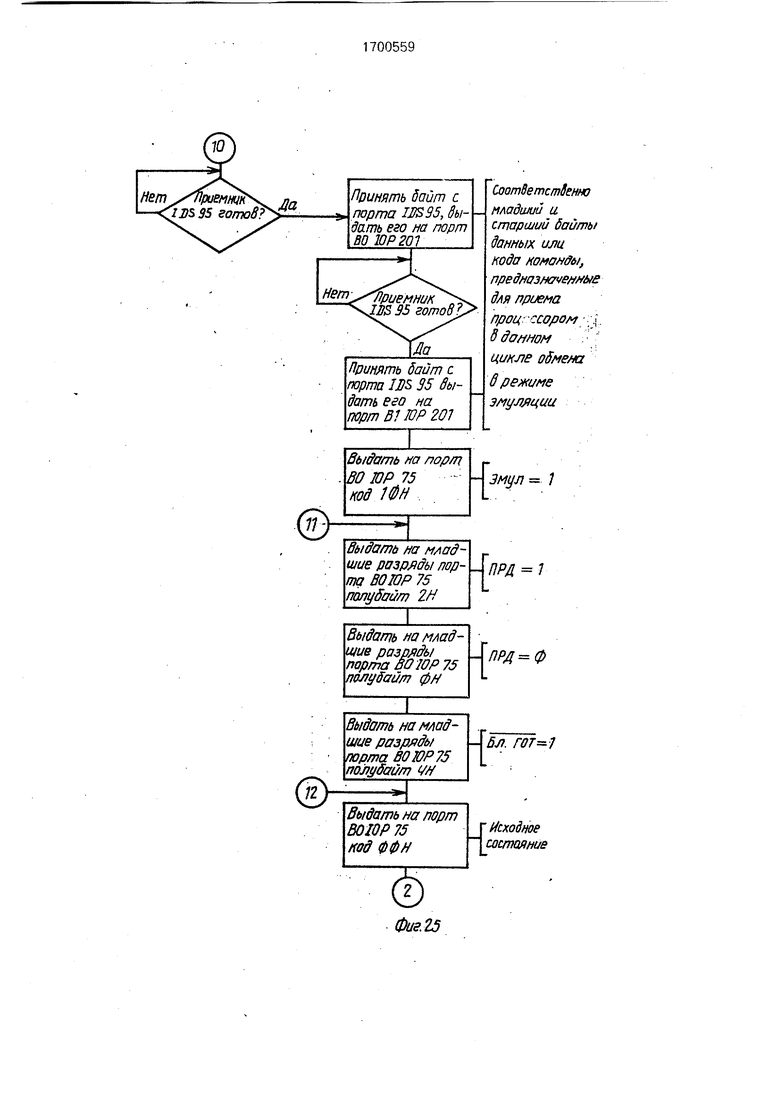

В режиме Эмуляция (фиг. 24) из инструментального комплекса через группу 17 входов-выходов принимается и заносится на порты В(5 и В1 блока 201 два байта данных и производится один цикл чтения блока 1 (фиг. 2) этих данных с сохранением пассивного состояния шины 16 (фиг. 1) По завершении цикла обмена система возвращается в исходное состояние

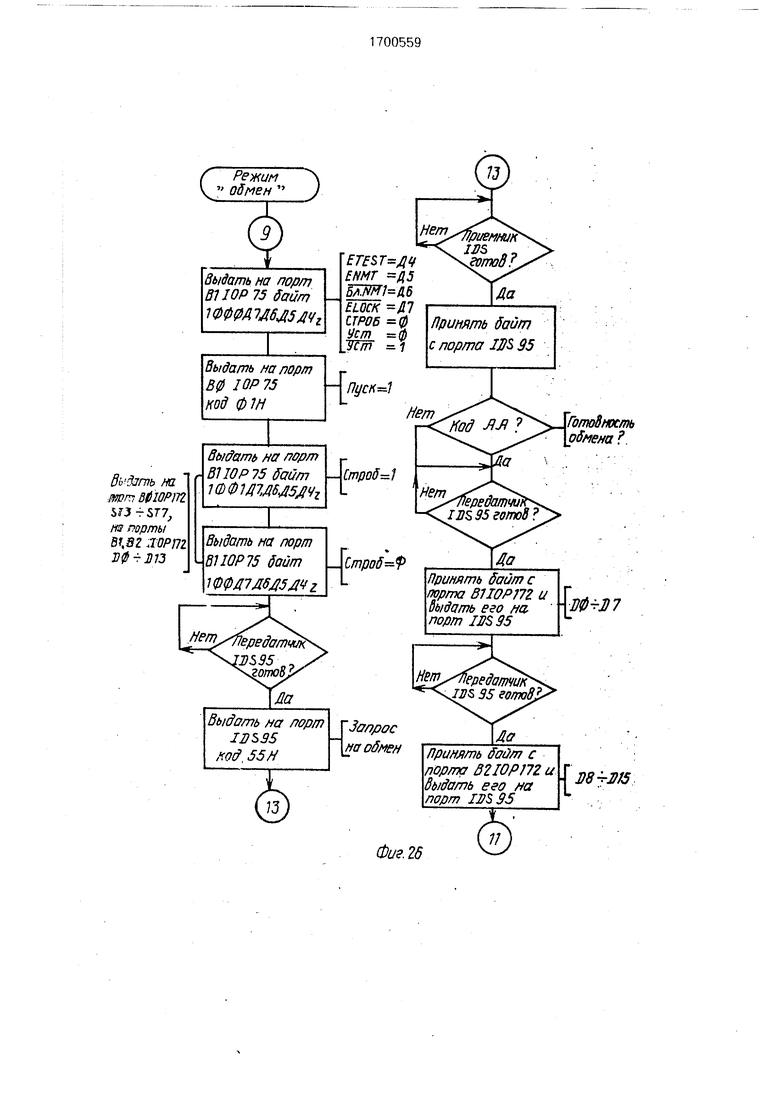

В режиме Обмен (фиг 26) производится один цикл обмена блока 1 с отлаживаемой системой по интерфейсу шины 16 (фиг

1).

В режиме Цикл (фиг 24) из инструментального комплекса через группу 17 входоввыходов принимаются и заносятся в порты В0 и В1 блока 201 два байта данных, представляющие собой команду чтения или записи данных в ячейку памяти или порт

ввода-вывода. При этом команда должна быть двух- или однобайтной (в последнем случае во втором байте содержится код ЗОН команды NOP), Система настраивается на режим циклического выполнения записанной в порты В, В1 блока 201 команды, аппаратный останов блокируется.

Блок 1 системы в этом режиме читает коды с портов В0 и 81 блока 201 также, как и в режиме Эмуляцияи. Другие циклы об5 мена выполняются по шине 16 аналогично режиму Ъбмен.

В режиме Автомат система принимает от инструментального комплекса семь байтов, определяющих условия основного и

0 вспомогательного остановов. Инициируется блок 12 останова (фиг. 1), После этого система настраивается на автоматическое выполнение программы отлаживаемой системы в реальном масштабе времени. Факти5 чески между двумя циклами обмена по шине 16 присутствует холостой такт. Для блока 1 (фиг. 2) эта задержка проявляется в виде наличия лишнего такта ожидания TW.

Выход из режима Автомат происходит

0 при останове по заданным условиям (на основе анализа кода состояния СП0-СГ2. который с выходов 30 блока 3 (фиг. 4) поступает на порт В2 блока 75 (фиг. 3) или по команде поступает через группу 17 Bko5 дов-выходов из инструментального комплекса)/

Формула изобретения 1, Система отладки микропроцессорных устройств, содержащая процессор, блок

0 коммутации управляющих сигналов, блок синхронизации процессора, блок задания режимов обмена, блок регистров состояния, первый блок регистров адреса, блок коммутации данных, причем группа входов-выхо5 дов обмена сигналами данных и группа управляющих чтением входов блока коммутации управляющих сигналов соединены соответственно с разрядами данных и управляющими разрядами шины обмена сис0 темы, группа выходов, управляющих сигналами разрешения блока коммутации управляющих сигналов, соединена с первой группой управляющих входов процессора, группа входов-выходов данных/адреса ко5 торого через внутреннюю шину данных соединена с группой информационных входов первого блока регистров адреса и первой группой входов-выходов данных блока коммутации данных, группа выходов кода состояния процессора соединена с группами информационных входов блока задания режимов обмена и блока регистров состояния, группы входов-выходов запросов, выходов состояния очереди команд и вторая группа управляющих входов процессора соединены соответственно с разрядами запросов, разрядами состояния очереди команд и управляющими разрядами внешней шины данных системы, первая группа выходов и выход блока синхронизации процессора соединены соответственно с группой входов синхронизации процессора и входом синхронизации блока задания режимов обмена, группа входов блока синхро- низации процессора соединена с разрядами синхронизации процессора и с разрядами синхронизации внешней шины данных системы, выход управления фиксацией адреса и выход разряда управления передачей-приемом данных группы выходов блока задания режимов обмена соединены соответственно с одноименными входами первого блока регистров адреса, блока регистров состояния и блока коммутации данных, первая группа выходов выдачи слова состояния микропроцессора, блока регистров состояния соединена с разрядами сигналов состояния внешней шины системы, группы выходов мультиплексированного кода и кода адреса/данных первого блока регистров адреса соединены с соответствующими группами разрядов адреса внешней шины данных системы, первая группа выходов данных, вторая группа входов-выходов данных и первая группа управляющих входов блока коммутации данных соединены соответственно с разрядами данных внешней шины данных, разрядами данных шины обмена и управляющими разрядами шины обмена системы, отличающаяся тем, что, с целью повышения быстродействия, она содержит блок окончания цикла обмена, блок задания режимов эмуляции, блек синхронизации обмена, блок выбора адреса, второй блок регистров адреса и блок останова, причем группа входов-выходов адреса/данных процессора соединена через внутреннюю шину данных с первой группой входов данных второго блока регистров адреса, группа выходов кода состояния процессора соединена с группой информационных входов блока выбора адреса, группа информационных выходов блока коммутации управляющих сигналов - с первой группой входов блока окончания цикла обмена, а выходы первых и вторых управляющих разрядов группы информационных выходов блока коммутации управляющих сигналов соединены с первой группой управляющих входов блока синхронизации

обмена и группой управляющих входов блока выбора адреса, выход разряда синхронизации адреса группы управляющих выходов блока коммутации управляющих сигналов 5 соединен с одноименным входом второго блока регистров адреса, группа выходов состояния, первый и второй выходы блока окончания цикла обмена соединены соответственно с группой информационных вхо- 0 дов блока коммутации управляющих сигналов, первым входом блока синхронизации процессора и первым управляющим входом блока выбора адреса, группа выходов, первый выход стробирования, первый

5 и второй выходы инверсного стробирования и второй выход стробирования которого соединены соответственное группой управляющих входов первого блока регистров адреса, управляющим входом процессора,

0 вторым входом блока синхронизации процессора, управляющим входом блока синхронизации обмена и входом управления связью с внешней шиной данных блока регистров состояния, вторая группа выходов

5 блока синхронизации процессора и выход тактового разряда этой группы соединены соответственно с второй группой входов блока окончания цикла обмена и вторым управляющим входом блока выбора адреса,

0 группа входов-выходов системы соединена с первой группой входов-выходов блока задания режима эмуляции, вторая группа входов-выходов которого соединена с шиной обмена системы, первый и второй выходы и

5 группа выходов блока синхронизации обмена соединены соответственно с первым управляющим входом блока окончания цикла обмена, третьим управляющим входом бло ка выбора адреса и второй группой управля0 ющих входов блока коммутации данных, вторая группа выходов данных которого соединена с первой группой входов данных блока останова, выход управления фиксацией адреса блока задания режимов обме5 на соединен с одноименными входами блока окончания цикла обмена, блока выбо- . ра адреса и второго блока регистров адреса, группа выходов блока задания режимов обмена соединена с второй группой управля0 ющих входов блока синхронизации обмена, группа выходов второго блока регистрои адреса - с группой адресных входов блока останова, группы входов-выходов данных и управляющих входов соответственно второ5 го блока регистров адреса и блока останова соединены с соответствующими разрядами данных и управляющими разрядами шины обмена системы, вторая группа входов данных блока останова соединена с соответствующими разрядами внутренней шины

данных системы, вторая группа выходов блока регистров состояния - с группой информационных входов блока синхронизации обмена, второй и третьей группами входов данных соответственно второго блока регистров адреса и блока останова, выход сигнала останова блока останова соединен с вторым управляющим входом блока окончания цикла обмена, третий управляющий вход которого соединен с разрядом готовности внешней шины данных системы.

2. Система по п. 1,отличающаяся тем. что блок окончания цикла обмена содержит первый, второй и третий триггеры, элемент И, первый, второй, третий и четвертый элементы ИЛИ, причем нулевой выход первого триггера подключен к инверсному входу первого элемента ИЛИ, выход которого подключен к совмещенным инверсному J-входу и К-входу второго триггера, а также к первому разряду группы выходов состояния блока окончания цикла обмена, единичный выход второго триггера подключен к первому выходу блока окончания цикла обмена, а нулевой выход второго триггера - к нулевому входу третьего триггера, единичный выход которого подключен к синхров- ходу первого триггера, к инверсному входу второго элемента ИЛИ, к второму разряду группы выходов состояния блока окончания цикла обмена, к прямому J-входу второго триггера, инверсный выход третьего триггера подключен к первому входу элемента И, выход которого подключен к второму выходу блока окончания цикла обмене), выход третьего элемента ИЛИ подключен к прямому J-входу второго триггера и к третьему разряду группы выходов состояния блока окончания цикла обмена, выход четвертого элемента ИЛИ подключен к прямому входу второго элемента ИЛИ, выход которого подключен к прямому входу первого элемента ИЛИ, первая группа входов блока окончания цикла обмена подключена первым разрядом к нулевому входу первого триггера, а вторым разрядом - к инверсному входу четвертого элемента ИЛИ, установочный и информационный входы третьего триггера подключены к заземляющей шине, прямой вход четвертого элемента ИЛИ - к заземляющей шине, вторая группа входов блока окончания цикла обмена подключена первым, вторым и третьим разрядами к синх- ровходам соответственно второго и третьего триггеров и второму входу элемента И, третий и первый управляющие входы блока окончания цикла обмена являются соответственно прямым и инверсным входами третьего элемента ИЛИ, вход управления

фиксацией адреса блока окончания цикла обмена подключен к установочным входам первого и второго триггеров, второй управляющий вход блока окончания цикла обме- на - к информационному входу первого триггера.

3.Система по п. 1,отличающаяся тем, что блок синхронизации процессора содержит первый и второй триггеры, первый,

второй и третий элементы НЕ, причем инверсный выход первого триггера подключен к первым разрядам первой и второй групп выходов блока синхронизации процессора, выход первого элемента НЕ - к второму

5 разряду первой группы выходов блока, а также к входу второго элемента НЕ и к син- хровходу второго триггера, инверсный выход которого подключен к второму разряду второй группы выходов блока, выход второ0 го элемента НЕ подключен к третьим разрядам первой и второй групп выходов блока и к выходу блока, выход третьего элемента НЕ - к информационному входу второго триггера, обнуляющий и информационный вход

5 первого триггера, установочные единичные и нулевой входы второго триггера подключены к заземляющей шине, первый и второй управляющие входы блока - к установочному единичному входу и синхровходу соот0 ветственно первого триггера, группа входов блока подключена первым разрядом к входу первого элемента НЕ, а вторым разрядом - к входу третьего элемента НЕ.

4,Система по п.1,отличающаяся 5 тем, что блок синхронизации обмена содержит пять элементов И, элемент ИЛИ и элемент НЕ, причем выход первого элемента И подключен к первому входу второго элемента И, инверсный выход которого подключен

0 к первому инверсному входу элемента ИЛИ и является вторым выходом блока синхронизации обмена, выход третьего элемента И подключен к первому входу четвертого элемента И и к входу элемента НЕ, выход кото5 рого подключен к первому входу пятого элемента И и является первым выходом блока синхронизации обмена, инверсный выход четвертого элемента И подключен к первому разряду группы выходов блока син0 хронизации обмена, выход пятого элемента И - к второму разряду группы выходов блока синхронизации обмена, выход элемента ИЛИ - к первому входу третьего элемента И, группа информационных входов блока син5 хронизации обмена подключена первым разрядом к второму входу второго элемента И, вторым разрядом и третьим разрядом - к первому и второму инверсным входам первого элемента И, вторая группа управляющих входов блока синхронизации обмена

первым разрядом подключена к инверсному входу четвертого элемента И, а вторым разрядом - к вторым входам четвертого и пятого элементов И, первая группа управляющих входов блока синхронизации обмена подключена первым разрядом к третьему входу второго элемента И и второму инверсному входу первого элемента ИЛИ, вторым разрядом - к второму входу третьего элемента И, управляющий вход блока синхронизации обмена является третьим входом пятого элемента И.

5. Система по п.1,отличающаяся тем, что блок выбора адреса содержит пять триггеров, пять элементов И, четыре элемента ИЛИ, элемент задержки и элемент НЕ, причем прямой выход первого триггера подключен к прямому входу первого элемента И, выход которого подключен к первому входу первого элемента ИЛИ, инверсный выход второго триггера подключен к установочным единичным входам третьего и четвертого триггеров и второму выходу стробирования, к входу элемента задержки, инверсный выход которого подключен к первому входу второго элемента И, инверсный выход третьего триггера - к первому разряду группы выходов блока, прямой, выход - к единичному входу пятого триггера и к первому входу третьего элемента И, инверсный выход которого является первым выходом стробирования блока, инверсный выход пятого триггера подключен к синхровходу четвертого триггера, инверсный выход которого подключен к второму разряду группы выходов блока, к вторым входам третьего и второго элементов И, выход четвертого элемента И подключен к второму входу первого элемента ИЛИ, выход которого подключен к информационному входу второго триггера, выход пятого элемента И подключен к первому входу второго элемента ИЛИ, выход которого подключен к синхровходу первого триггера, выход второго элемента И подключен к третьему разряду группы выходов блока, прямой выход третьего элемента И - к второму выходу инверсного стробирования блока, выход третьего элемента ИЛИ - к первому входу четвертого элемента И, выход четвертого элемента ИЛИ - к обнуляющему входу второго триггера, выход элемента НЕ - к первому входу пятого элемента И, к инверсному обнуляющему входу первого триггера и к первому выходу инверсного стробирования блока, группа информационных входов блока первым, вторым и третьим разрядами подключена соответственно к первому, второму и третьему инверсным входам третьего элемента ИЛИ, группа управляющих

входов подключена первым разрядом к. инверсному входу первого элемента И и к второму входу четвертого элемента И, вторым разрядом - к второму входу пятого элемента 5 И, третьим разрядом - к второму входу второго элемента ИЛИ, третий управляющий вход блока является третьим входом пятого элемента И, первый управляющий вход блока - инверсным входом четвертого элемента

0 ИЛИ, вход управления фиксацией адреса блока подключен к синхровходу третьего триггера и к входу элемента НЕ, второй уп- .равляющий вход блока подключен к синх- ровходам пятого и второго триггеров,

5 единичный и информационный входы первого триггера, единичный вход второго триггера, информационный и обнуляющий входы третьего, пятого и четвертого триггеров, а также прямой вход четвертого эле0 мента ИЛИ подключены к заземляющей шине.

6. Система по п. 1,отличающаяся тем, что блок останова содержит первое и второе программируемые устройства ввода5 вывода, шесть схем сравнения, элемент ИЛИ, причем группы выходов первого, второго и первая группа третьего каналов первого программируемого устройства ввода-вывода подключены к разрядам пер0 вой группы информационных входов первой схемы сравнения, выход которой подключен к первому входу элемента ИЛИ, вторая группа выходов третьего канала первого программируемого устройства ввода-вьпюда

5 подключена к первой группе информационных входов второй схемы сравнения, группы выходов первого и второго каналов, а также первая группа выходов третьего канала второго программируемого устройства

0 ввода-вывода подключены к разрядам первой группы информационных входов третьей схемы сравнения, выход которой подключен к второму входу элемента ИЛИ, вторая группа выходов третьего канала вто5 рого программируемого устройства ввода- вывода подключена к первой группе информационных входов четвертой схемы сравнения, выход которой подключен к второму входу элемента ИЛИ, третья группа

0 выходов третьего канала второго программируемого устройства ввода-вывода подключена к первой группе информационных входов пятой схемы сравнения, выход которой подключен к второму входу элемента

5 ИЛИ, третья группа выходов третьего канала первого программируемого устройства ввода-вывода подключена к первой группе информационных входов шестой схемы сравнения, группа входов адреса блока подключена к вторым группам информационных входов первой и третьей схем сравнения, группа входов-выходов блока подключена к группе информационных входов-выходов первого программируемого устройства ввода-вывода и к группе информационных входов второго программируемого устройства ввода-вывода, группа управляющих входов блока останова подключена первым разрядом к входу чтения, вторым разрядом - к входу записи первого и второго программируемых устройств ввода-вывода, третий разряд подключен к входу выбора первого программируемого устройства ввода-вывода, четвертый разряд - к первому входу адреса, пятый разряд - к второму входу адреса, шестой разряд - к входу начальной установки первого и второго программируемых устройств ввода-вывода, седьмой разряд- к входу выбора второго программируемого устройства ввода-вывода, третья группа входов данных блока оста- нова подключена к вторым группам

информационных входов второй и четвертой схем сравнения, вторая группа входов данных блока останова - к вторым группам информационных входов шестой и пятой

схем сравнения, первая группа входов данных блока останова первым разрядом - к единичному установочному входу первой схемы сравнения, вторым разрядом - к единичному установочному входу третьей схемы сравнения, третьим разрядом - к нулевому, а четвертым разрядом - к единичному установочному входам второй схемы сравнения, пятый разряд подключен к нулевому установочному входу четвертой схемы

сравнения, шестой, седьмой и восьмой разряды - к единичным установочным входам четвертой, шестой и пятой схем сравнения, выход второй схемы сравнения подключен к первому входу элемента ИЛИ, выход которого является выходом останова блока останова, выход шестой схемы сравнения подключен к первому входу элемента ИЛИ.

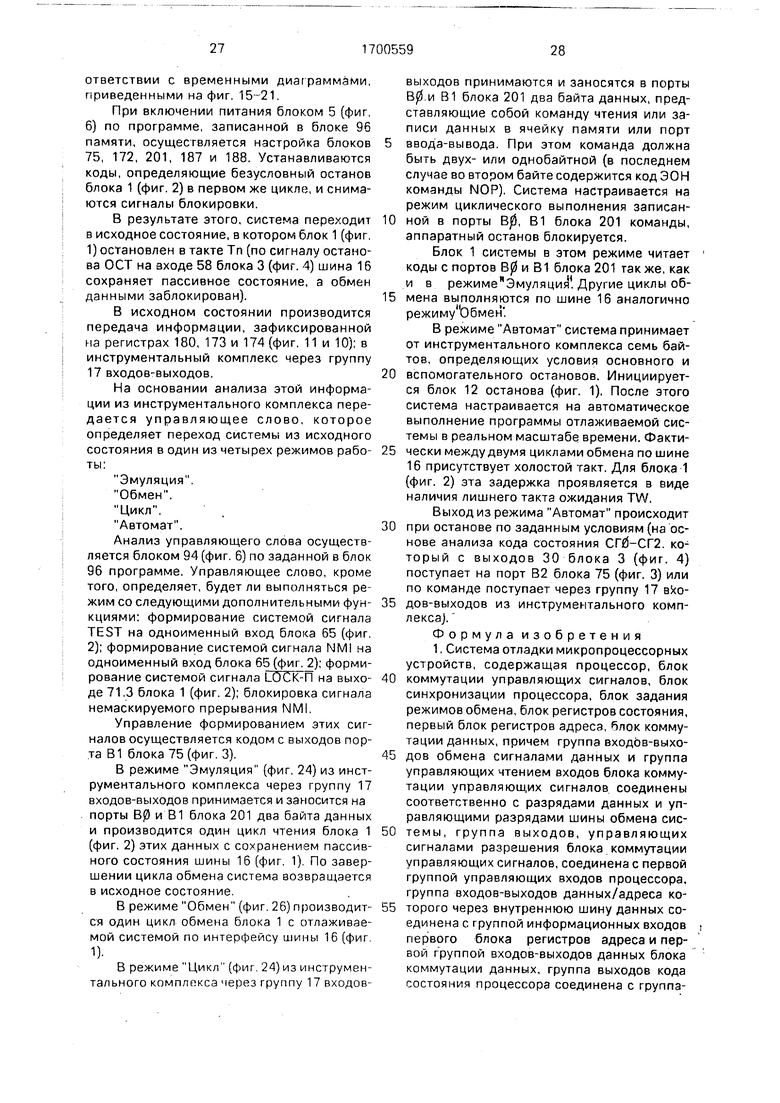

Таблица 1

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для сопряжения микропроцессора с системной шиной | 1990 |

|

SU1837299A1 |

| Устройство для сопряжения микроЭВМ с внешним устройством | 1985 |

|

SU1283780A1 |

| Система для отладки программ | 1987 |

|

SU1481774A1 |

| Система коммутации | 1985 |

|

SU1317448A1 |

| Устройство для отладки программ микроЭВМ | 1989 |

|

SU1815643A1 |

| Распределенная система управления | 1989 |

|

SU1732345A1 |

| Устройство для сопряжения двух ЭВМ | 1989 |

|

SU1681307A1 |

| Микропрограммное устройство управления | 1983 |

|

SU1156073A1 |

| Устройство для контроля и восстановления микропроцессорной системы | 1985 |

|

SU1317441A1 |

| Устройство для сопряжения магистрали ЭВМ с периферийными устройствами | 1990 |

|

SU1751775A1 |

Изобретение относится к вычислительной технике и может быть использовано при отладке программно-аппаратных средств микропроцессорных систем методом внутрисхемной эмуляции. Цель изобретения - повышение быстродействия системы за счет возможности реализации сложных логических условий остановов при отладке, а также обращений к отдельным заданным Изобретение относится к вычислительной технике и может быть использовано при отладке программно-аппаратных средств микропроцессорных систем методом внутрисхемной эмуляции. Целью изобретения является повышение быстродействия работы системы. На фиг. 1 приведена структурная схема системы; на фиг. 2-14-соответственно фунячейкам памяти, а не к массивам. Удобство отладки повышается за счет отказа от жесткого распределения памяти, а также прозрачности средств эмуляции для пользователя. Для достижения цели в систему введены следующие блоки с соответствующими связями: блок окончания цикла обмена, позволяющий инициировать очередной цикл обмена в системе; блок задания режимов эмуляции, позволяющий осуществлять связь с инструментальным комплексом; блок синхронизации обмена, формирующий необходимые для обеспечения работы системы управляющие сигналы; блоки выбора адреса л регистров адреса, позволяющие формировать сигналы управления выбором адреса, а также осуществлять обмен между шиной обмена и внутренней шиной данных; блок останова, формирующий сигналы останова при различных логических условиях, задаваемых пользователем. Система также содержит процессор, блок коммутации управляющих сигналов, блок синхронизации процессора, блок задания режимов обмена, блок регистров состояния, блок регистров адреса, блок коммутации данных. 5 з.п.ф-лы, 30 ил. 3 табл. кциональные схемы процессора, блока коммутации управляющих сигналов, блока окончания цикла обмена, Слока синхронизации процессора, блока задания режимов эмуляции, блока синхронизации обмена, блока выбора адреса, блока задания режимов обмена, второго блока регистров адреса, блока регистров.состояния, первого блока регистров адреса, блока останова, со с VI о о ел ел о

Таблица 2

1ST4 /2ST4/

1ST3 /2ST3/

1 2 3

0 0

1

0 1

J0

Останов в цикле обмена (физический адрес формируется от:носительно сегмента ES)

Останов в цикле обмена данными со стеком (физический

адрес формируется относительно сегмента SS) Останов в цикле чтения кода инструкции / физический адрес формируется относительно сегмента CS / или в цикле обмена, когда физический адрес формируется без использования

сегментных регистров /относительно нуля/ Останов в цикле обмена, в котором физический адрес

формируется относительно сегмента DS

Таблица 3

Условия останова по сегментному регистру

Внешняя шина данных.

г 4

ж ж

ж

- JfL52&6

L..

Фиг. 2

Фиг.З

Фиг.5

гь

Г

i

Фиг.7

1

Фиг. 9

Фиг. Ю

U МФ

69900А1

Г

W

Фиг. Щ

Такты работы эмулятора

(911)

C7WT

(167.3)

С7СЯ

(167.2}

СШ

(W)„ „