Изобретение относится к информационно-измерительной технике и может найти применение в составе бортовых систем преобразования аналоговой и дискретной информации, автоматизированных систем управления летательных аппаратов, а также в составе наземных автоматизированных систем контроля.

Весьма важным параметром устройства сбора данных является быстродействие, особенно при большом числе контролируемых объектов. Требуемое быстродействие можно, очевидно, обеспечить, применяя устройства с большей скоростью преобразования. Учитывая повышенные требования по снижению энергопотребления и стоимости, более предпочтительным является поиск усовершенствованных алгоритмов работы. Наряду с указанной задачей встречается и другая, когда быстродействующее устройство ввода аналоговой информации перегружает центральный процессор. В этом случае устройство аналогового ввода целесообразно дополнить ОЗУ, как это сделано в устройстве сбора данных [1].

Указанное устройство содержит блок ввода и преобразования аналоговой информации (БВПАИ), включающий в себя N трактов преобразования, запоминающее устройство (ЗУ), управляющий вычислитель (УВ), блок синхронизации, состоящий из коммутатора сигналов внешней синхронизации, формирователей длинных и коротких импульсов, источника эталонной частоты, счетчика, двух элементов И, элемента ИЛИ, блока управления, содержащего делитель частоты, четыре триггера, таймер, элемент ИЛИ, элемент И. Аналоговые сигналы поступают на N групп информационных входов блока БВПАИ. Цикл измерения аналоговых сигналов начинается с установки в ноль N трактов преобразования указанного блока. Для этого блок управления вырабатывает строб, который поступает на вход сброса блока БВПАИ. По окончании строба сброса N трактов преобразования осуществляют одновременное накопление n сигналов за время, равное или кратное целому числу периодов напряжения бортсети. Для этого блок управления вырабатывает строб накопления, который поступает на вход разрешения блока БВПАИ. По окончании строба накопления N трактов преобразования переходят в режим хранения аналоговых сигналов в течение n преобразований накопленной информации в цифровой код. Цифровые коды аналоговых сигналов записываются в ЗУ блока БВПАИ. После этого триггер прерывания блока управления вырабатывает сигнал-запрос на прерывание (ЗПР), который поступает в указанный блок. Последний на сигнал ЗПР вырабатывает сигнал предоставления прерывания (ПНР). Этот сигнал снимает запрос на прерывание, и блок управления вырабатывает следующий строб сброса. С этого момента происходит обмен информацией между ЗУ и УВ, а для трактов преобразования - следующий цикл измерения. Описанное устройство сбора данных имеет ограниченное быстродействие, т.к. ввод данных по прерыванию имеет ограниченную скорость передачи данных даже при условии, что осуществляется только передача данных без проверки условий или преобразования формата данных. Выполнение любой такой операции может значительно уменьшить эту скорость. Применение двухвходового ОЗУ в устройствах ввода аналоговой информации позволяет сократить затраты машинного времени процессора на работу с устройством аналогового ввода до минимально возможного уровня, в качестве которого следует считать время, требуемое процессору для работы с простейшим ОЗУ статического типа, имеющим объем, соответствующий произведению числа каналов АЦП на частоту спроса.

Известно устройство сбора данных [2], содержащее блок ввода информации, который включает в себя мультиплексор аналоговых сигналов и АЦП, двухвходовое ОЗУ, буфер, блок адресации, блок управления, регистр адреса, причем аналоговые входы блока ввода информации являются входами устройства, а выходы подключены к входам данных двухвходового ОЗУ, выходы которого через буфер соединены с шиной данных центрального процессора. Входы блока адресации подключены к адресной шине центрального процессора, а выход - к адресным входам записи двухвходового ОЗУ и к адресным входам мультиплексора блока ввода информации. Адресные входы чтения двухвходового ОЗУ соединены с выходами регистра адреса, информационные входы которого подключены к адресной шине, а управляющий вход - к управляющей шине центрального процессора. Первый выход блока управления соединен с управляющим входом блока адресации, а второй выход - с входом синхронизации двухвходового ОЗУ.

Центральный процессор осуществляет реализацию программы опроса источников сигналов и преобразования информации. Программа опроса источников сигналов представляет собой чередование во времени последовательности кодов адреса мультиплексора, который осуществляет коммутацию источников сигналов под управлением блока адресации. Сигналы с выхода мультиплексора поступают на вход АЦП, который преобразует эти сигналы в цифровые коды. Последние с выхода АЦП поступают на входы данных двухвходового ОЗУ. В соответствие с кодом адреса, поступающим из блока адресации на адресные входы записи двухвходового ОЗУ, преобразованная информация записывается в соответствующую ячейку. Центральный процессор осуществляет реализацию программы считывания информации, которая представляет собой чередование во времени последовательности кодов, записываемых в регистр адреса. Регистр адреса осуществляет адресацию двухвходового ОЗУ при считывании информации из него через буфер в шину данных. Блок управления вырабатывает импульсы записи для двухвходового ОЗУ и синхронизирует работу блока адресации. Использование двухвходового ОЗУ в данном устройстве предполагает значительные затраты времени на программное обслуживание аналого-цифрового преобразования. Снижение этих затрат времени может быть достигнуто переводом блока ввода информации в автономный режим работы. При этом центральный процессор освобождается от выполнения программы опроса источников сигналов, и исключаются затраты времени на циклы записи в блок адресации.

Предлагаемое изобретение решает задачу повышения быстродействия устройства. Техническим результатом является снижение затрат времени на программное обслуживание устройства сбора данных за счет перевода блока ввода информации в автономный режим работы при обеспечении достоверности информации в случае одновременного доступа к ОЗУ по чтению и по записи.

В устройство, содержащее блок ввода информации, двухвходовое ОЗУ, буфер, блок адресации, регистр адреса, блок управления, введены блок сравнения кодов, формирователь импульса записи, причем входы блока ввода информации являются информационными входами устройства, а информационные выходы соединены с входами данных двухвходового ОЗУ. Выходы данных последнего через буфер подключены к выходу устройства. Адресные входы блока ввода информации, адресные входы записи двухвходового ОЗУ и первая группа входов блока сравнения кодов соединены с выходами блока адресации, а выходы регистра адреса подключены к адресным входам чтения двухвходового ОЗУ и ко второй группе входов блока сравнения кодов, выход которого подключен к входу блокировки формирователя импульсов записи. Выход указанного формирователя соединен с входом синхронизации двухвходового ОЗУ. Входы регистра адреса являются адресными входами устройства, вход синхронизации указанного регистра и вход блока управления являются управляющими входами устройства. Первый выход блока управления соединен с тактовым входом блока адресации, второй выход - с входом управления блока сравнения кодов, третий выход - с входом формирователя импульса записи, четвертый выход - с входом управления буфера.

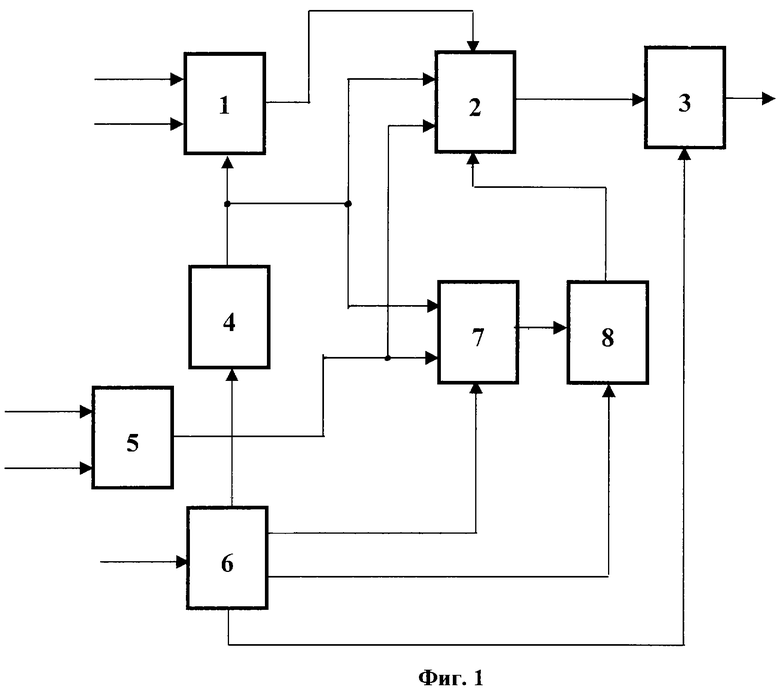

На фиг.1 представлена структурная схема устройства сбора данных, где 1 - блок ввода информации, 2 - двухвходовое ОЗУ, 3 - буфер, 4 - блок адресации, 5 - регистр адреса, 6 - блок управления, 7 - блок сравнения кодов, 8 - формирователь импульса записи.

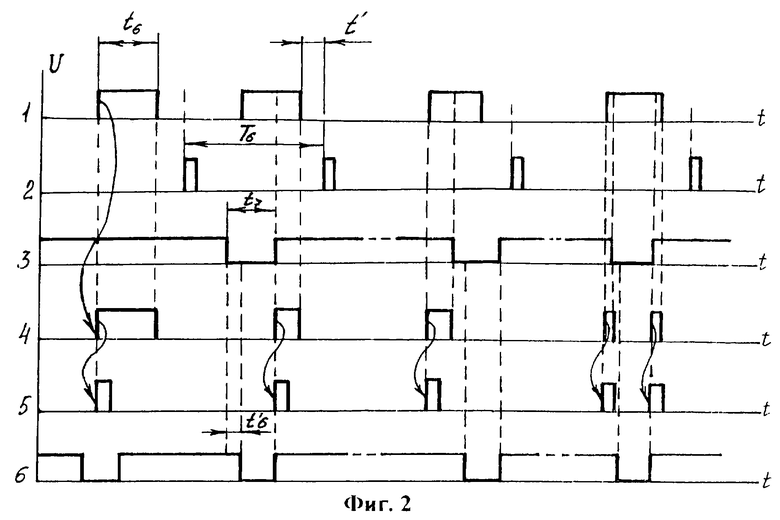

На фиг.2 представлены временные диаграммы работы, где 1 - импульс конца преобразования, 2 - импульс смены адреса, 3 - импульс блокировки, 4 - импульс записи, 5 - импульс записи в ОЗУ, 6 - импульс чтения данных.

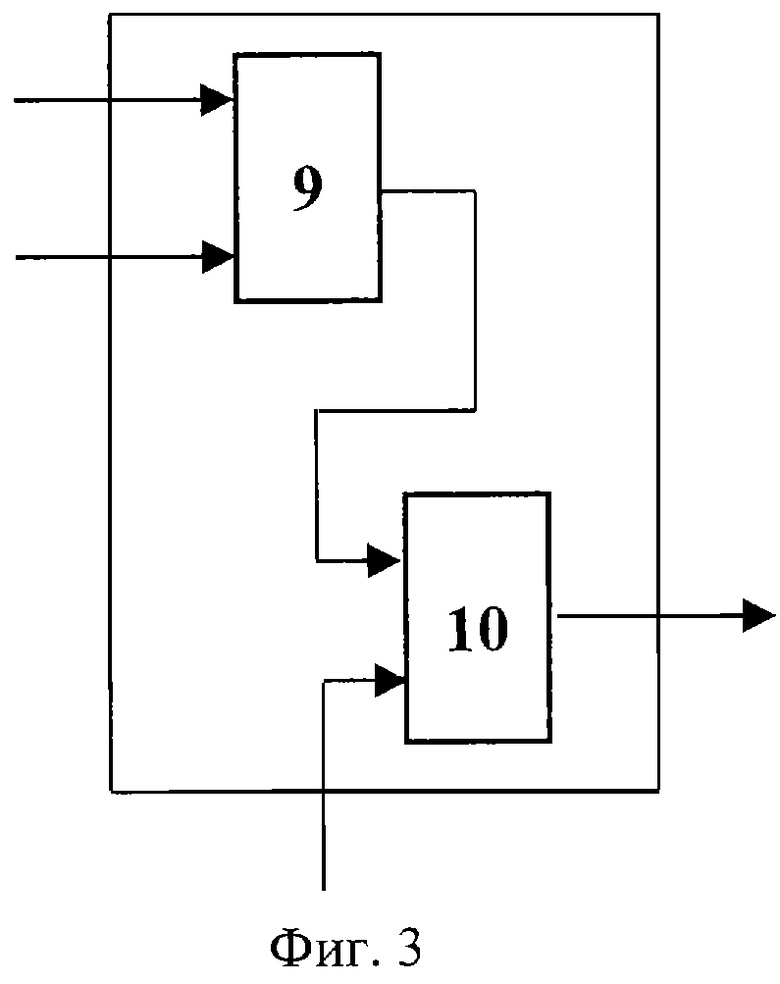

На фиг.3 представлена структурная схема блока сравнения кодов.

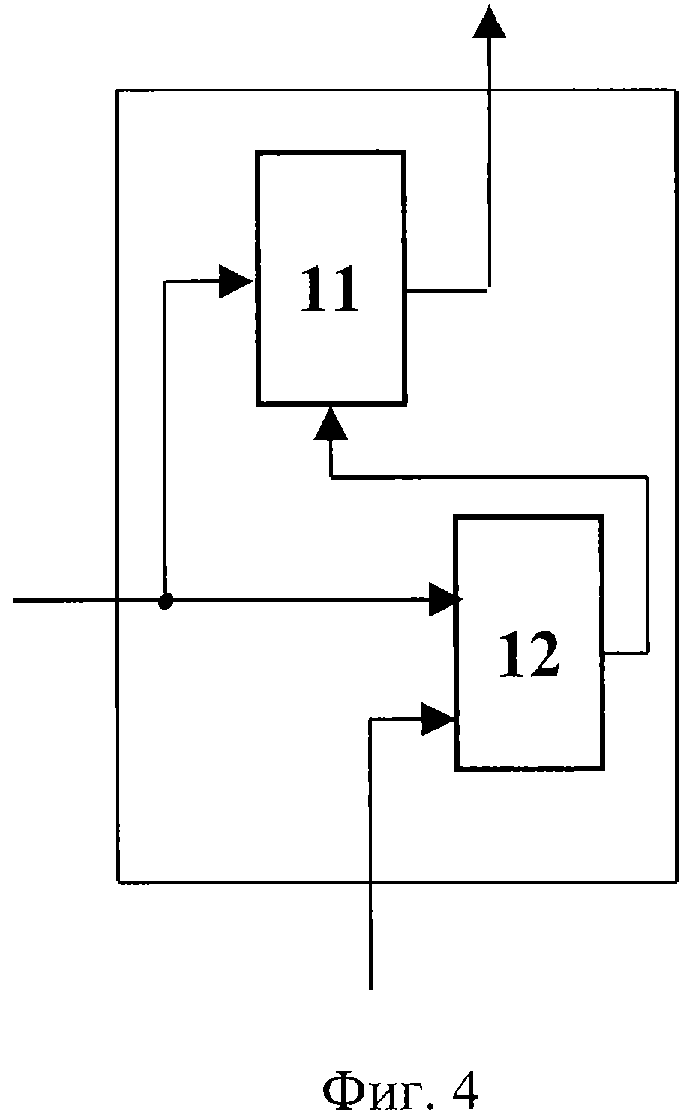

На фиг.4 представлена структурная схема формирователя импульса записи.

Как показано на фиг.1, входы блока ввода информации 1 служат для подключения к источникам сигналов. Назначение блока 1 - осуществление опроса источников сигналов, подключенных к информационным входам устройства, и преобразование сигналов в цифровой код. В состав блока 1 входят мультиплексор и АЦП (на фиг.1 не показаны). Двухвходовое ОЗУ 2 предназначено для временного хранения преобразованной информации и последующей выдачи через буфер 3 в шину данных процессора. Блок адресации 4 может быть выполнен в виде счетчика адреса. Счетчик адреса предназначен для осуществления адресации мультиплексора блока 1, двухвходового ОЗУ 2 в режиме преобразования и записи данных. Регистр адреса 5 осуществляет адресацию двухвходового ОЗУ 2 в режиме считывания данных из него под управлением центрального процессора. При этом входы регистра адреса 5 служат для подключения к адресной шине, а вход синхронизации - к управляющей шине центрального процессора. Блок управления 6 состоит из формирователя импульса смены адреса счетчика адреса блока 4, формирователя импульса чтения данных для буфера 3, осуществляющего ввод данных в центральный процессор, формирователя импульса разрешения для блока сравнения кодов 7, формирователя импульса конца преобразования (на фиг. 1 не показано). Блок сравнения кодов 7 предназначен для сравнения кодов адреса и формирования импульса блокировки для формирователя 8. Формирователь 8 предназначен для формирования импульса записи данных из блока ввода информации 1 в ОЗУ 2.

Как показано на фиг.3, блок сравнения кодов 7 может включать в себя компаратор кодов 9 и элемент ИЛИ 10, причем первая группа входов компаратора 9 является первой группой входов блока 7, а вторая группа входов - второй группой входов указанного блока. Выход компаратора 9 подключен к первому входу элемента ИЛИ 10, а второй вход этого элемента является входом управления блока сравнения кодов 7. Выход элемента ИЛИ 10 является выходом блока сравнения кодов 7.

Как показано на фиг.4, формирователь импульса записи 8 может включать в себя одновибратор 11 на основе тактируемого фронтом триггера и элемент И 12, причем вход блокировки работы одновибратора 11 и первый вход элемента И 12 объединены и являются входом блокировки формирователя 8, второй вход элемента И 12 является входом указанного формирователя. Выход одновибратора 11 является выходом формирователя 8, а вход синхронизации подключен к выходу элемента И 12.

Устройство работает следующим образом. Мультиплексор блока 1 под управлением счетчика адреса блока 4 осуществляет опрос источников сигналов. Период опроса Т6 определяется частотой тактовых импульсов с выхода блока 6, которые поступают на счетный вход указанного счетчика (фиг.2, диаграмма 2). Сигналы с выхода мультиплексора поступают на вход АЦП, который преобразует эти сигналы в цифровые коды. Каждый цифровой код сигнала записывается в соответствующую ячейку двухвходового ОЗУ 2, адресуемую с помощью счетчика блока 4. Причем код адреса соответствующей ячейки поступает на входы адреса записи указанного ОЗУ. Запись данных с выхода АЦП происходит по положительному перепаду импульса записи, поступающего с выхода формирователя 8. Центральный процессор осуществляет реализацию программы считывания информации, которая представляет собой чередование во времени последовательности кодов, записываемых в регистр адреса 5. Регистр адреса 5 осуществляет адресацию двухвходового ОЗУ 2, причем код адреса соответствующей ячейки поступает на входы адреса считывания ОЗУ 2. Считывание данных происходит при установлении кода адреса на адресных входах ОЗУ 2. Данные поступают в шину данных центрального процессора по сигналу чтения данных. Этот сигнал поступает из управляющей шины в блок 6, который формирует из него с необходимой задержкой импульс чтения данных (фиг. 2, диаграмма 6). Импульс чтения данных поступает на управляющий вход буфера и разрешает прохождение данных в шину центрального процессора. В случае несовпадения кодов адреса считывания и записи на выходе блока сравнения кодов 7 присутствует логическая "1", т.е. формирователь 8 разблокирован. Импульс конца преобразования t6 (фиг.2, диаграмма 1) с выхода блока 6 поступает на вход формирователя 8. По положительному перепаду указанного импульса формирователь 8 вырабатывает импульс записи в ОЗУ 2, который поступает на вход синхронизации ОЗУ 2. В случае совпадения кодов адреса считывания и записи блок сравнения кодов 7 вырабатывает импульс блокировки (фиг.2, диаграмма 3). Для нормальной работы устройства необходимо, чтобы длительность этого импульса t7<t6. Возможны три варианта работы устройства в случае совпадения кодов адреса. В первом случае импульс чтения данных приходит раньше импульса конца преобразования, во втором - импульс чтения данных приходит позже, в третьем - импульс чтения данных приходит во время действия импульса конца преобразования. Во всех трех случаях работы устройства компаратор кодов 9 вырабатывает сигнал разрешения, который поступает на вход элемента ИЛИ 10. На другой вход этого элемента поступает импульс чтения данных с выхода блока 6. На выходе элемента ИЛИ 10 появляется импульс блокировки (фиг. 2, диаграмма 3), который поступает на информационный вход одновибратора 11 и вход элемента И 12. На другой вход этого элемента поступает импульс конца преобразования. Элемент И 12 формирует импульс (фиг. 2, диаграмма 4), поступающий на тактирующий вход одновибратора 11. По положительному перепаду этого импульса на выходе одновибратора 11 формируется импульс записи в ОЗУ 2. Таким образом, в первом случае работы устройства сначала происходит считывание данных, а затем - запись данных в очередную ячейку ОЗУ 2. Как было указано выше, импульс чтения данных (фиг.2, диаграмма 6), формируется блоком 6 с задержкой t'6≥t'2+t'5+t'7, необходимой для установления данных на входе буфера 3, где t'2 - время срабатывания ОЗУ 2, t'5 - время срабатывания регистра адреса 5, t'7 - время срабатывания блока 7. Как показано на фиг.2, во втором случае работы устройства, сначала происходит запись данных в очередную ячейку ОЗУ 2, а затем считывание данных. В третьем случае работы устройства формируются два импульса записи в ОЗУ 2, соответственно до считывания данных и после. Причем для того чтобы данные были надежно записаны по установленному адресу, необходимо, чтобы импульс смены адреса был задержан относительно импульса конца преобразования на время t'≥t'2.

Как видно из описания и приведенных графических материалов, предлагаемое устройство за счет обеспечения автономного процесса опроса и преобразования данных позволяет разгрузить центральный процессор, исключить затраты машинного времени на обслуживание устройства и тем самым повысить быстродействие устройства сбора данных по сравнению с прототипом. Дополнительным преимуществом предлагаемого устройства являются небольшие аппаратные затраты на реализацию по сравнению, например, с устройствами, использующими прямой доступ в память центрального процессора. Предлагаемое устройство более эффективно и надежно при использовании в системах преобразования аналоговой и дискретной информации, обслуживающих большое число контролируемых объектов. Устройство сбора данных может быть реализовано с использованием недорогой элементной базы отечественного или импортного производства. Например, модуль приема частотных сигналов, использующий предлагаемое техническое решение, реализован на микросхемах серий 564, 140, 588.

Источники информации

1. Описание к авторскому свидетельству СССР 1642883.

2. Чернов В. Г. Устройства ввода-вывода аналоговой информации для цифровых систем сбора и обработки данных. - М.: Машиностроение, 1988, с.144.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для преобразования сейсморазведочной информации | 1987 |

|

SU1497599A1 |

| МИКРОЭВМ | 1991 |

|

SU1819017A1 |

| УСТРОЙСТВО ДЛЯ СБОРА И ОБРАБОТКИ ДАННЫХ | 2002 |

|

RU2218597C2 |

| УСТРОЙСТВО КОНТРОЛЯ ПРОЧНОСТИ КРЫЛА ВОЗДУШНОГО СУДНА | 2011 |

|

RU2469289C1 |

| Устройство для измерения интервалов времени | 1990 |

|

SU1739361A1 |

| Устройство для отображения информации | 1986 |

|

SU1437852A1 |

| Устройство для контроля интегральных схем | 1980 |

|

SU966699A1 |

| УСТРОЙСТВО РЕГИСТРАЦИИ СТАТИЧЕСКИХ ТЕЛЕВИЗИОННЫХ ИЗОБРАЖЕНИЙ | 1992 |

|

RU2054818C1 |

| МНОГОКАНАЛЬНАЯ ТЕЛЕМЕТРИЧЕСКАЯ СИСТЕМА СБОРА СЕЙСМИЧЕСКИХ ДАННЫХ | 2003 |

|

RU2244945C1 |

| Устройство для обработки и отображения видеоинформации | 1988 |

|

SU1748284A1 |

Изобретение относится к информационно-измерительной технике и может найти применение в составе бортовых систем преобразования аналоговой и дискретной информации, автоматизированных систем управления летательных аппаратов, а также в составе наземных автоматизированных систем контроля. Техническим результатом является снижение затрат времени на программное обслуживание устройства сбора данных. Технический результат достигается за счет того, что устройство сбора данных содержит блок ввода информации, двухфазовое ОЗУ, буфер, блок адресации, блок управления, регистр адреса, блок сравнения кодов и формирователь импульса записи. 3 з.п.ф-лы, 4 ил.

| Устройство для регистрации временных и информационных процессов | 1986 |

|

SU1363258A1 |

| Многоканальное устройство для регистрации аналоговых и цифровых сигналов | 1988 |

|

SU1564649A1 |

| УСТРОЙСТВО СБОРА, ПРЕОБРАЗОВАНИЯ И ПЕРЕДАЧИ РЕЗУЛЬТАТОВ ИЗМЕРЕНИЯ ПАРАМЕТРОВ ФИЗИЧЕСКОЙ СРЕДЫ | 1994 |

|

RU2079882C1 |

| Устройство подсчета кодов | 1987 |

|

SU1534457A1 |

| УСТРОЙСТВО для РЕГИСТРАЦИИ ОЧЕРЕДНОСТИ ДИСКРЕТНЫХ СОБЫТИЙ ВО ВРЕМЕНИ | 0 |

|

SU363976A1 |

| Устройство для цифровой регистрации электрических сигналов | 1987 |

|

SU1472920A1 |

| RU 94028792 A1, 20.05.1996. | |||

Авторы

Даты

2003-12-10—Публикация

2002-01-08—Подача