Изобретение относится к области радиотехники и связи и может быть использовано в качестве входных и промежуточных каскадов аналоговых микросхем различного функционального назначения (высокочастотных и сверхвысокочастотных усилителях, драйверах линий связи, фильтрах и т.д.).

Известны высокочастотные усилители на основе классических дифференциальных каскадов [1-25], которые стали основой построения многих аналоговых узлов современных систем связи. Проблема улучшения их параметров относится к числу одной из актуальных проблем современной аналоговой микросхемотехники.

В рамках собственных программ развития ряд ведущих микроэлектронных фирм, в т.ч. российских, начинают использовать технологическое оборудование для 0,25 мкм SiGe-технологии SGB25VD, способное в рамках единого цикла изготовить высококачественные гетеропереходы. Это позволяет реализовать субмикронные транзисторы Х диапазона, а также использовать экономичные режимы для СВЧ интегральных схем относительно высокого уровня интеграции. Однако технология SGB25VD накладывает дополнительные и существенные для схемотехники аналоговых микросхем ограничения, выражающиеся в невозможности использования комплементарных транзисторов и относительно низковольтных режимов их работы (Uкэ.max=2,9 В или напряжение двуполярного питания ±1,5 В). Создание IP блоков для SiGe технологии SGB25VD является (наряду с ее освоением) важнейшей задачей для зарубежных и отечественных центров проектирования аналоговых микросхем. Предлагаемое изобретение относится к данному направлению развития микроэлектроники.

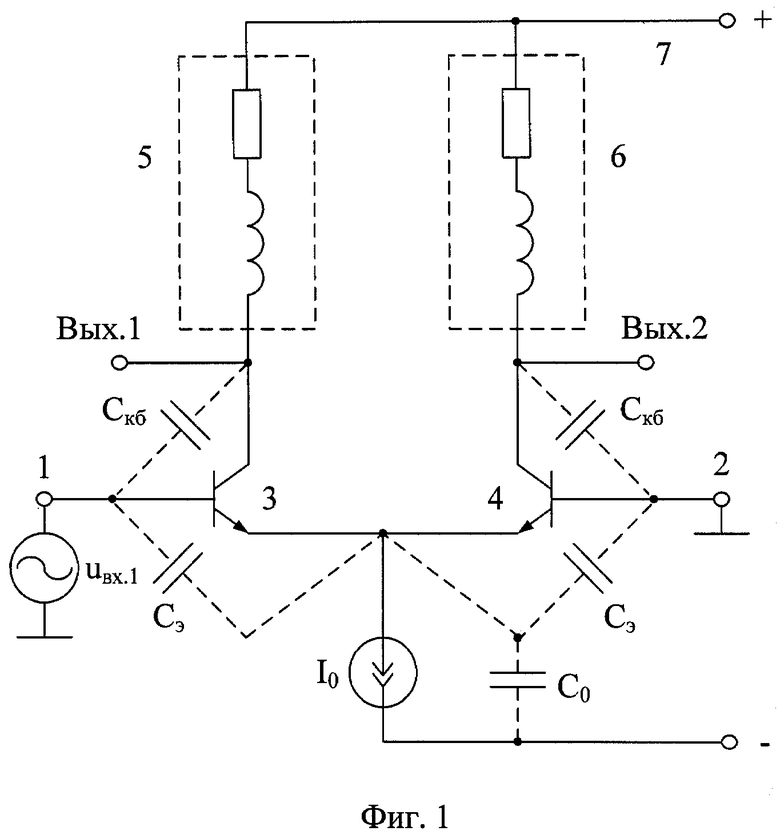

Основой современных ВЧ и СВЧ усилительных каскадов является классическая схема дифференциального усилителя фиг.1, которая используется во многих аналоговых узлах систем связи [1-25]. Однако с повышением диапазона рабочих частот до единиц-десятков гигагерц в этой схеме начинают проявляться погрешности преобразования сигналов, обусловленные особенностями ее архитектуры. В диапазоне СВЧ классический ВДУ не обеспечивает, в частности, качественное преобразование входного напряжения uвх в два противофазных выходных напряжения.

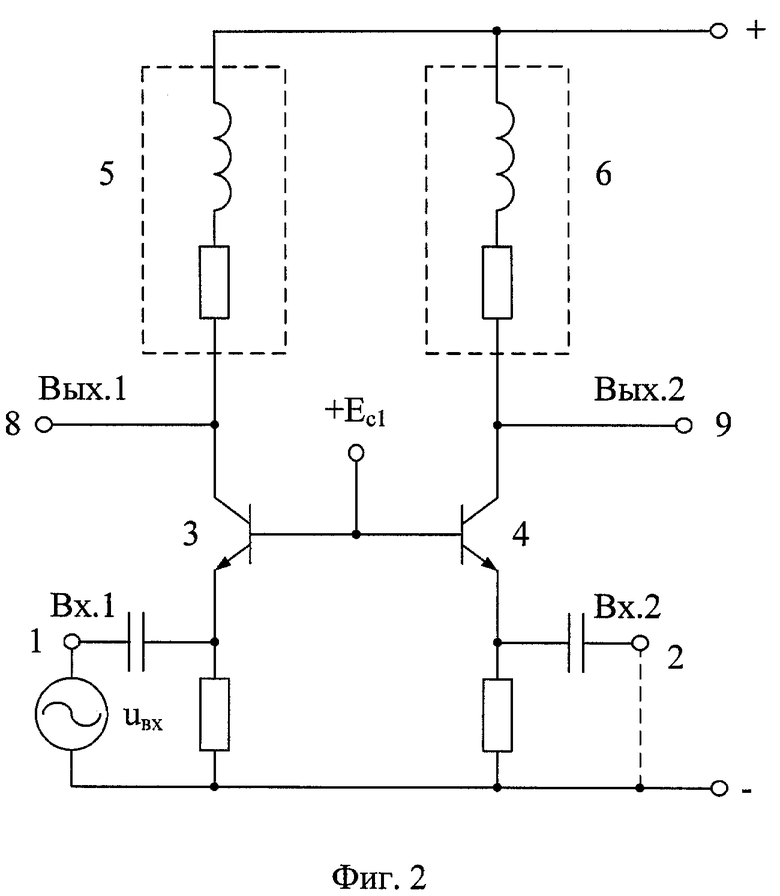

Известны также каскадные дифференциальные усилители [26-34] (фиг.2), у которых входной сигнал uвх подается в эмиттерную цепь входных транзисторов 3 и 4, включенных по схеме с общей базой. Это более высокочастотные каскады и они также применяются в СВЧ диапазоне, обеспечивая малые входные сопротивления. Однако ВДУ фиг.2 является, по существу, псевдодифференциальным усилителем, так как у него выходное напряжение, например на правом выходе, не зависит от напряжения на левом входе. То есть схема фиг.2 не может применяться в качестве преобразователя одного входного напряжения uвх в два противофазных выходных напряжения - данная функция в ВДУ фиг.2 не реализуется.

Ближайшим прототипом заявляемого устройства является высокочастотный дифференциальный усилитель, рассмотренный в патентной заявке США 2005/0162229. Кроме этого, данная архитектура присутствует в патентах [1-25], а также патенте №5378997 и патентной заявке США 2005/0093628.

Существенный недостаток известного устройства (фиг.1) состоит в том, что его коэффициенты передачи по напряжению (Ку) со входа Вх.1 (или входа Вх.2) на первый Вых.1 и второй Вых.2 выходы в диапазоне высоких частот (1÷10 ГГц) оказываются неодинаковы из-за повышенного влияния на Ку емкостей эмиттерного (Сэ) и коллекторного (Скб) р-n переходов, а также выходной емкости С0 источника опорного тока I0. Это не позволяет выполнить на базе ВДУ фиг.1 достаточно важные функциональные узлы систем связи СВЧ диапазона (согласующие каскады перемножителей и смесителей сигналов, управляемые усилители, элементы ФАПЧ и т.д.). Действительно, на паразитную передачу входного сигнала uвx.1 на выход Вых.1 существенно влияет емкость Скб транзистора 3, а канал передачи uвx.1 на выход Вых.2 шунтируется емкостью С0.

Таким образом, ВДУ-прототипу фиг.1 присущи принципиальные недостатки, связанные с обеспечением высокой идентичности коэффициентов усиления Ку по выходу Вых.1 и по выходу Вых.2 в СВЧ диапазоне. При этом данное противоречие не устраняется в ВДУ на основе известных дифференциальных каскадов, имеющих так называемую общую эмиттерную цепь (фиг.1). С другой стороны известные и более высокочастотные ВДУ с общей базовой цепью (фиг.2) также не позволяют реализовать на их основе качественное преобразование одного входного напряжения в два противофазных выходных сигнала.

Основная задача предлагаемого изобретения - расширение частотного диапазона высокочастотного дифференциального усилителя в режиме преобразования одного входного напряжения в два противофазных выходных напряжения.

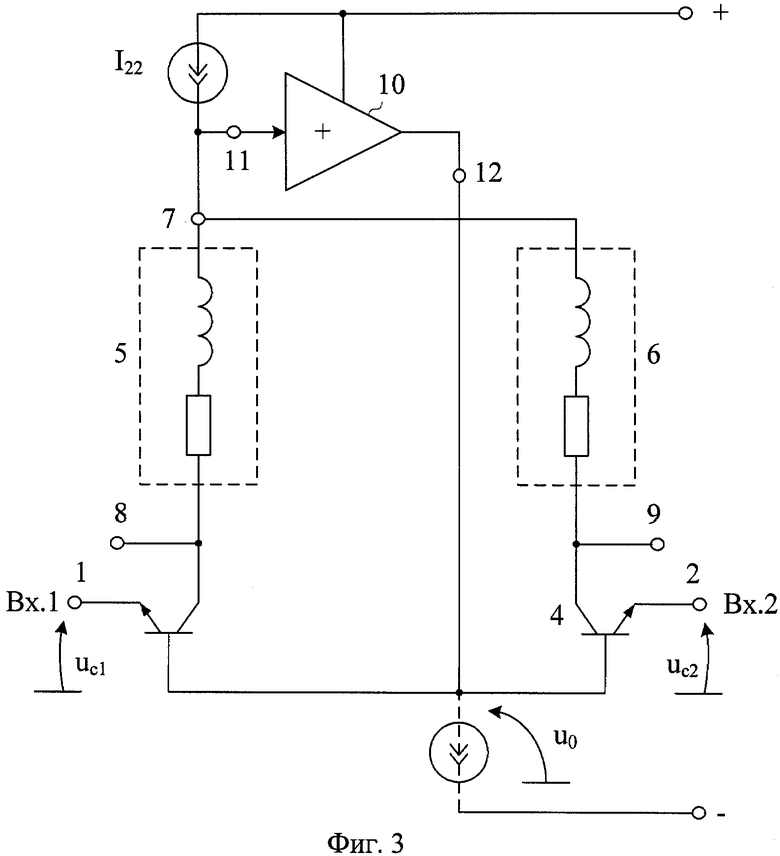

Поставленная задача достигается тем, что в известном устройстве фиг.1, содержащем первый 3 и второй 4 входные транзисторы, первый 5 и второй 6 импедансы нагрузки, имеющие общий узел 7, связанные с соответствующими первым 8 и вторым 9 выходами дифференциального усилителя, а также коллекторами первого 3 и второго 4 входных транзисторов, предусмотрены новые элементы и связи - в схему введен неинвертирующий усилитель тока 10, вход которого 11 соединен с общим узлом 7 первого 5 и второго 6 импедансов нагрузки и первым дополнительным двухполюсником I22, а выход 12 - подключен к объединенным базам первого 3 и второго 4 входных транзисторов.

На чертежах фиг.1 (прототип) и фиг.2 приведены схемы известных высокочастотных дифференциальных усилителей [1-34].

На чертеже фиг.3 представлена схема заявляемого ВДУ в соответствии с п.1 формулы изобретения.

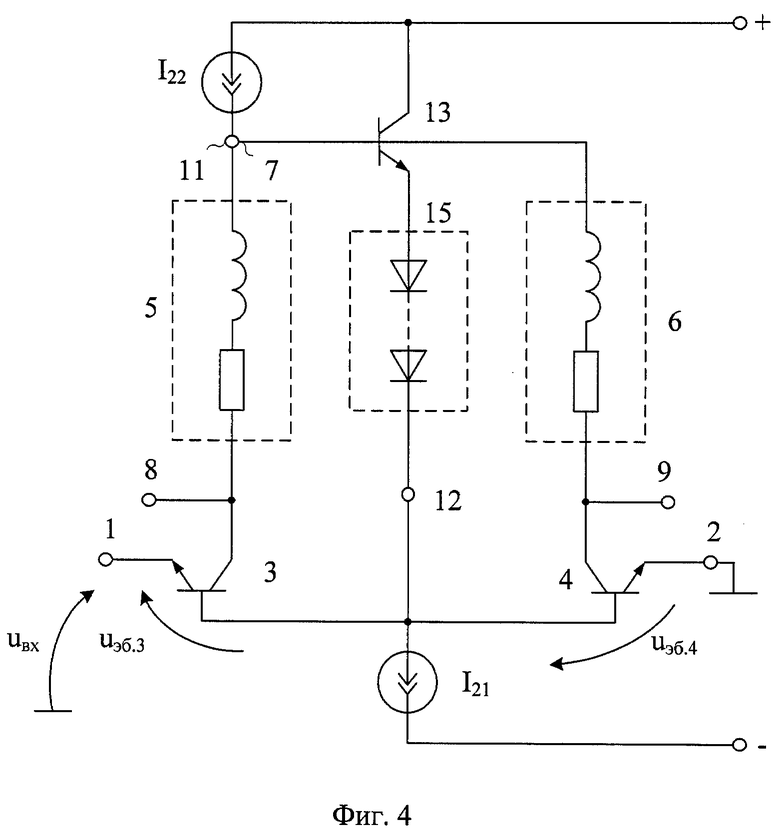

Схема фиг.4 соответствует п.2 формулы изобретения для случая, когда неинвертирующий усилитель тока реализован на транзисторе 13.

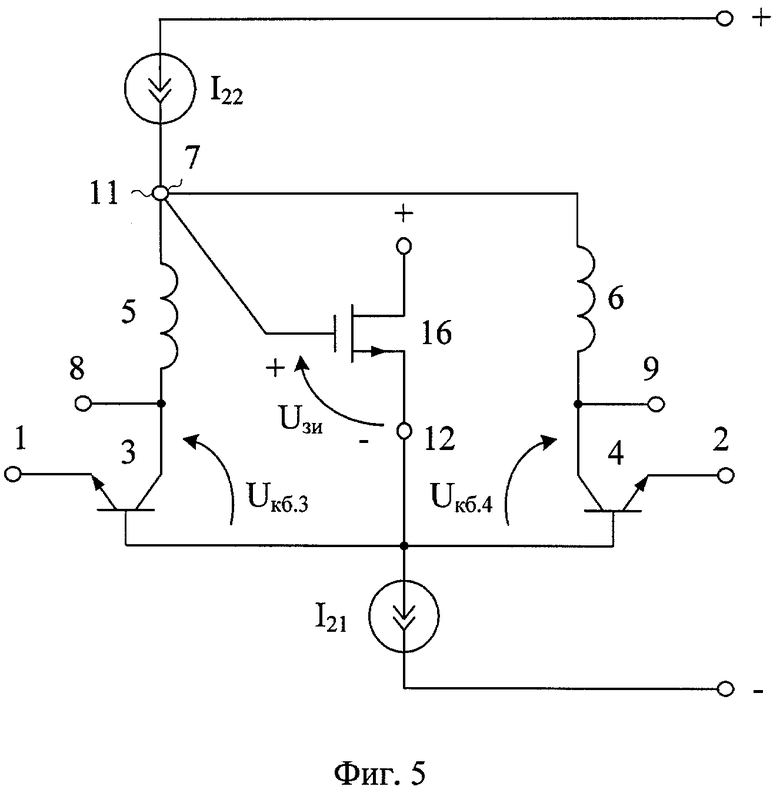

Чертеж фиг.5 соответствует п.3 и п.4 формулы изобретения.

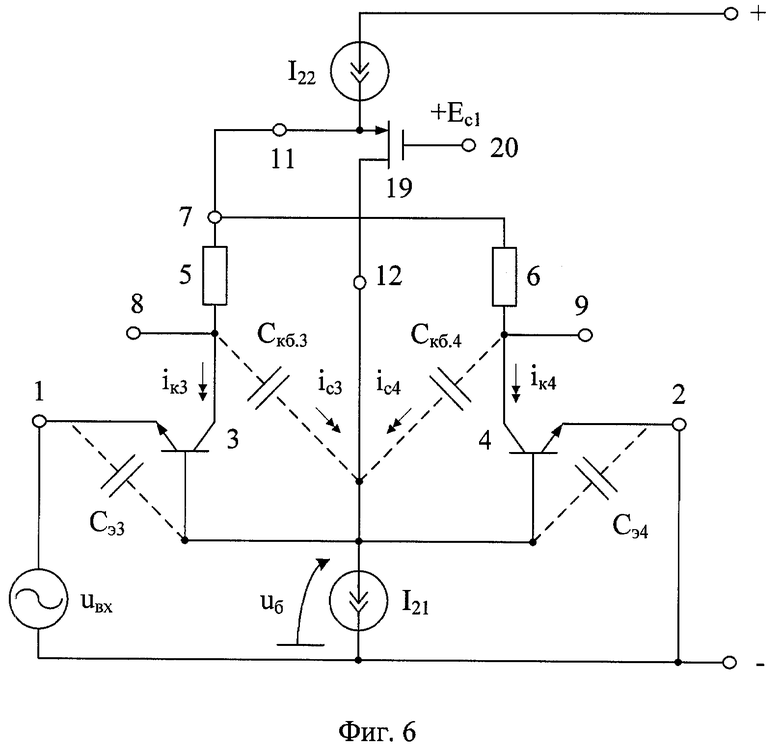

Схема фиг.6 соответствует п.5 формулы изобретения.

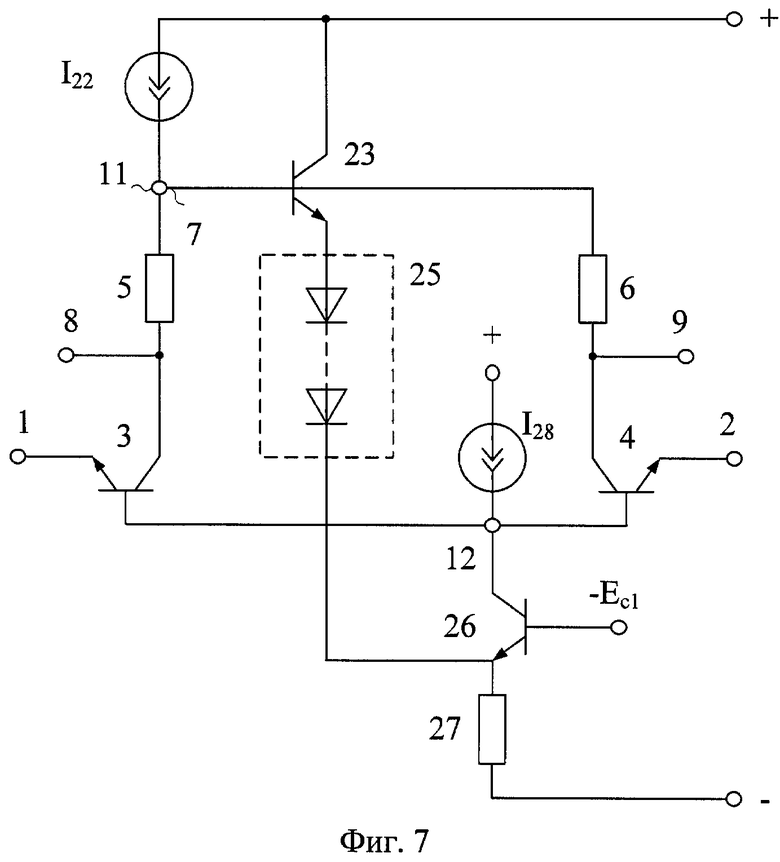

Схема ВДУ по п.6 формулы изобретения приведена на чертеже фиг.7.

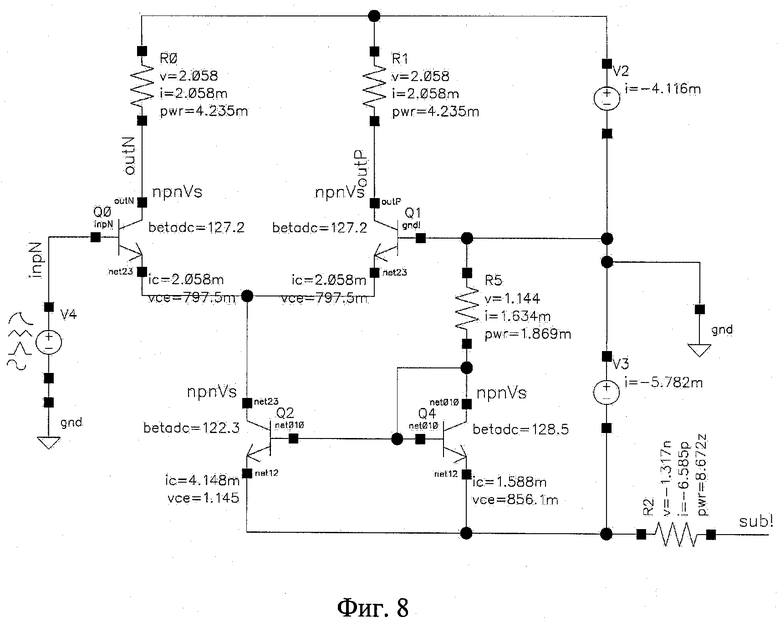

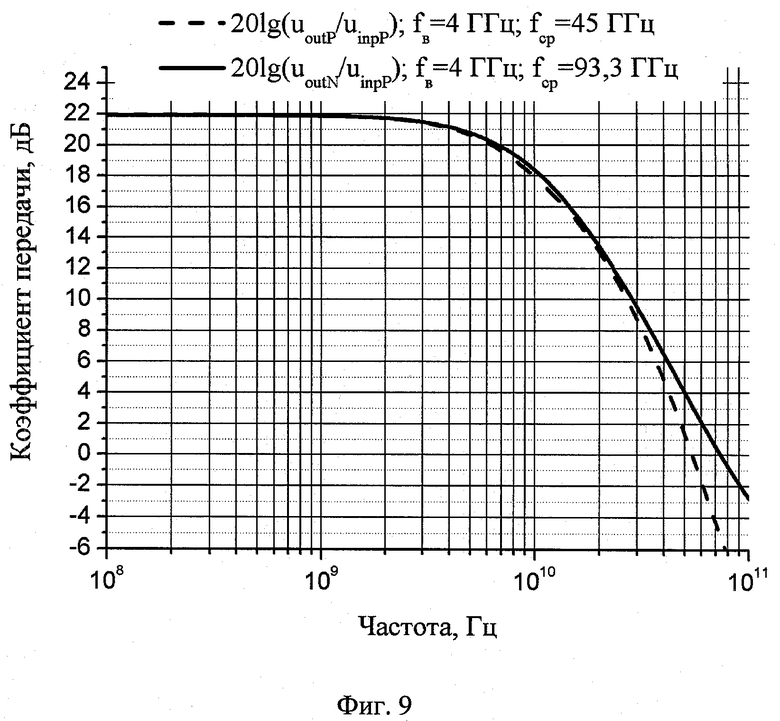

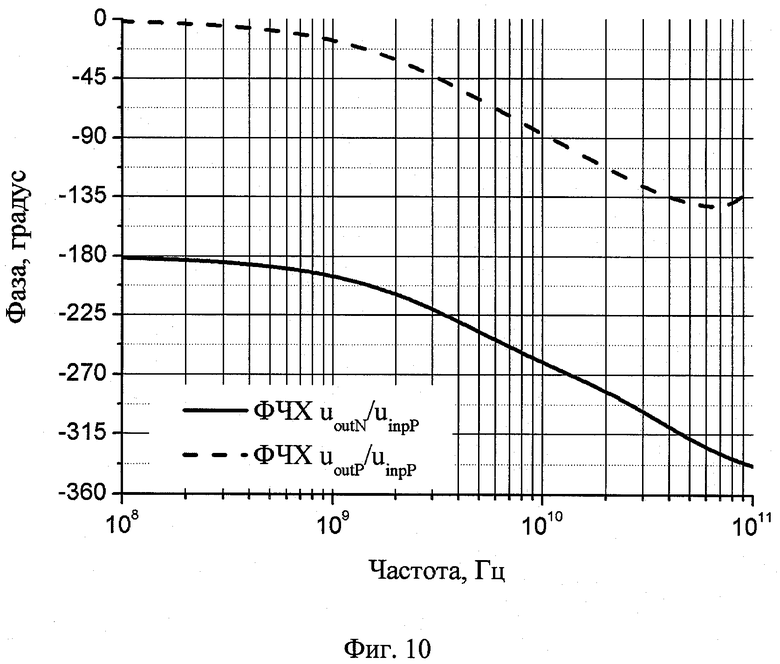

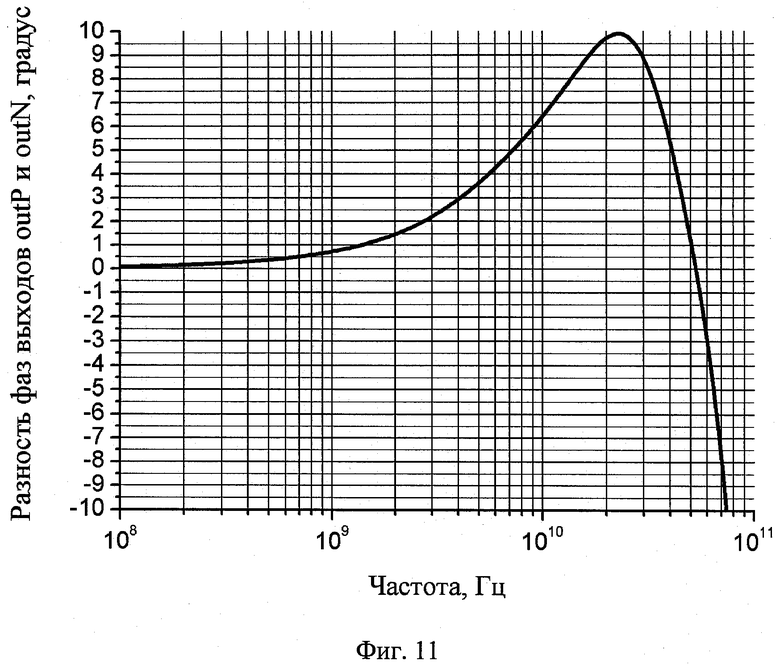

На чертеже фиг.8 представлена схема ВДУ-прототипа в среде компьютерного моделирования Cadance на моделях интегральных транзисторов IHP, а на чертежах фиг.9, фиг.10 и фиг.11 - зависимости его коэффициентов передачи по первому и второму выходам от частоты сигнала (фиг.9), фазы выходных напряжений от частоты (фиг.10) и разности фаз выходных сигналов от частоты (фиг.11).

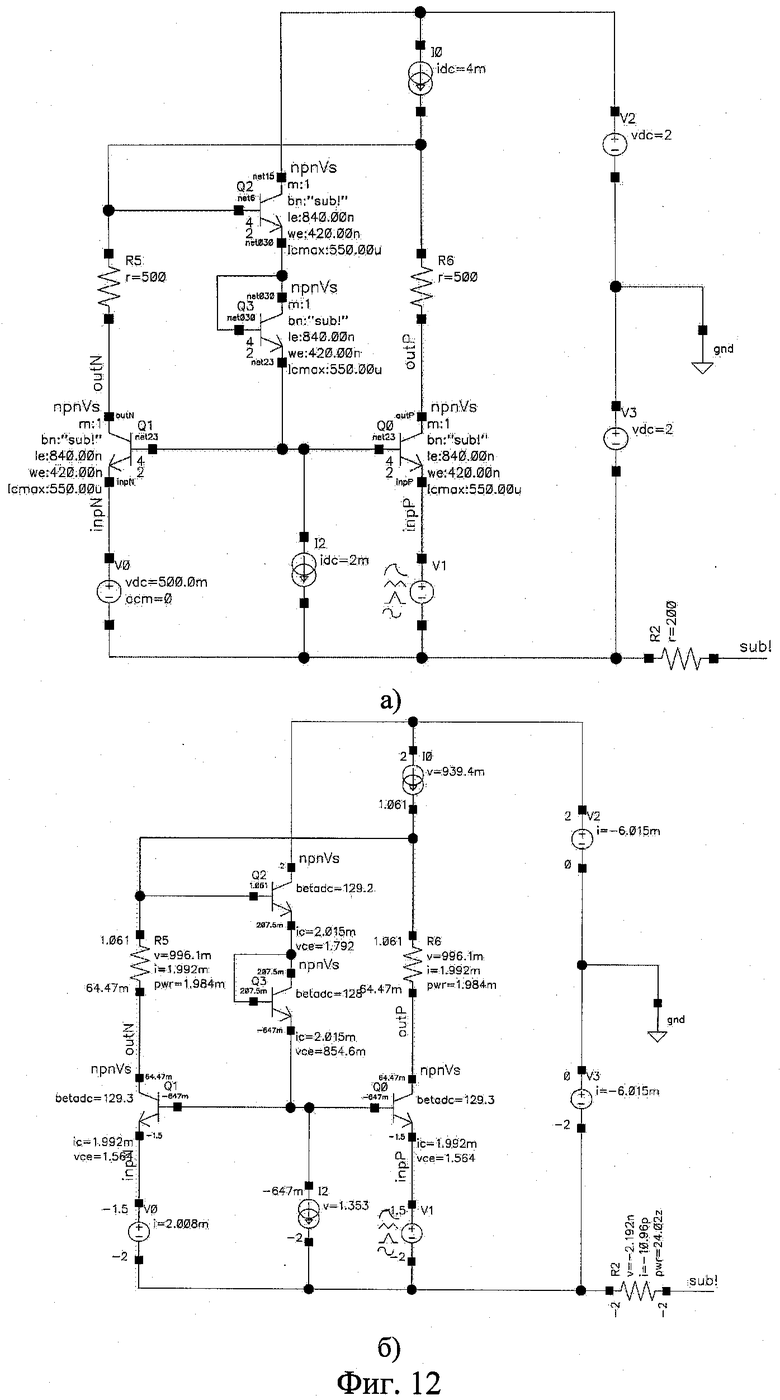

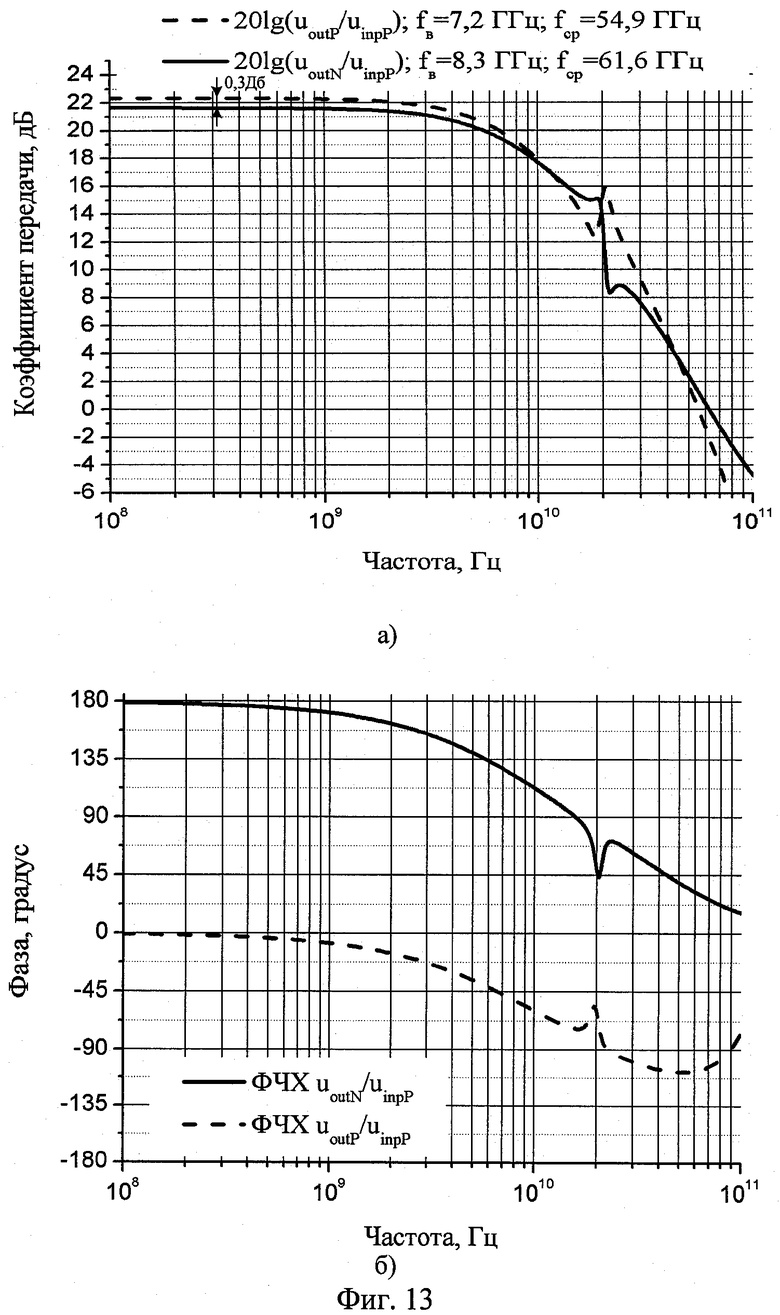

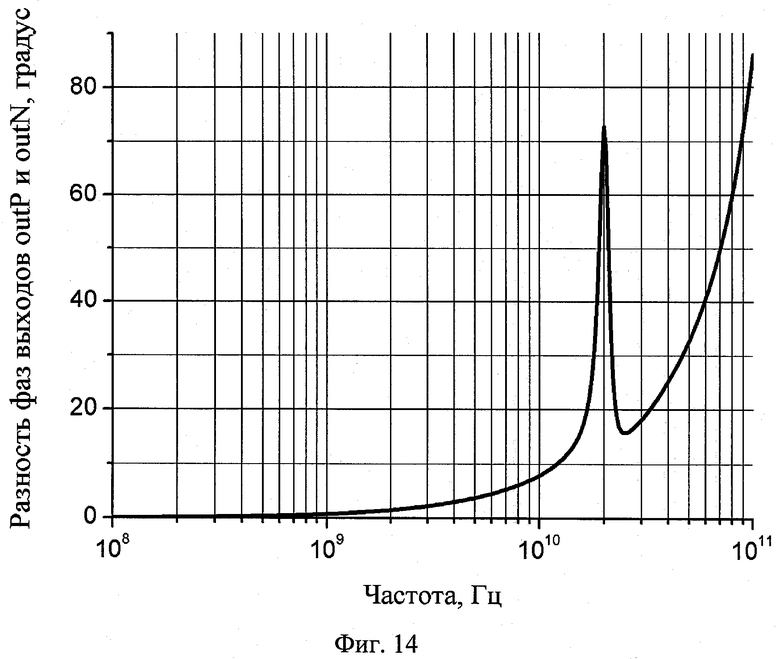

На чертеже фиг.12 представлена схема заявляемого (фиг.4) ВДУ (фиг.12а) и координаты его статического режима (фиг.12б) в среде компьютерного моделирования Cadance на моделях интегральных транзисторов IHP, а на чертежах фиг.13 и фиг.14 - зависимости его коэффициентов передачи по первому и второму выходам от частоты сигнала (фиг.13а), фазы выходных напряжений от частоты (фиг.13б) и разности фаз выходных сигналов от частоты (фиг.14).

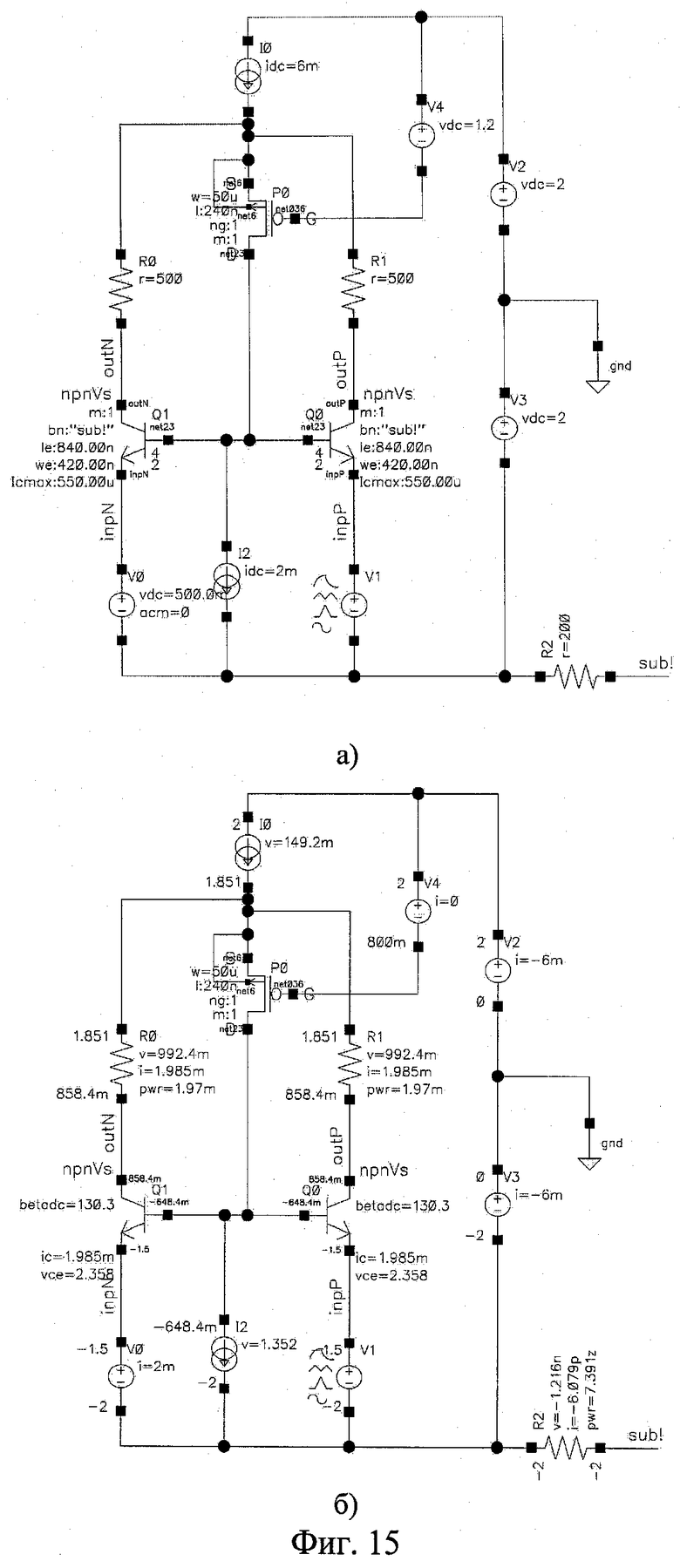

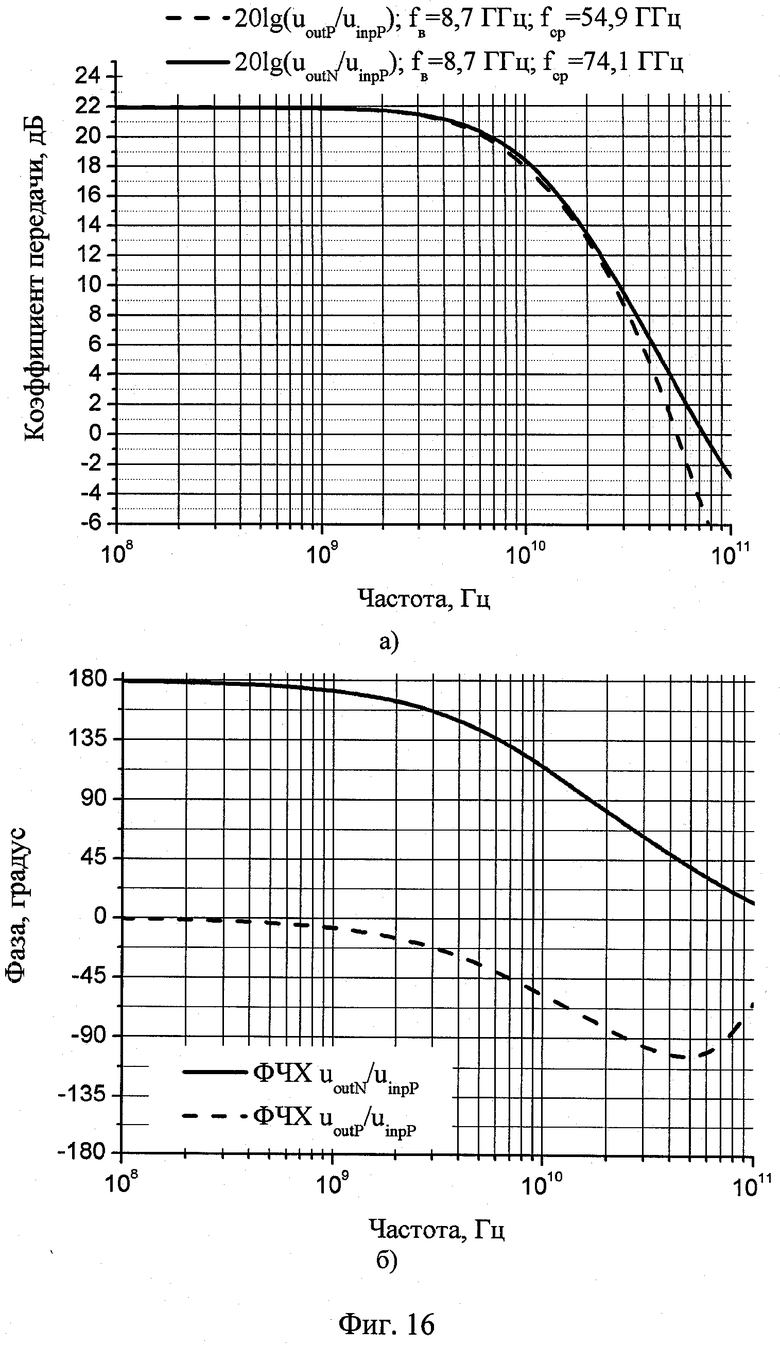

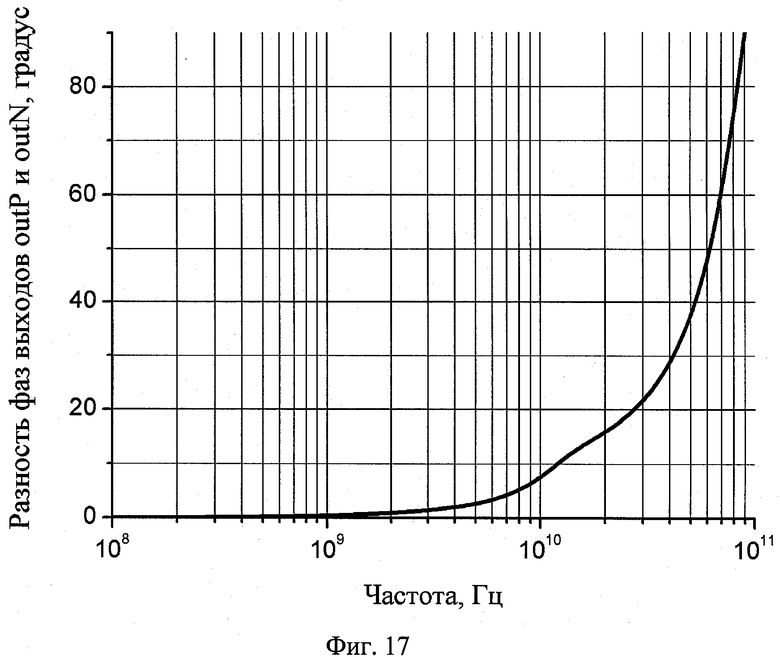

На чертежах фиг.15 представлена схема заявляемого (фиг.6) ВДУ (фиг.15а) и координаты его статического режима (фиг.15б) в среде компьютерного моделирования Cadance на моделях интегральных транзисторов IHP, а на чертежах фиг.16 и фиг.17 - зависимости его коэффициентов передачи по первому и второму выходам от частоты сигнала (фиг.16а), фазы выходных напряжений от частоты (фиг.16б) и разности фаз выходных сигналов от частоты (фиг.17).

Предлагаемый высокочастотный дифференциальный усилитель фиг.3 содержит первый 1 и второй 2 входы, первый 3 и второй 4 входные транзисторы, первый 5 и второй 6 импедансы нагрузки, имеющие общий узел 7, связанные с соответствующими первым 8 и вторым 9 выходами дифференциального усилителя, а также коллекторами первого 3 и второго 4 входных транзисторов. В схему введен неинвертирующий усилитель тока 10, вход которого 11 соединен с общим узлом 7 первого 5 и второго 6 импедансов нагрузки и первым дополнительным двухполюсником I22, а выход 12 - подключен к объединенным базам первого 3 и второго 4 входных транзисторов.

В устройстве по п.2 формулы изобретения (фиг.4) неинвертирующий усилитель тока 10 содержит первый основной транзистор 13, база которого соединена с входом 11 неинвертирующего усилителя тока, а эмиттер через цепь согласования потенциалов 15 связан с выходом 12 неинвертирующего усилителя тока (10).

В устройстве по п.3 формулы изобретения (фиг.5) неинвертирующий усилитель тока 10 содержит полевой транзистор 16, затвор которого соединен с входом 11 неинвертирующего усилителя тока 10, а исток связан с выходом 12 неинвертирующего усилителя тока 10.

В устройстве по п.4 формулы изобретения (фиг.5) к выходу 12 неинвертирующего усилителя тока 10 подключен вспомогательный двухполюсник I21.

В устройстве по п.5 формулы изобретения (фиг.6) неинвертирующий усилитель тока 10 содержит второй основной транзистор 19, затвор которого подключен к источнику напряжения смещения 20, сток соединен с выходом 12 неинвертирующего усилителя тока 10 и со вспомогательным двухполюсником I21, а исток связан с входом 11 неинвертирующего усилителя тока 10.

В устройстве по п.6 формулы изобретения (фиг.7) неинвертирующий усилитель тока 10 содержит третий основной транзистор 23, база которого подключена к входу 11 неинвертирующего усилителя тока 10, эмиттер через цепь согласования потенциалов 25 соединен с эмиттером транзистора 26 источника опорного тока и резистором 27, а коллектор подключен к выходу 12 неинвертирующего усилителя тока 10 и двухполюснику I28.

Описание чертежей фиг.8-17 дано на стр.6.

Рассмотрим работу предлагаемого устройства на примере схемы фиг.6.

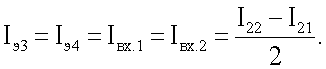

Статический режим транзисторов 3 и 4 ВДУ фиг.6 определяется двухполюсниками I21 и I22 и не зависит от синфазного напряжения на входах 1 и 2:

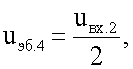

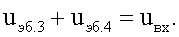

Если на вход 1 подается небольшое положительное напряжение uвх, то это вызывает уменьшение тока эмиттера (коллектора iк3) транзистора 3 и тока, протекающего в первом импедансе нагрузки 5. Особенность схемы фиг.6 состоит в том, что сумма переменных токов первого 5 и второго 6 импедансов нагрузки должна быть постоянна (iк3+iк4=0), что обеспечивается отрицательной обратной связью по синфазному сигналу. Поэтому уменьшение тока через двухполюсник 5 будет сопровождаться увеличением тока через двухполюсник 6 за счет увеличения напряжения на базе транзистора 4. В свою очередь, увеличение напряжения на базе транзистора 5 (uб≈uBX/2) вызывает увеличение тока эмиттера и коллектора транзистора 5 и, как следствие, тока в двухполюснике нагрузки 6.

Таким образом, увеличение uвх приводит к уменьшению тока в первом 5 импедансе нагрузки и увеличению тока через двухполюсник 6. Данные приращения токов оказываются одинаковыми, так как приращения напряжений эмиттер-база транзисторов 3 и 4 удовлетворяют условиям:

На высоких частотах емкости Скб.3, Скб.4 оказывают одинаковое влияние (в отличие от ВДУ-прототипа фиг.1) на амплитудно-частотную характеристику коэффициента усиления как по первому 8, так и по второму 9 выходам. Как следствие, в заявляемой схеме в связи с симметричным включением (относительно выходов 8 и 9) емкостей Скб.3 и Скб.4 расширяется частотный диапазон, в пределах которого сохраняется идентичность коэффициентов передачи входного напряжения uвх к узлам 8 и 9.

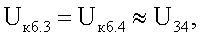

В схеме фиг.5 в качестве импедансов нагрузки 5 и 6 применяются индуктивности. Поэтому статическое падение напряжения на элементах 5 и 6 мало и необходимый статический режим транзисторов 3 и 4 по напряжению коллектор-база может быть установлен полевым транзистором 16

где U34 - напряжение затвор-исток полевого транзистора 16.

В заключение следует отметить, что предлагаемый дифференциальный усилитель относится к подклассу «полностью» дифференциальных усилителей - ВДУ с общей базовой цепью, которые в отличие от [25-34] имеют такие же свойства по низкочастотному усилению, ослаблению синфазных сигналов, диапазону активной работы и т.п., что и классические ВДУ с общей эмиттерной цепью [1-24]. Однако при этом заявляемый ВДУ имеет в СВЧ диапазоне меньшие погрешности преобразования сигналов и, кроме этого, характеризуется малым входным сопротивлением для дифференциального сигнала (25÷50 Ом).

Компьютерное моделирование (например, ВДУ фиг.13) показывает, что предлагаемый дифференциальный усилитель обеспечивает усиление до частоты 8,7 ГГц (по уровню -3 дБ) по первому и второму выходам, что более чем в два раза выше, чем в ВДУ-прототипе фиг.8. Схема фиг.13 имеет также и более высокие значения частоты единичного усиления.

Таким образом, предлагаемое схемотехническое решение позволяет использовать СВЧ SiGe-транзисторы техпроцесса SGB25VD с относительно низким напряжением питания 2,9 В в структуре не только различных аналоговых устройств, но и СФ блоков систем на кристалле. Этот важный результат расширяет область практического использования SGB25VD технологии и, следовательно, повышает технико-экономические показатели микроэлектронных изделий. Так, например, создание новой (под указанную технологию) схемотехники широкодиапазонных операционных усилителей позволит не только повысить качественные показатели СВЧ фильтров, квадратурных модуляторов, демодуляторов и других устройств нового поколения, образующих СФ блоки СВЧ РЭА, так и создать новую номенклатуру ИС широкого функционального применения.

БИБЛИОГРАФИЧЕСКИЙ СПИСОК

1. Патентная заявка Японии JP 200440465 А (фиг.4).

2. Патент США №7113744 В1.

3. Патент США №3693108.

4. Патент США №6157256 (фиг.4).

5. Патент США №5365192.

6. Патент США №6380777.

7. Патент США №7164321.

8. Патент США №7170349.

9. Патент США №7205836.

10. Патент США №7209842 (фиг.3).

11. Патентная заявка США №2006/0028275.

12. Патентная заявка США №2006/0049874.

13. Патентная заявка США №2006/0220736 (фиг.4).

14. Патентная заявка США №2004/0246051 (фиг.1).

15. Патентная заявка США №2004/0189387 (фиг.1).

16. Патент ЕР 1480333 А2.

17. Патент США №4524331.

18. Патент США №6236524.

19. Патент США №6765441.

20. Патентная заявка США №2007/0205829 А1.

21. Патентная заявка США №2007/0139115.

22. Патентная заявка США №2008/0012640.

23. Патентная заявка США №2006/0197597.

24. Патент США №6922108.

25. Патент Японии №2003037458.

26. Патентная заявка США №2005/0140443.

27. Патент США №5973562.

28. Патент США №4887047.

29. Патентная заявка Японии JP 2001308658.

30. Патент США №4277756.

31. Патент США №4065724.

32. Патент RE 30/587.

33. Патент США №4232271.

34. Патент США №5497123.

| название | год | авторы | номер документа |

|---|---|---|---|

| ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ | 2008 |

|

RU2374760C1 |

| ВЫСОКОЧАСТОТНЫЙ МУЛЬТИДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ | 2008 |

|

RU2374759C1 |

| ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ С ПОВЫШЕННЫМ ВХОДНЫМ СОПРОТИВЛЕНИЕМ | 2009 |

|

RU2413356C1 |

| КАСКОДНЫЙ ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ | 2008 |

|

RU2390912C2 |

| ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ С ПОВЫШЕННЫМ КОЭФФИЦИЕНТОМ УСИЛЕНИЯ | 2009 |

|

RU2416147C1 |

| ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ С ПОВЫШЕННЫМ КОЭФФИЦИЕНТОМ УСИЛЕНИЯ | 2009 |

|

RU2416146C1 |

| ФАЗОРАСЩЕПИТЕЛЬ ВЫСОКОЧАСТОТНОГО СИГНАЛА | 2011 |

|

RU2439782C1 |

| ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ С ПОВЫШЕННЫМ КОЭФФИЦИЕНТОМ УСИЛЕНИЯ ПО НАПРЯЖЕНИЮ | 2010 |

|

RU2419186C1 |

| УСИЛИТЕЛЬ ПЕРЕМЕННОГО ТОКА С ПАРАФАЗНЫМ ВЫХОДОМ | 2009 |

|

RU2419962C1 |

| ИЗБИРАТЕЛЬНЫЙ УСИЛИТЕЛЬ | 2011 |

|

RU2475945C1 |

Изобретение относится к области радиотехники и связи и может быть использовано в качестве входных и промежуточных каскадов аналоговых микросхем различного функционального назначения (высокочастотных и сверхвысокочастотных усилителях, драйверах линий связи, фильтрах и т.д.). Технический результат: расширение частотного диапазона в режиме преобразования одного входного напряжения в два противофазных выходных напряжения. Высокочастотный дифференциальный усилитель (ДУ) содержит первый (1) и второй (2) входы, первый (3) и второй (4) входные транзисторы (Т), первый (5) и второй (6) импедансы нагрузки, имеющие общий узел (7), связанные с соответствующими первым (8) и вторым (9) выходами ДУ, а также коллекторами (стоками) первого (3) и второго (4) входных Т. В схему введен неинвертирующий усилитель тока (10), вход которого (11) соединен с общим узлом (7) первого (5) и второго (6) импедансов нагрузки и первым дополнительным двухполюсником (I22); a выход (12) подключен к объединенным базам первого (3) и второго (4) входных Т. 5 з.п. ф-лы, 17 ил.

1. Высокочастотный дифференциальный усилитель, содержащий первый (1) и второй (2) входы, первый (3) и второй (4) входные транзисторы, первый (5) и второй (6) импедансы нагрузки, имеющие общий узел (7), связанные с соответствующими первым (8) и вторым (9) выходами дифференциального усилителя, а также коллекторами (стоками) первого (3) и второго (4) входных транзисторов, отличающийся тем, что в схему введен неинвертирующий усилитель (10), вход которого (11) соединен с общим узлом (7) первого (5) и второго (6) импедансов нагрузки и первым дополнительным двухполюсником (I22), а выход (12) подключен к объединенным базам первого (3) и второго (4) входных транзисторов.

2. Устройство по п.1, отличающееся тем, что неинвертирующий усилитель (10) содержит первый основной транзистор (13), база которого соединена со входом (11) неинвертирующего усилителя тока (10), а эмиттер через цепь согласования потенциалов (15) связан с выходом (12) неинвертирующего усилителя тока (10).

3. Устройство по п.1, отличающееся тем, что неинвертирующий усилитель тока (10) содержит полевой транзистор (16), затвор которого соединен со входом (11) неинвертирующего усилителя тока (10), а исток связан с выходом (12) неинвертирующего усилителя тока (10).

4. Устройство по п.2 или 3, отличающееся тем, что к выходу (12) неинвертирующего усилителя тока (10) подключен первый вспомогательный двухполюсник (I21).

5. Устройство по п.1, отличающееся тем, что неинвертирующий усилитель тока (10) содержит второй основной транзистор (19), затвор которого подключен к источнику напряжения смещения (20), сток соединен с выходом (12) неинвертирующего усилителя тока (10) и со вспомогательным двухполюсником (I21), а исток связан со входом (11) неинвертирующего усилителя тока (10).

6. Устройство по п.1, отличающееся тем, что неинвертирующий усилитель тока (10) содержит третий основной транзистор (23), база которого подключена ко входу (11) неинвертирующего усилителя тока (10), эмиттер через цепь согласования потенциалов (25) соединен с эмиттером транзистора (26) источника опорного тока и резистором (27), а коллектор подключен к выходу (12) неинвертирующего усилителя тока (10) и двухполюснику (I28).

| US 3972003 A, 27.07.1976 | |||

| Повторитель тока | 1987 |

|

SU1529410A1 |

| Способ обработки целлюлозных материалов, с целью тонкого измельчения или переведения в коллоидальный раствор | 1923 |

|

SU2005A1 |

| US 6417737 B1, 09.07.2002 | |||

| US 3895307 A, 15.07.1975. | |||

Авторы

Даты

2010-08-10—Публикация

2008-03-13—Подача