Область техники, к которой относится изобретение

Настоящее изобретение относится к области модулей защиты, содержащих, по меньшей мере, один процессор и элементы памяти и обычно выполненных в форме электронных смарт-карт. Такие модули могут быть контактными или бесконтактными и используются в различных приложениях, использующих безопасные транзакции, например операции платежей, обмен конфиденциальной информацией или контроль доступа.

Уровень техники

Как хорошо известно специалистам в данной области, модуль защиты может, по существу, быть выполнен в одной из трех различных форм. В первом варианте модуль может быть выполнен в виде микропроцессорной карты, электронной смарт-карты или, в более общем случае, электронного модуля (имеющего форму ключа, жетона и т.п.). Модули такого типа обычно выполняют съемными и подключаемыми к цифровым декодирующим устройствам (декодерам) систем платного телевидения. Чаще всего используют модули, использующие электрический контакт, однако возможно и использование бесконтактных соединений, например, типа ISO 14443.

Вторая известная форма представляет собой интегральную микросхему, обычно устанавливаемую в декодер окончательно и без возможности удаления. В альтернативном варианте модуль может представлять собой схему, припаянную или установленную на основании, или же перемычку, например перемычку модуля SIM.

В третьем варианте защитный модуль встроен в интегральную микросхему, имеющую также и другое назначение, например в модуль дешифратора (дескрамблера) декодера или в микропроцессор декодера.

Более конкретно, в области платного цифрового телевидения такие модули защиты выполняют в форме карт. Их используют в качестве средств персонализации и защиты доступа к кодированным программам, принимаемым декодерами, установленными по месту нахождения абонента.

С целью повышения защищенности доступа к данным с ограниченным доступом и предотвращения различных попыток незаконного использования применяют различные известные решения, например: заключение модулей защиты в физическую оболочку, сложные алгоритмы кодирования, двоичные ключи кодирования/декодирования большого размера, а также множественные карты или процессоры, как описано в патентной публикации US 5666412 или US 5774546.

В двух последних примерах декодер платного телевидения снабжен системой для считывания карт с двумя отверстиями, в каждое из которых вставляют электронную смарт-карту. Первая карта содержит идентификационный элемент, содержащий частично закодированные персональные и официальные данные. Вторая смарт-карта содержит прикладной элемент, содержащий ключи доступа и алгоритмы, обеспечивающие возможность доступа к данным, содержащимся в идентификационном элементе первой карты. В частности, конфигурацию такого типа используют в системах родительского контроля доступа с двумя уровнями контроля доступа, осуществляемых с использованием специального ключа.

В соответствии с другим известным решением интегральные микросхемы каждой из двух карт группируют на единой основе, формируя таким образом одну карту с обеспечением отдельного доступа системы считывания карт к каждой из ее интегральных микросхем. Такая карта содержит необходимые данные, которые определяют несколько уровней доступа в соответствии с данными, содержащимися в каждой из интегральных микросхем.

Было показано, что известные средства обеспечения защиты карт доступа к закодированным программам бывают уязвимы для некоторых типов атак, в частности для интерференционных атак или для атак с использованием принудительных искажений (глич-атак). При этом защиту криптографического процессора нарушают путем нарушения исполнения одной или нескольких инструкций. Атакующий анализирует сигналы, генерируемые конкретной последовательностью инструкций, выдаваемых процессором, и в точный момент исполнения инструкции сравнения или скачкового перехода вводит в шину, соединенную с процессором, например, через систему считывания карт, интерференционные сигналы. Такие сигналы в форме коротких импульсных последовательностей блокируют исполнение инструкций или вызывают короткое замыкание ключевых программ идентификации, тем самым открывая доступ к защищенным данным.

Раскрытие изобретения

Задача, на решение которой направлено настоящее изобретение, заключается в усовершенствовании оптимального метода обеспечения защищенности электронных смарт-карт от несанкционированного управления криптографическим процессором или процессорами при помощи внешних сигналов, создающих помехи нормальному выполнению таким процессором или процессорами их функций.

Для решения поставленной задачи предлагается компонент модуля защиты, содержащий, по меньшей мере, два процессора, каждый из которых соединен с программной памятью, с долговременной программируемой и стираемой (EEPROM) памятью, содержащей данные, и с оперативной (RAM) памятью, используемой в качестве временного хранилища данных на время обработки, причем первый процессор соединен через интерфейсную шину с системами, находящимися вне компонента, отличающийся тем, что второй процессор соединен с первым процессором через обменную память (DPR), причем долговременная программируемая и стираемая память первого процессора доступна для указанного первого процессора только для чтения, а второй процессор имеет доступ для чтения и записи к указанной долговременной программируемой и стираемой памяти первого процессора.

Под компонентом подразумевают систему, содержащую все элементы, необходимые для осуществления криптографических операций, установленные на единой основе для обеспечения его защищенности. Такие компоненты обычно выполняют в виде единых электронных микросхем, снабженных механическими и электронными средствами защиты от несанкционированного вмешательства в их работу. Другие конструкции, выполненные, например, из двух электронных микросхем, также подпадают под определение «компонента», т.к. они обладают тесной взаимосвязью и поставляются изготовителями в виде единого элемента.

Такой компонент предпочтительно изготавливают в виде единой кремниевой микросхемы, обычно встроенной в портативное основание, обычно представляющее собой съемную электронную смарт-карту. Карта оборудована каналами доступа, соединенными с первым процессором, которые выполнены либо в виде контактной панели, предусмотренной на одной из поверхности карты и соответствующей стандарту ISO 7816, либо в виде антенны, обеспечивающей возможность электромагнитного обмена данными без гальванического контакта (в соответствии со стандартом ISO 14443) с использованием соответствующей системы чтения/записи.

В соответствии с другим вариантом осуществления изобретения компонент может представлять собой часть более крупного электронного модуля, содержащего средства для обработки закодированных данных. Например, одна из частей такого модуля может обрабатывать закодированные данные программ цифрового телевидения (DVB), причем данный компонент может представлять собой лишь часть кремниевой электронной системы, обеспечивающей защиту такого декодирования. Следует отметить, что электронный модуль может быть либо установлен внутри приемной системы, либо подключен к такой приемной системе съемным образом.

Конфигурация компонента по изобретению обеспечивает возможность полной изоляции второго процессора от каналов внешнего доступа. Действительно, прямое соединение между двумя процессорами, которое сделало бы возможным доступ ко второму процессору при помощи соответствующих инструкций, переданных первому процессору через каналы внешнего доступа, отсутствует. Элементы памяти, соединяющие два процессора, играют роль барьера, который, с одной стороны, блокирует прохождение нежелательных команд, поступающих из каналов внешнего доступа, а с другой стороны, предотвращает возможность анализа сигналов, проходящих между двумя процессорами через те же каналы доступа.

Первый процессор не имеет возможности модифицировать свою программу. Любые изменения его программы должны быть проверены вторым процессором.

Таким образом, второй процессор может производить криптографические операции независимо от операций, выполняемых первым процессором. Кроме того, первый процессор не может выполнять некоторые существенные операции, влияющие на защищенность системы, без разрешающей команды второго процессора.

Краткое описание чертежей

Настоящее изобретение станет более понятно из нижеследующего подробного описания, содержащего ссылки на прилагаемый чертеж, который иллюстрируют пример осуществления изобретения, не накладывающий каких-либо ограничений.

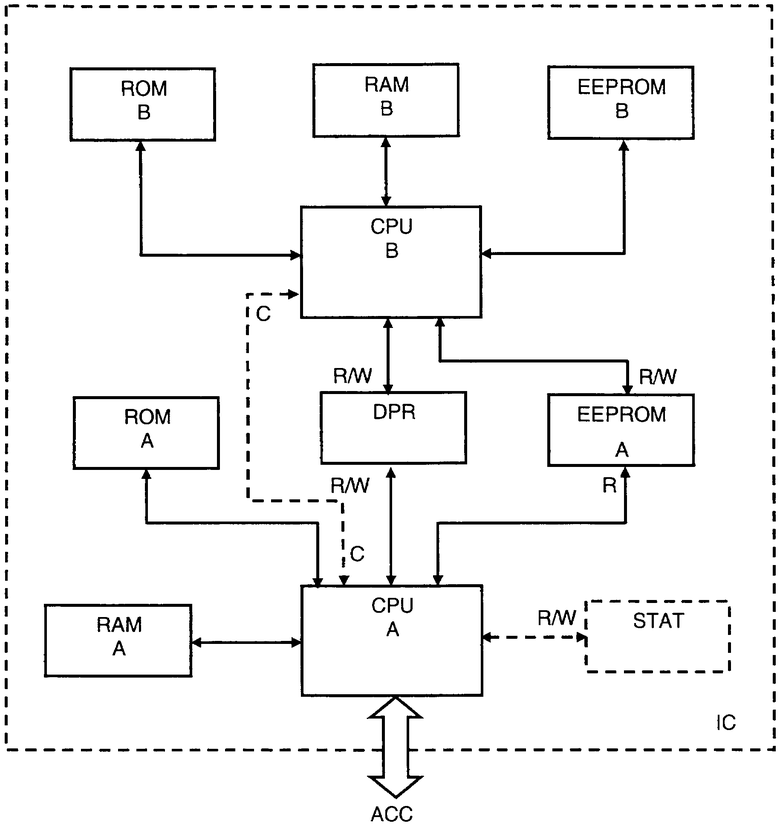

На чертеже приведена блок-схема компонента защитного модуля, содержащего два процессора, каждый из которых соединен с элементом памяти, а также с другим процессором через обменную память.

Осуществление изобретения

На чертеже изображен компонент IC, обычно выполняемый в виде одного микропроцессора, установленного на переносном основании, которое в соответствии с предпочтительным вариантом осуществления представляет собой электронную карту, содержащую канал АСС доступа в форме контактов или антенны.

Компонент IC содержит два процессора CPU A, CPU В, соединенные между собой при помощи обменной оперативной (с произвольным доступом) памяти DPR, а также при помощи долговременной программируемой и стираемой памяти EEPROM А. Первый процессор CPU А соединен, с одной стороны, с каналом АСС доступа, а с другой стороны, с оперативной памятью RAM А и с постоянной (доступной только для чтения) памятью ROM А. Второй процессор CPU В также соединен с оперативной памятью RAM В и с постоянной памятью ROM В, а также с долговременной программируемой и стираемой памятью EEPROM В.

В соответствии с одним из альтернативных вариантов осуществления к первому процессору CPU А может быть дополнительно подсоединена для чтения/записи (R/W) долговременная программируемая и стираемая память STAT. Она служит для хранения, например, данных, относящихся к истории эксплуатации компонента, доступных для чтения внешними системами через канал АСС доступа.

В соответствии с одной из существенных особенностей настоящего изобретения первый процессор CPU А соединен с долговременной программируемой и стираемой памятью EEPROM А с возможностью только для чтения (R), в то время как второй процессор CPU В соединен с ней с возможностью чтения и записи (R/W). Другой аспект изобретения заключается в наличии обменной оперативной памяти DPR, с которой оба процессора CPU А и CPU В соединены с возможностью чтения и записи (R/W).

Первый процессор CPU А компонента по изобретению, доступный для внешних систем, выполняет известные операции модулей защиты, т.е., например, управление контрольными словами (CW) и контрольными сообщениями (ЕСМ), а также проверку прав доступа электронных карт. Можно предположить, что такие операции как аутентификация, декодирование управляющих сообщений (EMM) или управление ключами и алгоритмами декодирования могут осуществляться вторым процессором CPU В.

Второй процессор CPU В осуществляет управление и исполнение всех защитных операций, требующих использования ключей кодирования/декодирования сохраненных, например, в постоянной памяти ROM В. Долговременная программируемая и стираемая память EEPROM В содержит программы, а также алгоритмы, необходимые для декодирования в соответствии с инструкциями, передаваемыми первым процессором CPU А через обменную оперативную память DPR.

Благодаря тому, что первый процессор CPU А соединен с долговременной программируемой и стираемой памятью EEPROM А только для чтения, ее содержимое не может быть изменено внешними системами. Каждую инструкцию процессора, выданную в соответствии с командами, полученными через канал АСС доступа, сохраняют в обменной оперативной памяти DPR, и второй процессор CPU В осуществляет проверку ее выполнения прежде, чем результирующие данные сохраняют при помощи указанного второго процессора CPU В в долговременной памяти EEPROM А через порт R/W.

В соответствии с одним из альтернативных вариантов осуществления процессор CPU В может непосредственно управлять процессором CPU А при помощи соединения С без посредства обменной памяти DPR. Такой тип управления позволяет, например, осуществлять активацию или быстрое блокирование процессора CPU А в зависимости от результата проверки, проведенной процессором CPU В.

Электронная карта, содержащая вышеописанный компонент, может быть использована в декодере системы платного телевидения, в которой требуется обеспечение высокого уровня защищенности, с одной стороны, прав доступа к закодированным данным видео/аудио потоков, передаваемых по кабелям или в виде спутниковых сигналов, а с другой стороны, операционного программного обеспечения такой карты.

Одна из функций карты заключается в контроле доступа к закодированным данным видео/аудио потоков, получаемых декодером, путем проверки контрольных сообщений ЕСМ, передаваемых вместе с указанными закодированными данными. По завершении проверки разрешение на декодирование данных потока выдается в соответствии с правами доступа к аудио/видео данным, определенными в сообщении ЕСМ.

С целью определения прав пользователя центр управления посылает управляющие сообщения EMM, обычно имеющие индивидуальный вид, а именно закодированные с помощью уникального ключа, соответствующего данному пользователю. В соответствии с одним из вариантов осуществления изобретения сообщения такого типа не могут быть декодированы процессором CPU А, т.к. он не располагает уникальным персональным ключом пользователя. Такой ключ может быть симметричным или асимметричным (секретным ключом или открытым ключом).

В данном примере памятью, в которой сохраняют эти права, является память EEPROM А. Поскольку эта память доступна для записи только для процессора CPU В, процессор CPU А передает управляющее сообщение EMM процессору CPU В через обменную память DPR. Процессор CPU В начинает цикл декодирования сообщения и, после проведения проверки, обновляет информацию о правах в памяти EEPROM A.

В соответствии с альтернативным вариантом осуществления права также могут быть сохранены в памяти STAT. В этом случае результат декодирования сообщения EMM передают процессору CPU А через обменную память DPR для сохранения в памяти STAT.

Загрузка программного обеспечения карты, сохраненного в долговременной памяти EEPROM А, или обновление такого программного обеспечение происходит в карте, оборудованной компонентом по изобретению, с обеспечением более надежной защиты. На практике сохранение программного обеспечения, введенного через канал АСС доступа и процессор CPU А без проведения его проверки при помощи процессора CPU В, невозможно.

Программное обеспечение или его обновленная версия поступает через декодер в виде закодированных блоков, которые поочередно (по одному) передают первому процессору CPU А через канал АСС доступа карты. Процессор CPU А не может декодировать такие блоки, так как не располагает соответствующим ключом. Блоки передают процессору CPU В через обменную память DPR. Процессор CPU В запускает процесс декодирования в защищенном и, следовательно, непрерываемом режиме. Результаты этой операции сохраняют в собственной памяти процессора CPU В, т.е. в памяти EEPROM В

Предполагается, что контрольное значение или подпись содержится в управляющем сообщении EMM. Процессор CPU В получает это сообщение через обменную память DPR и может вычислить подпись предварительно декодированного блока данных и сравнить ее с подписью, полученной в сообщении.

Только после проведения такой проверки процессор CPU В может инициировать цикл записи в память процессора CPU А, т.е. в память EEPROM A.

В случае отрицательного результата такого сравнения загрузку или обновление программного обеспечения останавливают, и процессор CPU А передает декодеру либо сообщение об ошибке, либо команду повторной инициализации загрузки.

После успешной проверки и сохранения всех блоков в памяти EEPROM В процессор CPU В передает указанные блоки в память EEPROM А. После этого процессор CPU А должен осуществить установку и активацию нового программного обеспечения.

В соответствии с одним из альтернативных вариантов осуществления перед передачей какого-либо блока данных в память EEPROM А процессор CPU В может проводить дополнительную проверку всех блоков данных, сохраненных в памяти EEPROM В путем вычисления суммарной подписи всех блоков. После этого производят сравнение полученной подписи с суммарной подписью программного обеспечения, также содержащейся в сообщении EMM.

В соответствии с еще одним из альтернативных вариантов осуществления обработка управляющих сообщений EMM производится процессором CPU А. Следует отметить, что во время каждого сеанса декодирования таких сообщений EMM процессор CPU А запрашивает у процессора CPU В ключ, необходимый для непосредственного осуществления такого декодирования. По завершении декодирования ключ стирают и сохраняют только в оперативной памяти RAM A процессора CPU А. Таким образом, не происходит промежуточного сохранения ключа в долговременной памяти EEPROM А, которая при этом была бы доступна для чтения через канал АСС доступа. В оперативной памяти RAM А сохраняют только промежуточные результаты вычисления, а окончательные данные (например, права доступа) процессор CPU А передает в память STAT.

Если число задач по обеспечению защиты возрастает настолько, что производительности одного процессора оказывается недостаточно, число процессоров может быть увеличено в соответствии со сложностью выполняемых операций. Блок-схема конфигурации такого типа представляет собой расширенный вариант блок-схемы по чертежу, в котором каждый дополнительный процессор соединен с обменной оперативной памятью DPR с двумя портами, первый из которых соединен с первым процессором, соединенным с каналом внешнего доступа.

В соответствии с одним из альтернативных вариантов осуществления обменная разделительная оперативная память DPR может быть оборудована таким количеством дополнительных портов, которое необходимо для подсоединения дополнительных процессоров.

| название | год | авторы | номер документа |

|---|---|---|---|

| ИСПОЛЬЗОВАНИЕ АУТЕНТИФИЦИРОВАННЫХ МАНИФЕСТОВ ДЛЯ ОБЕСПЕЧЕНИЯ ВНЕШНЕЙ СЕРТИФИКАЦИИ МНОГОПРОЦЕССОРНЫХ ПЛАТФОРМ | 2014 |

|

RU2599340C2 |

| СИСТЕМА ВЕЩАНИЯ И ПРИЕМА, А ТАКЖЕ СИСТЕМА УСЛОВНОГО ДОСТУПА ДЛЯ НЕЕ | 1997 |

|

RU2196389C2 |

| СИСТЕМА ПРИЕМА ВЕЩАНИЯ, СОДЕРЖАЩАЯ КОМПЬЮТЕР И ДЕКОДЕР | 1998 |

|

RU2199831C2 |

| ГЕНЕРИРОВАНИЕ СИГНАЛОВ И ИХ ВЕЩАНИЕ | 1997 |

|

RU2187207C2 |

| СИСТЕМА И СПОСОБ РЕГИСТРАЦИИ ОПЛАТЫ ТЕЛЕВИЗИОННЫХ ПРОГРАММ | 1998 |

|

RU2225077C2 |

| СПОСОБ И УСТРОЙСТВО ДЛЯ ЗАПИСИ ЗАШИФРОВАННЫХ ЦИФРОВЫХ ДАННЫХ | 1999 |

|

RU2225681C2 |

| ТАБЛИЦА ДАННЫХ О ПРИЛОЖЕНИЯХ ДЛЯ СИСТЕМЫ ЦИФРОВОЙ ПЕРЕДАЧИ, ПРЕДОСТАВЛЯЮЩЕЙ МНОЖЕСТВО СЕРВИСОВ | 1999 |

|

RU2257687C2 |

| СПОСОБ ОБЕСПЕЧЕНИЯ БЕЗОПАСНОСТИ ИГРОВЫХ УСТРОЙСТВ И ИГРОВОЕ УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 2006 |

|

RU2310907C1 |

| МЕХАНИЗМ ОБЕСПЕЧЕНИЯ БЕЗОПАСНОСТИ ДЛЯ ВНЕШНЕГО КОДА | 2011 |

|

RU2582863C2 |

| СПОСОБ И УСТРОЙСТВО ДЛЯ ПРЕДОТВРАЩЕНИЯ НЕЧЕСТНОГО ДОСТУПА В СИСТЕМЕ УСЛОВНОГО ДОСТУПА | 1998 |

|

RU2199832C2 |

Задача, на решение которой направлено настоящее изобретение, и технический результат заключаются в усовершенствовании оптимального метода обеспечения защищенности электронных смарт-карт от несанкционированного управления криптографическим процессором или процессорами при помощи внешних сигналов, создающих помехи нормальному выполнению таким процессором или процессорами их функций. Предлагается компонент IC защитного модуля, содержащий, по меньшей мере, два процессора CPU A, CPU В, каждый из которых соединен с программной памятью ROM A, ROM В, с долговременной программируемой и стираемой (EEPROM) памятью EEPROM A, EEPROM В, содержащей данные, и с оперативной (RAM) памятью RAM A, RAM В, используемой в качестве временного хранилища данных на время обработки, причем первый процессор CPU А соединен через интерфейсную шину с системами, находящимися вне компонента IC, отличающийся тем, что второй процессор CPU В соединен с первым процессором CPU А через обменную память DPR, причем долговременная программируемая и стираемая память EEPROM A первого процессора CPU А доступна для указанного первого процессора CPU А только для чтения (R), а второй процессор CPU В имеет доступ для чтения и записи (R/W) к указанной долговременной программируемой и стираемой памяти EEPROM А первого процессора CPU A. 9 з.п. ф-лы, 1 ил.

1. Компонент (IC) модуля защиты, содержащий, по меньшей мере, два процессора (CPU A, CPU В), каждый из которых соединен с программной памятью (ROM A, ROM В), с долговременной программируемой и стираемой памятью (EEPROM A, EEPROM В), содержащей данные, и с оперативной памятью (RAM A, RAM В), используемой в качестве временного хранилища данных на время обработки, причем первый процессор (CPU А) соединен через интерфейсную шину с системами, находящимися вне компонента (IC), отличающийся тем, что второй процессор (CPU В) соединен с первым процессором (CPU А) через обменную память (DPR), а долговременная программируемая и стираемая память (EEPROM А) первого процессора (CPU А) доступна для указанного первого процессора (CPU А) только для чтения (R), а второй процессор (CPU В) имеет доступ для чтения и записи (R/W) к указанной долговременной программируемой и стираемой памяти (EEPROM A) первого процессора (CPU A).

2. Компонент по п.1, отличающийся тем, что обменная память (DPR) представляет собой оперативную память, предназначенную для временного хранения данных, причем указанная обменная память (DPR) оборудована двумя портами, каждый из которых открыт для чтения и записи (R/W), и один из указанных портов соединен с первым процессором (CPU А), а второй порт соединен со вторым процессором (CPU В).

3. Компонент по п.1, отличающийся тем, что установлен на портативной основе, содержащей каналы (АСС) доступа, предназначенные для обмена данными с внешней системой обработки данных, причем указанные каналы (АСС) доступа соединены с первым процессором (CPU А) через интерфейсную шину.

4. Компонент по п.1, отличающийся тем, что первый процессор (CPU A) содержит средства для выполнения функций известных модулей защиты, а второй процессор (CPU В) содержит средства для управления и выполнения таких защитных операций, как аутентификация, декодирование или управление ключами и алгоритмами декодирования.

5. Компонент по п.2, отличающийся тем, что программная память (ROM В) и долговременная программируемая и стираемая память (EEPROM В) содержат программы и алгоритмы, необходимые для декодирования в соответствии с инструкциями, переданными первым процессором (CPU A) через обменную память (DPR).

6. Компонент по п.4, отличающийся тем, что второй процессор (CPU В) содержит средства проверки данных, полученных через каналы (АСС) доступа и обменную память (DPR), причем указанные данные на время проверки временно сохраняют в долговременной памяти (EEPROM В).

7. Компонент по любому из пп.1-6, отличающийся тем, что второй процессор (CPU В) содержит средства сохранения проверенных данных в долговременной памяти (EEPROM А) через порт (R/W).

8. Компонент по п.2, отличающийся тем, что установлен на электронной карте, оборудованной гальваническими контактами формата ISO 7816, образующими каналы (АСС) доступа, причем указанная карта представляет собой съемный защитный модуль декодера системы платного телевидения.

9. Компонент по п.1, отличающийся тем, что содержит, по меньшей мере, один дополнительный процессор, соединенный с возможностью чтения и записи с первым портом дополнительной долговременной программируемой и стираемой памяти, причем второй порт указанной памяти соединен только с возможностью чтения с первым процессором.

10. Компонент по п.1, отличающийся тем, что содержит, по меньшей мере, один дополнительный процессор, соединенный для чтения и записи с дополнительным портом долговременной программируемой и стираемой памяти, причем указанная память соединена с первым процессором только с возможностью чтения.

| US 5666412 А, 09.09.1997 | |||

| US 5774546 A, 30.06.1998 | |||

| СПОСОБ И УСТРОЙСТВО ДЛЯ ОБРАБОТКИ ДАННЫХ | 1997 |

|

RU2198423C2 |

| СПОСОБ БЛОЧНОГО ИТЕРАТИВНОГО ШИФРОВАНИЯ ЦИФРОВЫХ ДАННЫХ | 2000 |

|

RU2184423C2 |

| DE 19811646 A, 23.09.1999 | |||

| ИНДИВИДУАЛЬНЫЙ МНОГОФУНКЦИОНАЛЬНЫЙ МАСКИРОВОЧНЫЙ ЧЕХОЛ ДЛЯ АВТОМОБИЛЬНОЙ ТЕХНИКИ | 2022 |

|

RU2787900C1 |

| Способ прогнозирования формирования цирроза печени у пациентов с хроническим гепатитом C | 2024 |

|

RU2834154C1 |

| WO 03107585 A1, 24.12.2003 | |||

| WO 03090886 A1, 06.11.2003. | |||

Авторы

Даты

2009-12-27—Публикация

2005-06-02—Подача