Предлагаемое изобретение относится к вычислительной технике и может быть использовано при построении многоразрядных быстродействующих сумматоров и АЛУ.

Известен сумматор [а.с. № 1034031, СССР, G06F 7/50], названный автором как «Одноразрядный двоичный сумматор на комплементарных МДП-транзисторах».

Недостатком известного сумматора является низкое быстродействие формирования сигнала переноса. В указанном сумматоре увеличена длительность фронта и спада сигнала на выходе 5  который является инверсным выходом сигнала переноса, за счет подключения дополнительной паразитной емкости в виде емкости затворов транзисторов 26 и 29. Поэтому появление сигнала переноса на выходе имеет дополнительную задержку, пропорциональную величине вклада дополнительной емкости в общую емкость узла выхода 5

который является инверсным выходом сигнала переноса, за счет подключения дополнительной паразитной емкости в виде емкости затворов транзисторов 26 и 29. Поэтому появление сигнала переноса на выходе имеет дополнительную задержку, пропорциональную величине вклада дополнительной емкости в общую емкость узла выхода 5

Кроме того, известен сумматор [IEEE JOURNAL OF SOLID-STATE CIRCUITS, VOL. 32, NO. 7, JULY 1997, p.1085, Fig.4(p)], являющийся прототипом предлагаемого изобретения и содержащий полевые транзисторы первый, второй …, двенадцатый - первого типа проводимости, тринадцатый, четырнадцатый …, двадцать четвертый - второго типа проводимости, вход слагаемого А, соединенный с затворами первого, пятого, шестого, десятого, четырнадцатого, шестнадцатого, девятнадцатого и двадцать четвертого транзисторов, вход слагаемого В, соединенный с затворами второго, четвертого, седьмого, одиннадцатого, пятнадцатого, семнадцатого, двадцатого и двадцать третьего транзисторов, вход переноса СIN, соединенный с затворами третьего, восьмого, двенадцатого, тринадцатого, двадцать первого и двадцать второго транзисторов, вывод питания первого уровня напряжения, соединенный с истоками первого, второго, четвертого, шестого, седьмого, восьмого и десятого транзисторов, вывод питания второго уровня напряжения, соединенный с истоками четырнадцатого, пятнадцатого, семнадцатого, девятнадцатого, двадцатого, двадцать первого и двадцать четвертого транзисторов, причем стоки первого и второго транзисторов соединены с истоком третьего транзистора, сток четвертого - с истоком пятого, стоки шестого, седьмого и восьмого - с истоком девятого, сток десятого - с истоком одиннадцатого, сток одиннадцатого - с истоком двенадцатого, стоки четырнадцатого и пятнадцатого - с истоком тринадцатого, сток семнадцатого - с истоком шестнадцатого, стоки девятнадцатого, двадцатого и двадцать первого - с истоком восемнадцатого, сток двадцать четвертого - с истоком двадцать третьего и сток двадцать третьего - с истоком двадцать второго, и стоки третьего, пятого, тринадцатого и шестнадцатого - с затворами девятого и восемнадцатого транзисторов и входом первого инвертора, выход которого является выходом сигнала переноса

СOUT, а стоки девятого, двенадцатого, восемнадцатого и двадцать второго транзисторов - с входом второго инвертора, выход которого является выходом результата сложения S.

Однако в указанном сумматоре вход переноса CIN соединен с затворами трех комплементарных пар транзисторов, которые вносят основной вклад в величину входной емкости по этому входу. Так как входная емкость является емкостной нагрузкой для сигнала переноса СIN, то ее величина оказывает непосредственное влияние на длительность переключения транзисторов, подсоединенных к входу переноса СIN, и эта длительность, при прочих равных условиях, прямо пропорциональна значению этой емкости и, следовательно, значению времени формирования входного и соответственно выходного сигнала первого инвертора.

Задачей предлагаемого изобретения является повышение быстродействия формирования сигнала переноса на выходе СOUT.

Поставленная задача достигается тем, что в сумматор, содержащий полевые транзисторы первый, второй …, двенадцатый - первого типа проводимости, тринадцатый, четырнадцатый …, двадцать четвертый - второго типа проводимости, вход слагаемого А, соединенный с затворами первого, пятого, шестого, десятого, четырнадцатого, шестнадцатого, девятнадцатого и двадцать четвертого транзисторов, вход слагаемого В, соединенный с затворами второго, четвертого, седьмого, одиннадцатого, пятнадцатого, семнадцатого, двадцатого и двадцать третьего транзисторов, вход переноса CIN, соединенный с затворами третьего, двенадцатого, тринадцатого и двадцать второго транзисторов, вывод питания первого уровня напряжения, соединенный с истоками первого, второго, четвертого, шестого, седьмого, восьмого и десятого транзисторов, вывод питания второго уровня напряжения, соединенный с истоками четырнадцатого, пятнадцатого, семнадцатого, девятнадцатого, двадцатого, двадцать первого и двадцать четвертого транзисторов, причем стоки первого и второго транзисторов соединены с истоком третьего транзистора, сток четвертого - с истоком пятого, стоки шестого и седьмого - с истоком девятого, сток десятого - с истоком одиннадцатого, сток одиннадцатого - с истоком двенадцатого, стоки четырнадцатого и пятнадцатого - с истоком тринадцатого, сток семнадцатого - с истоком шестнадцатого, стоки девятнадцатого и двадцатого - с истоком восемнадцатого, сток двадцать четвертого - с истоком двадцать третьего и сток двадцать третьего - с истоком двадцать второго, и стоки третьего, пятого, тринадцатого и шестнадцатого - с затворами девятого и восемнадцатого и входом первого инвертора, выход которого является выходом сигнала переноса СOUT, а стоки девятого, двенадцатого, восемнадцатого и двадцать второго транзисторов - с входом второго инвертора, выход которого является выходом результата сложения S, введены двухвходовой логический элемент И-НЕ, первый и второй входы которого соединены с входами слагаемых соответственно А и В, а выход - с затвором восьмого транзистора, сток которого соединен со стоком одиннадцатого и истоком двенадцатого транзисторов, и двухвходовой логический элемент ИЛИ-НЕ, первый и второй входы которого соединены с входами слагаемых соответственно А и В, а выход - с затвором двадцать первого транзистора, сток которого соединен со стоком двадцать третьего и истоком двадцать второго транзисторов.

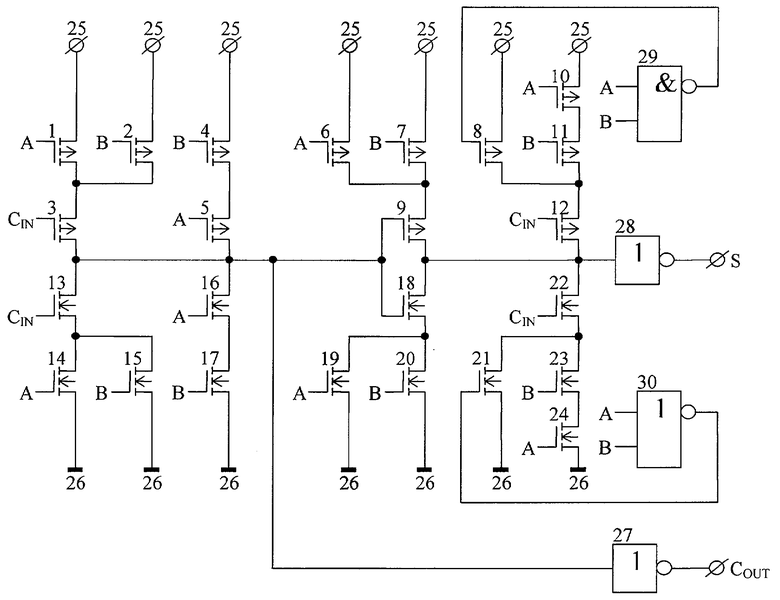

На чертеже приведен предлагаемый сумматор, реализованный на КМОП транзисторах, в котором в качестве полевых транзисторов с каналом первого типа проводимости использованы МОП транзисторы Р-типа, а в качестве полевых транзисторов с каналом второго типа проводимости - МОП транзисторы N-типа, на выводы питания первого и второго уровней напряжения поданы напряжения соответственно высокого и низкого уровней.

Предлагаемый сумматор содержит: полевые транзисторы первый 1, второй 2 …, двенадцатый 12 - первого типа проводимости, тринадцатый 13, четырнадцатый 14 …, двадцать четвертый 24 - второго типа проводимости, вход слагаемого А, соединенный с затворами первого 1, пятого 5, шестого 6, десятого 10, четырнадцатого 14, шестнадцатого 16, девятнадцатого 19 и двадцать четвертого 24 транзисторов, вход слагаемого В, соединенный с затворами второго 2, четвертого 4, седьмого 7, одиннадцатого 11, пятнадцатого 15, семнадцатого 17, двадцатого 20 и двадцать третьего 23 транзисторов, вход переноса СIN, соединенный с затворами третьего 3, двенадцатого 12, тринадцатого 13 и двадцать второго 22 транзисторов, вывод питания первого уровня напряжения 25, соединенный с истоками первого 1, второго 2, четвертого 4, шестого 6, седьмого 7, восьмого 8 и десятого 10 транзисторов, вывод питания второго уровня напряжения 26, соединенный с истоками четырнадцатого 14, пятнадцатого 15, семнадцатого 17, девятнадцатого 19, двадцатого 20, двадцать первого 21 и двадцать четвертого 24 транзисторов, причем стоки первого 1 и второго 2 транзисторов соединены с истоком третьего 3 транзистора, сток четвертого 4 - с истоком пятого 5, стоки шестого 6 и седьмого 7 - с истоком девятого 9, сток десятого 10 - с истоком одиннадцатого 11, сток одиннадцатого 11 - с истоком двенадцатого 12 и стоком 8, стоки четырнадцатого 14 и пятнадцатого 15 - с истоком тринадцатого 13, сток семнадцатого 17 - с истоком шестнадцатого 16, стоки девятнадцатого 19 и двадцатого 20 - с истоком восемнадцатого 18, сток двадцать четвертого 24 - с истоком двадцать третьего 23 и сток двадцать третьего 23 - с истоком двадцать второго 22 и стоком 21, и стоки третьего 3, пятого 5, тринадцатого 13 и шестнадцатого 16 - с затворами девятого 9 и восемнадцатого 18 транзисторов и входом первого инвертора 27, выход которого является выходом сигнала переноса

СOUT, а стоки девятого 9, двенадцатого 12, восемнадцатого 18 и двадцать второго 22 транзисторов - с входом второго инвертора 28, выход которого является выходом результата сложения S, двухвходовой логический элемент И-НЕ 29, первый и второй входы которого соединены с входами слагаемых соответственно А и В, а выход - с затвором восьмого 8 транзистора, и двухвходовой логический элемент ИЛИ-НЕ 30, первый и второй входы которого соединены с входами слагаемых соответственно А и В, а выход - с затвором двадцать первого 21 транзистора.

Допускается произвольное выполнение логических элементов первого и второго инверторов и двухвходовых элементов И-НЕ и ИЛИ-НЕ, реализующих соответствующую функцию.

Предлагаемый сумматор представляет собой логическую схему комбинационного типа и работает следующим образом.

На входы слагаемых А и В поступают значения сигналов, требующих сложения, а на вход переноса СIN - значение сигнала переноса.

В результате действия поступающих сигналов, на выходах сумматора СOUT и S должны появиться значения сигналов, соответствующих нижеприведенной таблице истинности.

В комбинациях №№ 1-4 на вход переноса CIN и на затворы подключенных к нему транзисторов 3, 12, 13 и 22 поступает напряжение низкого уровня, которое соответствует значению «0» таблицы истинности сумматора. При этом транзисторы P-типа 3 и 12 - открываются, а N-типа 13 и 22 - закрывается. Если при этом на входы слагаемых А и В поступает напряжение низкого уровня, то транзисторы P-типа 1, 2, 4-7, 10 и 11, подключенные своими затворами к этим входам - открываются, а N-типа 14-17, 19, 20, 23, 24 - закрываются. Через открытые транзисторы 1-5 с вывода источника питания высокого уровня 25 на затворы транзисторов 9, 18 и на вход первого инвертора 27 поступает напряжение высокого уровня, которое соответствует значению «1» таблицы истинности сумматора и поэтому транзистор P-типа 9 закрывается, а N-типа 18 - открывается. Так как на входе первого инвертора 27 напряжение высокого уровня - «1», то после инверсии на его выходе СOUT формируется напряжение низкого уровня - «0». В то же время, на выходах двухвходовых логических элементов И-НЕ 29 и ИЛИ-НЕ 30, в соответствии с выполняемыми ими функциями, формируется напряжение высокого уровня - «1», которое поступает на затворы транзисторов P-типа 8 и N-типа 21. Поэтому транзистор 8 закрывается, а транзистор 21 - открывается. Так как транзисторы P-типа 10, 11 и 12 - открыты, через них на вход второго инвертора 28 с вывода источника питания высокого уровня 25 поступает напряжение высокого уровня - «1». Поэтому на выходе этого инвертора S формируется инверсное относительно входного напряжение низкого уровня - «0». При этом входы первого 27 и второго 28 инверторов остаются изолированными от напряжения низкого уровня закрытыми транзисторами N-типа 13-17, 19, 20, 22. Таким образом, реализуется комбинация №1 таблицы истинности сумматора.

Если же на вход слагаемого А(В) поступает напряжение низкого уровня - «0», а на вход слагаемого В(А) высокого - «1», то транзисторы P-типа 1(2), 5(4), 6(7), 10(11) и N-типа 15(14), 17(16), 20(19), 23(24), подключенные своими затворами к этим входам, - открываются, а P-типа 2(1), 4(5), 7(6), 11(10) и N-типа 14(15), 16(17), 19(20), 24(23) - закрываются. Через открытые транзисторы 1(2), 3 с вывода источника питания высокого уровня 25 на затворы транзисторов 9, 18 и на вход первого инвертора 27 поступает напряжение высокого уровня - «1» и поэтому транзистор P-типа 9 закрывается, а N-типа 18 - открывается. Так как на входе первого инвертора 27 напряжение высокого уровня - «1», то после инверсии на его выходе СOUT формируется напряжение низкого уровня - «0». В то же время, на выходе двухвходового логического элемента И-НЕ 29, в соответствии с выполняемой им функцией, формируется напряжение высокого уровня - «1», которое поступает на затвор транзистора P-типа 8, а на выходе двухвходового логического элемента ИЛИ-НЕ 30 низкого - «0», которое поступает на затвор транзистора N-типа 21. Поэтому транзисторы 8 и 21 - закрываются. Так как транзисторы N-типа 18 и 20(19) - открыты, через них на вход второго инвертора 28 с вывода источника питания низкого уровня 26 поступает напряжение низкого уровня - «0». Поэтому на выходе этого инвертора S формируется инверсное относительно входного напряжение высокого уровня - «1». При этом вход первого инвертора 27 остается изолированным от напряжения низкого уровня закрытыми транзисторами N-типа 13 и 16(17), а вход второго 28 - от напряжения высокого уровня закрытыми транзисторами P-типа 8, 9 и 11(10). Таким образом, реализуется комбинация №2(№3) таблицы истинности сумматора.

В случае, когда на входы А и В поступает напряжение высокого уровня - «1», транзисторы P-типа 1, 2, 4-7,10 и 11, подключенные своими затворами к этим входам, - закрываются, а N-типа 14-17, 19, 20, 23, 24 - открываются. Через открытые транзисторы 16-17 с вывода источника питания низкого уровня 26 на затворы транзисторов 9, 18 и на вход первого инвертора 27 поступает напряжение низкого уровня - «0» и поэтому транзистор P-типа 9 открывается, а N-типа 18 - закрывается. Так как на входе первого инвертора 27 напряжение низкого уровня - «0», то после инверсии на его выходе СOUT формируется напряжение высокого уровня - «1». В то же время, на выходах двухвходовых логических элементов И-НЕ 29 и ИЛИ-НЕ 30, в соответствии с выполняемыми ими функциями, формируется напряжение низкого уровня -«0», которое поступает на затворы транзисторов P-типа 8 и N-типа 21. Поэтому транзистор 8 открывается, а транзистор 21 - закрывается. Так как транзисторы P-типа 8 и 12 - открыты, через них на вход второго инвертора 28 с вывода источника питания высокого уровня 25 поступает напряжение высокого уровня «1». Поэтому на выходе этого инвертора S формируется инверсное относительно входного напряжение низкого уровня - «0». При этом вход первого инвертора 27 остается изолированным от напряжения высокого уровня закрытыми транзисторами P-типа 1, 2, 4, 5 и второго 28 от напряжения низкого уровня соответственно транзисторами N-типа 18, 21, 22. Таким образом, реализуется комбинация №4 таблицы истинности сумматора.

В комбинациях №№5-8 на вход переноса CIN и на затворы подключенных к нему транзисторов 3, 12, 13 и 22 поступает напряжение высокого уровня - «1». Поэтому транзисторы P-типа 3 и 12 - закрываются, а N-типа 13 и 22 - открываются. Если при этом на входы слагаемых А и В поступает напряжение низкого уровня, то транзисторы P-типа 1, 2, 4-7, 10 и 11, подключенные своими затворами к этим входам, - открываются, а N-типа 14-17, 19, 20, 23, 24 - закрываются. Через открытые транзисторы 4-5 с вывода источника питания высокого уровня 25 на затворы транзисторов 9,18 и на вход первого инвертора 27 поступает напряжение высокого уровня - «1» и поэтому транзистор P-типа 9 закрывается, а N-типа 18 - открывается. Так как на входе первого инвертора 27 напряжение высокого уровня - «1», то после инверсии на его выходе СOUT формируется напряжение низкого уровня - «0». В то же время, на выходах двухвходовых логических элементов И-НЕ 29 и ИЛИ-НЕ 30, в соответствии с выполняемыми ими функциями, формируется напряжение высокого уровня - «1», которое поступает на затворы транзисторов P-типа 8 и N-типа 21. Поэтому транзистор 8 закрывается, а транзистор 21 - открывается. Так как транзисторы N-типа 21, 22 - открыты, через них на вход второго инвертора 28 с вывода источника питания низкого уровня 26 поступает напряжение низкого уровня - «0». Поэтому на выходе этого инвертора S формируется инверсное относительно входного напряжение высокого уровня - «1». При этом вход первого инвертора 27 остается изолированным от напряжения низкого уровня закрытыми транзисторами N-типа 14-17 и второго 28 соответственно от напряжения высокого уровня транзисторами P-типа 9, 12. Таким образом, реализуется комбинация №5 таблицы истинности сумматора.

Если же на вход слагаемого А(В) поступает напряжение низкого уровня - «0», а на вход слагаемого В(А) высокого - «1», то транзисторы P-типа 1(2), 5(4), 6(7), 10(11) и N-типа 15(14), 17(16), 20(19), 23(24), подключенные своими затворами к этим входам, - открываются, а P-типа 2(1), 4(5), 7(6), 11(10) и N-типа 14(15), 16(17), 19(20), 24(23) - закрываются. Через открытые транзисторы 13, 15(14) с вывода источника питания низкого уровня 26 на затворы транзисторов 9, 18 и на вход первого инвертора 27 поступает напряжение низкого уровня - «0» и поэтому транзистор P-типа 9 открывается, а N-типа 18 - закрывается. Так как на входе первого инвертора 27 напряжение низкого уровня - «0», то после инверсии на его выходе СOUT формируется напряжение высокого уровня - «1». В то же время, на выходе двухвходового логического элемента И-НЕ 29, в соответствии с выполняемой им функцией, формируется напряжение высокого уровня - «1», которое поступает на затвор транзистора P-типа 8, а на выходе двухвходового логического элемента ИЛИ-НЕ 30 низкого - «0», которое поступает на затвор транзистора N-типа 21. Поэтому транзисторы 8 и 21 - закрываются. Так как транзисторы P-типа 6(7) и 9 - открыты, через них на вход второго инвертора 28 с вывода источника питания высокого уровня 25 поступает напряжение высокого уровня - «1». Поэтому на выходе этого инвертора S формируется инверсное относительно входного напряжение низкого уровня - «0». При этом вход первого инвертора 27 остается изолированным от напряжения высокого уровня закрытыми транзисторами P-типа 3 и 4(5), а вход второго 28 - от напряжения низкого уровня закрытыми транзисторами N-типа 18 и 21, 24(23). Таким образом, реализуется комбинация №6(№7) таблицы истинности сумматора.

В случае, когда на входы А и В поступает напряжение высокого уровня - «1», транзисторы P-типа 1, 2, 4-7, 10 и 11, подключенные своими затворами к этим входам, - закрываются, а N-типа 14-17, 19, 20, 23, 24 - открываются. Через открытые транзисторы 16-17 с вывода источника питания низкого уровня 26 на затворы транзисторов 9, 18 и на вход первого инвертора 27 поступает напряжение низкого уровня - «0» и поэтому транзистор P-типа 9 открывается, а N-типа 18 - закрывается. Так как на входе первого инвертора 27 напряжение низкого уровня - «0», то после инверсии на его выходе СOUT формируется напряжение высокого уровня - «1». В то же время, на выходах двухвходовых логических элементов И-НЕ 29 и ИЛИ-НЕ 30, в соответствии с выполняемыми ими функциями, формируется напряжение высокого уровня - «1», которое поступает на затворы транзисторов P-типа 8 и N-типа 21. Поэтому транзистор 8 закрывается, а транзистор 21 - открывается. Так как транзисторы N-типа 21 и 22 - открыты, через них на вход второго инвертора 28 с вывода источника питания низкого уровня 26 поступает напряжение низкого уровня «0». Поэтому на выходе этого инвертора S формируется инверсное относительно входного напряжение высокого уровня - «1». При этом входы первого 27 и второго 28 инверторов остаются изолированными от напряжения высокого уровня закрытыми транзисторами P-типа 1-7 и 10-12. Таким образом, реализуется комбинация №8 таблицы истинности сумматора.

В предлагаемой схеме сумматора исключено соединение затворов восьмого и двадцать первого транзисторов с входом переноса CIN, вследствие чего суммарная емкость входа переноса СIN уменьшена. Таким образом, при прочих равных условиях, длительность фронта и спада входного сигнала на входе переноса СIN уменьшена, благодаря чему ускорено переключение третьего и тринадцатого транзисторов и, следовательно, появление сигнала на входе первого инвертора. Так как сигнал на входе первого инвертора появляется быстрее, то он соответственно быстрее переключается и сигнал на его выходе появляется быстрее тоже.

Таким образом, в предлагаемом сумматоре повышено быстродействие формирования сигнала переноса на выходе СOUT.

| название | год | авторы | номер документа |

|---|---|---|---|

| СУММАТОР | 2011 |

|

RU2455680C1 |

| ОДНОРАЗРЯДНЫЙ ДВОИЧНЫЙ СУММАТОР | 2011 |

|

RU2450324C1 |

| ПОЛНЫЙ СУММАТОР | 2011 |

|

RU2475811C1 |

| СУММАТОР | 2011 |

|

RU2469381C1 |

| ОДНОРАЗРЯДНЫЙ ДВОИЧНЫЙ СУММАТОР | 2009 |

|

RU2408922C1 |

| ОДНОРАЗРЯДНЫЙ СУММАТОР | 2009 |

|

RU2408058C2 |

| ОДНОРАЗРЯДНЫЙ СУММАТОР | 2011 |

|

RU2444050C1 |

| СУММАТОР | 2010 |

|

RU2435196C1 |

| ПРЕОБРАЗОВАТЕЛЬ УРОВНЯ НАПРЯЖЕНИЯ | 2017 |

|

RU2667798C1 |

| ПРЕОБРАЗОВАТЕЛЬ УРОВНЯ НАПРЯЖЕНИЯ | 2018 |

|

RU2679186C1 |

Изобретение относится к вычислительной технике и может быть использовано при построении многоразрядных быстродействующих сумматоров и АЛУ. Техническим результатом является повышение быстродействия формирования сигнала переноса на выходе СOUT. Для этого сумматор содержит: полевые транзисторы первый, второй …, двенадцатый 12 - первого типа проводимости, тринадцатый, четырнадцатый …, двадцать четвертый - второго типа проводимости, входы слагаемых А и В, вход переноса СIN, выводы питания первого 25 и второго 26 уровней напряжения, первый инвертор 27, выход которого является выходом сигнала переноса СOUT, второй инвертор 28, выход которого является выходом результата сложения S, двухвходовой логический элемент И-НЕ 29 и двухвходовой логический элемент ИЛИ-НЕ 30. 1 табл., 1 ил.

Сумматор, содержащий полевые транзисторы первый, второй, …, двенадцатый - первого типа проводимости, тринадцатый, четырнадцатый, …, двадцать четвертый - второго типа проводимости, вход слагаемого А, соединенный с затворами первого, пятого, шестого, десятого, четырнадцатого, шестнадцатого, девятнадцатого и двадцать четвертого транзисторов, вход слагаемого В, соединенный с затворами второго, четвертого, седьмого, одиннадцатого, пятнадцатого, семнадцатого, двадцатого и двадцать третьего транзисторов, вход переноса СIN, соединенный с затворами третьего, двенадцатого, тринадцатого и двадцать второго транзисторов, вывод питания первого уровня напряжения, соединенный с истоками первого, второго, четвертого, шестого, седьмого, восьмого и десятого транзисторов, вывод питания второго уровня напряжения, соединенный с истоками четырнадцатого, пятнадцатого, семнадцатого, девятнадцатого, двадцатого, двадцать первого и двадцать четвертого транзисторов, причем стоки первого и второго транзисторов соединены с истоком третьего транзистора, сток четвертого - с истоком пятого, стоки шестого и седьмого - с истоком девятого, сток десятого - с истоком одиннадцатого, сток одиннадцатого - с истоком двенадцатого, стоки четырнадцатого и пятнадцатого - с истоком тринадцатого, сток семнадцатого - с истоком шестнадцатого, стоки девятнадцатого и двадцатого - с истоком восемнадцатого, сток двадцать четвертого - с истоком двадцать третьего и сток двадцать третьего - с истоком двадцать второго и стоки третьего, пятого, тринадцатого и шестнадцатого - с затворами девятого и восемнадцатого транзисторов и входом первого инвертора, выход которого является выходом сигнала переноса СOUT, а стоки девятого, двенадцатого, восемнадцатого и двадцать второго транзисторов - с входом второго инвертора, выход которого является выходом результата сложения S, отличающийся тем, что в него введены двухвходовой логический элемент И-НЕ, первый и второй входы которого соединены с входами слагаемых соответственно А и В, а выход - с затвором восьмого транзистора, сток которого соединен со стоком одиннадцатого и истоком двенадцатого транзисторов, и двухвходовой логический элемент ИЛИ-НЕ, первый и второй входы которого соединены с входами слагаемых соответственно А и В, а выход - с затвором двадцать первого транзистора, сток которого соединен со стоком двадцать третьего и истоком двадцать второго транзисторов.

| IEEE JOURNAL OF SOLID-STATE CIRCUITS, VOL.32, NO.7, JULY 1997, p.1085, Fig.4(p) | |||

| ОДНОРАЗРЯДНЫЙ СУММАТОР НА МОП ТРАНЗИСТОРАХ | 1996 |

|

RU2152641C1 |

| СУММАТОР | 1994 |

|

RU2049346C1 |

| KR 20050023978 A, 10.03.2005 | |||

| US 7185042 B1, 27.02.2007 | |||

| DE 3630605 A1, 17.03.1988 | |||

| JP 2075019, 14.03.1990. | |||

Авторы

Даты

2010-01-27—Публикация

2008-07-28—Подача