Предлагаемое изобретение относится к цифровой вычислительной технике и может быть использовано при согласовании схем, имеющих различные уровни напряжений источников питания и внутренних сигналов.

Известен Преобразователь уровней сигналов на МДП-транзисторах [1]. Это устройство предназначено для преобразования уровня напряжения сигнала (например, при сопряжении ТТЛ- и КМДП логических элементов).

Недостатком указанной выше схемы является низкое быстродействие. Низкое быстродействие схемы вызвано ограничением появления напряжения высокого уровня на выходах схемы по цепи низкой проводимости, вплоть до подключения транзистора с высокой проводимостью, шунтирующего низко-проводящую цепь, которое задерживается на время распространения сигнала, необходимое на последовательное переключение двух вентилей.

Кроме того, каждый из выходных узлов триггера, помимо затворов выходных транзисторов, подключен к затворам двух транзисторов P-типа, что дополнительно увеличивает паразитную емкость выходных узлов триггера и затягивает переходный процесс переключения.

Задачей предлагаемого изобретения является повышение быстродействия Преобразователя уровня напряжения.

Поставленная задача достигается тем, что в Преобразователь уровня напряжения, содержащий полевые транзисторы P-типа с первого по шестой и N-типа - седьмой и восьмой, входы прямого IN и инверсного  входных сигналов, соединенные с затворами, соответственно, седьмого и восьмого транзисторов, стоки которых соединены, соответственно, седьмого - со стоком шестого и затвором пятого транзисторов, а восьмого - со стоком пятого и затвором шестого транзисторов, и истоки транзисторов пятого и шестого соединены, соответственно, со стоками транзисторов второго и третьего, вывод питания высокого уровня напряжения VDD, соединенный с истоками первого, второго, третьего и четвертого транзисторов, вывод питания низкого уровня напряжения GND, введены полевые транзисторы P-типа - девятый и десятый, соединенные своими затворами с выводом питания низкого уровня напряжения GND, истоками, соответственно, со стоками транзисторов первого и четвертого, а стоками, соответственно, со стоками пятого и шестого, полевые транзисторы N-типа с одиннадцатого по шестнадцатый, причем истоки одиннадцатого, двенадцатого, тринадцатого и четырнадцатого транзисторов соединены с выводом питания низкого уровня напряжения GND, а стоки, соответственно, с истоками пятнадцатого, седьмого, восьмого и шестнадцатого транзисторов, затворы пятнадцатого и шестнадцатого - с выводом питания высокого уровня напряжения VDD, а одиннадцатого и четырнадцатого, соответственно, с входами входных сигналов инверсного

входных сигналов, соединенные с затворами, соответственно, седьмого и восьмого транзисторов, стоки которых соединены, соответственно, седьмого - со стоком шестого и затвором пятого транзисторов, а восьмого - со стоком пятого и затвором шестого транзисторов, и истоки транзисторов пятого и шестого соединены, соответственно, со стоками транзисторов второго и третьего, вывод питания высокого уровня напряжения VDD, соединенный с истоками первого, второго, третьего и четвертого транзисторов, вывод питания низкого уровня напряжения GND, введены полевые транзисторы P-типа - девятый и десятый, соединенные своими затворами с выводом питания низкого уровня напряжения GND, истоками, соответственно, со стоками транзисторов первого и четвертого, а стоками, соответственно, со стоками пятого и шестого, полевые транзисторы N-типа с одиннадцатого по шестнадцатый, причем истоки одиннадцатого, двенадцатого, тринадцатого и четырнадцатого транзисторов соединены с выводом питания низкого уровня напряжения GND, а стоки, соответственно, с истоками пятнадцатого, седьмого, восьмого и шестнадцатого транзисторов, затворы пятнадцатого и шестнадцатого - с выводом питания высокого уровня напряжения VDD, а одиннадцатого и четырнадцатого, соответственно, с входами входных сигналов инверсного  и прямого IN, и первый и второй инверторы, входы которых соединены, соответственно, первого инвертора со стоками транзисторов девятого и пятнадцатого и второго - со стоками десятого и шестнадцатого, выход первого инвертора - с затворами транзисторов первого, третьего и двенадцатого и является инверсным выходом

и прямого IN, и первый и второй инверторы, входы которых соединены, соответственно, первого инвертора со стоками транзисторов девятого и пятнадцатого и второго - со стоками десятого и шестнадцатого, выход первого инвертора - с затворами транзисторов первого, третьего и двенадцатого и является инверсным выходом  Преобразователя уровня напряжения, а выход второго инвертора - с затворами транзисторов второго, четвертого и тринадцатого и является прямым выходом OUT Преобразователя уровня напряжения.

Преобразователя уровня напряжения, а выход второго инвертора - с затворами транзисторов второго, четвертого и тринадцатого и является прямым выходом OUT Преобразователя уровня напряжения.

Таким образом, в предлагаемой схеме Преобразователя уровня напряжения, вследствие отличий от известного устройства, описанных выше, в любом установившемся статическом режиме в парах цепочек транзисторов высокой проводимости, состоящих из транзисторов P-типа второго и пятого, третьего и шестого, и N-типа седьмого и двенадцатого, восьмого и тринадцатого, один из транзисторов всегда закрыт. Схема подключения элементов в предлагаемом Преобразователе уровня напряжения исключает протекание тока во время переходных процессов одновременно по цепочкам высокой проводимости Р- и N-типа. Поэтому переходные процессы по перезаряду выходных емкостей триггера всегда протекают по цепочкам транзисторов высокой проводимости одного типа и цепочкам транзисторов низкой проводимости противоположного типа.

Также, в отличие от известного Преобразователя уровней сигналов на МДП-транзисторах [1], в предлагаемой схеме Преобразователя уровня напряжения исключено подключение лишних затворов транзисторов P-типа, которые в предлагаемом Преобразователе уровня напряжения подключены к выходам Первого и Второго инверторов. Предложенное соединение уменьшает паразитную емкость выходных узлов триггера и дополнительно ускоряет переходный процесс переключения Преобразователя уровня напряжения.

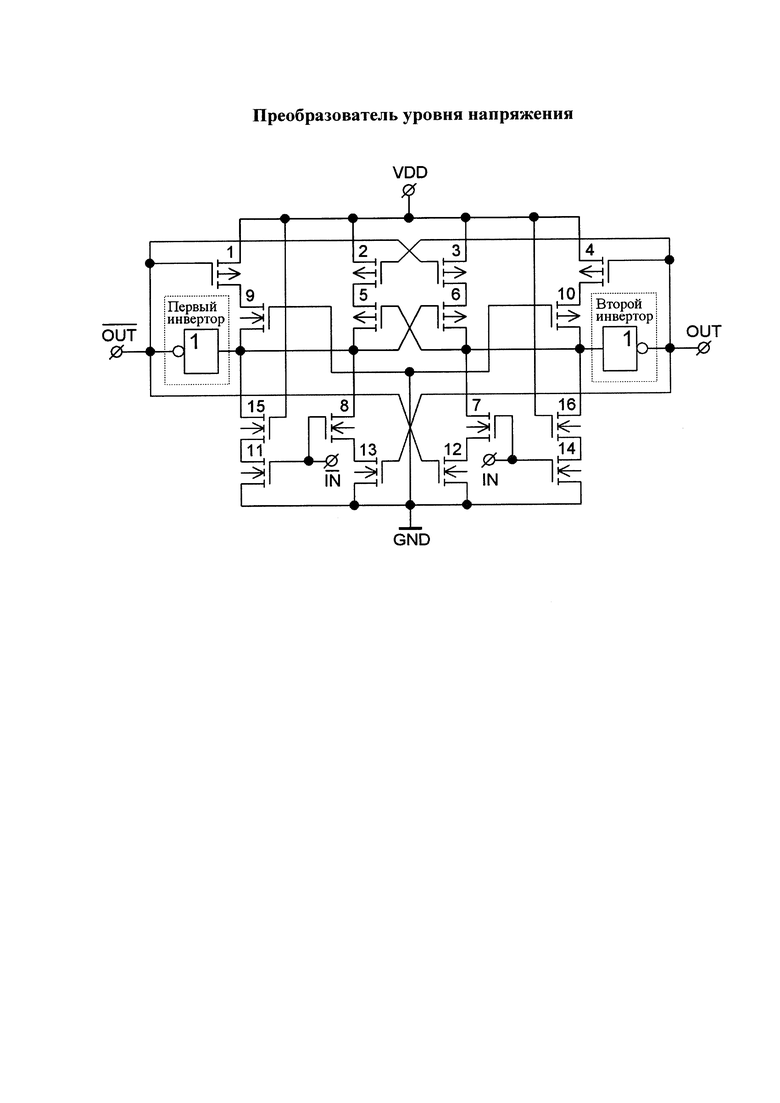

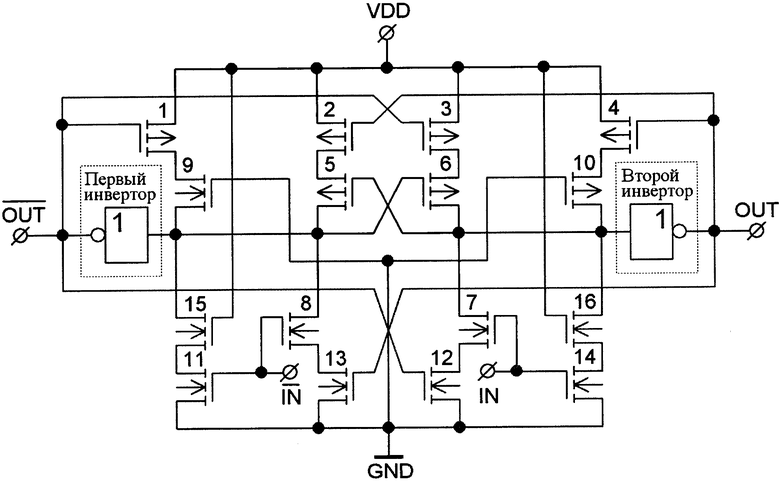

На чертеже приведена схема предлагаемого Преобразователя уровня напряжения.

Предлагаемый Преобразователь уровня напряжения, содержит полевые транзисторы P-типа с первого по шестой (1-6), девятый (9) и десятый (10) и N-типа седьмой (7), восьмой (8) и с одиннадцатого по шестнадцатый (11-16), вход прямого входного сигнала IN, соединенный с затворами транзисторов седьмого (7) и четырнадцатого (14) и вход инверсного входного сигнала  , соединенный с затворами транзисторов восьмого (8) и одиннадцатого (11), вывод питания высокого уровня напряжения VDD, соединенный с истоками транзисторов с первого по четвертый (1-4) и затворами транзисторов пятнадцатого (15) и шестнадцатого (16), вывод питания низкого уровня напряжения GND, соединенный с истоками транзисторов с одиннадцатого по четырнадцатый (11-14) и затворами транзисторов девятого (9) и десятого (10), причем стоки транзисторов первого (1), второго (2), третьего (3) и четвертого (4) соединены, соответственно, с истоками транзисторов девятого (9), пятого (5), шестого (6) и десятого (10), стоки транзисторов одиннадцатого (11), двенадцатого (12), тринадцатого (13) и четырнадцатого (14) соединены, соответственно, с истоками транзисторов пятнадцатого (15), седьмого (7), восьмого (8) и шестнадцатого (16), стоки транзисторов пятого (5) и девятого (9) соединены со стоками транзисторов восьмого (8) и пятнадцатого (15), затвором шестого (6) и входом первого инвертора, выход которого соединен с затворами транзисторов первого (1), третьего (3) и двенадцатого (12) и является инверсным выходом

, соединенный с затворами транзисторов восьмого (8) и одиннадцатого (11), вывод питания высокого уровня напряжения VDD, соединенный с истоками транзисторов с первого по четвертый (1-4) и затворами транзисторов пятнадцатого (15) и шестнадцатого (16), вывод питания низкого уровня напряжения GND, соединенный с истоками транзисторов с одиннадцатого по четырнадцатый (11-14) и затворами транзисторов девятого (9) и десятого (10), причем стоки транзисторов первого (1), второго (2), третьего (3) и четвертого (4) соединены, соответственно, с истоками транзисторов девятого (9), пятого (5), шестого (6) и десятого (10), стоки транзисторов одиннадцатого (11), двенадцатого (12), тринадцатого (13) и четырнадцатого (14) соединены, соответственно, с истоками транзисторов пятнадцатого (15), седьмого (7), восьмого (8) и шестнадцатого (16), стоки транзисторов пятого (5) и девятого (9) соединены со стоками транзисторов восьмого (8) и пятнадцатого (15), затвором шестого (6) и входом первого инвертора, выход которого соединен с затворами транзисторов первого (1), третьего (3) и двенадцатого (12) и является инверсным выходом  Преобразователя уровня напряжения, а стоки транзисторов шестого (6) и десятого (10) соединены со стоками транзисторов седьмого (7) и шестнадцатого (16), затвором пятого (5) и входом Второго инвертора, выход которого соединен с затворами транзисторов второго (2), четвертого (4) и тринадцатого (13) и является прямым выходом OUT Преобразователя уровня напряжения.

Преобразователя уровня напряжения, а стоки транзисторов шестого (6) и десятого (10) соединены со стоками транзисторов седьмого (7) и шестнадцатого (16), затвором пятого (5) и входом Второго инвертора, выход которого соединен с затворами транзисторов второго (2), четвертого (4) и тринадцатого (13) и является прямым выходом OUT Преобразователя уровня напряжения.

Предлагаемый Преобразователь уровня напряжения представляет собой цифровое логическое устройство, предназначенное для преобразования входного напряжения логической единицы «1*» (VCC), в напряжение логической «1», соответствующее напряжению питания высокого уровня напряжения VDD и работает следующим образом.

Исходное состояние. На вывод питания GND и на вход IN подано напряжение низкого уровня, соответствующее напряжению логического «0», на вывод VDD - высокого («1»), а на вход  - напряжение логической единицы «1*» (VCC). Минимальное значение напряжения логической единицы «1*» должно быть больше либо равно значению порогового напряжения транзистора N-типа. Кроме того, напряжение источника питания высокого уровня VDD («1») и напряжение логической единицы VCC («1*») должны быть больше или равны сумме пороговых напряжений транзисторов Р- и N-типа. Транзисторы низкой проводимости P-типа 9 и 10 и N-типа 15 и 16 открыты всегда, т.к. их затворы подключены, соответственно, 9 и 10 - к источнику питания низкого уровня напряжения GND («0»), а 15 и 16 - к источнику питания высокого уровня напряжения VDD («1»). На затворы транзисторов N-типа 7 и 14 с входа IN поступает напряжение низкого уровня GND («0»), а на затворы транзисторов N-типа 8 и 11 с входа

- напряжение логической единицы «1*» (VCC). Минимальное значение напряжения логической единицы «1*» должно быть больше либо равно значению порогового напряжения транзистора N-типа. Кроме того, напряжение источника питания высокого уровня VDD («1») и напряжение логической единицы VCC («1*») должны быть больше или равны сумме пороговых напряжений транзисторов Р- и N-типа. Транзисторы низкой проводимости P-типа 9 и 10 и N-типа 15 и 16 открыты всегда, т.к. их затворы подключены, соответственно, 9 и 10 - к источнику питания низкого уровня напряжения GND («0»), а 15 и 16 - к источнику питания высокого уровня напряжения VDD («1»). На затворы транзисторов N-типа 7 и 14 с входа IN поступает напряжение низкого уровня GND («0»), а на затворы транзисторов N-типа 8 и 11 с входа  поступает напряжение логической единицы VCC («1*»). Поэтому транзисторы 7 и 14 закрыты, а транзисторы 8 и 11 открыты. Кроме того, в результате действия предыдущего регенеративного цикла транзисторы 2, 4, 6 и 12 открыты, а транзисторы 1, 3, 5 и 13 закрыты. Поэтому на входе первого инвертора установлено напряжение низкого уровня GND («0»), и, следовательно, на выходе

поступает напряжение логической единицы VCC («1*»). Поэтому транзисторы 7 и 14 закрыты, а транзисторы 8 и 11 открыты. Кроме того, в результате действия предыдущего регенеративного цикла транзисторы 2, 4, 6 и 12 открыты, а транзисторы 1, 3, 5 и 13 закрыты. Поэтому на входе первого инвертора установлено напряжение низкого уровня GND («0»), и, следовательно, на выходе  Преобразователя уровня напряжения - напряжение высокого уровня VDD («1»), а на входе второго инвертора напряжение высокого уровня VDD («1»), и, следовательно, на выходе OUT Преобразователя уровня напряжения - напряжение низкого уровня GND («0»).

Преобразователя уровня напряжения - напряжение высокого уровня VDD («1»), а на входе второго инвертора напряжение высокого уровня VDD («1»), и, следовательно, на выходе OUT Преобразователя уровня напряжения - напряжение низкого уровня GND («0»).

В режиме преобразования высокого напряжения логической единицы «1*» (VCC) в напряжение высокого уровня VDD на выходе OUT, а на выходе  напряжения низкого уровня GND, на вход IN, и следовательно, на затворы транзисторов N-типа 7 и 14, поступает напряжение логической единицы «1*» (VCC), а на вход

напряжения низкого уровня GND, на вход IN, и следовательно, на затворы транзисторов N-типа 7 и 14, поступает напряжение логической единицы «1*» (VCC), а на вход  , и, следовательно, на затворы транзисторов N-типа 8 и 11, - напряжение низкого уровня GND, в результате чего транзисторы 7 и 14 открываются, а транзисторы 8 и 11 - закрываются. Через открытые транзисторы 12 и 7, на затвор транзистора 5 и на вход второго инвертора поступает напряжение низкого уровня GND. Поэтому транзистор P-типа 5 открывается, а на выходе второго инвертора формируется напряжение высокого уровня VDD. Одновременно через открытые транзисторы P-типа 2 и 5 напряжение высокого уровня VDD поступает на затвор транзистора 6 и вход первого инвертора. Поэтому транзистор P-типа 6 закрывается, а на выходе первого инвертора формируется напряжение низкого уровня GND. Напряжение высокого уровня VDD с выхода второго инвертора поступает на затворы транзисторов 2 и 13 и прямой выход OUT Преобразователя уровня напряжения. Поэтому транзистор P-типа 2 закрывается, N-типа 13 открывается, а на прямом выходе OUT Преобразователя уровня напряжения устанавливается напряжение высокого уровня VDD. Одновременно, напряжение низкого уровня GND с выхода первого инвертора поступает на затворы транзисторов 3 и 12 и инверсный выход

, и, следовательно, на затворы транзисторов N-типа 8 и 11, - напряжение низкого уровня GND, в результате чего транзисторы 7 и 14 открываются, а транзисторы 8 и 11 - закрываются. Через открытые транзисторы 12 и 7, на затвор транзистора 5 и на вход второго инвертора поступает напряжение низкого уровня GND. Поэтому транзистор P-типа 5 открывается, а на выходе второго инвертора формируется напряжение высокого уровня VDD. Одновременно через открытые транзисторы P-типа 2 и 5 напряжение высокого уровня VDD поступает на затвор транзистора 6 и вход первого инвертора. Поэтому транзистор P-типа 6 закрывается, а на выходе первого инвертора формируется напряжение низкого уровня GND. Напряжение высокого уровня VDD с выхода второго инвертора поступает на затворы транзисторов 2 и 13 и прямой выход OUT Преобразователя уровня напряжения. Поэтому транзистор P-типа 2 закрывается, N-типа 13 открывается, а на прямом выходе OUT Преобразователя уровня напряжения устанавливается напряжение высокого уровня VDD. Одновременно, напряжение низкого уровня GND с выхода первого инвертора поступает на затворы транзисторов 3 и 12 и инверсный выход  Преобразователя уровня напряжения. Поэтому транзистор P-типа 3 закрывается, N-типа 12 открывается, а на инверсном выходе

Преобразователя уровня напряжения. Поэтому транзистор P-типа 3 закрывается, N-типа 12 открывается, а на инверсном выходе  Преобразователя уровня напряжения устанавливается напряжение низкого уровня GND. Таким образом, в парах цепочек транзисторов высокой проводимости P-типа второго 2 и пятого 5, третьего 3 и шестого 6, и N-типа седьмого 7 и двенадцатого 12, восьмого 8 и тринадцатого 13, один из транзисторов (в данном режиме 2, 6, 8 и 12) закрыт, и на инверсном выходе

Преобразователя уровня напряжения устанавливается напряжение низкого уровня GND. Таким образом, в парах цепочек транзисторов высокой проводимости P-типа второго 2 и пятого 5, третьего 3 и шестого 6, и N-типа седьмого 7 и двенадцатого 12, восьмого 8 и тринадцатого 13, один из транзисторов (в данном режиме 2, 6, 8 и 12) закрыт, и на инверсном выходе  Преобразователя уровня напряжения установлено напряжение низкого уровня GND («0»), а на прямом выходе OUT Преобразователя уровня напряжения - напряжение высокого уровня VDD («1»), полученное преобразованием входного высокого напряжения логической единицы «1*» (VCC).

Преобразователя уровня напряжения установлено напряжение низкого уровня GND («0»), а на прямом выходе OUT Преобразователя уровня напряжения - напряжение высокого уровня VDD («1»), полученное преобразованием входного высокого напряжения логической единицы «1*» (VCC).

При переходе Преобразователя уровня напряжения в исходное состояние и режим формирования на выходе OUT напряжения низкого уровня GND, а на выходе  напряжения высокого уровня VDD, на вход IN, и следовательно, на затворы транзисторов N-типа 7 и 14, поступает напряжение низкого уровня GND, а на вход

напряжения высокого уровня VDD, на вход IN, и следовательно, на затворы транзисторов N-типа 7 и 14, поступает напряжение низкого уровня GND, а на вход  , и, следовательно, на затворы транзисторов N-типа 8 и 11, - напряжение логической единицы «1*» (VCC), в результате чего транзисторы 7 и 14 закрываются, а транзисторы 8 и 11 - открываются. Через открытые транзисторы 13 и 8, на затвор транзистора 6 и на вход первого инвертора поступает напряжение низкого уровня GND. Поэтому транзистор P-типа 6 открывается, а на выходе первого инвертора формируется напряжение высокого уровня VDD. Одновременно через открытые транзисторы P-типа 3 и 6 напряжение высокого уровня VDD поступает на затвор транзистора 5 и вход второго инвертора. Поэтому транзистор P-типа 5 закрывается, а на выходе первого инвертора формируется напряжение низкого уровня GND. Напряжение низкого уровня GND с выхода второго инвертора поступает на затворы транзисторов 2 и 13 и прямой выход OUT Преобразователя уровня напряжения. Поэтому транзистор P-типа 2 открывается, N-типа 13 закрывается, а на прямом выходе OUT Преобразователя уровня напряжения устанавливается напряжение низкого уровня GND. Одновременно, напряжение высокого уровня VDD с выхода первого инвертора поступает на затворы транзисторов 3 и 12 и инверсный выход

, и, следовательно, на затворы транзисторов N-типа 8 и 11, - напряжение логической единицы «1*» (VCC), в результате чего транзисторы 7 и 14 закрываются, а транзисторы 8 и 11 - открываются. Через открытые транзисторы 13 и 8, на затвор транзистора 6 и на вход первого инвертора поступает напряжение низкого уровня GND. Поэтому транзистор P-типа 6 открывается, а на выходе первого инвертора формируется напряжение высокого уровня VDD. Одновременно через открытые транзисторы P-типа 3 и 6 напряжение высокого уровня VDD поступает на затвор транзистора 5 и вход второго инвертора. Поэтому транзистор P-типа 5 закрывается, а на выходе первого инвертора формируется напряжение низкого уровня GND. Напряжение низкого уровня GND с выхода второго инвертора поступает на затворы транзисторов 2 и 13 и прямой выход OUT Преобразователя уровня напряжения. Поэтому транзистор P-типа 2 открывается, N-типа 13 закрывается, а на прямом выходе OUT Преобразователя уровня напряжения устанавливается напряжение низкого уровня GND. Одновременно, напряжение высокого уровня VDD с выхода первого инвертора поступает на затворы транзисторов 3 и 12 и инверсный выход  Преобразователя уровня напряжения. Поэтому транзистор P-типа 3 открывается, N-типа 12 закрывается, а на инверсном выходе

Преобразователя уровня напряжения. Поэтому транзистор P-типа 3 открывается, N-типа 12 закрывается, а на инверсном выходе  Преобразователя уровня напряжения устанавливается напряжение высокого уровня VDD. Таким образом, в парах цепочек транзисторов высокой проводимости P-типа второго 2 и пятого 5, третьего 3 и шестого 6, и N-типа седьмого 7 и двенадцатого 12, восьмого 8 и тринадцатого 13, один из транзисторов (в данном режиме 3, 5, 7 и 13) закрыт, и на инверсном выходе

Преобразователя уровня напряжения устанавливается напряжение высокого уровня VDD. Таким образом, в парах цепочек транзисторов высокой проводимости P-типа второго 2 и пятого 5, третьего 3 и шестого 6, и N-типа седьмого 7 и двенадцатого 12, восьмого 8 и тринадцатого 13, один из транзисторов (в данном режиме 3, 5, 7 и 13) закрыт, и на инверсном выходе  Преобразователя уровня напряжения установлено напряжение высокого уровня VDD («1»), полученное преобразованием входного высокого напряжения логической единицы «1*» (VCC), а на прямом выходе OUT Преобразователя уровня напряжения - напряжение низкого уровня GND («0»). Схема Преобразователя уровня напряжения возвращается в исходное состояние.

Преобразователя уровня напряжения установлено напряжение высокого уровня VDD («1»), полученное преобразованием входного высокого напряжения логической единицы «1*» (VCC), а на прямом выходе OUT Преобразователя уровня напряжения - напряжение низкого уровня GND («0»). Схема Преобразователя уровня напряжения возвращается в исходное состояние.

Таким образом, в предлагаемом Преобразователе уровня напряжения исключено протекание тока во время переходных процессов одновременно по цепочкам высокой проводимости Р- и N-типа. Поэтому формирование выходных сигналов высокого уровня VDD («1») на выходах прямом OUT или инверсном  проходит в переходном процессе противостояния тока, протекающего через цепочки транзисторов высокой проводимости и цепочки транзисторов низкой проводимости, что существенно ускоряет время этих переходных процессов по перезаряду выходных емкостей триггера, и, тем самым, повышает общее быстродействие работы схемы.

проходит в переходном процессе противостояния тока, протекающего через цепочки транзисторов высокой проводимости и цепочки транзисторов низкой проводимости, что существенно ускоряет время этих переходных процессов по перезаряду выходных емкостей триггера, и, тем самым, повышает общее быстродействие работы схемы.

Кроме того, в предлагаемом Преобразователе уровня напряжения, в отличие от известного Преобразователя уровней сигналов на МДП-транзисторах [1], к выходным узлам триггера, помимо затворов транзисторов инвертора, подключен затвор только одного транзистора P-типа, что уменьшает паразитную емкость выходных узлов триггера и дополнительно ускоряет переходный процесс переключения Преобразователя уровня напряжения.

Литература

1. Авторское свидетельство СССР (SU) №1538246, «Преобразователь уровней сигналов на МДП-транзисторах», / В.А. Максимов, А.Е. Заболотный и Я.Я. Петричкович // Бюллетень №3 от 23.01.90.

| название | год | авторы | номер документа |

|---|---|---|---|

| ПРЕОБРАЗОВАТЕЛЬ УРОВНЯ НАПРЯЖЕНИЯ | 2018 |

|

RU2679186C1 |

| ПРЕОБРАЗОВАТЕЛЬ УРОВНЯ НАПРЯЖЕНИЯ | 2016 |

|

RU2604054C1 |

| ПРЕОБРАЗОВАТЕЛЬ УРОВНЯ НАПРЯЖЕНИЯ | 2020 |

|

RU2739487C1 |

| ПРЕОБРАЗОВАТЕЛЬ УРОВНЯ НАПРЯЖЕНИЯ | 2021 |

|

RU2756445C1 |

| ПРЕОБРАЗОВАТЕЛЬ УРОВНЯ НАПРЯЖЕНИЯ | 2016 |

|

RU2632567C1 |

| ПРЕОБРАЗОВАТЕЛЬ ЛОГИЧЕСКОГО УРОВНЯ НАПРЯЖЕНИЯ | 2016 |

|

RU2642416C1 |

| ЭЛЕМЕНТ ВХОДНОГО РЕГИСТРА | 2021 |

|

RU2771447C1 |

| ЭЛЕМЕНТ ВХОДНОГО РЕГИСТРА | 2022 |

|

RU2787930C1 |

| ВЫСОКОВОЛЬТНЫЙ ПРЕОБРАЗОВАТЕЛЬ УРОВНЯ НАПРЯЖЕНИЯ | 2019 |

|

RU2702979C1 |

| ЛОГИЧЕСКИЙ ВЕНТИЛЬ ИСКЛЮЧАЮЩЕЕ-ИЛИ | 2023 |

|

RU2802665C1 |

Изобретение относится к области вычислительной техники и может быть использовано при согласовании схем, имеющих различные уровни напряжений источников питания и внутренних сигналов. Технический результат – повышение быстродействия преобразователя уровня напряжения. Преобразователь уровня напряжения содержит восемь полевых транзисторов P-типа (1-6, 9, 10) и восемь N-типа (7, 8, 11-16), входы прямого (IN) и инверсного ( ) входных сигналов, вывод питания высокого уровня напряжения (VDD), вывод питания низкого уровня напряжения (GND) и выходы прямой (OUT) и инверсный (

) входных сигналов, вывод питания высокого уровня напряжения (VDD), вывод питания низкого уровня напряжения (GND) и выходы прямой (OUT) и инверсный ( ). 1 ил.

). 1 ил.

Преобразователь уровня напряжения, содержащий полевые транзисторы Р-типа с первого по шестой и N-типа - седьмой и восьмой, входы прямого (IN) и инверсного ( ) входных сигналов, соединенные с затворами, соответственно, седьмого и восьмого транзисторов, стоки которых соединены, соответственно, седьмого - со стоком шестого и затвором пятого транзисторов, а восьмого - со стоком пятого и затвором шестого транзисторов, и истоки транзисторов пятого и шестого соединены, соответственно, со стоками транзисторов второго и третьего, вывод питания высокого уровня напряжения (VDD), соединенный с истоками первого, второго, третьего и четвертого транзисторов, вывод питания низкого уровня напряжения (GND), отличающийся тем, что в него введены полевые транзисторы Р-типа - девятый и десятый, соединенные своими затворами с выводом питания низкого уровня напряжения (GND), истоками, соответственно, со стоками транзисторов первого и четвертого, а стоками, соответственно, со стоками пятого и шестого, полевые транзисторы N-типа с одиннадцатого по шестнадцатый, причем истоки одиннадцатого, двенадцатого, тринадцатого и четырнадцатого транзисторов соединены с выводом питания низкого уровня напряжения (GND), а стоки, соответственно, с истоками пятнадцатого, седьмого, восьмого и шестнадцатого транзисторов, затворы пятнадцатого и шестнадцатого - с выводом питания высокого уровня напряжения (VDD), а одиннадцатого и четырнадцатого, соответственно, с входами входных сигналов инверсного (

) входных сигналов, соединенные с затворами, соответственно, седьмого и восьмого транзисторов, стоки которых соединены, соответственно, седьмого - со стоком шестого и затвором пятого транзисторов, а восьмого - со стоком пятого и затвором шестого транзисторов, и истоки транзисторов пятого и шестого соединены, соответственно, со стоками транзисторов второго и третьего, вывод питания высокого уровня напряжения (VDD), соединенный с истоками первого, второго, третьего и четвертого транзисторов, вывод питания низкого уровня напряжения (GND), отличающийся тем, что в него введены полевые транзисторы Р-типа - девятый и десятый, соединенные своими затворами с выводом питания низкого уровня напряжения (GND), истоками, соответственно, со стоками транзисторов первого и четвертого, а стоками, соответственно, со стоками пятого и шестого, полевые транзисторы N-типа с одиннадцатого по шестнадцатый, причем истоки одиннадцатого, двенадцатого, тринадцатого и четырнадцатого транзисторов соединены с выводом питания низкого уровня напряжения (GND), а стоки, соответственно, с истоками пятнадцатого, седьмого, восьмого и шестнадцатого транзисторов, затворы пятнадцатого и шестнадцатого - с выводом питания высокого уровня напряжения (VDD), а одиннадцатого и четырнадцатого, соответственно, с входами входных сигналов инверсного ( ) и прямого (IN), и первый и второй инверторы, входы которых соединены, соответственно, первого инвертора со стоками транзисторов девятого и пятнадцатого и второго - со стоками десятого и шестнадцатого, выход первого инвертора - с затворами транзисторов первого, третьего и двенадцатого и является инверсным выходом (

) и прямого (IN), и первый и второй инверторы, входы которых соединены, соответственно, первого инвертора со стоками транзисторов девятого и пятнадцатого и второго - со стоками десятого и шестнадцатого, выход первого инвертора - с затворами транзисторов первого, третьего и двенадцатого и является инверсным выходом ( ) преобразователя уровня напряжения, а выход второго инвертора - с затворами транзисторов второго, четвертого и тринадцатого и является прямым выходом (OUT) преобразователя уровня напряжения.

) преобразователя уровня напряжения, а выход второго инвертора - с затворами транзисторов второго, четвертого и тринадцатого и является прямым выходом (OUT) преобразователя уровня напряжения.

| Преобразователь уровней сигналов на МДП-транзисторах | 1988 |

|

SU1538246A1 |

| Преобразователь уровней напряжения на дополняющих МДП-транзисторах | 1983 |

|

SU1129739A1 |

| Преобразователь уровней (его варианты) | 1985 |

|

SU1256165A1 |

| Устройство преобразования уровней логических сигналов на КМОП-транзисторах | 1989 |

|

SU1775853A1 |

| Пломбировальные щипцы | 1923 |

|

SU2006A1 |

| US 7804326 B1, 28.09.2010 | |||

| Токарный резец | 1924 |

|

SU2016A1 |

Авторы

Даты

2018-09-24—Публикация

2017-11-20—Подача