Предлагаемое изобретение относится к цифровой вычислительной технике и может быть использовано при согласовании схем, имеющих различные уровни напряжений источников питания и внутренних сигналов.

Известен Преобразователь уровня напряжения [1]. Это устройство предназначено для преобразования уровня напряжения сигнала (например, при сопряжении ТТЛ- и КМДП логических элементов).

Недостатком указанной выше схемы является низкое быстродействие. Низкое быстродействие схемы вызвано ограничением появления напряжения высокого уровня на входах выходных инверторах по цепи низкой проводимости, вплоть до подключения транзистора с высокой проводимостью, шунтирующего низко-проводящую цепь, которое задерживается на время распространения сигнала, необходимое на последовательное переключение двух вентилей.

Задачей предлагаемого изобретения является повышение быстродействия Преобразователя уровня напряжения.

Поставленная задача достигается тем, что в Преобразователь уровня напряжения, содержащий полевые транзисторы Р-типа с первого по шестой и N-типа - с седьмого по десятый, входы прямого IN и инверсного  входных сигналов, соединенные с затворами, соответственно, седьмого и восьмого транзисторов, стоки которых соединены, соответственно, седьмого - со стоком шестого и затвором пятого транзисторов, а восьмого - со стоком пятого и затвором шестого транзисторов, и истоки транзисторов пятого и шестого соединены, пятого - со стоками транзисторов первого и второго, а шестого - со стоками третьего и четвертого, вывод питания высокого уровня напряжения VDD, соединенный с истоками транзисторов с первого по четвертый, вывод питания низкого уровня напряжения GND, соединенный с истоками транзисторов девятого и десятого и затворами транзисторов первого и четвертого, прямой выход OUT, соединенный с затвором второго транзистора и инверсный выход

входных сигналов, соединенные с затворами, соответственно, седьмого и восьмого транзисторов, стоки которых соединены, соответственно, седьмого - со стоком шестого и затвором пятого транзисторов, а восьмого - со стоком пятого и затвором шестого транзисторов, и истоки транзисторов пятого и шестого соединены, пятого - со стоками транзисторов первого и второго, а шестого - со стоками третьего и четвертого, вывод питания высокого уровня напряжения VDD, соединенный с истоками транзисторов с первого по четвертый, вывод питания низкого уровня напряжения GND, соединенный с истоками транзисторов девятого и десятого и затворами транзисторов первого и четвертого, прямой выход OUT, соединенный с затвором второго транзистора и инверсный выход  , соединенный с затвором третьего транзистора, введены полевые транзисторы N-типа с одиннадцатого по четырнадцатый и Первый и Второй инверторы, входы которых соединены, соответственно, Первого инвертора - со стоками пятого, восьмого и одиннадцатого транзисторов, и Второго - стоками шестого, седьмого и двенадцатого транзисторов, а выходы, соответственно, Первого инвертора - с инверсным выходом

, соединенный с затвором третьего транзистора, введены полевые транзисторы N-типа с одиннадцатого по четырнадцатый и Первый и Второй инверторы, входы которых соединены, соответственно, Первого инвертора - со стоками пятого, восьмого и одиннадцатого транзисторов, и Второго - стоками шестого, седьмого и двенадцатого транзисторов, а выходы, соответственно, Первого инвертора - с инверсным выходом  и затвором десятого транзистора, сток которого соединен с истоком седьмого, и Второго инвертора - с прямым выходом OUT и затвором девятого транзистора, сток которого соединен с истоком восьмого, причем затворы одиннадцатого и двенадцатого транзисторов соединены с выводом питания высокого уровня напряжения VDD, а истоки, соответственно, со стоками тринадцатого и четырнадцатого транзисторов, истоки которых соединены с выводом питания низкого уровня напряжения GND, а затворы, соответственно, с входами прямого IN и инверсного

и затвором десятого транзистора, сток которого соединен с истоком седьмого, и Второго инвертора - с прямым выходом OUT и затвором девятого транзистора, сток которого соединен с истоком восьмого, причем затворы одиннадцатого и двенадцатого транзисторов соединены с выводом питания высокого уровня напряжения VDD, а истоки, соответственно, со стоками тринадцатого и четырнадцатого транзисторов, истоки которых соединены с выводом питания низкого уровня напряжения GND, а затворы, соответственно, с входами прямого IN и инверсного  входных сигналов.

входных сигналов.

Таким образом, в предлагаемой схеме Преобразователя уровня напряжения, вследствие отличий от известного устройства, описанных выше, в любом установившемся статическом режиме в парах цепочек транзисторов высокой проводимости, состоящих из транзисторов Р-типа второго и пятого, третьего и шестого, и N-типа седьмого и десятого, восьмого и девятого, один из транзисторов всегда закрыт.Схема подключения элементов в предлагаемом Преобразователе уровня напряжения исключает протекание тока во время переходных процессов одновременно по цепочкам высокой проводимости Р- и N-типа. Поэтому переходные процессы по перезаряду узловых емкостей триггера, к которым подключены выходные первый и второй инверторы, всегда протекают по цепочкам транзисторов высокой проводимости одного типа и цепочкам транзисторов низкой проводимости противоположного типа.

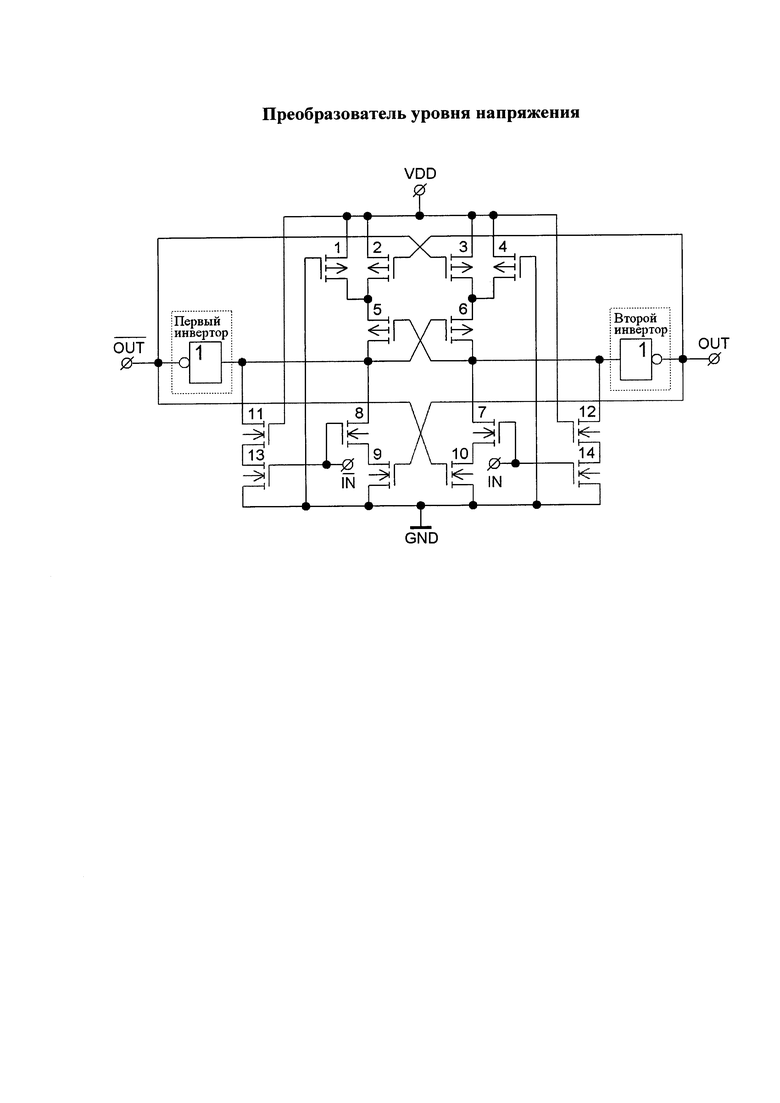

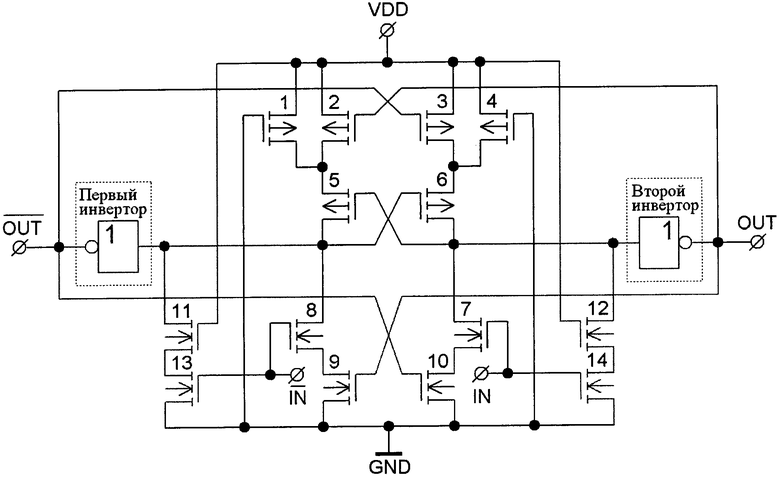

На чертеже приведена схема предлагаемого Преобразователя уровня напряжения.

Предлагаемый Преобразователь уровня напряжения, содержит полевые транзисторы Р-типа с первого по шестой (1-6) и N-типа с седьмого по четырнадцатый (7-14), вход прямого входного сигнала IN, соединенный с затворами транзисторов седьмого (7) и четырнадцатого (14) и вход инверсного входного сигнала  , соединенный с затворами транзисторов восьмого (8) и тринадцатого (13), вывод питания высокого уровня напряжения VDD, соединенный с истоками транзисторов с первого по четвертый (1-4) и затворами транзисторов одиннадцатого (11) и двенадцатого (12), вывод питания низкого уровня напряжения GND, соединенный с истоками транзисторов девятого (9), десятого (10), тринадцатого (13), четырнадцатого (14) и затворами транзисторов первого (1) и четвертого (4), причем стоки транзисторов первого (1) и второго (2) соединены с истоком пятого (5), третьего (3) и четвертого (4) - с истоком шестого (6), а стоки транзисторов девятого (9), десятого (10), тринадцатого (13) и четырнадцатого (14) - с истоками, соответственно, восьмого (8), седьмого (7), одиннадцатого (11) и двенадцатого (12). Стоки транзисторов пятого (5), восьмого (8) и одиннадцатого (11) соединены с затвором шестого (6) транзистора и входом Первого инвертора, выход которого является инверсным выходом

, соединенный с затворами транзисторов восьмого (8) и тринадцатого (13), вывод питания высокого уровня напряжения VDD, соединенный с истоками транзисторов с первого по четвертый (1-4) и затворами транзисторов одиннадцатого (11) и двенадцатого (12), вывод питания низкого уровня напряжения GND, соединенный с истоками транзисторов девятого (9), десятого (10), тринадцатого (13), четырнадцатого (14) и затворами транзисторов первого (1) и четвертого (4), причем стоки транзисторов первого (1) и второго (2) соединены с истоком пятого (5), третьего (3) и четвертого (4) - с истоком шестого (6), а стоки транзисторов девятого (9), десятого (10), тринадцатого (13) и четырнадцатого (14) - с истоками, соответственно, восьмого (8), седьмого (7), одиннадцатого (11) и двенадцатого (12). Стоки транзисторов пятого (5), восьмого (8) и одиннадцатого (11) соединены с затвором шестого (6) транзистора и входом Первого инвертора, выход которого является инверсным выходом  Преобразователя уровня напряжения, а стоки транзисторов шестого (6), седьмого (7) и двенадцатого (12) соединены с затвором пятого (5) транзистора и входом Второго инвертора, выход которого является прямым выходом OUT Преобразователя уровня напряжения.

Преобразователя уровня напряжения, а стоки транзисторов шестого (6), седьмого (7) и двенадцатого (12) соединены с затвором пятого (5) транзистора и входом Второго инвертора, выход которого является прямым выходом OUT Преобразователя уровня напряжения.

Предлагаемый Преобразователь уровня напряжения представляет собой цифровое логическое устройство, предназначенное для преобразования входного напряжения логической единицы «1*» (VCC), в напряжение логической «1», соответствующее напряжению питания высокого уровня напряжения VDD и работает следующим образом.

Исходное состояние. На вывод питания GND и на вход IN подано напряжение низкого уровня, соответствующее напряжению логического «0», на вывод VDD - высокого («1»), а на вход  - напряжение логической единицы «1*» (VCC). Транзисторы низкой проводимости Р-типа 1 и 4 и N-типа 11 и 12 открыты всегда, т.к. их затворы подключены, соответственно, 1 и 4 - к источнику питания низкого уровня напряжения GND («0»), а 11 и 12 - к источнику питания высокого уровня напряжения VDD («1»). На затворы транзисторов N-типа 7 и 14 с входа IN поступает напряжение низкого уровня GND («О»), а на затворы транзисторов N-типа 8 и 13 с входа

- напряжение логической единицы «1*» (VCC). Транзисторы низкой проводимости Р-типа 1 и 4 и N-типа 11 и 12 открыты всегда, т.к. их затворы подключены, соответственно, 1 и 4 - к источнику питания низкого уровня напряжения GND («0»), а 11 и 12 - к источнику питания высокого уровня напряжения VDD («1»). На затворы транзисторов N-типа 7 и 14 с входа IN поступает напряжение низкого уровня GND («О»), а на затворы транзисторов N-типа 8 и 13 с входа  поступает напряжение логической единицы VCC («1*»). Поэтому транзисторы 7 и 14 закрыты, а транзисторы 8 и 13 открыты. Кроме того, в результате действия предыдущего регенеративного цикла транзисторы 2, 6 и 10 открыты, а транзисторы 3, 5, 7 и 9 закрыты. На входе первого инвертора установлено напряжение низкого уровня GND («0»), и, следовательно, на выходе

поступает напряжение логической единицы VCC («1*»). Поэтому транзисторы 7 и 14 закрыты, а транзисторы 8 и 13 открыты. Кроме того, в результате действия предыдущего регенеративного цикла транзисторы 2, 6 и 10 открыты, а транзисторы 3, 5, 7 и 9 закрыты. На входе первого инвертора установлено напряжение низкого уровня GND («0»), и, следовательно, на выходе  Преобразователя уровня напряжения - напряжение высокого уровня VDD («1»), а на входе второго инвертора - напряжение высокого уровня VDD («1»), и, следовательно, на выходе OUT Преобразователя уровня напряжения - напряжение низкого уровня GND («0»).

Преобразователя уровня напряжения - напряжение высокого уровня VDD («1»), а на входе второго инвертора - напряжение высокого уровня VDD («1»), и, следовательно, на выходе OUT Преобразователя уровня напряжения - напряжение низкого уровня GND («0»).

В режиме преобразования высокого напряжения логической единицы «1*» (VCC) в напряжение высокого уровня VDD на выходе OUT, а на выходе  напряжения низкого уровня GND, на вход IN, и следовательно, на затворы транзисторов N-типа 7 и 14, поступает напряжение логической единицы «1*» (VCC), а на вход

напряжения низкого уровня GND, на вход IN, и следовательно, на затворы транзисторов N-типа 7 и 14, поступает напряжение логической единицы «1*» (VCC), а на вход  , и, следовательно, на затворы транзисторов N-типа 8 и 13, - напряжение низкого уровня GND, в результате чего транзисторы 7 и 14 открываются, а транзисторы 8 и 13 - закрываются. Через открытые транзисторы 10 и 7, на затвор транзистора 5 и на вход второго инвертора поступает напряжение низкого уровня GND. Поэтому транзистор Р-типа 5 открывается, а на выходе второго инвертора формируется напряжение высокого уровня VDD. Одновременно через открытые транзисторы Р-типа 2 и 5 напряжение высокого уровня VDD поступает на затвор транзистора 6 и вход первого инвертора. Поэтому транзистор Р-типа 6 закрывается, а на выходе первого инвертора формируется напряжение низкого уровня GND. Напряжение высокого уровня VDD с выхода второго инвертора поступает на затворы транзисторов 2 и 9 и прямой выход OUT Преобразователя уровня напряжения. Поэтому транзистор Р-типа 2 закрывается, N-типа 9 открывается, а на прямом выходе OUT Преобразователя уровня напряжения устанавливается напряжение высокого уровня VDD. Одновременно, напряжение низкого уровня GND с выхода первого инвертора поступает на затворы транзисторов 3 и 10 и инверсный выход

, и, следовательно, на затворы транзисторов N-типа 8 и 13, - напряжение низкого уровня GND, в результате чего транзисторы 7 и 14 открываются, а транзисторы 8 и 13 - закрываются. Через открытые транзисторы 10 и 7, на затвор транзистора 5 и на вход второго инвертора поступает напряжение низкого уровня GND. Поэтому транзистор Р-типа 5 открывается, а на выходе второго инвертора формируется напряжение высокого уровня VDD. Одновременно через открытые транзисторы Р-типа 2 и 5 напряжение высокого уровня VDD поступает на затвор транзистора 6 и вход первого инвертора. Поэтому транзистор Р-типа 6 закрывается, а на выходе первого инвертора формируется напряжение низкого уровня GND. Напряжение высокого уровня VDD с выхода второго инвертора поступает на затворы транзисторов 2 и 9 и прямой выход OUT Преобразователя уровня напряжения. Поэтому транзистор Р-типа 2 закрывается, N-типа 9 открывается, а на прямом выходе OUT Преобразователя уровня напряжения устанавливается напряжение высокого уровня VDD. Одновременно, напряжение низкого уровня GND с выхода первого инвертора поступает на затворы транзисторов 3 и 10 и инверсный выход  Преобразователя уровня напряжения. Поэтому транзистор Р-типа 3 закрывается, N-типа 10 открывается, а на инверсном выходе

Преобразователя уровня напряжения. Поэтому транзистор Р-типа 3 закрывается, N-типа 10 открывается, а на инверсном выходе  Преобразователя уровня напряжения устанавливается напряжение низкого уровня GND. Таким образом, в парах цепочек транзисторов высокой проводимости Р-типа 2 и 5, 3 и 6, и N-типа 7 и 10, 8 и 9, один из транзисторов (в данном режиме 2, 6, 8 и 10) закрыт, и на инверсном выходе

Преобразователя уровня напряжения устанавливается напряжение низкого уровня GND. Таким образом, в парах цепочек транзисторов высокой проводимости Р-типа 2 и 5, 3 и 6, и N-типа 7 и 10, 8 и 9, один из транзисторов (в данном режиме 2, 6, 8 и 10) закрыт, и на инверсном выходе  Преобразователя уровня напряжения установлено напряжение низкого уровня GND («0»), а на прямом выходе OUT Преобразователя уровня напряжения - напряжение высокого уровня VDD («1»), полученное преобразованием входного высокого напряжения логической единицы «1*» (VCC). В то же время на входе Первого инвертора по цепи низкой проводимости, образованной транзисторами Р-типа 1 и 5, удерживается напряжение высокого уровня VDD («1»), а на входе Второго инвертора по цепи низкой проводимости, образованной транзисторами N-Типа 12 и 14, - напряжение низкого уровня GND («0»).

Преобразователя уровня напряжения установлено напряжение низкого уровня GND («0»), а на прямом выходе OUT Преобразователя уровня напряжения - напряжение высокого уровня VDD («1»), полученное преобразованием входного высокого напряжения логической единицы «1*» (VCC). В то же время на входе Первого инвертора по цепи низкой проводимости, образованной транзисторами Р-типа 1 и 5, удерживается напряжение высокого уровня VDD («1»), а на входе Второго инвертора по цепи низкой проводимости, образованной транзисторами N-Типа 12 и 14, - напряжение низкого уровня GND («0»).

При переходе Преобразователя уровня напряжения в исходное состояние и режим формирования на выходе OUT напряжения низкого уровня GND, а на выходе  напряжения высокого уровня VDD, на вход IN, и следовательно, на затворы транзисторов N-типа 7 и 14, поступает напряжение низкого уровня GND, а на вход

напряжения высокого уровня VDD, на вход IN, и следовательно, на затворы транзисторов N-типа 7 и 14, поступает напряжение низкого уровня GND, а на вход  , и, следовательно, на затворы транзисторов N-типа 8 и 13, - напряжение логической единицы «1*» (VCC), в результате чего транзисторы 7 и 14 закрываются, а транзисторы 8 и 13 - открываются. Через открытые транзисторы 8 и 9, на затвор транзистора 6 и на вход Первого инвертора поступает напряжение низкого уровня GND. Поэтому на выходе Первого инвертора формируется напряжение высокого уровня VDD («1») и транзистор Р-типа 6 открывается. Одновременно через открытые транзисторы Р-типа 3 и 6 напряжение высокого уровня VDD поступает на затвор транзистора 5 и вход Второго инвертора. Поэтому на выходе Второго инвертора формируется напряжение низкого уровня GND («0»), а транзистор Р-типа 5 закрывается. Напряжение низкого уровня GND с выхода Второго инвертора поступает на затворы транзисторов 2 и 9 и прямой выход OUT Преобразователя уровня напряжения. Поэтому транзистор Р-типа 2 открывается, N-типа 9 закрывается, а на прямом выходе OUT Преобразователя уровня напряжения устанавливается напряжение низкого уровня GND («0»). Одновременно, напряжение высокого уровня VDD с выхода Первого инвертора поступает на затворы транзисторов 3 и 10 и инверсный выход

, и, следовательно, на затворы транзисторов N-типа 8 и 13, - напряжение логической единицы «1*» (VCC), в результате чего транзисторы 7 и 14 закрываются, а транзисторы 8 и 13 - открываются. Через открытые транзисторы 8 и 9, на затвор транзистора 6 и на вход Первого инвертора поступает напряжение низкого уровня GND. Поэтому на выходе Первого инвертора формируется напряжение высокого уровня VDD («1») и транзистор Р-типа 6 открывается. Одновременно через открытые транзисторы Р-типа 3 и 6 напряжение высокого уровня VDD поступает на затвор транзистора 5 и вход Второго инвертора. Поэтому на выходе Второго инвертора формируется напряжение низкого уровня GND («0»), а транзистор Р-типа 5 закрывается. Напряжение низкого уровня GND с выхода Второго инвертора поступает на затворы транзисторов 2 и 9 и прямой выход OUT Преобразователя уровня напряжения. Поэтому транзистор Р-типа 2 открывается, N-типа 9 закрывается, а на прямом выходе OUT Преобразователя уровня напряжения устанавливается напряжение низкого уровня GND («0»). Одновременно, напряжение высокого уровня VDD с выхода Первого инвертора поступает на затворы транзисторов 3 и 10 и инверсный выход  Преобразователя уровня напряжения. Поэтому транзистор Р-типа 3 открывается, N-типа 10 закрывается, а на инверсном выходе

Преобразователя уровня напряжения. Поэтому транзистор Р-типа 3 открывается, N-типа 10 закрывается, а на инверсном выходе  Преобразователя уровня напряжения устанавливается напряжение высокого уровня VDD («1»). Таким образом, в парах цепочек транзисторов высокой проводимости Р-типа 2 и 5, 3 и 6, и N-типа седьмого 7 и 10, 8 и 9, один из транзисторов (в данном режиме 3, 5, 7 и 9) закрыт, и на инверсном выходе

Преобразователя уровня напряжения устанавливается напряжение высокого уровня VDD («1»). Таким образом, в парах цепочек транзисторов высокой проводимости Р-типа 2 и 5, 3 и 6, и N-типа седьмого 7 и 10, 8 и 9, один из транзисторов (в данном режиме 3, 5, 7 и 9) закрыт, и на инверсном выходе  Преобразователя уровня напряжения установлено напряжение высокого уровня VDD («1»), полученное преобразованием входного высокого напряжения логической единицы «1*» (VCC), а на прямом выходе OUT Преобразователя уровня напряжения - напряжение низкого уровня GND («0»). Схема Преобразователя уровня напряжения возвращается в исходное состояние. При этом на входе Первого инвертора по цепи низкой проводимости, образованной транзисторами N-типа 11 и 13, удерживается напряжение низкого уровня GND («0»), а на входе Второго инвертора по цепи низкой проводимости, образованной транзисторами Р-Типа 4 и 6, - напряжение высокого уровня VDD («1»),

Преобразователя уровня напряжения установлено напряжение высокого уровня VDD («1»), полученное преобразованием входного высокого напряжения логической единицы «1*» (VCC), а на прямом выходе OUT Преобразователя уровня напряжения - напряжение низкого уровня GND («0»). Схема Преобразователя уровня напряжения возвращается в исходное состояние. При этом на входе Первого инвертора по цепи низкой проводимости, образованной транзисторами N-типа 11 и 13, удерживается напряжение низкого уровня GND («0»), а на входе Второго инвертора по цепи низкой проводимости, образованной транзисторами Р-Типа 4 и 6, - напряжение высокого уровня VDD («1»),

Таким образом, в предлагаемом Преобразователе уровня напряжения исключено протекание тока во время переходных процессов одновременно по цепочкам высокой проводимости Р- и N-типа. Поэтому формирование выходных сигналов высокого уровня VDD («1») на выходах прямом OUT или инверсном  проходит в переходном процессе противостояния тока, протекающего через цепи транзисторов высокой проводимости с цепями транзисторов низкой проводимости, что существенно ускоряет время этих переходных процессов по перезаряду выходных емкостей триггера, и, тем самым, повышает общее быстродействие работы схемы.

проходит в переходном процессе противостояния тока, протекающего через цепи транзисторов высокой проводимости с цепями транзисторов низкой проводимости, что существенно ускоряет время этих переходных процессов по перезаряду выходных емкостей триггера, и, тем самым, повышает общее быстродействие работы схемы.

Литература

1. Патент на изобретение №2604054, «Преобразователь уровня напряжения», / В.В. Шубин // Бюллетень №34 от 10.12.2016.

| название | год | авторы | номер документа |

|---|---|---|---|

| ПРЕОБРАЗОВАТЕЛЬ УРОВНЯ НАПРЯЖЕНИЯ | 2020 |

|

RU2739487C1 |

| ПРЕОБРАЗОВАТЕЛЬ УРОВНЯ НАПРЯЖЕНИЯ | 2017 |

|

RU2667798C1 |

| ПРЕОБРАЗОВАТЕЛЬ УРОВНЯ НАПРЯЖЕНИЯ | 2021 |

|

RU2756445C1 |

| ПРЕОБРАЗОВАТЕЛЬ УРОВНЯ НАПРЯЖЕНИЯ | 2016 |

|

RU2604054C1 |

| ПРЕОБРАЗОВАТЕЛЬ ЛОГИЧЕСКОГО УРОВНЯ НАПРЯЖЕНИЯ | 2016 |

|

RU2642416C1 |

| ПРЕОБРАЗОВАТЕЛЬ УРОВНЯ НАПРЯЖЕНИЯ | 2016 |

|

RU2632567C1 |

| ЭЛЕМЕНТ ВХОДНОГО РЕГИСТРА | 2022 |

|

RU2787930C1 |

| ЭЛЕМЕНТ ВХОДНОГО РЕГИСТРА | 2021 |

|

RU2771447C1 |

| ВЫСОКОВОЛЬТНЫЙ ПРЕОБРАЗОВАТЕЛЬ УРОВНЯ НАПРЯЖЕНИЯ | 2019 |

|

RU2702979C1 |

| КМОП ЛОГИЧЕСКИЙ ВЕНТИЛЬ ИСКЛЮЧАЮЩЕЕ-ИЛИ | 2023 |

|

RU2814896C1 |

Изобретение относится к вычислительной технике и может быть использовано для построения быстродействующих преобразователей уровня напряжения, в том числе при сопряжении элементов электронных систем с несколькими источниками питания. Технический результат заключается в том, что предложенный преобразователь уровня напряжения имеет более высокое быстродействие преобразования напряжения высокого уровня и возврата к низкому уровню напряжения. Схема Преобразователя уровня напряжения содержит: шесть полевых транзисторов Р-типа (1-6) и восемь N-типа (7-14), два инвертора, входы прямого IN и инверсного  входных сигналов, вывод питания высокого уровня напряжения VDD, вывод питания низкого уровня напряжения (GND) и выходы прямой OUT и инверсный

входных сигналов, вывод питания высокого уровня напряжения VDD, вывод питания низкого уровня напряжения (GND) и выходы прямой OUT и инверсный  . 1 ил.

. 1 ил.

Преобразователь уровня напряжения, содержащий полевые транзисторы Р-типа с первого по шестой и N-типа - с седьмого по десятый, входы прямого IN и инверсного  входных сигналов, соединенные с затворами, соответственно, седьмого и восьмого транзисторов, стоки которых соединены, соответственно, седьмого - со стоком шестого и затвором пятого транзисторов, а восьмого - со стоком пятого и затвором шестого транзисторов, и истоки транзисторов пятого и шестого соединены, пятого - со стоками транзисторов первого и второго, а шестого - со стоками третьего и четвертого, вывод питания высокого уровня напряжения VDD, соединенный с истоками транзисторов с первого по четвертый, вывод питания низкого уровня напряжения GND, соединенный с истоками транзисторов девятого и десятого и затворами транзисторов первого и четвертого, прямой выход OUT, соединенный с затвором второго транзистора, и инверсный выход

входных сигналов, соединенные с затворами, соответственно, седьмого и восьмого транзисторов, стоки которых соединены, соответственно, седьмого - со стоком шестого и затвором пятого транзисторов, а восьмого - со стоком пятого и затвором шестого транзисторов, и истоки транзисторов пятого и шестого соединены, пятого - со стоками транзисторов первого и второго, а шестого - со стоками третьего и четвертого, вывод питания высокого уровня напряжения VDD, соединенный с истоками транзисторов с первого по четвертый, вывод питания низкого уровня напряжения GND, соединенный с истоками транзисторов девятого и десятого и затворами транзисторов первого и четвертого, прямой выход OUT, соединенный с затвором второго транзистора, и инверсный выход  , соединенный с затвором третьего транзистора, отличающийся тем, что в него введены полевые транзисторы N-типа с одиннадцатого по четырнадцатый и Первый и Второй инверторы, входы которых соединены, соответственно, Первого инвертора - со стоками пятого, восьмого и одиннадцатого транзисторов, и Второго – со стоками шестого, седьмого и двенадцатого транзисторов, а выходы, соответственно, Первого инвертора - с инверсным выходом OUT и затвором десятого транзистора, сток которого соединен с истоком седьмого, и Второго инвертора - с прямым выходом

, соединенный с затвором третьего транзистора, отличающийся тем, что в него введены полевые транзисторы N-типа с одиннадцатого по четырнадцатый и Первый и Второй инверторы, входы которых соединены, соответственно, Первого инвертора - со стоками пятого, восьмого и одиннадцатого транзисторов, и Второго – со стоками шестого, седьмого и двенадцатого транзисторов, а выходы, соответственно, Первого инвертора - с инверсным выходом OUT и затвором десятого транзистора, сток которого соединен с истоком седьмого, и Второго инвертора - с прямым выходом  и затвором девятого транзистора, сток которого соединен с истоком восьмого, причем затворы одиннадцатого и двенадцатого транзисторов соединены с выводом питания высокого уровня напряжения VDD, а истоки, соответственно, со стоками тринадцатого и четырнадцатого транзисторов, истоки которых соединены с выводом питания низкого уровня напряжения GND, а затворы, соответственно, с входами прямого IN и инверсного

и затвором девятого транзистора, сток которого соединен с истоком восьмого, причем затворы одиннадцатого и двенадцатого транзисторов соединены с выводом питания высокого уровня напряжения VDD, а истоки, соответственно, со стоками тринадцатого и четырнадцатого транзисторов, истоки которых соединены с выводом питания низкого уровня напряжения GND, а затворы, соответственно, с входами прямого IN и инверсного  входных сигналов.

входных сигналов.

| ПРЕОБРАЗОВАТЕЛЬ УРОВНЯ НАПРЯЖЕНИЯ | 2016 |

|

RU2604054C1 |

| WO 2016057088, 14.04.2016 | |||

| US 2006220682, 05.10.2006 | |||

| US 4616189, 07.10.1986. | |||

Авторы

Даты

2019-02-06—Публикация

2018-04-09—Подача