Предлагаемое изобретение относится к вычислительной технике и может быть использовано при построении многоразрядных быстродействующих сумматоров и АЛУ.

Известен одноразрядный сумматор [а.с. №1034031, СССР, G06F 7/50], названный автором как «Одноразрядный двоичный сумматор на комплементарных МДП-транзисторах».

Недостатком известного одноразрядного сумматора является низкое быстродействие формирования сигнала переноса. В указанном одноразрядном сумматоре повышена длительность фронта и спада сигнала на выходе 5  , который является инверсным выходом сигнала переноса, за счет подключения дополнительной паразитной емкости в виде емкости затворов транзисторов 26 и 29. Поэтому появление сигнала переноса на выходе имеет дополнительную задержку, пропорциональную величине вклада дополнительной емкости в общую емкость узла выхода 5

, который является инверсным выходом сигнала переноса, за счет подключения дополнительной паразитной емкости в виде емкости затворов транзисторов 26 и 29. Поэтому появление сигнала переноса на выходе имеет дополнительную задержку, пропорциональную величине вклада дополнительной емкости в общую емкость узла выхода 5  .

.

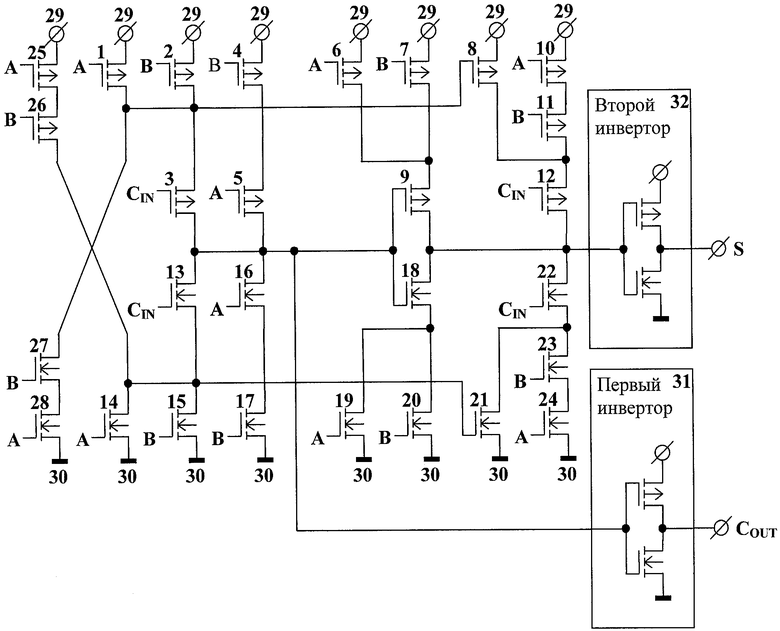

Кроме того, известен одноразрядный сумматор [IEEE JOURNAL OF SOLID-STATE CIRCUITS, VOL. 32, NO.7, JULY 1997, p.1085, Fig.4(p)], являющийся прототипом предлагаемого изобретения и содержащий полевые транзисторы первый, второй…, двенадцатый - первого типа проводимости, тринадцатый, четырнадцатый…, двадцать четвертый - второго типа проводимости, вход слагаемого А, соединенный с затворами первого, пятого, шестого, десятого, четырнадцатого, шестнадцатого, девятнадцатого и двадцать четвертого транзисторов, вход слагаемого В, соединенный с затворами второго, четвертого, седьмого, одиннадцатого, пятнадцатого, семнадцатого, двадцатого и двадцать третьего транзисторов, вход переноса CIN, соединенный с затворами третьего, восьмого, двенадцатого, тринадцатого, двадцать первого и двадцать второго транзисторов, вывод питания первого уровня напряжения, соединенный с истоками первого, второго, четвертого, шестого, седьмого, восьмого и десятого транзисторов, вывод питания второго уровня напряжения, соединенный с истоками четырнадцатого, пятнадцатого, семнадцатого, девятнадцатого, двадцатого, двадцать первого и двадцать четвертого транзисторов, причем стоки первого и второго транзисторов соединены с истоком третьего транзистора, сток четвертого - с истоком пятого, стоки шестого, седьмого и восьмого транзисторов - с истоком девятого, сток десятого - с истоком одиннадцатого, сток одиннадцатого - с истоком двенадцатого, стоки четырнадцатого и пятнадцатого - с истоком тринадцатого, сток семнадцатого - с истоком шестнадцатого, стоки девятнадцатого, двадцатого и двадцать первого транзисторов - с истоком восемнадцатого, сток двадцатого четвертого транзистора - с истоком двадцать третьего, сток двадцать третьего - с истоком двадцать второго, стоки третьего, пятого, тринадцатого и шестнадцатого транзисторов - с затворами девятого и восемнадцатого транзисторов и входом первого инвертора, выход которого является выходом сигнала переноса COUT, а стоки девятого, двенадцатого, восемнадцатого и двадцать второго - с входом второго инвертора, выход которого является выходом результата сложения S.

Недостатком известного одноразрядного сумматора является низкое быстродействие формирования сигнала переноса. В указанном сумматоре вход переноса CIN соединен с затворами трех комплементарных пар транзисторов - третьего-тринадцатого, восьмого-двадцать первого и двенадцатого-двадцать второго транзисторов, которые вносят основной вклад в величину паразитной входной емкости по этому входу. Так как входная емкость является емкостной нагрузкой для сигнала переноса CIN, то ее величина оказывает непосредственное влияние на длительность переключения транзисторов, подсоединенных к входу переноса CIN, и эта длительность, при прочих равных условиях, прямо пропорциональна значению этой емкости и, следовательно, значению времени формирования входного и, соответственно, выходного сигнала первого инвертора. Таким образом, повышенная величина значения паразитной входной емкости приводит к увеличению задержки формирования сигнала переноса на выходе COUT.

Задачей предлагаемого изобретения является повышение быстродействия формирования сигнала переноса на выходе COUT.

Поставленная задача достигается тем, что в сумматор, содержащий полевые транзисторы первый, второй…, двенадцатый - первого типа проводимости, тринадцатый, четырнадцатый…, двадцать четвертый - второго типа проводимости, вход слагаемого А, соединенный с затворами первого, пятого, шестого, десятого, четырнадцатого, шестнадцатого, девятнадцатого и двадцать четвертого транзисторов, вход слагаемого В, соединенный с затворами второго, четвертого, седьмого, одиннадцатого, пятнадцатого, семнадцатого, двадцатого и двадцать третьего транзисторов, вход переноса CIN, соединенный с затворами третьего, двенадцатого, тринадцатого и двадцать второго транзисторов, вывод питания первого уровня напряжения, соединенный с истоками первого, второго, четвертого, шестого, седьмого, восьмого и десятого транзисторов, вывод питания второго уровня напряжения, соединенный с истоками четырнадцатого, пятнадцатого, семнадцатого, девятнадцатого, двадцатого, двадцать первого и двадцать четвертого транзисторов, причем стоки первого и второго транзисторов соединены с истоком третьего транзистора, сток четвертого - с истоком пятого, стоки шестого и седьмого - с истоком девятого, сток десятого - с истоком одиннадцатого, сток одиннадцатого - с истоком двенадцатого, стоки четырнадцатого и пятнадцатого - с истоком тринадцатого, сток семнадцатого - с истоком шестнадцатого, стоки девятнадцатого и двадцатого - с истоком восемнадцатого, сток двадцать четвертого - с истоком двадцать третьего и сток двадцать третьего - с истоком двадцать второго, и стоки третьего, пятого, тринадцатого и шестнадцатого - с затворами девятого и восемнадцатого транзисторов и входом первого инвертора, выход которого является выходом сигнала переноса COUT, а стоки девятого, двенадцатого, восемнадцатого и двадцать второго транзисторов - с входом второго инвертора, выход которого является выходом результата сложения S, введены транзисторы двадцать пятый и двадцать шестой - первого типа проводимости и двадцать седьмой и двадцать восьмой - второго типа проводимости, затворы которых соединены с входами слагаемых, двадцать пятого и двадцать восьмого - с входом А и двадцать шестого и двадцать седьмого - с входом В, истоки соединены, соответственно, двадцать пятого - с выводом питания первого уровня напряжения, двадцать восьмого - с выводом питания второго уровня напряжения, двадцать шестого - со стоком двадцать пятого и двадцать седьмого - со стоком двадцать восьмого и стоки двадцать шестого и двадцать седьмого транзисторов соединены, соответственно, двадцать шестого - со стоками четырнадцатого и пятнадцатого, истоком тринадцатого и затвором двадцать первого транзисторов, а двадцать седьмого - со стоками первого и второго, истоком третьего и затвором восьмого транзисторов.

Таким образом, в предлагаемом одноразрядном сумматоре к входу CIN подключено две комплементарные пары транзисторов - третий-тринадцатый и двенадцатый- двадцать второй транзисторы, вместо трех пар у прототипа, что позволяет повысить быстродействие формирования сигнала переноса на выходе COUT.

Предлагаемый одноразрядный сумматор содержит: полевые транзисторы первый 1, второй 2…, двенадцатый 12, двадцать пятый 25, двадцать шестой 26 - первого типа проводимости, тринадцатый 13, четырнадцатый 14…, двадцать четвертый 24, двадцать седьмой 27, двадцать восьмой 28 - второго типа проводимости, вход слагаемого А, соединенный с затворами первого 1, пятого 5, шестого 6, десятого 10, четырнадцатого 14, шестнадцатого 16, девятнадцатого 19, двадцать четвертого 24, двадцать пятого 25 и двадцать восьмого 28 транзисторов, вход слагаемого В, соединенный с затворами второго 2, четвертого 4, седьмого 7, одиннадцатого 11, пятнадцатого 15, семнадцатого 17, двадцатого 20, двадцать третьего 23, двадцать шестого 26 и двадцать седьмого 27 транзисторов, вход переноса CIN, соединенный с затворами третьего 3, двенадцатого 12, тринадцатого 13 и двадцать второго 22 транзисторов, вывод питания первого уровня напряжения 29, соединенный с истоками первого 1, второго 2, четвертого 4, шестого 6, седьмого 7, восьмого 8 и десятого 10 и двадцать девятого 29 транзисторов, вывод питания второго уровня напряжения 30, соединенный с истоками четырнадцатого 14, пятнадцатого 15, семнадцатого 17, девятнадцатого 19, двадцатого 20, двадцать первого 21, двадцать четвертого 24 и двадцать пятого 25 транзисторов, причем стоки первого 1 и второго 2, транзисторов соединены с истоками третьего 3 и двадцать седьмого 27 и затвором восьмого 8 транзисторов, сток четвертого 4 - с истоком пятого 5, стоки шестого 6 и седьмого 7 - с истоком девятого 9, сток десятого 10 - с истоком одиннадцатого 11, сток одиннадцатого 11 - с истоком двенадцатого 12, стоки четырнадцатого 14 и пятнадцатого 15 - с истоками тринадцатого 13 и двадцать шестого 26 и затвором двадцать первого 21 транзисторов, сток семнадцатого 17 - с истоком шестнадцатого 16, стоки девятнадцатого 19 и двадцатого 20 - с истоком восемнадцатого 18, сток двадцать четвертого 24 - с истоком двадцать третьего 23, сток двадцать третьего 23 - с истоком двадцать второго 22, сток двадцать пятого 25 - с истоком двадцать шестого 26, сток двадцать восьмого 28 - с истоком двадцать седьмого 27, и стоки третьего 3, пятого 5, тринадцатого 13 и шестнадцатого 16 - с затворами девятого 9 и восемнадцатого 18 транзисторов и входом первого инвертора 31, выход которого является выходом сигнала переноса COUT, а стоки девятого 9, двенадцатого 12, восемнадцатого 18 и двадцать второго 22 транзисторов - с входом второго инвертора 32, выход которого является выходом результата сложения S.

Допускается произвольное выполнение логических элементов первого и второго инверторов, реализующих функцию инверсии.

Предлагаемый одноразрядный сумматор представляет собой логическую схему комбинационного типа и работает следующим образом.

На входы слагаемых А и В поступают значения сигналов, требующих сложения, а на вход переноса CIN - значение сигнала переноса.

В результате действия поступающих сигналов на выходах одноразрядного сумматора COUT и S должны появиться значения сигналов, соответствующих нижеприведенной таблице истинности.

В комбинациях №№1-4 на вход переноса CIN и на затворы подключенных к нему транзисторов 3, 12, 13 и 22 поступает напряжение низкого уровня, которое соответствует значению «0» таблицы истинности сумматора. При этом транзисторы P-типа 3 и 12 - открываются, а N-типа 13 и 22 - закрывается.

Если при этом на входы слагаемых А и В поступает напряжение низкого уровня, то транзисторы P-типа 1, 2, 4-7, 10, 11, 25 и 26, подключенные своими затворами к этим входам, - открываются, а N-типа 14-17,19, 20, 23, 24, 27 и 28 - закрываются. Через открытые транзисторы 1-5, 25 и 26 с вывода питания высокого уровня напряжения 29 на затворы транзисторов 8, 9, 18 и 21 и на вход первого инвертора 31 поступает напряжение высокого уровня, которое соответствует значению «1» таблицы истинности сумматора, и поэтому транзисторы P-типа 8 и 9 закрываются, а транзисторы N-типа 18 и 21 - открываются. Так как на входе первого инвертора 31 напряжение высокого уровня - «1», то после инверсии на его выходе COUT формируется напряжение низкого уровня - «0». Одновременно с вывода питания высокого уровня напряжения 29 через открытые транзисторы 10, 11 и 12 на вход второго инвертора 32 поступает напряжение высокого уровня - «1». Поэтому на выходе S этого инвертора формируется инверсное относительно входного напряжение низкого уровня - «0». При этом входы первого 31 и второго 32 инверторов остаются изолированными от напряжения низкого уровня закрытыми транзисторами N-типа 13-17,19, 20 и 22-24. Таким образом, реализуется комбинация №1 таблицы истинности сумматора.

Если же на вход слагаемого А(В) поступает напряжение низкого уровня - «0», а на вход слагаемого В(А) высокого - «1», то транзисторы P-типа 1(2), 5(4), 6(7), 10(11), 25(26) и N-типа 15(14), 17(16), 20(19), 23(24), 27(28), подключенные своими затворами к этим входам, - открываются, а P-типа 2(1), 4(5), 7(6), 11(10), 26(25) и N-типа 14(15), 16(17), 19(20), 24(23), 28(27) - закрываются. Через открытые транзисторы 1(2), 3 с вывода питания высокого уровня напряжения 29 на затворы транзисторов 8, 9, 18 и на вход первого инвертора 31 поступает напряжение высокого уровня - «1» и поэтому транзисторы N-типа 8, 9 закрываются, а транзистор N-типа 18 - открывается. Так как на входе первого инвертора 31 напряжение высокого уровня - «1», то после инверсии на его выходе COUT формируется напряжение низкого уровня - «0». Одновременно с вывода питания низкого уровня напряжения 30 через открытые транзисторы 20(19) и 18 на вход второго инвертора 32 поступает напряжение низкого уровня - «0». Поэтому на выходе S этого инвертора формируется инверсное относительно входного напряжение высокого уровня - «1». При этом вход первого инвертора 31 остается изолированным от напряжения низкого уровня закрытыми транзисторами N-типа 13 и 16(17), а вход второго 32 - от напряжения высокого уровня закрытыми транзисторами P-типа 8, 9 и 11(10). Таким образом, реализуется комбинация №2(№3) таблицы истинности сумматора.

В случае, когда на входы А и В поступает напряжение высокого уровня - «1», транзисторы P-типа 1, 2, 4-7, 10, 11, 25 и 26, подключенные своими затворами к этим входам, - закрываются, а N-типа 14-17, 19, 20, 23, 24, 27 и 28 - открываются. Через открытые транзисторы 14-17, 27 и 28 с вывода питания низкого уровня напряжения 30 на затворы транзисторов 8, 9,18 и 21 и на вход первого инвертора 31 поступает напряжение низкого уровня - «0» и поэтому транзисторы P-типа 8 и 9 открываются, а N-типа 18 и 21 - закрываются. Так как на входе первого инвертора 31 напряжение низкого уровня - «0», то после инверсии на его выходе СOUT формируется напряжение высокого уровня - «1». Одновременно с вывода питания высокого уровня напряжения 29 через открытые транзисторы P-типа 8 и 12 на вход второго инвертора 32 поступает напряжение высокого уровня - «1». Поэтому на выходе S этого инвертора формируется инверсное относительно входного напряжение низкого уровня - «0». При этом вход первого инвертора 31 остается изолированным от напряжения высокого уровня закрытыми транзисторами P-типа 1, 2, 4, 5 и второго инвертора 32 - от напряжения низкого уровня закрытыми транзисторами N-типа 18, 21 и 22. Таким образом, реализуется комбинация №4 таблицы истинности сумматора.

В комбинациях №№5-8 на вход переноса CIN и на затворы подключенных к нему транзисторов 3, 12, 13 и 22 поступает напряжение высокого уровня - «1». Поэтому транзисторы P-типа 3 и 12 - закрываются, а N-типа 13 и 22 - открывается.

Если при этом на входы слагаемых А и В поступает напряжение низкого уровня, то транзисторы P-типа 1, 2, 4-7, 10, 11, 25 и 26, подключенные своими затворами к этим входам, - открываются, а N-типа 14-17, 19, 20, 23, 24, 27 и 28 - закрываются. Через открытые транзисторы 1, 2, 4, 5, 25, 26 с вывода питания высокого уровня напряжения 29 на затворы транзисторов 8, 9, 18, 21 и на вход первого инвертора 31 поступает напряжение высокого уровня - «1» и поэтому транзисторы P-типа 8 и 9 закрываются, а N-типа 18 и 21 - открываются. Так как на входе первого инвертора 31 напряжение высокого уровня - «1», то после инверсии на его выходе COUT формируется напряжение низкого уровня - «0». Одновременно с вывода питания низкого уровня напряжения 30 через открытые транзисторы N-типа 21, 22 на вход второго инвертора 32 поступает напряжение низкого уровня - «0». Поэтому на выходе S этого инвертора формируется инверсное относительно входного напряжение высокого уровня - «1». При этом вход первого инвертора 31 остается изолированным от напряжения низкого уровня закрытыми транзисторами N-типа 14-17 и второго 32 - от напряжения высокого уровня закрытыми транзисторами N-типа 9, 12. Таким образом, реализуется комбинация №5 таблицы истинности сумматора.

Если же на вход слагаемого А(В) поступает напряжение низкого уровня - «0», а на вход слагаемого В(А) высокого - «1», то транзисторы P-типа 1(2), 5(4), 6(7), 10(11), 25(26) и N-типа 15(14), 17(16), 20(19), 23(24), 27(28), подключенные своими затворами к этим входам, - открываются, а P-типа 2(1), 4(5), 7(6), 11(10), 26(25) и N-типа 14(15), 16(17), 19(20), 24(23), 28(27) - закрываются. Через открытые транзисторы 13, 15(14) с вывода питания низкого уровня напряжения 30 на затворы транзисторов 9, 18, 21 и на вход первого инвертора 31 поступает напряжение низкого уровня - «0» и поэтому транзисторы N-типа 18 и 21 закрываются, а транзистор P-типа 9 - открывается. Так как на входе первого инвертора 31 напряжение низкого уровня - «0», то после инверсии на его выходе COUT формируется напряжение высокого уровня - «1». Одновременно с вывода питания высокого уровня напряжения 29 через открытые транзисторы P-типа 6(7) и 9 на вход второго инвертора 32 поступает напряжение высокого уровня - «1». Поэтому на выходе S этого инвертора формируется инверсное относительно входного напряжение низкого уровня - «0». При этом вход первого инвертора 31 остается изолированным от напряжения высокого уровня закрытыми транзисторами P-типа 3 и 4(5), а вход второго 32 - от напряжения низкого уровня закрытыми транзисторами N-типа 18, 21 и 24(23). Таким образом, реализуется комбинация №6(№7) таблицы истинности сумматора.

В случае, когда на входы А и В поступает напряжение высокого уровня - «1», транзисторы P-типа 1, 2, 4-7, 10, 11, 25 и 26, подключенные своими затворами к этим входам, - закрываются, а N-типа 14-17, 19, 20, 23, 24, 27 и 28 - открываются. Через открытые транзисторы 13-17 с вывода питания низкого уровня напряжения 30 на затворы транзисторов 9, 18, 21 и на вход первого инвертора 31 поступает напряжение низкого уровня - «0» и поэтому транзистор P-типа 9 открывается, а транзисторы N-типа 18 и 21 - закрываются. Так как на входе первого инвертора 31 напряжение низкого уровня - «0», то после инверсии на его выходе COUT формируется напряжение высокого уровня - «1». Одновременно с вывода питания низкого уровня напряжения 30 через открытые транзисторы N-типа 22-24 на вход второго инвертора 32 поступает напряжение низкого уровня - «0». Поэтому на выходе S этого инвертора формируется инверсное относительно входного напряжение высокого уровня - «1». При этом входы первого 31 и второго 32 инверторов остаются изолированными от напряжения высокого уровня закрытыми транзисторами P-типа 1-7 и 10-12. Таким образом, реализуется комбинация №8 таблицы истинности сумматора.

В предлагаемой схеме одноразрядного сумматора исключено соединение затворов восьмого и двадцать первого транзисторов с входом переноса CIN, вследствие чего суммарная емкость входа переноса CIN уменьшена. Таким образом, при прочих равных условиях, длительность фронта и спада входного сигнала на входе переноса CIN уменьшена, благодаря чему ускорено переключение третьего и тринадцатого транзисторов и, следовательно, появление сигнала на входе первого инвертора. Так как сигнал на входе первого инвертора появляется быстрее, то инвертор, соответственно, переключается быстрее и сигнал на его выходе появляется быстрее тоже.

Таким образом, в предлагаемом одноразрядном сумматоре повышено быстродействие формирования сигнала переноса на выходе COUT.

| название | год | авторы | номер документа |

|---|---|---|---|

| ОДНОРАЗРЯДНЫЙ ДВОИЧНЫЙ СУММАТОР | 2009 |

|

RU2408922C1 |

| ОДНОРАЗРЯДНЫЙ СУММАТОР | 2011 |

|

RU2444050C1 |

| СУММАТОР | 2010 |

|

RU2435196C1 |

| СУММАТОР | 2008 |

|

RU2380739C1 |

| СУММАТОР | 2011 |

|

RU2455680C1 |

| ОДНОРАЗРЯДНЫЙ ДВОИЧНЫЙ СУММАТОР | 2011 |

|

RU2450324C1 |

| СУММАТОР | 2011 |

|

RU2469381C1 |

| ПОЛНЫЙ СУММАТОР | 2011 |

|

RU2475811C1 |

| ПРЕОБРАЗОВАТЕЛЬ УРОВНЯ НАПРЯЖЕНИЯ | 2017 |

|

RU2667798C1 |

| ПРЕОБРАЗОВАТЕЛЬ УРОВНЯ НАПРЯЖЕНИЯ | 2018 |

|

RU2679186C1 |

Изобретение относится к вычислительной технике и может быть использовано при построении многоразрядных быстродействующих сумматоров и АЛУ. Техническим результатом является повышение быстродействия формирования сигнала переноса за счет уменьшения емкостных нагрузок в цепи прохождения сигнала от входа переноса CIN до выхода результата сложения S. Устройство содержит 14 полевых транзисторов Р-типа проводимости, 14 полевых транзисторов N-типа проводимости, входы слагаемых А и В, вход переноса CIN, выводы питания высокого и низкого уровней напряжения, первый инвертор, выход которого является выходом сигнала переноса COUT, второй инвертор, выход которого является выходом результата сложения S. 1 ил., 1 табл.

Одноразрядный сумматор, содержащий с первого по двенадцатый полевые транзисторы Р-типа, с тринадцатого по двадцать четвертый полевые транзисторы N-типа, вход слагаемого А, соединенный с затворами первого, пятого, шестого, десятого, четырнадцатого, шестнадцатого, девятнадцатого и двадцать четвертого транзисторов, вход слагаемого В, соединенный с затворами второго, четвертого, седьмого, одиннадцатого, пятнадцатого, семнадцатого, двадцатого и двадцать третьего транзисторов, вход переноса CIN, соединенный с затворами третьего, двенадцатого, тринадцатого и двадцать второго транзисторов, вывод питания высокого уровня напряжения, соединенный с истоками первого, второго, четвертого, шестого, седьмого, восьмого и десятого транзисторов, вывод питания низкого уровня напряжения, соединенный с истоками четырнадцатого, пятнадцатого, семнадцатого, девятнадцатого, двадцатого, двадцать первого и двадцать четвертого транзисторов, причем стоки первого и второго транзисторов соединены с истоком третьего транзистора, сток четвертого - с истоком пятого, стоки шестого и седьмого - с истоком девятого, сток десятого - с истоком одиннадцатого, сток одиннадцатого - с истоком двенадцатого, стоки четырнадцатого и пятнадцатого - с истоком тринадцатого, сток семнадцатого - с истоком шестнадцатого, стоки девятнадцатого и двадцатого - с истоком восемнадцатого, сток двадцать четвертого - с истоком двадцать третьего и сток двадцать третьего - с истоком двадцать второго, и стоки третьего, пятого, тринадцатого и шестнадцатого - с затворами девятого и восемнадцатого транзисторов и входом первого инвертора, выход которого является выходом сигнала переноса COUT, а стоки девятого, двенадцатого, восемнадцатого и двадцать второго транзисторов - с входом второго инвертора, выход которого является выходом результата сложения S, отличающийся тем, что в него введены полевые транзисторы двадцать пятый и двадцать шестой - Р-типа и двадцать седьмой и двадцать восьмой - N-типа, затворы которых соединены с входами слагаемых, двадцать пятого и двадцать восьмого - с входом А и двадцать шестого и двадцать седьмого - с входом В, истоки соединены, соответственно, двадцать пятого - с выводом питания высокого уровня напряжения, двадцать восьмого - с выводом питания низкого уровня напряжения, двадцать шестого - со стоком двадцать пятого и двадцать седьмого - со стоком двадцать восьмого и стоки двадцать шестого и двадцать седьмого транзисторов соединены, соответственно, двадцать шестого - со стоками четырнадцатого и пятнадцатого, истоком тринадцатого и затвором двадцать первого транзисторов, двадцать первого - со стоком двадцать третьего и истоком двадцать второго, а двадцать седьмого - со стоками первого и второго, истоком третьего и затвором восьмого транзисторов и восьмого - со стоком одиннадцатого и истоком двенадцатого транзисторов.

| IEEE JOURNAL OF SOLID-STATE CIRCUITS, VOL.32, NO.7, JULY 1997, p.1085, fig | |||

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

| ОДНОРАЗРЯДНЫЙ СУММАТОР | 1996 |

|

RU2164036C2 |

| ОДНОРАЗРЯДНЫЙ СУММАТОР НА МОП ТРАНЗИСТОРАХ | 1996 |

|

RU2152641C1 |

| Одноразрядный двоичный сумматор на комплементарных МДП-транзисторах | 1982 |

|

SU1034031A1 |

| Пюпитр для работы на пишущих машинах | 1922 |

|

SU86A1 |

| DE 3630605 A1, 17.03.1988. | |||

Авторы

Даты

2010-12-27—Публикация

2009-03-23—Подача