Изобретение относится к вычислительной технике, в частности к устройствам на КМДП-транзисторах для арифметической и логической обработки цифровой информации.

Известен сумматор с выбором переноса, содержащий в каждом разряде первый и второй элементы И-НЕ, элемент ИЛИ-НЕ, два инвертора, по четыре МДП-транзистора р- и n-типа, первый логический узел, выполняющий функцию сложения двух сигналов по mod2, и второй логический узел, содержащий в четных разрядах, считая младший нулевым, элемент И-ИЛИ-НЕ, а в нечетных разрядах инвертор и элемент ИЛИ-И-НЕ, причем каждый разряд сумматора соединен с входом начального переноса сумматора, имеет первый и второй выходы управления и первый и второй входы управления, соединенные с соответствующими выходами управления соседнего младшего разряда сумматора [2]

В таком устройстве отсутствуют средства для формирования на его выходах результатов логических операций над входными данными, оно имеет невысокое быстродействие из-за возможного последовательного прохождения сигналов подготовки и генерации переноса через входы и выходы управления каждого разряда.

Известен многофункциональный сумматор, выполняющий логические функции и содержащий в каждом разряде два элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, четыре КМДП-коммутатора с двух направлений и один КМДП-коммутатор с трех направлений [1]

Такое устройство содержит большое число транзисторов и имеет невысокое быстродействие из-за возможного последовательного прохождения сигнала переноса через каждый его разряд.

Наиболее близким по технической сущности к изобретению является сумматор, выполняющий логические функции конъюнкции, дизъюнкции, равнозначности, констант "0" и единицы и содержащий в каждом разряде элемент И-НЕ, ИЛИ-НЕ, инвертор, два элемента ИСКЛЮЧАЮЩЕЕ ИЛИ и по четыре МДП-транзистора р- и n-типа с соответствующими связями [3]

Такое устройство не обладает высоким быстродействием из-за возможного последовательного прохождения сигнала переноса через каждый его разряд.

Сущность изобретения состоит в том, что в сумматор, каждый разряд которого содержит элемент И-НЕ, элемент ИЛИ-НЕ, первый и второй элементы ИСКЛЮЧАЮЩЕЕ ИЛИ, инвертор, первый, второй, третий и четвертый МДП-транзисторы р-типа и первый, второй, третий и четвертый МДП-транзисторы n-типа, причем в каждом разряде выход элемента И-НЕ соединен с затвором первого МДП-транзистора р-типа и первым входом первого элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, выход элемента ИЛИ-НЕ соединен с затвором первого МДП-транзистора n-типа и вторым входом первого элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, выход элемента ИЛИ-НЕ соединен с затвором первого МДП-транзистора n-типа и вторым входом первого элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, выход первого элемента ИСКЛЮЧАЮЩЕЕ ИЛИ соединен с первым входом второго элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, второй вход которого соединен с входом переноса данного разряда сумматора, а выход образует его выход суммы, стоки первых МДП-транзисторов n- и р-типа соединены со стоками вторых МДП-транзисторов n- и р-типа, исток первого МДП-транзистора n-типа соединен со стоком третьего МДП-транзистора n-типа, исток которого соединен с шиной нулевого потенциала сумматора, а затвор соединен с первым входом задания функции сумматора, исток третьего МДП- транзистора р-типа соединен со стоком четвертого МДП-транзистора р-типа, исток которого соединен с шиной питания сумматора, а затвор соединен с затвором четвертого МДП-транзистора n-типа и с входом управления данного разряда сумматора, первый и второй входы элементов И-НЕ, ИЛИ-НЕ данного разряда сумматора соединены с соответствующим разрядом входов первого и второго операндов сумматора, а их третьи входы соединены соответственно с вторым и третьим входами задания функции сумматора, в каждый разряд введены дополнительно пятый и шестой МДП-транзисторы р-типа и пятый, шестой и седьмой МДП-транзисторы n-типа, а также дополнительный вход переноса и дополнительный вход управления, причем вход инвертора соединен со стоками первых МДП-транзисторов n- и р-типа, а его выход образует выход переноса данного разряда сумматора, исток второго МДП-транзистора р-типа соединен со стоками третьего и пятого МДП-транзисторов р-типа, исток второго МДП-транзистора n-типа соединен со стоками пятого и шестого МДП-транзисторов n-типа, истоки первого, пятого и шестого МДП-транзисторов р-типа соединены с шиной питания сумматора, сток шестого МДП-транзистора р-типа соединен со входом инвертора, а его затвор соединен с первым входом задания функции сумматора, истоки четвертого и седьмого МДП-транзисторов n-типа соединены с шиной нулевого потенциала сумматора, а их стоки соединены соответственно с истоками пятого и шестого МДП-транзисторов n-типа, затвор пятого МДП-транзистора n-типа соединен с первым входом задания функции сумматора, затворы пятого МДП-транзистора р-типа и седьмого МДП-транзистора n-типа соединены с дополнительным входом управления данного разряда сумматора, затворы третьего МДП-транзистора р-типа и шестого МДП-транзистора n-типа соединены с дополнительным входом переноса данного разряда сумматора, затворы вторых МДП-транзисторов р- и n-типа образуют первый и второй выходы управления данного разряда сумматора и соединены соответственно с выходами элементов ИЛИ-НЕ и И-НЕ, выход переноса каждого разряда сумматора соединен со входом переноса соседнего старшего разряда сумматора и с дополнительным входом переноса следующего за ним разряда сумматора, первый и второй выходы управления каждого разряда сумматора соединены соответственно со входом управления и с дополнительным входом управления соседнего старшего разряда сумматора, дополнительные входы переноса младшей пары разрядов сумматора соединены со входом переноса самого младшего разряда сумматора и со входом начального переноса сумматора, вход управления самого младшего разряда сумматора соединен с шиной логического "0", а его дополнительный вход управления соединен с шиной логической "1".

Достигаемый технический эффект заключается в повышении быстродействия сумматора, выполняющего логические функции конъюнкции, дизъюнкции, равнозначности, констант "0" и единицы.

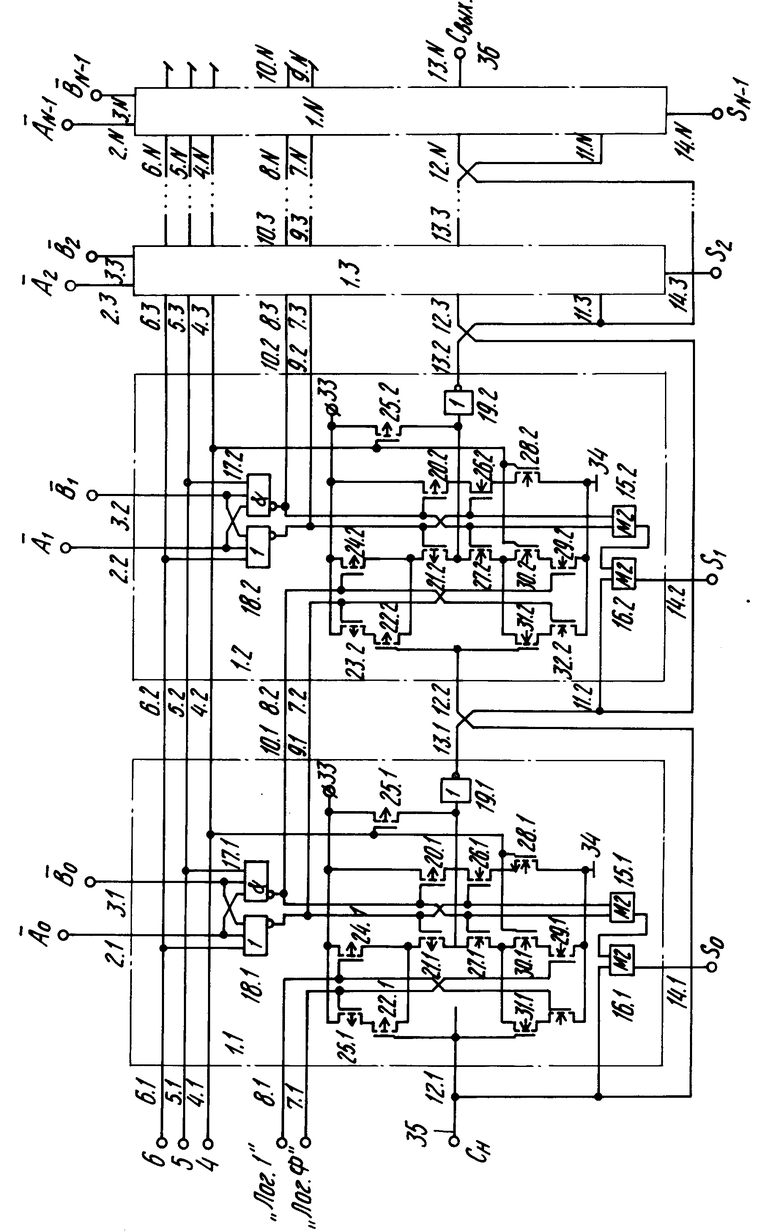

На чертеже представлена электрическая функциональная схема заявляемого устройства.

Здесь условно показаны младшие разряды заявляемого устройства, где каждый разряд 1 содержит входы 2 и 3 первого и второго операндов соответственно, первый 4, второй 5 и третий 6 входы задания функции, вход управления 7 и дополнительный вход управления 8, первый 9 и второй 10 выходы управления, вход переноса 11 и дополнительный вход переноса 12, выходы переноса 13 и суммы 14, первый 15 и второй 16 элементы ИСКЛЮЧАЮЩЕЕ ИЛИ, элементы И-НЕ 17 и ИЛИ-НЕ 18, инвертор 19, первый шестой МДП-транзисторы р-типа 20-25, первый седьмой МДП-транзисторы n-типа 26-32, шины 33 питания и 34 нулевого потенциала, причем входы переноса 11 и 12 самого младшего разряда устройства соединены с дополнительным входом переноса 12 следующего за ним разряда устройства и с входом 35 начального переноса устройства, выход переноса самого старшего разряда устройства образует выход 36 переноса устройства, вход управления самого младшего разряда устройства соединен с шиной логического "0", а его дополнительный вход управления соединен с шиной логической "1".

Обозначим прямые значения j-го разряда первого и второго входных операндов устройства как Аj и Bj соответственно, где j (0,1,N-1), N разрядность входных операндов; прямые значения сигналов переноса, поступающих на вход 11 переноса и дополнительный вход 12 переноса j-го разряда устройства как Сj и Cj-1 соответственно, прямое значение суммы, формируемое этим разрядом, как Sj, а прямые значения начального и выходного переносов устройства как Сн и Свых соответственно.

Будем считать, что уровень "логической 1" ("1") соответствует напряжению шины 33 питания устройства, а уровень "логического 0" ("0") соответствует напряжению шины 34 нулевого потенциала устройства.

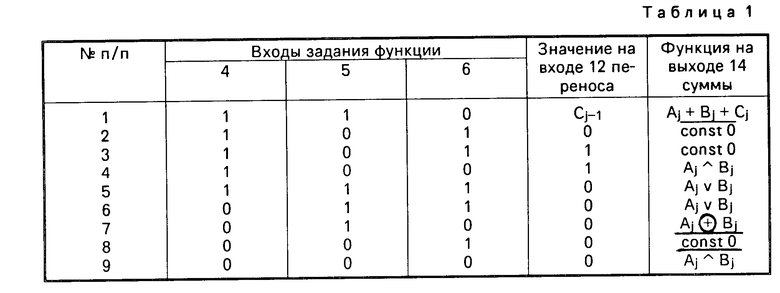

Набор функций, выполняемых сумматором, с соответствующими значениями сигналов на входах задания функции каждого из разрядов и на их дополнительных входах переноса представлен в табл.1.

Рассмотрим работу сумматора на примере одного разряда.

При подаче "1" на первый вход 4 задания функции третий 28 и пятый 30 МДП-транзисторы n-типа открыты, шестой 25 МДП-транзистор р-типа закрыт, и выполняемая разрядом сумматора функция определяется состоянием его входов 5 и 6 задания функции, входов управления 7 и 8 и входов 11 и 12 переноса.

При подаче на воды 5 и 6 комбинации "10" разряд сумматора работает в одном из следующих режимов:

режиме генерации собственного переноса;

режиме передачи сквозного переноса.

Разряд сумматора работает в режиме генерации собственного переноса при совпадении сигналов на его входах 2 и 3 разрядов операндов; при этом на его выходах управления 9 и 10 формируются сигналы "00" или "11" и, в случае комбинации "00", открыт первый МДП-транзистор 20 р-типа, закрыты первый 26 и второй 27 МДП-транзисторы n-типа, на входе инвертора 19 устанавливается "1", а на выходе 13 переноса данного разряда "0"; в случае комбинации "11" открыт первый МДП-транзиcтор 26 n-типа, закрыты первый 20 и второй 21 МДП-транзисторы р-типа, на входе инвертора 19 через открытый третий МДП-транзистор 28 n-типа устанавливается "0", а на выходе 13 переноса разряда "1".

Разряд сумматора работает в режиме передачи сквозного переноса при несовпадении сигналов на его входах 2 и 3 разрядов операндов; при этом на его первом 9 и втором 10 выходах управления формируются соответственно "0" и "1", первые МДП-транзисторы р-типа 20 и n-типа 26 закрыты, вторые МДП-транзисторы р-типа 21 и n-типа 27 открыты, и состояние сигнала на входе инвертора 19 определяется уровнями сигналов на входах управления 7 и 8 разряда, а также уровнем сигнала на его дополнительном входе 12 переноса.

Так, если на входах 7 и 8 управления данного разряда установлена комбинация "00", соответствующая режиму генерации собственного переноса соседнего разряда сумматора, у рассматриваемого разряда открыт пятый МДП-транзистор 24 р-типа, закрыты четвертый 29 и седьмой 32 МДП-транзисторы n-типа, на входе инвертора 19 через открытый второй МДП-транзистор 21 р-типа устанавливается уровень "1", а на выходе 13 переноса данного разряда "0", если же на входах 7 и 8 управления данного разряда сумматора установлена комбинация "11", также соответствующая режиму генерации собственного переноса соседнего младшего разряда сумматора, у рассматриваемого разряда открыт четвертый МДП-транзистор 29 n-типа, закрыты четвертый 23 и пятый 24 МДП-транзисторы р-типа, на входе инвертора 19 через открытые второй 27 и четвертый 30 МДП-транзисторы n-типа устанавливается уровень "0", а на выходе 13 переноса данного разряда "1"; если же на входах 7 и 8 управления данного разряда установлена комбинация "01", соответствующая режиму передачи сквозного переноса соседнего младшего разряда сумматора, у рассматриваемого разряда сумматора пятый МДП-транзистор 24 р-типа и четвертый МДП-транзистор 29 n-типа закрыты, четвертый МДП-транзистор 23 р-типа и седьмой МДП-транзистор 32 n-типа открыты, что в совокупности с открытыми вторыми МДП-транзисторами р-типа 21 и n-типа 27 обеспечивает передачу через третий 22 МПД-транзистор р-типа и шестой 31 МДП-транзистор n-типа двоичной инверсии сигнала с дополнительного входа 12 переноса на вход инвертора 19, так что на выходе 13 переноса данного разряда устанавливается уровень, соответствующий прямому значению сигнала на его входе 12 переноса; комбинация "10" на входах 7 и 8 управления разрядов запрещена.

Для обеспечения правильного распространения переноса в сумматоре у самого младшего его разряда входы 7 и 8 управления соединены соответственно с "0" и "1", а у самой младшей пары его разрядов дополнительные входы 12 переноса соединены со входом 35 начального переноса сумматора.

Пусть на вход 35 начального переноса сумматора подается прямое значение сигнала переноса. Тогда в режиме передачи сквозного переноса, на выходах 13 переноса разрядов устанавливаются прямые значения поразрядных переносов, и в режиме генерации собственного переноса "0" на них соответствует комбинации "00" прямых значений сигналов входных операндов, а "1" комбинации "11" этих сигналов.

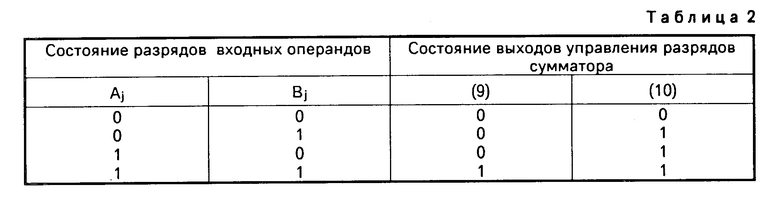

В табл.2 отражены возможные состояния на выходах 9 и 10 управления разрядов сумматора, из которой следует, что они могут быть описаны как:

F(9)= Aj∧Bj=  , F(10)= Aj∨Bj=

, F(10)= Aj∨Bj=

При этом на выходе первого элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 15 формируется функция отрицания равнозначности:

F(15)= ( )∧(

)∧( )∨(

)∨( )∧(

)∧( ) (

) ( )∨(A

)∨(A ) которая в каждом разряде сумматора складывается по mod2 на втором элементе ИСКЛЮЧАЮЩЕЕ ИЛИ 16 с выходным переносом соседнего младшего разряда, поступающим через вход 11 переноса, так что на выходах 14 разрядов сумматора формируется прямое значение суммы входных операндов; для обеспечения правильности функционирования вход 11 переноса самого младшего разряда сумматора соединен со входом 35 начального переноса сумматора.

) которая в каждом разряде сумматора складывается по mod2 на втором элементе ИСКЛЮЧАЮЩЕЕ ИЛИ 16 с выходным переносом соседнего младшего разряда, поступающим через вход 11 переноса, так что на выходах 14 разрядов сумматора формируется прямое значение суммы входных операндов; для обеспечения правильности функционирования вход 11 переноса самого младшего разряда сумматора соединен со входом 35 начального переноса сумматора.

Таким образом, при подаче на сумматор начального переноса в прямом коде разряды входных операндов подаются на него в двоично-инверсном коде, а последовательное распространение сигнала переноса происходит не через каждый разряд сумматора, как у прототипа, а двумя параллельными путями через каждый второй его разряд.

При подаче на входы 5 и 6 задания функции комбинации "01" на выходах 9 и 10 каждого разряда сумматора устанавливается соответственно "0" и "1", на выходах первых элементов ИСКЛЮЧАЮЩЕЕ ИЛИ 15 устанавливается "1", закрыты первый 20 и пятый 24 МДП-транзисторы р-типа, а также первый 26 и четвертый 29 МДП-транзисторы n-типа, открыты второй 21 и четвертый 23 МДП-транзисторы р-типа, а также второй 27 и седьмой 32 МДП-транзисторы n-типа, и каждый разряд сумматора работает в режиме передачи сквозного переноса.

Так, если на входе 35 начального переноса сумматора установлен "0", он передается на выходы 13 переноса каждого разряда сумматора без изменений и поступает на их входы 11 переноса, формируя через вторые элементы ИСКЛЮЧАЮЩЕЕ ИЛИ 16 значение "1" на выходах 14 суммы каждого из разрядов; аналогично "1" со входа 35 начального переноса сумматора передается на входы 11 переноса каждого из разрядов, инвертируя на вторых элементах ИСКЛЮЧАЮЩЕЕ ИЛИ 16 состояние выходов первых элементов ИСКЛЮЧАЮЩЕЕ ИЛИ 15 и формируя "0" на выходах 14 сумматора.

Таким образом, в зависимости от состояния входа 35 начального переноса, сумматор формирует на выходах 14 либо значение константы "0", либо ее поразрядную инверсию, которая может, в частности, представлять значение константы "-1" в дополнительном коде. При этом последовательное распространение сигнала переноса происходит в сумматоре двумя параллельными путями через каждый второй его разряд.

При подаче на входы 5 и 6 задания функции "0" на втором выходе 10 управления каждого разряда сумматора устанавливается "1", на выходах первых элементов ИСКЛЮЧАЮЩЕЕ ИЛИ 15 устанавливается отрицание конъюнкции прямых значений входных операндов, первый 20 и пятый 24 МДП-транзисторы р-типа закрыты, второй 27 и седьмой 32 МДП-транзисторы n-типа открыты, а состояние первого 26 МДП-транзистора n-типа, второго 21 и четвертого 23 МДП-транзисторов р-типа определяется состоянием входных операндов.

В этом случае устойчивое функционирование сумматора обеспечивается подачей "1" на его вход 35 начального переноса, которая у самой младшей пары разрядов закрывает третьи МДП-транзисторы 22 р-типа и открывает шестые МДП-транзисторы 31 n-типа, устанавливая через инверторы 19 на выходах 13 переноса этих разрядов "1", и т.д. от более младшей пары разрядов к следующей старшей; "1" с выходов 13 переноса разрядов поступает на входы 11 переноса и инвертирует на вторых элементах ИСКЛЮЧАЮЩЕЕ ИЛИ 16 состояние первых элементов ИСКЛЮЧАЮЩЕЕ ИЛИ 15, формируя на выходах 14 сумматора поразрядную конъюнкцию прямых значений входных операндов.

При подаче на входы 5 и 6 задания функции "1" на первом выходе 9 управления каждого разряда сумматора устанавливается "0", на выходах первых элементов ИСКЛЮЧАЮЩЕЕ ИЛИ 15 устанавливается дизъюнкция прямых значений входных операндов, первый 26 и четвертый 29 МДП-транзисторы n-типа закрыты, второй 21 и четвертый 23 МДП-транзисторы р-типа открыты, а состояние первого 20 и пятого 24 МДП-транзистров р-типа, второго 27 и седьмого 32 МДП-транзисторов n-типа определяются состоянием разрядов входных операндов.

В этом случае устойчивое функционирование сумматора обеспечивается подачей "0" на его вход 35 начального переноса, который у самой младшей пары разрядов закрывает шестые МДП-транзисторы 31 n-типа и открывает третьи МДП-транзисторы 22 n-типа, устанавливая через инверторы 19 на выходах переноса 13 этих разрядов значения "0", и т.д. от более младшей пары разрядов к следующей старшей; "0" с выходов 13 переноса разрядов поступает через входы 11 переноса на вторые элементы ИСКЛЮЧАЮЩЕЕ ИЛИ 16, которые передают на выходы 14 сумматора поразрядную дизъюнкцию прямых значений входных операндов с выходов первых элементов ИСКЛЮЧАЮЩЕЕ ИЛИ 15 без изменения. При этом последовательное распространение сигнала переноса происходит в сумматоре двумя параллельными путями через каждый второй его разряд.

При подаче "0" на первый вход 4 задания функции третий 28 и пятый 30 МДП-транзисторы n-типа закрыты, шестой МДП-транзистор 25 р-типа открыт, и устойчивое функционирование сумматора обеспечивается в каждом разряде выключением шестого МДП-транзистора 31 n-типа:

в младшей паре разрядов сумматора подачей "0" на вход 35 начального переноса сумматора;

в остальных разрядах сумматора подачей "0" на входы 12 переноса с выходов 13 переноса соответствующих более младших разрядов.

При подаче на входы 5 и 6 задания функции "1" на первом выходе 9 управления каждого разряда сумматора устанавливается "0", а на выходах первых элементов ИСКЛЮЧАЮЩЕЕ ИЛИ 15 устанавливается дизъюнкция прямых значений входных операндов. Учитывая, что на входах 11 переноса разрядов сумматора установлен "0", во всех его разрядах вторые элементы ИСКЛЮЧАЮЩЕЕ ИЛИ 16 передают на выходы 14 сумматора состояние первых элементов ИСКЛЮЧАЮЩЕЕ ИЛИ 15 без изменений, устанавливая на них поразрядную дизъюнкцию прямых значений входных операндов.

При подаче на входы 5 и 6 задания функции комбинации "10" состояние первого 9 и второго 10 выходов управления разрядов сумматора определяется состоянием разрядов входных операндов, и на выходах первых элементов ИСКЛЮЧАЮЩЕЕ ИЛИ 15 устанавливается поразрядное отрицание равнозначности их прямых значений, которое и передается через вторые элементы ИСКЛЮЧАЮЩЕЕ ИЛИ 16 на выходы 14 сумматора без изменений.

При подаче на входы 5 и 6 задания функции комбинации "01" на выходах 9 и 10 каждого разряда сумматора устанавливается соответственно "0" и "1", а на выходах первых элементов ИСКЛЮЧАЮЩЕЕ ИЛИ 15 устанавливается значение "1", которое и передается через вторые элементы ИСКЛЮЧАЮЩЕЕ ИЛИ 16 на выходы 14 сумматора без изменений.

При подаче на входы 5 и 6 задания функции "0" на втором выходе 10 управления каждого разряда сумматора устанавливается "1", а на выходах первых элементов ИСКЛЮЧАЮЩЕЕ ИЛИ 15 устанавливается поразрядное отрицание конъюнкции прямых значений входных операндов, которое и передается через вторые элементы ИСКЛЮЧАЮЩЕЕ ИЛИ 16 на выходы 14 сумматора без изменений.

Не указанные выше сочетания сигналов на входах 4, 5, 6 и 35 сумматора не используются.

В качестве примера рассмотрим реализацию схемы формирования начального переноса заявляемого устройства в предположении, что константа единицы на выходах сумматора формируется согласно восьмой строке табл.1, а функция поразрядной дизъюнкции входных операндов формируется согласно шестой строке табл.1; при этом комбинации второй и пятой строк табл.1 не используются.

Из табл.1 следует что в этом случае сигнал Сн может быть описан как:

Cн= F(4)∧( Cвх)

Cвх)  где Свх прямое значение сигнала входного переноса заявляемого устройства. Реализация такой схемы на КМДП-транзисторах не требует больших аппаратурных затрат и не приводит к существенному ухудшению динамических параметров арифметико-логического устройства, использующего заявляемый сумматор.

где Свх прямое значение сигнала входного переноса заявляемого устройства. Реализация такой схемы на КМДП-транзисторах не требует больших аппаратурных затрат и не приводит к существенному ухудшению динамических параметров арифметико-логического устройства, использующего заявляемый сумматор.

Таким образом, из вышеизложенного видно, что во всех режимах работы у N-разрядного заявляемого сумматора, выполняющего функции конъюнкции, дизъюнкции, равнозначности, констант "0" и единицы, максимальная задержка распространения сигнала переноса соответствует времени его распространения в Е[(N+1)/2] последовательно соединенных разрядах, где E[x] целая часть х, что в два раза меньше, чем у прототипа.

| название | год | авторы | номер документа |

|---|---|---|---|

| Формирователь переноса | 1991 |

|

SU1798778A1 |

| Формирователь переноса | 1990 |

|

SU1702361A1 |

| Узел формирования переноса | 1986 |

|

SU1363189A1 |

| Узел формирования переноса в сумматоре | 1985 |

|

SU1287147A1 |

| Сумматор | 1986 |

|

SU1406591A1 |

| УСТРОЙСТВО СЛОЖЕНИЯ С УСКОРЕННЫМ ПЕРЕНОСОМ | 2000 |

|

RU2198421C2 |

| СУММАТОР НА КМДП ТРАНЗИСТОРАХ | 2001 |

|

RU2185655C1 |

| Устройство для формирования группового переноса | 1985 |

|

SU1335981A1 |

| УСТРОЙСТВО СРАВНЕНИЯ НА КМДП ТРАНЗИСТОРАХ | 2003 |

|

RU2236696C1 |

| Узел формирования переноса в сумматоре | 1985 |

|

SU1312567A1 |

Изобретение относится к вычислительной технике, в частности к устройствам на КМДП-транзисторах для арифметической и логической обработки цифровой информации. Сумматор содержит в каждом разряде элементы ИСКЛЮЧАЮЩЕЕ ИЛИ, И НЕ, ИЛИ НЕ, инвертор, шесть МДП-транзисторов p-типа, семь МДП-транзисторов n-типа, первый, второй и третий входы задания функции, входы управления, выходы управления, вход переноса и дополнительный вход переноса, выходы переноса и суммы. Достигаемый технический эффект заключается в повышении быстродействия сумматора, выполняющего логические функции конъюнкции, дизъюнкции, разнозначности, констант "0" и единицы. 1 ил. 2 табл.

СУММАТОР, каждый разряд которого содержит элемент И-НЕ, элемент ИЛИ-НЕ, первый и второй элементы ИСКЛЮЧАЮЩЕЕ ИЛИ, инвертор, первый, второй, третий и четвертый МДП-транзисторы p-типа и первый, второй, третий и четвертый МДП-транзисторы n-типа, причем в каждом разряде выход элемента И-НЕ соединен с затвором первого МДП-транзистора p-типа и первым входом первого элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, выход элемента ИЛИ-НЕ соединен с затвором первого МДП-транзистора n-типа и вторым входом первого элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, выход которого соединен с первым входом второго элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, второй вход которого соединен с входом переноса данного разряда сумматора, а выход образует его выход суммы, стоки первых МДП-транзисторов n- и p-типа соединены со стоками вторых МДП-транзисторов n- и p-типа, исток первого МДП-транзистора n-типа соединен со стоком третьего МДП-транзистора n-типа, исток которого соединен с шиной нулевого потенциала сумматора, а затвор соединен с первым входом задания функции сумматора, исток третьего МДП-транзистора p-типа соединен со стоком четвертого МДП-транзистора p-типа, исток которого соединен с шиной питания сумматора, а затвор соединен с затвором четвертого МДП-транзистора n-типа и входом управления данного разряда сумматора, первый и второй входы элементов И-НЕ, ИЛИ-НЕ данного разряда сумматора соединены с соответствующим разрядом входов первого и второго операндов сумматора, а их третьи входы соединены соответственно с вторым и третьим входами задания функции сумматора, отличающийся тем, что каждый разряд дополнительно содержит пятый и шестой МДП-транзисторы p-типа и пятый, шестой и седьмой МДП-транзисторы n-типа, а также дополнительный вход переноса и дополнительный вход управления, причем вход инвертора соединен со стоками первых МДП-транзисторов n- и p-типа, а его выход образует выход переноса данного разряда сумматора, исток второго МДП-транзистора p-типа соединен со стоками третьего и пятого МДП-транзисторов p-типа, исток второго МДП-транзистора n-типа соединен со стоками пятого и шестого МДП-транзисторов n-типа, истоки первого, пятого и шестого МДП-транзисторов p-типа соединены с шиной питания сумматора, сток шестого МДП-транзистора p-типа соединен с входом инвертора, а его затвор соединен с первым входом задания функции сумматора, истоки четвертого и седьмого МДП-транзисторов p-типа соединены с шиной нулевого потенциала сумматора, а их стоки соединены соответственно с истоками пятого и шестого МДП-транзисторов n-типа, затвор пятого МДП-транзистора n-типа соединен с первым входом задания функции сумматора, затворы пятого МДП-транзистора p-типа и седьмого МДП-транзистора n-типа соединены с дополнительным входом управления данного разряда сумматора, затворы третьего МДП-транзистора p-типа и шестого МДП-транзистора n-типа соединены с дополнительным входом переноса данного разряда сумматора, затворы вторых МДП-транзисторов p- и n-типа образуют первый и второй выходы управления данного разряда сумматора и соединены соответственно с выходами элементов ИЛИ-НЕ и И-НЕ, выход переноса каждого разряда сумматора соединен с входом переноса соседнего старшего разряда сумматора и с дополнительным входом переноса следующего за ним разряда сумматора, первый и второй выходы управления каждого разряда сумматора соединены соответственно с входом управления и с дополнительным входом управления соседнего старшего разряда сумматора, дополнительные входы переноса младшей пары разрядов сумматора соединены с входом переноса самого младшего разряда сумматора и входом начального переноса сумматора, вход управления самого младшего разряда сумматора соединен с шиной логического нуля, а его дополнительный вход управления соединен с шиной логической единицы.

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Сумматор | 1986 |

|

SU1406591A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1995-11-27—Публикация

1994-03-10—Подача