Предлагаемое устройство относится к устройствам управления визуальных индикаторов и может быть использовано в индикаторах с растровой и/или векторной разверткой для коррекции геометрических и масштабных искажений.

Известно устройство, содержащее цифроаналоговые преобразователи, усилители отклонения, электронно-лучевую трубку (ЭЛТ) с отклоняющей системой, блоки узловых значений, интерполятор и блок адресов. Входы цифроаналоговых преобразователей, интерполятора и блока адресов являются входами устройства. Выходы блоков узловых значений соединены с вторыми входами усилителей отклонения по осям Х и Y, первые входы которых соединены с выходами соответствующих цифроаналоговых преобразователей, а выходы - с отклоняющими катушками отклоняющей системы ЭЛТ, см. авторское свидетельство СССР №791558 от 21.09.1977 по классу В41В 19/00.

В данном устройстве функции формирования координат узлов и значений сигналов отклонения в межузловых точках разделены между блоком узловых значений и интерполятором соответственно. Его настройка сводится к подбору значений сигналов отклонения в узловых точках, вычислению и вводу в запоминающее устройство интерполятора значений приращений для каждой из зон. Блок адресов, блоки узловых значений и интерполятор данного устройства представляют собой аналого-цифровой (гибридный) функциональный преобразователь функций двух переменных по осям Х и Y, которому присуща низкая точность из-за разброса параметров (в основном, сопротивление аналоговых ключей в открытом состоянии) и погрешности выполнения операций сложения и умножения аналоговым способом.

Известно также устройство, содержащее блок адресов прямоугольных зон, блок узловых значений по оси X, блок узловых значений по оси Y, двухкоординатный интерполятор по осям Х и Y. Выходы блока адресов прямоугольных зон соединены с входами блоков узловых значений по осям Х и Y и соответствующими адресными входами двухкоординатного интерполятора. Адресные входы двухкоординатного интерполятора подсоединены к выходам блоков узловых значений по осям Х и Y соответственно. Входы развертывающих функций по осям Х и Y двухкоординатного интерполятора подсоединены к входам блока адресов зон и к входам устройства по осям Х и Y. Выходы двухкоординатного интерполятора являются выходами устройства по осям Х и Y, см. патент на изобретение №2262747 от 24.12.2003 по классу G09G 1/07, 1/10, 1/18.

Его настройка сводится к подбору значений сигналов отклонения по осям Х и Y в узловых точках и ввод их координат в блоки узловых значений. Данное устройство принято за прототип.

Недостатком прототипа является низкое быстродействие, обусловленное большим объемом последовательно выполняемых операций: формирование адресов зон, считывание узловых значений интерполирующей функции по осям Х и Y и, кроме того, выполнение в интерполяторе вычислений, необходимых для формирования интерполирующей функции.

Целью заявляемого изобретения является повышение быстродействия в рабочем режиме.

Сущность предлагаемого устройства заключается в том, что оно содержит блок адресов прямоугольных зон, блоки узловых значений по осям Х и Y и двухкоординатный интерполятор по осям Х и Y. Выходы блока адресов прямоугольных зон соединены с адресными входами двухкоординатного интерполятора и с входами блоков узловых значений по осям Х и Y соответственно. Входы блока адресов прямоугольных зон соединены с входами развертывающих функций по осям Х и Y двухкоординатного интерполятора, а выходы блоков узловых значений по осям Х и Y соединены с входами данных двухкоординатного интерполятора по одноименным осям.

В отличие от прототипа в него введены генератор тактовых импульсов, счетчик адресный по оси X, счетчик адресный по оси Y, первый блок замыкающих ключей по оси X, первый блок замыкающих ключей по оси Y, блок размыкающих ключей по оси X, блок размыкающих ключей по оси Y, запоминающее устройство, второй блок замыкающих ключей по оси X, второй блок замыкающих ключей по оси Y, инвертор и вход управления.

Входы блоков размыкающих ключей по осям Х и Y соединены с входами устройства по соответствующим осям. Выходы блока размыкающих ключей по оси Х и первого блока замыкающих ключей по оси Х соединены с соответствующим входом блока адресов прямоугольных зон и входом адреса запоминающего устройства по оси X. Выход блока размыкающих ключей по оси Y и первого блока замыкающих ключей по оси Y соединены с соответствующим входом блока адресов прямоугольных зон и входом адреса запоминающего устройства по оси Y.

Генератор тактовых импульсов подсоединен к входу счетчика адресного по оси X. Выход счетчика адресного по оси Х соединен с входом счетчика адресного по оси Y и с входом первого блока замыкающих ключей по оси X. Выход счетчика адресного по оси Y соединен с входом первого блока замыкающих ключей по оси Y.

Выходы двухкоординатного интерполятора по осям Х и Y через вторые блоки замыкающих ключей соединены с входом данных запоминающего устройства по одноименным осям, которые являются также выходами устройства по осям Х и Y.

Входы управления всех ключей и вход разрешения записи запоминающего устройства подсоединены к входу управления предлагаемого устройства. Вход разрешения чтения запоминающего устройства соединен с входом управления предлагаемого устройства через инвертор.

Повышение быстродействия предлагаемого устройства в рабочем режиме обусловлено тем, что откорректированные значения развертывающих функций по осям Х и Y считываются из запоминающего устройства.

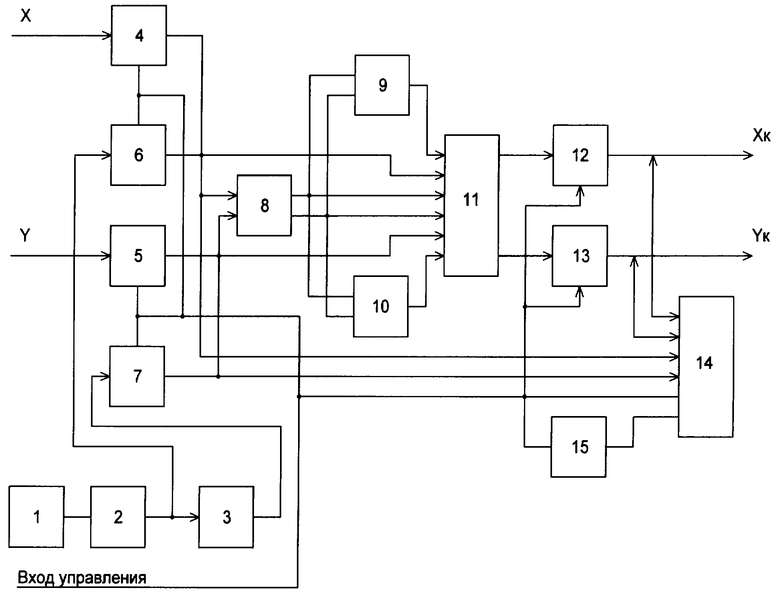

На чертеже приведена блок-схема предлагаемого устройства.

Предлагаемое устройство содержит генератор 1 тактовых импульсов, счетчик 2 адресный по оси X, счетчик 3 адресный по оси Y, блоки 4 и 5 размыкающих ключей соответственно по осям Х и Y, первые блоки 6 и 7 замыкающих ключей соответственно по осям Х и Y, блок 8 адресов прямоугольных зон, блоки 9 и 10 узловых значений соответственно по осям Х и Y, двухкоординатный интерполятор 11, вторые блоки 12 и 13 замыкающих ключей соответственно по осям Х и Y, запоминающее устройство 14, инвертор 15.

Входы блоков 4 и 5 размыкающих ключей по оси Х и по оси Y соединены с входом устройства по соответствующим осям. Генератор 1 тактовых импульсов соединен с входом счетчика 2 адресного по оси X, выход которого соединен с входом счетчика 3 адресного по оси Y и входом первого блока 6 замыкающих ключей по оси X. Выход счетчика 3 адресного по оси Y соединен с входом первого блока 7 замыкающих ключей по оси Y.

Выходы первого блока 4 размыкающих ключей и блока 6 замыкающих ключей по оси Х подсоединены к входу блока 8 адресов прямоугольных зон по оси Х и входу адреса по оси Х запоминающего устройства 14.

Выходы первого блока 5 размыкающих ключей и блока 7 замыкающих ключей по оси Y подсоединены к входу блока 8 адресов прямоугольных зон по оси Y и входу адреса по оси Y запоминающего устройства 14.

Первый и второй выходы блока 8 адресов прямоугольных зон соединены с адресными входами двухкоординатного интерполятора 11 и с первым и вторым входами блока 9 узловых значений по оси Х и блока 10 узловых значений по оси Y соответственно. Входы блока 8 адресов прямоугольных зон соединены с входами развертывающих функций по осям Х и Y двухкоординатного интерполятора 11.

Выходы блоков 9, 10 узловых значений по осям Х и Y соединены с соответствующими входами данных двухкоординатного интерполятора.

Выходы двухкоординатного интерполятора по осям Х и Y через вторые блоки 12, 13 замыкающих ключей соединены с входами данных запоминающего устройства 14 по соответствующим осям, которые являются также выходами устройства по осям Х и Y.

Входы управления первых 6, 7 и вторых 12, 13 блоков замыкающих ключей и блоков 4, 5 размыкающих ключей по осям Х и Y и вход разрешения записи запоминающего устройства 14 подсоединены к входу управления устройства. Вход разрешения чтения запоминающего устройства 14 подсоединен к входу управления устройства через инвертор 15.

Устройство работает в режиме настройки и в рабочем режиме.

Устройство настраивается в два этапа:

- обмер;

- калибровка.

Обмер заключается в определении узловых значений интерполирующей функции. На входы устройства от внешнего графического контроллера поступают цифровые развертывающие функции по осям Х и Y в прямоугольной системе координат с диапазоном измерения: 0 Х К, 0 Y L. Таким образом формируется поле изображения, содержащее К×L пикселей. В этом режиме сигнал на входе управления отсутствует, и, следовательно, поступающий с выхода инвертора сигнал переводит запоминающее устройство, в ячейки которого предварительно занесены адреса этих же ячеек, в режим чтения. Размыкающие ключи блоков размыкающих ключей замкнуты, и входы устройства по осям Х и Y подсоединены к соответствующим адресным входам запоминающего устройства. Следовательно, значения развертывающих функций по осям Х и Y на соответствующих входах и выходах устройства совпадают.

Поле изображения формируется устройством отображения, в состав которого входит предлагаемое устройство. Оно условно разбито на зоны, образующие прямоугольную сетку, узлы которой имеют координаты Х0, X1, …, Xm по оси Х и Y0, Y1, …, Yn по оси Y. С экраном устройства отображения, в которое входит предлагаемое устройство, оптически сопряжен трафарет с изображением прямоугольной сетки, координаты Хтi, Yтj узлов которой связаны с координатами узлов Xi, Yj сетки поля изображения соотношением:

Хтi=кХi;

Yтj=кYj;

где к - масштабный коэффициент.

Изменяя значения развертывающих функций в окрестностях точек с координатами Xi, Yj, добиваются совмещения формируемого на экране изображения узла с узлом Хтi, Yтj трафаретной сетки. Подобранные таким образом узловые значения интерполирующей функции X0i,j по оси Х и Y0i,j по оси Y каким-либо образом, например с помощью программатора, записываются в блоки узловых значений по оси Х и оси Y соответственно.

После обмера производится калибровка устройства. Калибровка заключается в записи в запоминающее устройство откорректированных значений развертывающих функций для каждого пикселя формируемого поля изображения.

Для проведения калибровки на вход управления устройства подается сигнал управления. В результате ключи в блоках 4, 5 размыкающих ключей переходят в разомкнутое состояние, ключи в блоках 6, 7 замыкающих ключей переходят в замкнутое состояние, запоминающее устройство 14 переключается в режим записи.

Длительность периода следования импульсов, формируемых генератором 1 тактовых импульсов, больше суммы времен определения адреса зоны блоком 8 адреса прямоугольных зон, выборки узловых значений интерполирующей функции из блоков 9, 10 узловых значений по осям Х и Y, формирования корректированных координат Хк, Yк двухкоординатным интерполятором 11 и записи данных в запоминающее устройство 14.

Последовательно соединенные счетчики 2 и 3 адресные по оси Х и по оси Y формируют из последовательности импульсов, вырабатываемых генератором 1 тактовых импульсов, поступающих на вход счетчика 2 адресного по оси X, последовательность линейно изменяющихся значений кодов адресов пикселей поля изображения. Коэффициенты деления счетчиков 2, 3 адресных по осям Х и Y равны К и L соответственно. Таким образом обеспечивается формирование адресов для всех К×L пикселей поля изображения.

С выходов счетчиков 2, 3 адресных по оси Х и по оси Y через замкнутые ключи блоков 6, 7 замыкающих ключей по оси Х и по оси Y коды адресов поступают на соответствующие входы блока 8 адресов прямоугольных зон, двухкоординатного интерполятора 11 и запоминающего устройства 14.

Блок 8 адресов прямоугольных зон формирует значения координат прямоугольных зон, которые определяются в своей Р, Q системе координат, оси которой совпадают с осями X, Y:

Р=i при Xi Х<Xi-1;

Q=j при Yj Y<Yj+1.

Диапазон изменения значений координат зон:

Р=0, … m-1;

Q=0, … n-1.

С выхода блока 8 адресов зон коды адресов зон поступают на адресные входы двухкоординатного интерполятора 11 и соответствующие входы блоков 9, 10 узловых значений по оси Х и по оси Y. При этом подобранные на этапе обмера и занесенные в блоки 9, 10 узловых значений узловые значения интерполирующей функции Х0ij по оси Х и Y0ij по оси Y считываются из них и поступают на входы данных двухкоординатного интерполятора 11, на входы развертывающих функций которого поступают также коды адресов пикселей поля изображения по осям Х и Y.

По кодам адресов пикселей изображения по осям X, Y адресов зон Р, Q и узловым значениям интерполирующей функции X0i,j, Y0i,j двухкоординатный интерполятор 11, используя один из известных методов (кусочно-линейная интерполяция, сплайн интерполяция и т.д.), вычисляет корректированные координаты пикселей поля изображения Хк, Yк.

С выходов двухкоординатного интерполятора 11 через замкнутые ключи блоков 12, 13 замыкающих ключей корректированные координаты пикселей изображения Хк, Yк поступают на соответствующие входы данных запоминающего устройства 14, на адресные входы которого поступают неоткорректированные координаты пикселей поля изображения. Таким образом, в каждую ячейку запоминающего устройства 14 с адресом X, Y заносятся откорректированные координаты Хк, Yк. Процесс настройки заканчивается после записи откорректированных координат во все К×L ячейки запоминающего устройства 14.

Для перехода в рабочий режим снимается сигнал с входа управления предлагаемого устройства. При этом поступающий с выхода инвертора 15 сигнал переводит запоминающее устройство 14 в режим чтения. Ключи блоков 4, 5 замыкающих ключей замкнуты, и входы устройства по осям X, Y подключены к соответствующим адресным входам запоминающего устройства 14. Ключи блоков 12, 13 размыкающих ключей разомкнуты, и выходы устройства по осям X, Y подключены к соответствующим выходам данных запоминающего устройства 14. Таким образом, развертывающие функции по осям X, Y поступают на соответствующие адресные входы запоминающего устройства 14, с выходов которого за один цикл чтения считываются откорректированные значения развертывающей функции Хк, Yк.

Был разработан и испытан макет предлагаемого устройства, все функциональные блоки, кроме запоминающего устройства, реализованы на ПЛИС ф. XILIX. Запоминающее устройство было выполнено на постоянных запоминающих устройствах Am 29LV033C-90EE типа FLAH.

Быстродействие устройства в рабочем режиме определяется минимально допустимой длительностью цикла чтения запоминающего устройства, которая в данном случае равна 90 нс.

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО УПРАВЛЕНИЯ ДЛЯ ЭЛЕКТРОННО-ЛУЧЕВОГО ИНДИКАТОРА | 2003 |

|

RU2262747C1 |

| Устройство для управления графопостроителем | 1975 |

|

SU610108A1 |

| Интерполятор функций двух аргументов | 1984 |

|

SU1247893A1 |

| Многокоординатный цифровой интерполятор | 1984 |

|

SU1200246A1 |

| Многоканальный интерполятор функций | 1986 |

|

SU1361588A1 |

| Устройство для формирования окружностей | 1983 |

|

SU1096688A2 |

| Цифровой квадратичный интерполятор | 1985 |

|

SU1290354A1 |

| Многокоординатный линейно-круговой интерполятор | 1988 |

|

SU1603345A1 |

| Устройство для формирования динамического изображения на экране электронно-лучевой трубки | 1980 |

|

SU941988A1 |

| Линейный интерполятор для систем интерактивной графики | 1988 |

|

SU1608691A1 |

Изобретение относится к устройствам управления визуальных индикаторов. Техническим результатом является повышение быстродействия формирования поля изображения. Результат достигается тем, что в устройство, содержащее блок адресов прямоугольных зон, блоки узловых значений по осям Х и Y и двухкоординатный интерполятор, введены генератор тактовых импульсов, счетчики адресные по осям Х и Y, первые и вторые блоки замыкающих и блоки размыкающих ключей по осям Х и Y, запоминающее устройство и инвертор. 1 ил.

Устройство управления визуального индикатора, содержащее блок адресов прямоугольных зон, блоки узловых значений по осям Х и Y и двухкоординатный интерполятор, причем выходы блока адресов прямоугольных зон соединены с адресными входами двухкоординатного интерполятора и с входами блоков узловых значений по осям Х и Y соответственно, входы блока адресов прямоугольных зон соединены с входами развертывающих функций по осям Х и Y двухкоординатного интерполятора, а выходы блоков узловых значений по осям Х и Y соединены с входами данных двухкоординатного интерполятора по одноименным осям, отличающееся тем, что, с целью повышения быстродействия в рабочем режиме, в него введены генератор тактовых импульсов, счетчики адресные по осям Х и Y, первые и вторые блоки замыкающих ключей по осям Х и Y, блоки размыкающих ключей по осям Х и Y, запоминающее устройство и инвертор, при этом генератор тактовых импульсов соединен с входом счетчика адресного по оси X, выход которого соединен с входом счетчика адресного по оси Y, а выходы счетчиков адресных по осям Х и Y соединены с одноименными входами первых замыкающих ключей по осям Х и Y, входы блоков размыкающих ключей по осям Х и Y соединены с входами устройства по одноименным осям, выходы первого блока размыкающих ключей по оси Х и блока замыкающих ключей по оси Х соединены с первым входом блока адресов прямоугольных зон и входом адреса по оси Х запоминающего устройства, выходы первого блока размыкающих ключей по оси Y и блока замыкающих ключей по оси Y соединены со вторым входом блока адресов прямоугольных зон и входом адреса по оси Y запоминающего устройства, выходы двухкоординатного интерполятора по осям Х и Y через вторые блоки замыкающих ключей подключены к входам данных запоминающего устройства по одноименным осям, которые являются также выходами устройства по осям Х и Y, причем другие входы управления первых и вторых блоков замыкающих ключей и блоков размыкающих ключей по осям Х и Y и вход разрешения записи запоминающего устройства соединены с входом управления устройства, а вход разрешения чтения запоминающего устройства соединен с входом управления устройства через инвертор.

| УСТРОЙСТВО УПРАВЛЕНИЯ ДЛЯ ЭЛЕКТРОННО-ЛУЧЕВОГО ИНДИКАТОРА | 2003 |

|

RU2262747C1 |

| Устройство управления матричным индикатором | 1990 |

|

SU1785036A1 |

| СИСТЕМА ДИСПЛЕЯ | 1991 |

|

RU2119187C1 |

| Насос | 1917 |

|

SU13A1 |

| US 2008001900 A1, 03.01.2008. | |||

Авторы

Даты

2010-01-27—Публикация

2008-03-05—Подача