Изобретение относится к электроизмерительной технике, а именно к измерительным приборам с устройством управления матричным индикатором, и может быть использовано в системах регистрации и отображения кодовой информации, в частности может быть использовано в индикаторных приборах различного назначения. v Известно устройство управления световой шкалой, содержащее дешифратор и элементы световой шкалы, которые соединены матрицей, генератор констант. набор схем совпадения и набор схем объединения.

Недостаток устройства заключается в том, что для сохранения достаточной интегральной яркости шкалы необходима коммутация больших токов через ее элементы, что приводит к ускорению процесса их деградации. Недостатком устройства является также малая достоверность отображаемой информации при неисправности отдельных эл ементо в ш кал ы.s;,

Известно устройство управления световой шкалой, содержащее дешифратор, состоящий из преобразователей кода младших и старших разрядов в линейный

код, коммутаторы младших и старших разрядов, входы которых подключены соответственно к выходам преобразователей кода младших и старших разрядов, а выходы соединены с шинами строк и столбцов матрицы элементов световой шкалы и тактирующий генератор, подключенный к управляющим входам коммутаторов.

Недостатком устройства является низкая надежность, связанная с возникновением импульсных токовых перегрузок в процессе работы устройства, а также малая достоверность отображаемой информации при неисправности отдельных элементов шкалы.

Наиболее близким по технической сущности является устройство управления световой шкалой, содержащее два преобразователя, элементы НЕ, две группы коммутаторов, генератор тактовых импульсов и матричный индикатор. Первые входы коммутаторов первой и второй групп соединены соответственно с выходами первого и второго преобразователей кода, а выходы подключены соответственно к горизонтальным и вертикальным шинам матричного инч

ы

Ё

J 00 СП

о

А

ON

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для индикации | 1989 |

|

SU1667150A1 |

| Многоканальный преобразователь амплитуды телевизионного сигнала во временной интервал | 1983 |

|

SU1124452A1 |

| УСТРОЙСТВО ДЛЯ ТЕКУЩЕГО КОНТРОЛЯ И СТАТИСТИЧЕСКОГО АНАЛИЗА ОТКЛОНЕНИЙ НАПРЯЖЕНИЯ | 1997 |

|

RU2130199C1 |

| Устройство индикации измерительного прибора | 1984 |

|

SU1262395A1 |

| СТАТИСТИЧЕСКИЙ АНАЛИЗАТОР ОТКЛОНЕНИЙ НАПРЯЖЕНИЯ | 1992 |

|

RU2041497C1 |

| Устройство для измерения параметров газовых сред | 1980 |

|

SU894527A1 |

| АНАЛИЗАТОР ОТКЛОНЕНИЙ НАПРЯЖЕНИЯ | 1995 |

|

RU2106009C1 |

| ОПЕРАТИВНЫЙ КОНТРОЛЛЕР СУММАРНОЙ МОЩНОСТИ НАГРУЗКИ ГРУППЫ ЭНЕРГОПОТРЕБИТЕЛЕЙ | 1998 |

|

RU2145717C1 |

| Вычислительный узел цифровой сетки | 1983 |

|

SU1132295A2 |

| Вычислительный узел цифровой сетки | 1987 |

|

SU1501053A1 |

Использование: область автоматики и вычислительной техники, системы сбора и отображения информации. Сущность изобретения: устройство содержит четыре пре- образовател я кода, две группы коммутаторов, матричный индикатор, генератор тактовых импульсов, два элемента НЕ, элемент ИСКЛЮЧАЮЩЕЕ ИЛИ. два элемента ИЛИ-НЕ, три элемента ИЛИ, элемент И, счетчик, сумматор. 2 ип.

fe fe-fiP 3 S jBU-j.

i T fca4- i., fc.. .$

икатора. Генератор тактовых импульсов одключен к управляющим входам коммуаторов. Входы элементов НЕ подключены выходам первого преобразователя кода, а выходы соединены с вторыми входами комутаторов первой группы, вторые входы оммутаторов второй группы с удельным веом а -1 подключены к выходам второго преобразователя кода с удельным весом а , где 1 а п, где п - число вертикальных шин матричного индикатора.

Недостатком известного устройства явяется низкая надежность, связанная с воз- нйкноеением импульсных тактовых перегрузок в процессе работы устройства.

Цель изобретения - повышение надежности устройства.

Поставленная цель достигается тем, что в устройство управления матричным индикатором, содержащее первый преобразователь кода, вход которого является первым информационным входом устройства, второй преобразователь кода, коммутаторы первой и второй Групп, выходы которых подключены соответственно к горизонтальным и вертикальным шинам матричного индикатора, генератор тактовых импульсов, два элемента НЕ, введены два преобразователя кода, элементы ИСКЛЮЧАЮЩЕЕ ИЛИ, элемент И, два элемента ИЛИ-НЕ, три элемента ИЛИ, счетчик и сумматор, первый информационный вход которого подключен к шине нулевого потенциала, а второй информационный ёход является вторым информационным входом устройства, выход сумматора соединен со входом второго преобразователя кода, выходы которого соединены с первыми информационными входами соответствующих коммутаторов второй группы и с соответствующими входами третьего преобразователя кода, выходы которого соединены с вторыми информационными входами соответствующих коммутаторов второй группы, управляющие входы которых соединены с выходом первого элемента ИЛИ и с управляющими входами ком- мутаторов первой группы, первые информационные входы которых подключены к выходам соответствующих элементов ИСКЛЮЧАЮЩЕЕ ИЛИ. первые входы которых подключены к соответствующим выхо- дам первого преобразователя кода и к соответствующим входам четвертого преоб- разователя кода, а вторые входы соединены с первым выходом счетчика и с первым входом первого элемента ИЛИ, второй вход которого соединен с первым входом второго элемента ИЛИ и со вторым выходом счетчика, тактовый вход которого подключен к

выходу генератора тактовых импульсов, а третий выход соединен со входом первого элемента НЕ и с первым входом элемента И, второй вход которого соединен с выходом

младшего разряда первого преобразователя кода и с первым входом первого элемента ИЛИ-НЕ. второй вход которого подключен к выходу первого элемента НЕ. а выход соединен с первым входом третьего элемента

0 ИЛИ, второй вход которого подключен к выходу старшего разряда четвертого преобразователя кода, а выход соединен со вторым информационным входом коммутатора старшего разряда коммутаторов первой

5 группы, вторые информационные входы остальных коммутаторов первой группы подключены к соответствующим выходам четвертого преобразователя кода, выход элемента И подключен ко второму входу

0 второго элемента ИЛИ, выход которого соединен со входом второго элемента НЕ, выход которого соединен с первым входом второго элемента ИЛИ-НЕ, второй вход которого соединен с выходом старшего разря5 Да третьего преобразователя кода, а выход подключен к управляющему входу сумматора.

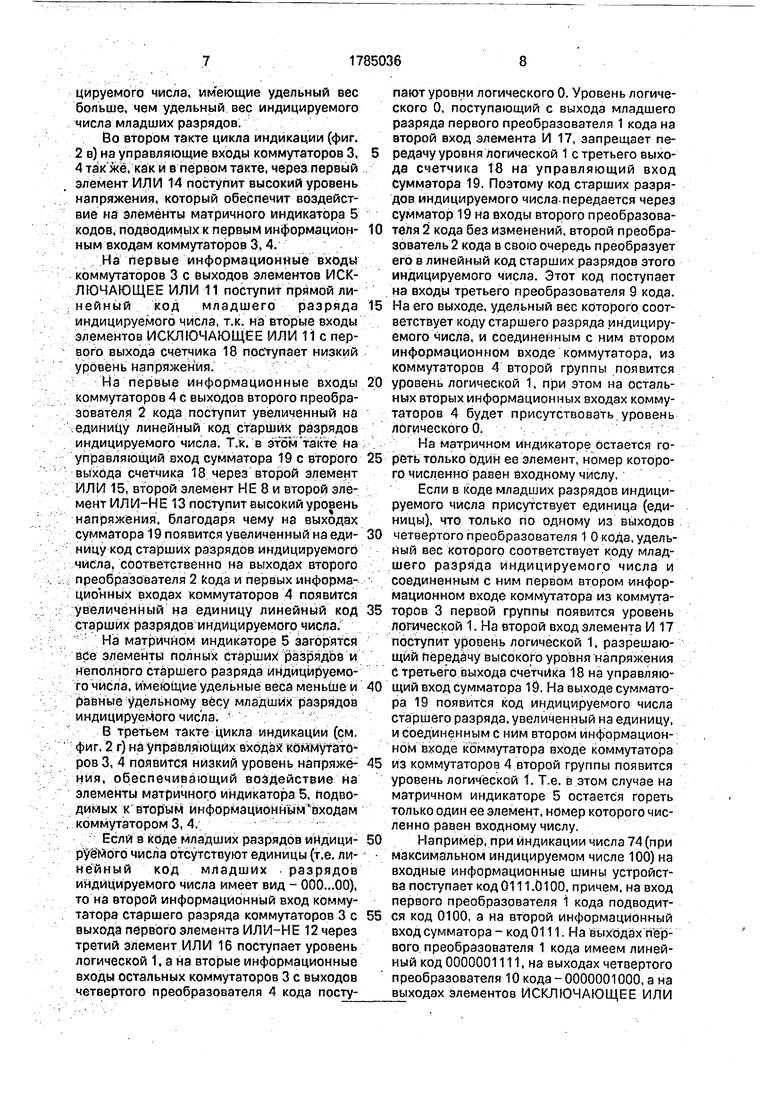

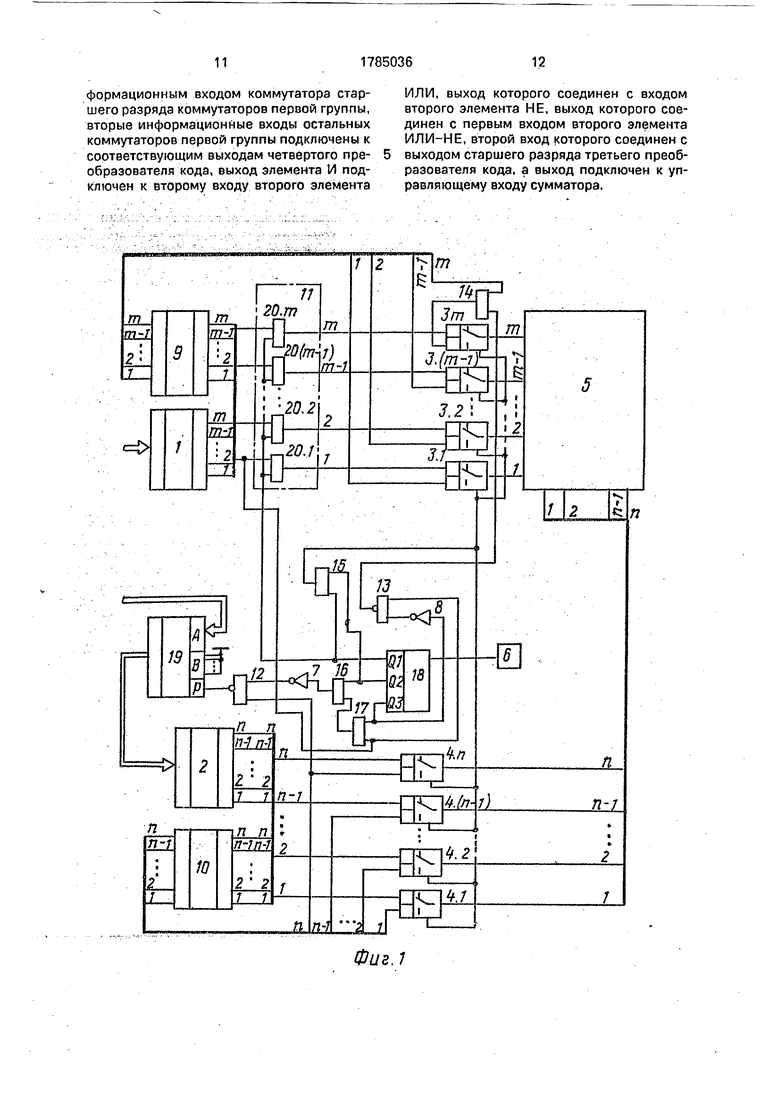

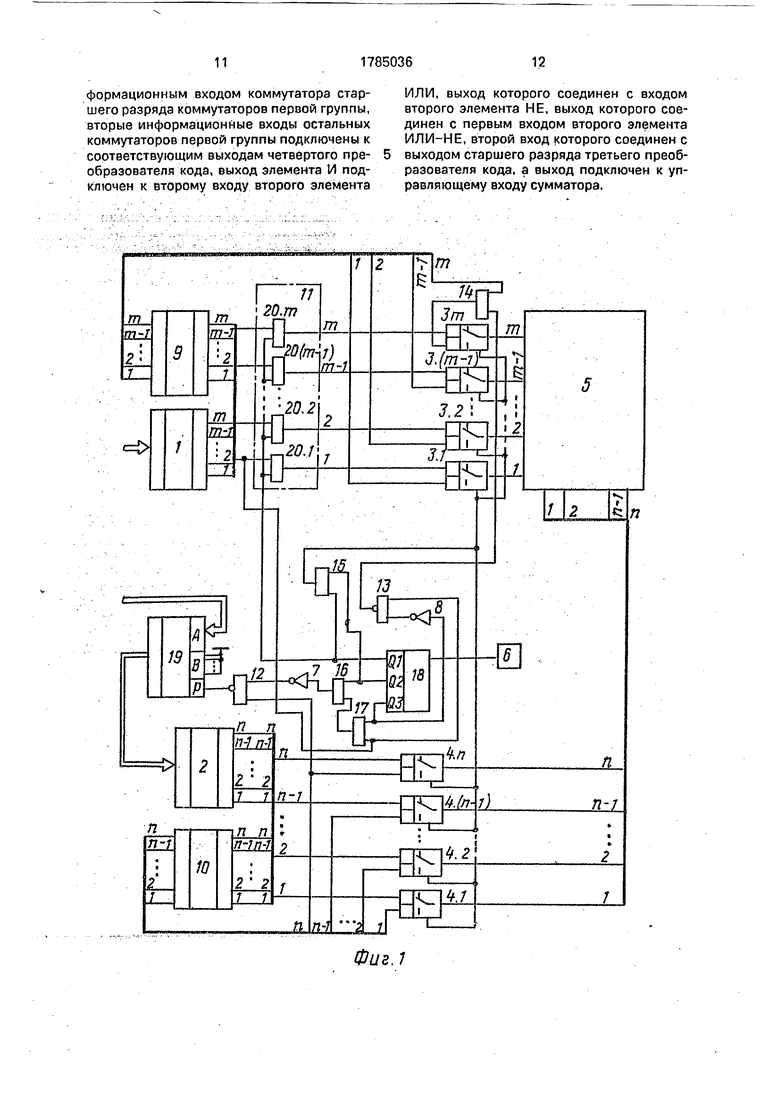

На фиг. 1 приведена функциональная схема устройства управления матричным

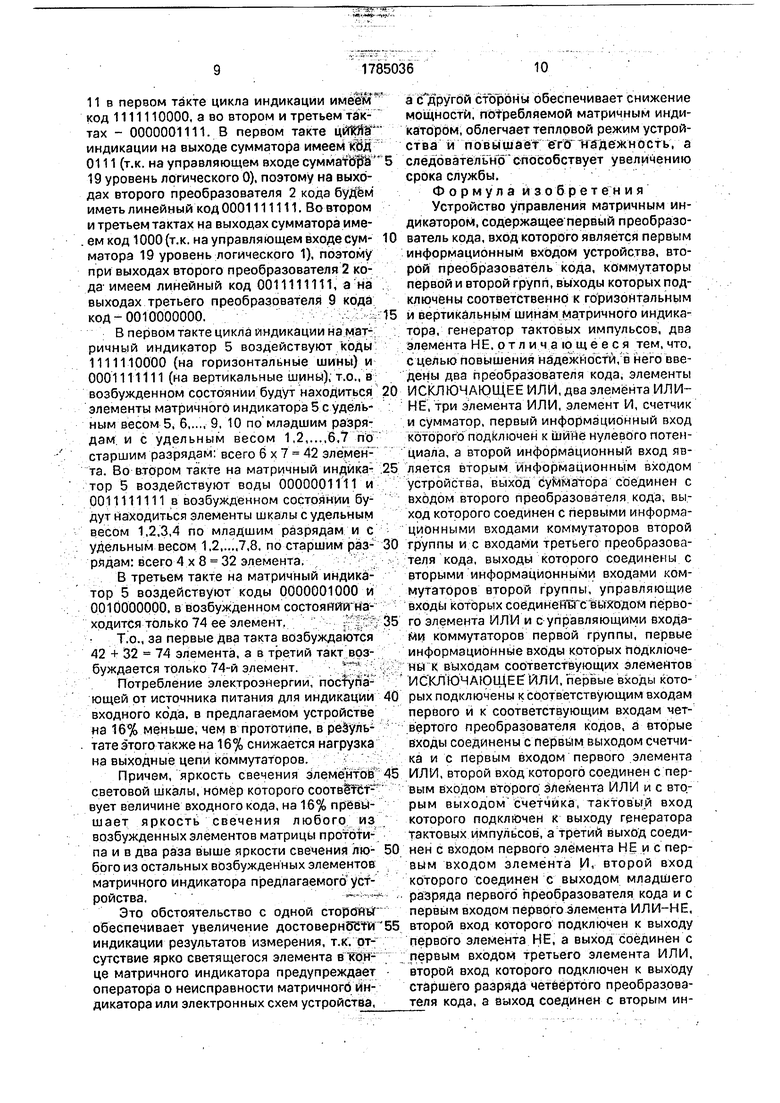

0 индикатором; на фиг. 2 - временные диаграммы работ генератора тактовых импульсов и трехразрядного кольцевого счетчика. Устройство управления матричным индикатором содержит (см. фиг. 1) первый пре5 образователь 1 кода младших разрядов в линейный код, второй преобразователь 2 кода старших разрядов в линейный код, коммутаторы 3 первой группы, коммутаторы 4 второй группы, матричный индикатор 5,

0 генератор 6 тактовых импульсов, первый и второй элементы НЕ 7, 8, третий и четвертый преобразователи 9,10 кода, группу элементов ИСКЛЮЧАЮЩЕЕ ИЛИ 11, первый и второй элементы ИЛИ-НЕ 12, 13, первый,

5 второй и третий элементы ИЛИ 14, 15, 16, элемент И 17, кольцевой счетчик 18 и сумматор 19.

Вход первого преобразователя 1 кода является первым информационным входом

0 устройства, а выходы соединены с соответствующими входами четвертого преобразователя 10 кода и первыми входами соответствующих элементов ИСКЛЮЧАЮЩЕЕ ИЛИ 11, вторые входы которых соеди5 нены с первым входом первого элемента ИЛИ 14 и первым выходом счетчика 18, а выходы с первыми информационными входами соответствующих коммутаторов 3 первой группы, выходы которых соединены с соответствующими горизонтальными шинами матричного индикатора 5, вертикальные шины которого подключены к выходам соответствующих коммутаторов 4 второй группы, первые информационные входы которых соединены с соответствующими выходами второго преобразователя 2 кода и с соответствующими входами третьего преобразователя 9 кода, выходы которого подключены к вторым информационным входам соответствующих коммутаторов 4 второй группы, управляющие входы которых соединены с управляющими входами коммутаторов 3 первой группы и выходом первого элемента ИЛИ 14, второй вход которого соединен с вторым выходом счетчи- ка 18 и первым входом второго элемента ИЛИ 15, выход которого соединен с входом второго элемента НЕ 8, а второй вход с выходом элемента И 17, первый вход которого соединен с третьим выходом счётчика 18 и первым элементом НЕ 7, а второй в ход с выходом младшего разряда первоп Птре- образователя 1 кода и с первым входомТтер- вого элемента ИЛИ-НЕ 12, второй вход которого соединен с выходом первого §Лемента НЕ 7, а выход с первым входомТреть- его элемента ИЛИ 16, второй вход которого соединен с выходом старшего разряда четвертого преобразователя 10 кода, а выходе вторым информационным входом коммута- тора старшего разряда комммутаторов 3 первой группы, вторые информационные входы остальных коммутаторов 3 первой группы подключены к соответствующим выходам четвертого преобразователя 10 кода, выход генератора 6 тактовых импульсов соединен с тактовым входом счетчика 18, первый информационный вход сумматора 19 подключен к шине нулевого потенциала, а второй информационный вход является вто- рым информационным входом устройства, выходы сумматора 19 соединены с соответствующими входами второго преобразователя 2 кода, выход второго элемента НЕ 8 соединен с первым входом второго элемен- та ИЛИ-НЕ 13, второй вход которого соединен с вторым информационным входом коммутатора старшего разряда коммутаторов 4 второй группы, а выход подключен к управляющему входу сумматора 19.

Первый и второй преобразовате лй 1, 2 кода являются преобразователями входного кода, поступающего на первый младших разрядов входного кода и второй старших разрядов входного кода информационные входы устройства в соответствующие линейные коды.

Третий и четвертый преобразователи 9, 10 кода преобразуют линейные коды старших и младших разрядов входного кода в

позиционные коды 1 из п и 1 из т, где п и т - число разряд6в с6отвётственно старших и младших разрядов линейных кодов.

Устройство управления матричным индикатором работает следующим образом,

На входные информационные шины устройства поступает подлежащий отображению сигнал в виде кодов младших и старших разрядов, причем код младшего разряда поступает на входы преобразователя 1 кода, а код старшего разряда поступает на вторые информационные входы сумматора 19.

С генератора 6 тактовых импульсов на вход трехразрядного кольцевого счетчика 18 поступает последовательность импульсов (фиг. 2 а). При этом на каждом из выходов счетчика 18 Q1, Q2 и Q3 на время, равное периоду колебаний генератора 6, через каждые два импульса генерируемой мм последовательности появится высокий уровень напряжения (состояние логической 1), что обеспечивает трехтактный цикл индикации устройством входного сигнала.

Учитываем также, что при работе усг- ройстваТагораютс я тольТб те ЗлёмёнтьГмат« Г XSf t,- ь.ч---

ричного индикатора 5, которые подключены к ее горизонтальным V вертикальным шинам, на которые подводятся возбуждающие напряжения одновременно. Возбуждающие напряжения к горизонтальным и вертикальным шинам матричного индикатора 5 поступают с выходов коммутаторов 3,4 первой и второй групп соответственно, если их вторые информационные входы находятся в состоянии логической 1 при низком уровне напряжения на их управляющих входах, или если их первые информационные входы находятся в состоянии логической 1 при высоком уровне напряжения на их управляющих входах.

В первом такте цикла индикации (фиг. 26) на управляющие входы коммутаторов 3, 4 с первого выхода счетчика 18 через первый элемент ИЛИ 14 поступает высокий уро- вень напряжения, обеспечивающий воздействие на элементы матричного индикатора 5 кодов, подводимых к первым информационным входам коммутаторов 3, 4.

Поскольку в этом такте на первые информационные входы коммутаторов 3 первой группы с вьгходов элементов ИСКЛЮЧАЮЩЕЕ ИЛИ 11 поступит инверсный линейный код младшего разряда индицируемого числа, а на первые информационные входы коммутаторов 4 второй группы с выходов второго преобразователя 2 кода поступит линейный код старшего разряда индицируемого числа, то на матричном индикаторе 5 загорятся все элементы полных старших разрядов индицируемого числа, имеющие удельный вес больше, чем удельный вес индицируемого числа младших разрядов.

Во втором такте цикла индикации (фиг, 2 в) на управляющие входы коммутаторов 3, 4 так же, как и в первом такте, через первый элемент ИЛИ 14 поступит высокий уровень напряжения, который обеспечит воздействие на элементы матричного индикатора 5 кодов, подводимых к первым информационным входам коммутаторов 3,4.

На первые информационные входы коммутаторов 3 с выходов элементов ИСКЛЮЧАЮЩЕЕ ИЛИ 11 поступит прямой линейный код младшего разряда индицируемого числа, т.к. на вторые входы элементов ИСКЛЮЧАЮЩЕЕ ИЛИ 11с первого выхода счетчика 18 поступает низкий уровень напряжения.

На первые информационные входы коммутаторов 4 с выходов второго преобразователя 2 кода поступит увеличенный на единицу линейный код старших разрядов индицируемого числа. Т.к. в этом такте на управляющий вход сумматора 19 с второго выхода счетчика 18 через второй элемент ИЛИ 15, второй элемент НЕ 8 и второй элемент ИЛИ-НЕ 13 поступит высокий уровень напряжения, благодаря чему на выходах сумматора 19 появится увеличенный на единицу код старших разрядов индицируемого числа, соответственно на выходах второго преобразователя 2 Кода и первых информационных входах коммутаторов 4 появится увеличенный на единицу линейный код старших разрядов индицируемого числа.

На матричном индикаторе 5 загорятся все элементы полных старших разрядов и неполного старшего разряда индицируемого числа, имеющие удельные веса меньше и равные удельному весу младших разрядов индицируемого числа.

В третьем такте цикла индикации (см. фиг. 2 г) на управляющих входа коммутаторов 3, 4 появится низкий уровень напряжения, обеспечивающий воздействие на элементы матричного индикатора 5, подводимых к вторым информационным входам коммутатором 3, 4.

Если в коде младших разрядов индицируемого числа отсутствуют единицы (т.е. ли- нейный код младших разрядов индицируемого числа имеет вид - 000...00), то на второй информационный вход коммутатора старшего разряда коммутаторов 3 с выхода первого элемента ИЛИ-НЕ 12 через третий элемент ИЛИ 16 поступает уровень логической 1, а на вторые информационные входы остальных коммутаторов 3 с выходов четвертого преобразователя 4 кода поступают уровни логического 0. Уровень логического 0, поступающий с выхода младшего разряда первого преобразователя 1 кода на второй вход элемента И 17, запрещает пе5 редачу уровня логической 1 с третьего выхода счетчика 18 на управляющий вход Сумматора 19. Поэтому код старших разрядов индицируемого числа передается через сумматор 19 на входы второго преобразова0 теля 2 кода без изменений, второй преобразователь 2 кода в свою очередь преобразует его в линейный код старших разрядов этого индицируемого числа. Этот код поступает на входы третьего преобразователя 9 кода.

5 На его выходе, удельный вес которого соответствует коду старшего разряда индицируемого числа, и соединенным с ним втором информационном входе коммутатора, из коммутаторов 4 второй группы появится

0 уровень логической 1, при этом на остальных вторых информационных входах коммутаторов 4 будет присутствовать уровень логического 0.

На матричном индикаторе остается го5 реть только один ее элемент, номер которого численно равен входному числу.

Если в коде младших разрядов индицируемого числа присутствует единица (еди- ницы), что только по одному из выходов

0 четвертого преобразователя 1 0 кода, удельный вес которого соответствует коду младшего разряда индицируемого числа и соединенным с ним первом втором информационном входе коммутатора из коммута5 торов 3 первой группы появится уровень логической 1. На второй вход элемента И 17 поступит уровень логической 1, разрешающий передачу высокого уровня напряжения с третьего выхода счетчика 18 на управляю0 щий вход сумматора 19. На выходе сумматора 19 появится код индицируемого числа старшего разряда, увеличенный на единицу, и соединенным с ним втором информационном входе коммутатора входе коммутатора

5 из коммутаторов 4 второй группы появится уровень логической 1. Т.е. в этом случае на матричном индикаторе 5 остается гореть только один ее элемент, номер которого численно равен входному числу.

0 Например, при индикации числа 74 (при максимальном индицируемом числе 100) на входные информационные шины устройства поступает код 0111.0100, причем, на вход первого преобразователя 1 кода подводит5 ся код 0100, а на второй информационный вход сумматора - код 0111. На выходах первого преобразователя 1 кода имеем линейный код 0000001111, на выходах четвертого преобразователя 10 кода -0000001000, а на

выходах элементов ИСКЛЮЧАЮЩЕЕ ИЛИ

11 в первом такте цикла индикации имеем код 1111110000, а во втором и третьем тактах - 0000001111. В первом такте цйШ индикации на выходе сумматора имеем код 0111 (т.к. на управляющем входе сумматора 19 уровень логического 0), поэтому на выходах второго преобразователя 2 кода будем иметь линейный код 0001111111. Во втором и третьем тактах на выходах сумматора имеем код 1000{т.к. на управляющем входе сум- матора 19 уровень логического 1), поэтому при выходах второго преобразователя 2 кода имеем линейный код 0011111111, а на выходах третьего преобразователя 9 кода код-0010000000.

В первом такте цикла индикации на матричный индикатор 5 воздействуют коды 1111110000 (на горизонтальные шины) и 0001111111 (на вертикальные шины), т.о., в возбужденном состоянии будут находиться элементы матричного индикатора 5 с удельным весом 5, 6,..., 9, 10 по младшим разрядам и с удельным весом 1,26,7 по

старшим разрядам: всего 6 х 7 42 элемента. Во втором такте на матричный индика- тор 5 воздействуют воды 0000001111 и 0011111111 в возбужденном состоянии будут находиться элементы шкалы с удельным весом 1,2,3,4 по младшим разрядам и с

удельным весом 1.27,8, по старшим раз-

рядам: всего 4 х 8 32 элемента.

В третьем такте на матричный индикатор 5 воздействуют коды 0000001000 и 0010000000. в возбужденном состоянШгна- ходится только 74 ее элемент. -

Т.о., за первые два такта возбуждаются 42 + 32 74 элемента, а в третий такт возбуждается только 74-й элемент.

Потребление электроэнергии, поступающей от источника питания для индикации входного кода, в предлагаемом устройстве на 16% меньше, чем в прототипе, в результате этого также на 16% снижается нагрузка на выходные цепи коммутаторов.

Причем, яркость свечения элементов световой шкалы, номер которого cooTeefcT вует величине входного кода, на 16% превышает яркость свечения любого из возбужденных элементов матрицы прототипа и в два раза выше яркости свечения лю- бого из остальных возбужденных элементов матричного индикатора предлагаемого устройства.Это обстоятельство с одной сторонъг обеспечивает увеличение достоверности индикации результатов измерения, т.к. отсутствие ярко светящегося элемента в конце матричного индикатора предупреждает оператора о неисправности матричного индикатора или электронных схем устройства,

а с другой стороны обеспечивает снижение мощности, потребляемой матричным индикатором, облегчает тепловой режим устройства и повышает его надежность, а следовательно способствует увеличению срока службы.

Формула изобретения Устройство управления матричным индикатором, содержащее первый преобразователь кода, вход которого является первым информационным входом устройства, второй преобразователь кода, коммутаторы первой и второй групп, выходы которых подключены соответственно к горизонтальным и вертикальным шинам матричного индикатора, генератор тактовых импульсов, два элемента НЕ. отличающееся тем, что, с целью повышения надежности, в него введены два преобразователя кода, элементы ИСКЛЮЧАЮЩЕЕ ИЛИ, два элемента ИЛИ- НЕ, три элемента ИЛИ, элемент И, счетчик и сумматор, первый информационный вход которого подключен к шине нулевого потенциала, а второй информационный вход является вторым информационным входом устройства, выход Сумматора соединен с входом второго преобразователя кода, выход которого соединен с первыми информационными входами коммутаторов второй группы и с входами третьего преобразователя кода, выходы которого соединены с вторыми информационными входами коммутаторов второй группы, управляющие входы которых соединен ьТс выходом первого элемента ИЛИ и с управляющими входами коммутаторов первой группы, первые информационные входы которых подключены к выходам соответствующих элементов ИСКЛЮЧАЮЩЕЕ ИЛИ. первые входы которых подключены к соответствующим входам первого и к соответствующим входам четвертого преобразователя кодов, а вторые входы соединены с первым выходом счетчика и с первым входом первого элемента ИЛИ, второй вход которого соединен с первым входом второго элемента ИЛИ и с вторым выходом счетчика, тактовый вход которого подключен к выходу генератора тактовых импульсов, а третий выход соединен с входом первого элемента НЕ и с первым входом элемента И, второй вход которого соединен с выходом младшего разряда первого преобразователя кода и с первым входом первого элемента ИЛИ-НЕ, второй вход которого подключен к выходу первого элемента НЕ, а выход соединен с первым входом третьего элемента ИЛИ, второй вход которого подключен к выходу старшего разряда четвертого преобразователя кода, а аыход соединен с вторым информационным входом коммутатора старшего разряда коммутаторов первой группы, вторые информационные входы остальных коммутаторов первой группы подключены к соответствующим выходам четвертого преобразователя кода, выход элемента И подключен к второму входу второго элемента

ИЛИ, выход которого соединен с входом второго элемента НЕ, выход которого соединен с первым входом второго элемента ИЛИ-НЕ, второй вход которого соединен с выходом старшего разряда третьего преобразователя кода, а выход подключен к управляющему входу сумматора.

Фиг. 7

г

т Lii.21

т

п-1 я-М

п-1 Cn-tf

tin Ш. mj

п CmJ

п

4-;

I

..J

9№

т-11 fwJ

Фиг I

| Авторское свидетельство СССР № 759965,кл | |||

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Устройство управления световой шкалой | 1981 |

|

SU1007031A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

Авторы

Даты

1992-12-30—Публикация

1990-07-26—Подача