ОБЛАСТЬ ТЕХНИКИ

Настоящее изобретение в целом относится с устройству для компенсации и линеаризации нелинейного IQ-модулятора (I - синфазный, Q - квадратурная фаза (Quadrature phase)).

УРОВЕНЬ ТЕХНИКИ

Архитектура прямого преобразования IQ на радиочастоту содержит модификацию данных базовой полосы, цифроаналоговое преобразование (ЦАП) и аналоговую IQ-квадратурную модуляцию для окончательного преобразования комплексного сигнала I+jQ на радиочастоту (РЧ). IQ-модулятору свойственны постоянная составляющая, амплитудная погрешность и фазовая погрешность. Обе ветви (I и Q) IQ-модулятора характеризуются этим разбалансом.

Для того чтобы обеспечить лучший энергетический потенциал, в архитектуре прямого преобразования IQ на РЧ для цифрового предыскажения (для компенсации неидентичностей усилителя мощности) предусматривается, что аналоговый IQ-модулятор возбуждается посредством более высокой входной мощностью. В результате элементы смесителей IQ-модулятора становятся по существу нелинейными выше линейного амплитудного и фазового разбаланса.

В настоящее время не существует конкретного решения, как линеаризовать IQ-модулятор. Отсутствие линеаризатора приводит к дополнительной нежелательной интермодуляции сигнала вследствие использования в режиме высокой мощности IQ-модулятора. Существует потребность в противодействии нелинейностям для того, чтобы удовлетворять техническим условиями и в то же время поддерживать хороший потенциал кид по мощности.

СУЩНОСТЬ ИЗОБРЕТЕНИЯ

Целью настоящего изобретения является создание устройства ввода предыскажений IQ-модулятора для компенсации этих погрешностей.

Дополнительной целью является создание базовой станции, включающей такое устройство ввода предыскажений IQ-модулятора.

Эти цели достигаются в соответствии с прилагаемой формулой изобретения.

Вкратце, настоящее изобретение решает эту задачу посредством использования отдельных итеративно обновляемых цифровых фильтров для компенсации амплитудных погрешностей и погрешностей интермодуляции и итеративно обновляемых компенсаторов сдвига.

КРАТКОЕ ОПИСАНИЕ ЧЕРТЕЖЕЙ

Изобретение, вместе с его другими целями и преимуществами, поясняется в последующем описании, иллюстрируемом чертежами, на которых представлено следующее:

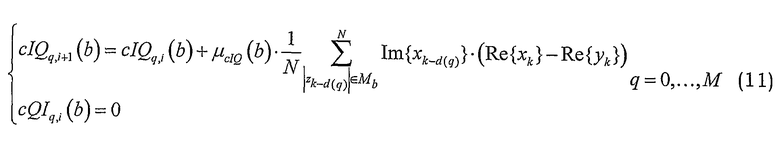

Фиг.1 -блок-схема, иллюстрирующая принципы IQ-модулятора;

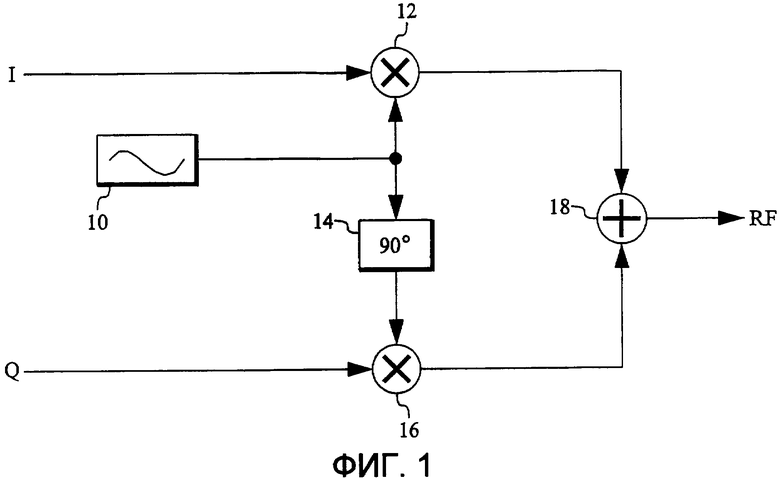

Фиг.2 - модель IQ-модулятора, иллюстрирующая различные источники погрешностей;

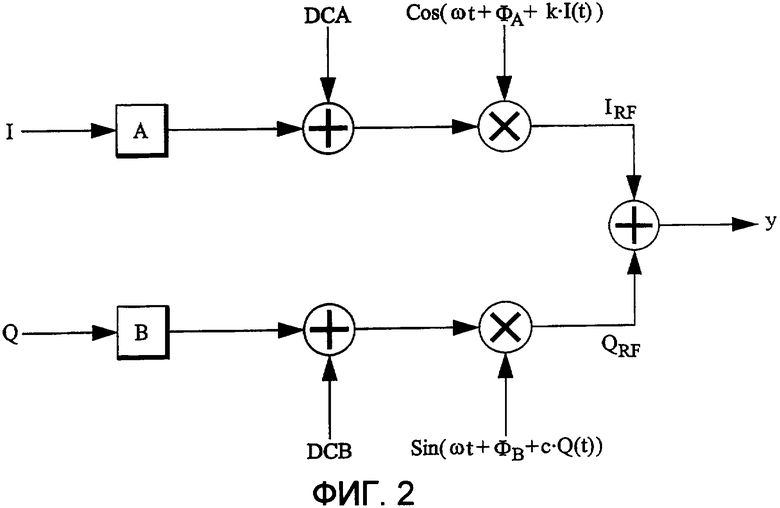

Фиг.3 - блок-схема первого варианта осуществления устройства предыскажений IQ-модулятора в соответствии с настоящим изобретением;

Фиг.4 - блок-схема первого варианта осуществления базовой станции, содержащей устройство предыскажений IQ-модулятора в соответствии с настоящим изобретением;

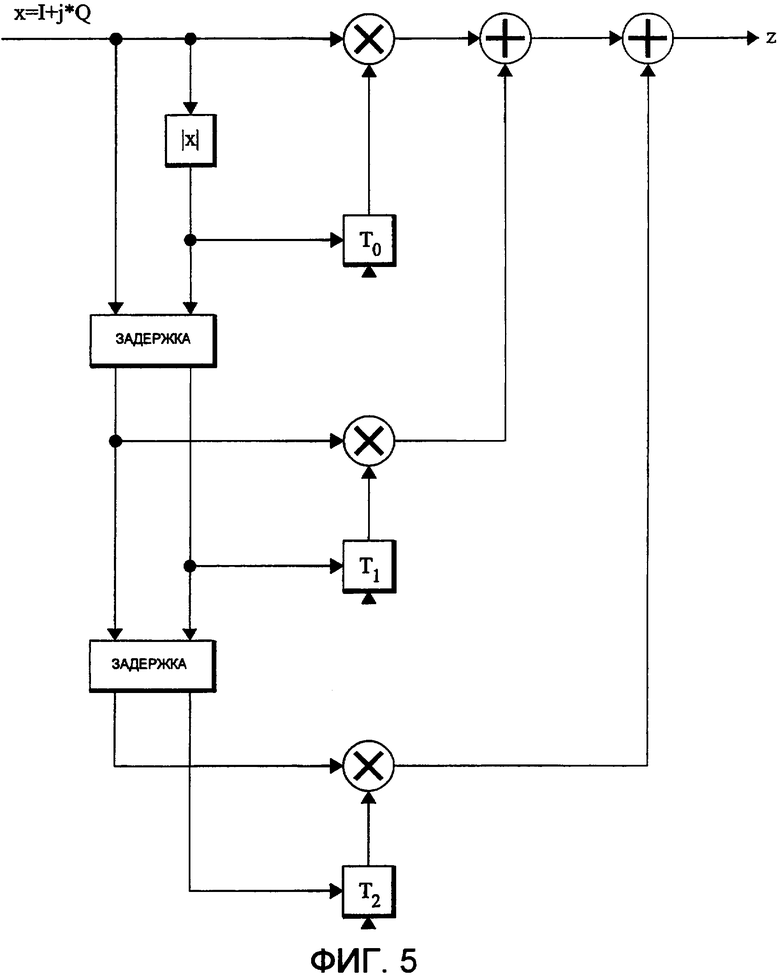

Фиг.5 - блок-схема варианта осуществления устройства предыскажений усилителя мощности, пригодного для использования во втором варианте осуществления базовой станции в соответствии с настоящим изобретением;

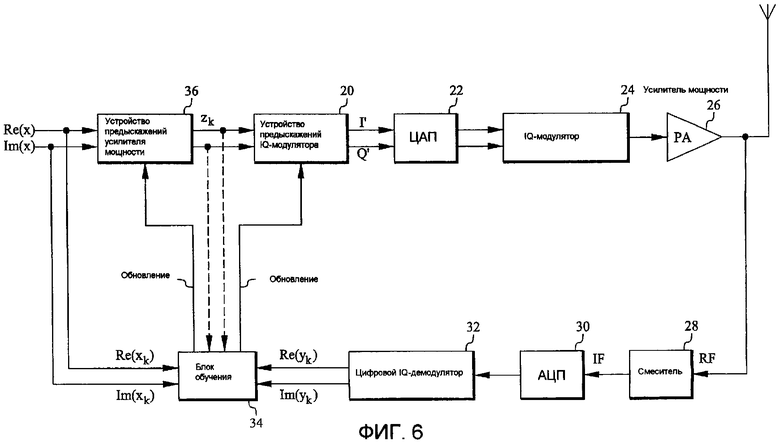

Фиг.6 - блок-схема второго варианта осуществления базовой станции, содержащей устройство предыскажений IQ-модулятора в соответствии с настоящим изобретением;

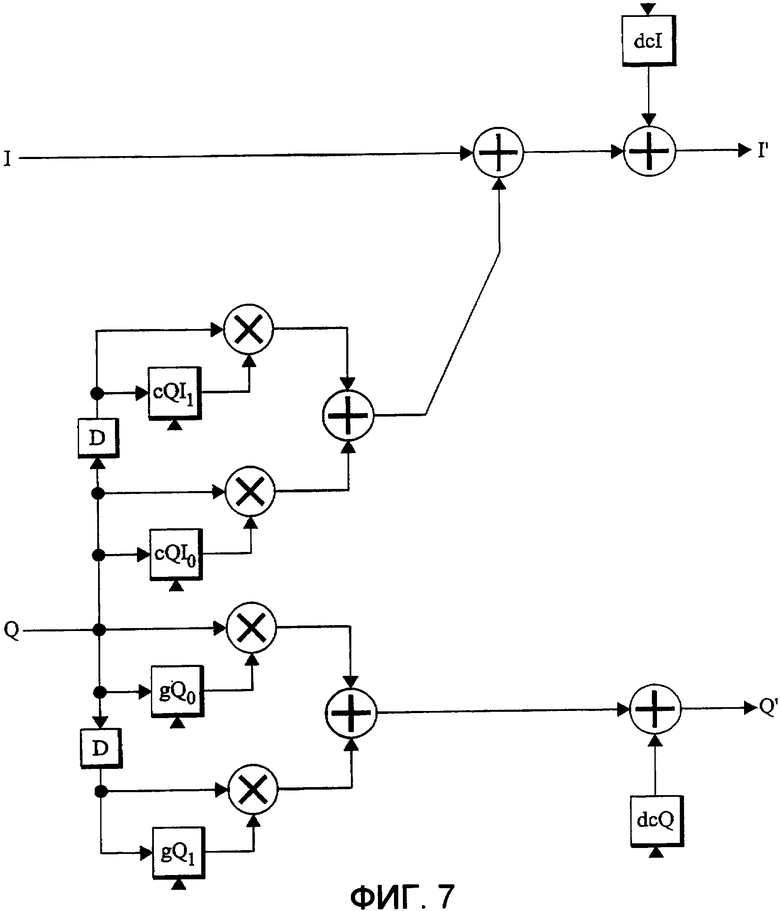

Фиг.7 - блок-схема второго варианта осуществления устройства предыскажений IQ-модулятора в соответствии с настоящим изобретением; и

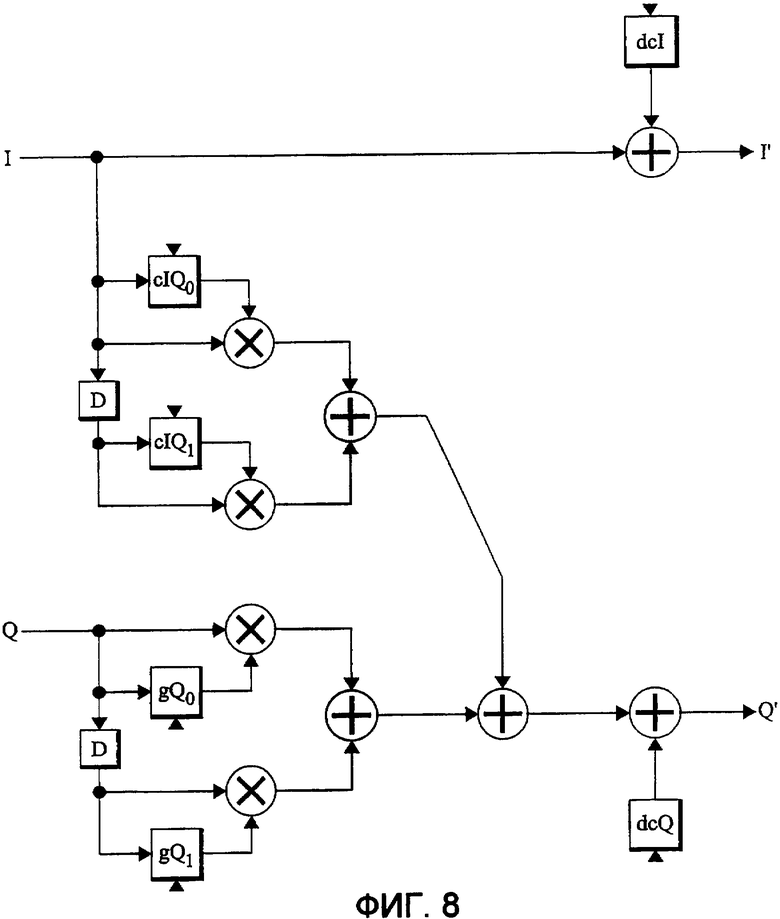

Фиг.8 - блок-схема третьего варианта осуществления устройства предыскажений IQ-модулятора в соответствии с настоящим изобретением.

ПОДРОБНОЕ ОПИСАНИЕ

Последующее описание концентрируется только на элементах, которые являются значимыми для объяснения настоящего изобретения. Другие элементы, такие как фильтры, кодеры сигнала, кодеры каналов, и т.д., которые являются очевидными для специалиста в данной области техники, опущены в целях наглядности чертежей.

Фиг.1 - блок-схема аналогового IQ-модулятора. IQ-модулятор содержит гетеродин 10, выходной сигнал которого умножается на I-компоненту сигнала, которая должна быть преобразована на радиочастоту в смесителе 12. Выходной сигнал гетеродина 10 также подается на 90° фазовращатель 14 и затем на второй смеситель 16 для преобразования Q-компоненты входного сигнала на радиочастоту. Преобразованные сигналы со смесителей 12, 16 затем объединяются в сумматоре 18 для формирования требуемого радиочастотного сигнала.

Поскольку два сигнала гетеродина сдвинуты по фазе на 90°, две компоненты могут считаться ортогональными. Однако, если существует ошибка в фазах смешивающихся сигналов гетеродина, а также различие в коэффициенте усиления, то I и Q-ветви более не являются ортогональными. Это будет приводить к утечке сигналов между ветвями.

В дополнение к чистому нарушению баланса ортогональности каждая ветвь имеет нелинейные эффекты. Считается, что эти эффекты обусловлены фазовой модуляцией смешивающихся сигналов с гетеродина.

На фиг.2 показана примерная модель IQ-модулятора, иллюстрирующая различные источники погрешностей. В этой модели I-компонента усиливается с коэффициентом усиления A, объединяется со смещением постоянной составляющей и умножается на сигнал смесителя cos(ω∙t+ΦA+k∙I(t)) для создания трансформированного или преобразованного с повышением частоты радиочастотного сигнала IРЧ. Преобразование с повышением частоты Q-компоненты моделируется сходным образом. Математически модель может быть выражена как:

Преобразованные с повышением частоты сигналы затем комбинируются для создания радиочастотного сигнала:

По существу IQ-модулятор рассматривается как имеющий два входных порта, каждый из которых имеет собственную нелинейность. Так как существует две отдельные ветви, то для этого необходимо иметь два отдельных нелинейных компенсатора. На фиг.2 каждый сигнал гетеродина имеет фазовую модуляцию, которая дает частотную интермодуляцию в сигналах I и Q (смещения фазы, которые включают коэффициенты k и с).

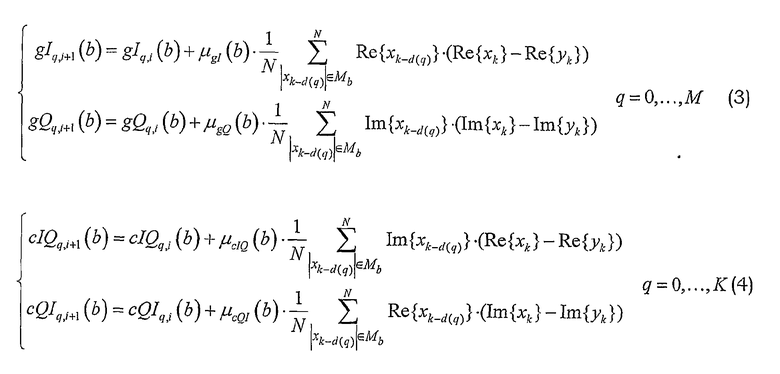

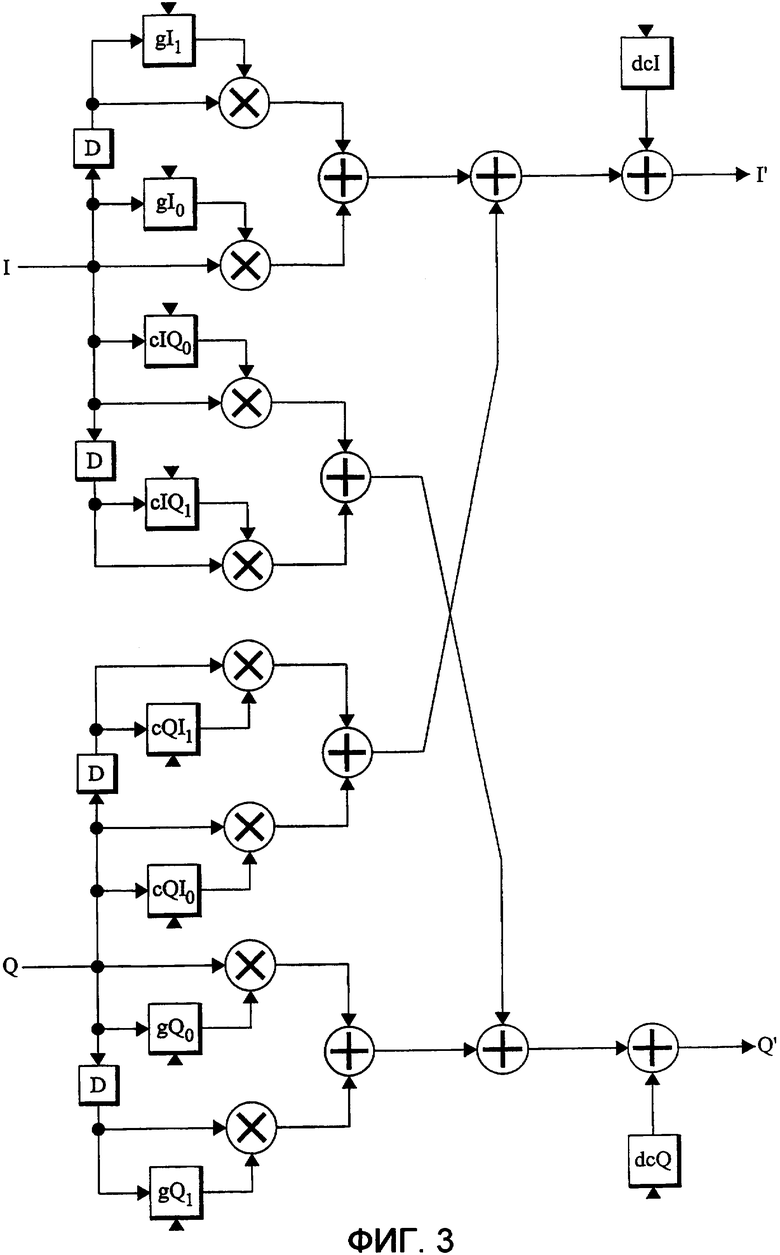

Как показано ниже, погрешности IQ-модулятора могут быть нейтрализованы при помощи цифрового предыскажения IQ-сигнала в базовой полосе с использованием итеративно обновляемых структур фильтров, в которых отводы фильтров зависят от величин компонент I и Q. Эти структуры фильтров могут, например, обновляться в соответствии с алгоритмом минимальных среднеквадратичных отклонений, как:

Здесь уравнение (3) представляет отводы фильтров gIQ, gQq для фильтрации компонент I и Q для компенсации амплитудных погрешностей, создаваемых IQ-модулятором без учета интермодуляционной погрешности. Интермодуляция обрабатывается отводами фильтров gIQq, gQIq в уравнении (4), а ошибки смещения обрабатываются посредством dcI, dcQ в уравнении (5).

В уравнениях (3)-(5) xk и yk представляют входной сигнал устройства предыскажений IQ-модулятора (опорный сигнал) и преобразованный с понижением частоты выходной сигнал IQ-модулятора соответственно. Эти сигналы дополнительно иллюстрируются на фиг.4. Отметим, что эти сигналы рассматриваются как комплексные, т.е. они имеют действительную и мнимую часть (соответственно I и Q-компонентам). Сигналы xk и yk также предполагаются синхронизированными по времени и по фазе.

Кроме того, в уравнениях (3)-(5)

q - индекс, представляющий задержку d(q),

различные μ - постоянные контура,

b устанавливает элемент отвода фильтра,

i - индекс итерации,

N - количество входных выборок опорного сигнала x в пакете выборок, которые имеют амплитуду, попадающую в интервал Mb вблизи центральной амплитуды элемента b,

M, К представляют количество отводов фильтра+1.

В уравнениях (3)-(4) используется различное количество (M+l and K+1 соответственно) отводов фильтров. Тем не менее, возможно использовать одинаковое количество отводов фильтра для gIQ, gQq и gIQq, gQIq. Более того, также возможно использовать различные интервалы Mb для двух случаев. Упрощение может быть получено посредством допущения, что каждая (или по меньшей мере одна) из постоянных контура не зависит от элемента b.

Более того, в крайнем случае, где b покрывает целый диапазон I и Q, отводы фильтра будут независимы от текущих значений входных сигналов (например, gIq(b) не будет зависеть от b). Как указано индексом q, задержка d(q) зависит от q. В простейшем варианте осуществления d(q) просто установлено на q. Другие варианты осуществления могут использовать значения, кратные q.

Фиг.3 - блок-схема первого варианта осуществления блока предыскажений IQ-модулятора в соответствии с настоящим изобретением на основе уравнений (3)-(5). В этом варианте осуществления использовано только 2 отвода фильтра (M=l) в целях наглядности чертежей. Тем не менее, принимается во внимание, что возможно большее количество отводов фильтра в практическом варианте осуществления. I-компонента умножается на отвод gI0 фильтра, значение которого зависит от величины самой I-компоненты. I-компонента также пересылается на элемент D задержки, и задержанный сигнал умножается при помощи отвода gI1 фильтра, значение которого зависит от значения самой задержанной I-компоненты. Умноженные сигналы затем суммируются. I-компонента обрабатывается сходным способом посредством отводов фильтра gIQ0, gIQ1. Однако результирующий сигнал не сохраняется в I-ветви. Вместо этого он перекрестно ответвляется в Q-ветвь, где он добавляется к Q-компоненте после того, как последняя отфильтрована отводами фильтра gQ0, gQ1. Сходным образом, перекрестно ответвленный сигнал из Q-ветви суммируется с отфильтрованной I-компонентой. В заключение, смещения dcI, dcQ добавляются к I и Q-ветвям соответственно.

На фиг.4 представлена блок-схема первого варианта осуществления базовой станции, содержащей блок предыскажений IQ-модулятора в соответствии с настоящим изобретением. Устройство 20 предыскажений IQ-модулятора подсоединено к ЦАП 22. Аналоговый предыскаженный IQ-вектор направляется на IQ-модулятор 24, и преобразованный с повышением частоты радиочастотный сигнал усиливается усилителем 26 мощности для передачи антенной. Выход IQ-модулятора 24 также соединен со смесителем 28, который преобразует с понижением частоты радиочастотный сигнал на промежуточную частоту (ПЧ). ПЧ-сигнал оцифровывается в аналого-цифровом преобразователе (АЦП) 30. Оцифрованный ПЧ-сигнал дополнительно преобразуется с понижением частоты и преобразуется в IQ-сигнал посредством IQ-демодулятора 32. IQ-демодулятор 32 подключен к блоку 34 обучения устройства предыскажений для определения текущего предыскажения. Комплексные входные сигналы xk и yk, подаваемые в блок 34 обучения, показаны на фиг.4. После определения предыскажения, например, в соответствии с процедурой, описанной уравнениями (3)-(5), блок обучения направляет сигналы отводов фильтра в устройство 20 предыскажений. Отводы фильтров могут обновляться на каждый период выборки или с более протяженными интервалами. Обновление отводов фильтров указано несвязанными стрелками на отводах на фиг.3.

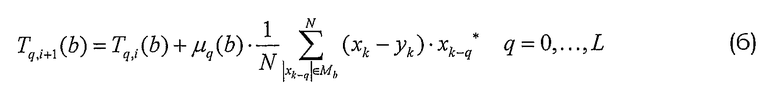

На фиг.4 отмечено, что имеется усилитель 26 мощности. Поскольку усилитель мощности также является нелинейным компонентом, желательно компенсировать погрешности, создаваемые усилителем, посредством включения устройства предыскажений усилителя мощности. Любое подходящее устройство ввода предыскажений может быть использовано для этих целей. Тем не менее, такое устройство предыскажений также может быть основано на итеративных методах, таких как алгоритмы LMS. Например, оно может использовать комплексные отводы фильтров на основе следующих уравнений:

где "*" обозначает комплексное сопряжение.

Хотя L используется для представления количества отводов фильтра (которое равно L+1), понятно, что количество отводов может быть тем же, что и в одном из равенств (3)-(4) (или в обоих равенствах, если M=K). Кроме того, не требуется, чтобы интервал Мb был равным интервалу для устройства предыскажений IQ-модулятора. Упрощение может быть получено посредством допущения, что каждая (или по меньшей мере одна) из постоянных контура не зависит от элемента b.

На фиг.5 показана блок-схема варианта осуществления устройства ввода предыскажений усилителя мощности, пригодного для использования во втором варианте осуществления базовой станции в соответствии с настоящим изобретением. Это устройство предыскажений усилителя мощности основано на отводах фильтра, определенных, например, в соответствие с уравнением (6). В этом примере фильтр включает в себя 3 отвода фильтра. Комплексный входной сигнал x=I+jQ умножается на первый отвод T0 фильтра, величина которого определяется амплитудой |x| входного сигнала. Входной сигнал x и его амплитуда |x| задерживаются, и задержанный сигнал умножается на отвод T1 фильтра, значение которого определяется задержанной амплитудой. После дополнительной задержки выполняется другое умножение на T1. После этого умноженные сигналы суммируются друг с другом для формирования сигнала z, который предыскажается для компенсации погрешностей, создаваемых усилителем мощности. Обновление отводов фильтров указано несвязанными стрелками по фиг.5, обозначенными на отводах на фиг.3.

На фиг.6 показана блок-схема второго варианта осуществления базовой станции, содержащей устройство предыскажений IQ-модулятора в соответствии с настоящим изобретением. Этот вариант осуществления объединяет устройство 20 предыскажений IQ-модулятора с устройством 36 предыскажений усилителя мощности в один и той же контур управления. Устройство предыскажений усилителя мощности, например, может быть реализовано, как на фиг.5. Отметим, что в этом случае радиочастотный сигнал, который преобразован с понижением частоты для блока 34 обучения, берется с выхода усилителя мощности, вместо выхода IQ-модулятора. Более того, блок 34 обучения теперь обновляет оба устройства предыскажений.

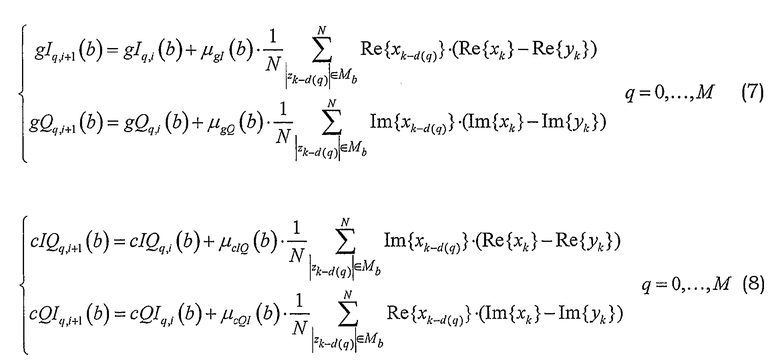

В одном варианте осуществления блок 34 обучения может обновлять различные отводы фильтров в соответствии с уравнениями (3)-(6). Однако обнаружено, что объединенный контур управления, показанный на фиг.6, работает даже лучше, если уравнения (3)-(4) несколько изменены и представлены в виде:

Различием является то, что выходной сигнал z с устройства 36 предыскажений усилителя мощности, вместо входного сигнала x, используется для определения, включена ли выборка в интервал Mb или нет. В фактическом суммировании, однако, входной сигнал x по-прежнему используется.

Одной из причин для такого изменения является то, что оно позволяет более эффективно обрабатывать нелинейности IQ-модулятора лучше, чем исходные уравнения (3)-(4).

На фиг.6 эта модификация обозначена пунктирными линиями к блоку обучения.

Для предотвращения перекомпенсации и конкуренции между алгоритмами, один из параметров усиления (gI и gQ) и один из параметров перекрестной связи (cIQ or cQI) могут быть установлены как константы. Это разделяет функции между устройством предыскажений усилителя мощности и устройством предыскажений IQ-модулятора. IQ-компенсация становится ведомой и компенсирует только погрешности в разнице между I-сигналом и Q-сигналом. Устройство предыскажений усилителя мощности будет иметь основную функцию по компенсации усиления, фазы и линеаризации.

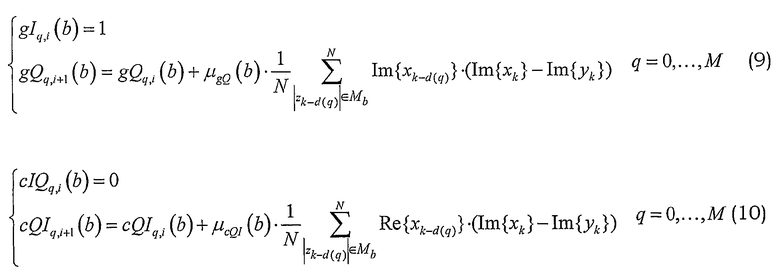

На фиг.7 показана блок-схема второго варианта осуществления устройства предыскажений IQ-модулятора в соответствии с настоящим изобретением. Этот упрощенный вариант осуществления может быть использован в базовой станции по фиг.6 вместо варианта осуществления по фиг.3. Для устройства предыскажений IQ-модулятора по фиг.7 уравнения (3)-(4) сводятся к:

Однако следует отметить, что поскольку не существует существенной разницы между I и Q-компонентами IQ-сигнала, роли I и Q могут быть реверсированы на фиг.7 и уравнениях (9)-(10).

На фиг.8 показана блок-схема третьего варианта осуществления устройства предыскажений IQ-модулятора в соответствии с настоящим изобретением. Этот вариант осуществления отличается от варианта осуществления по фиг.7 тем, что имеет перекрестно подключенный цифровой фильтр от I-ветви к Q-ветви вместо подключения от Q-ветви к I-ветви. В этом варианте осуществления уравнение (10) заменяется на:

Устройство предыскажений IQ-модулятора в соответствии с настоящим изобретением может быть реализовано как FPGA (программируемая вентильная матрица) или ASIC (специализированная интегральная схема). Другой возможностью является использование микропроцессора или сочетания микропроцессора и процессора обработки сигналов и соответствующего программного обеспечения.

Фильтры также могут быть выполнены симметричными с положительной и отрицательной задержками.

Вышеописанное изобретение имеет следующие преимущества.

- Не требуется моделирование системы.

- Необходимые вычисления являются простыми.

- Реализация является экономичной.

- Компенсация погрешностей IQ-модулятора возможна для сигналов с большой шириной полосы.

Специалисту в данной области техники будет понятно, что могут быть сделаны различные модификации и изменения в настоящем изобретении без отступления от его объема, который определен прилагаемой формулой изобретения.

Изобретение относится к устройству для компенсации погрешностей и линеаризации нелинейного IQ-модулятора. Достигаемый технический результат - компенсация амплитудной и фазовой погрешностей. Устройство предыскажений IQ-модулятора включает в себя два цифровых фильтра, для компенсации создаваемых IQ-модулятором погрешностей амплитуды и фильтрации интермодуляции от квадратурной к синфазной компоненте сигнала, первый компенсатор сдвига для компенсации погрешности сдвига синфазной компоненты сигнала и второй компенсатора сдвига для компенсации погрешности сдвига квадратурной компоненты сигнала, два итеративно обновляемых цифровых фильтра (gQ0, gQ1, gI0, gI1) для фильтрации каждой ветви IQ-сигнала для компенсации создаваемых IQ-модулятором погрешностей амплитуды в каждой ветви. 4 н. и 8 з.п. ф-лы, 8 ил.

1. Устройство предыскажений синфазного квадратурного модулятора (IQ-модулятора), включающее в себя: первый цифровой фильтр, имеющий первый и второй итеративно обновляемые отводы (gQ0, gQ1) фильтра для фильтрации квадратурной компоненты сигнала, для компенсации создаваемых IQ-модулятором погрешностей амплитуды; второй цифровой фильтр, имеющий первый и второй итеративно обновляемые отводы (cQI0, cQI1) фильтра для фильтрации интермодуляции от квадратурной к синфазной компоненте сигнала, перекрестно соединенный от одной из ветвей к другой ветви, для компенсации создаваемой IQ-модулятором интермодуляции между ветвями; и первый компенсатор (dcI) сдвига для компенсации погрешности сдвига синфазной компоненты сигнала и второй компенсатор (dcQ) сдвига для компенсации погрешности сдвига квадратурной компоненты сигнала, причем выходные значения первого и второго компенсатора итеративно вычисляются на основе синфазной компоненты и квадратурной компоненты сигнала соответственно для компенсации погрешностей сдвига, создаваемых IQ-модулятором.

2. Устройство предыскажений по п.1, включающее в себя два итеративно обновляемых цифровых фильтра (gQ0, gQ1, gI0, gI1) для фильтрации каждой ветви IQ-сигнала для компенсации создаваемых IQ-модулятором погрешностей амплитуды в каждой ветви.

3. Устройство предыскажений по п.1 или 2, включающее в себя два итеративно обновляемых цифровых фильтра (cQI0, cQI1, cIQ0, cIQ1), перекрестно соединенных от одной из ветвей к другой ветви, для фильтрации обеих компонент IQ-сигнала для компенсации создаваемой IQ-модулятором интермодуляции между ветвями.

4. Устройство предыскажений по п.1 или 2, в котором каждый отвод каждого фильтра реализован как таблица поиска, значение отвода фильтра которой зависит от значения компоненты сигнала, которая на него умножается.

5. Объединенное устройство предыскажений усилителя мощности и IQ-модулятора, включающее в себя устройство предыскажений усилителя мощности, соединенное с устройством предыскажений IQ-модулятора по п.1.

6. Объединенное устройство предыскажений по п.5, в котором устройство предыскажений усилителя мощности включает в себя итеративно обновляемые комплексные фильтры (Tq), каждый из отводов каждого из которых реализован как таблица поиска, при этом каждое значение отвода фильтра зависит от амплитуды компоненты сигнала, которая на него умножается.

7. Базовая станция, содержащая устройство предыскажений IQ-модулятора, причем упомянутое устройство предыскажений IQ-модулятора включает в себя: первый итеративно обновляемый цифровой фильтр, имеющий первый и второй отводы (gQ0, gQ1) фильтра для фильтрации квадратурной компоненты сигнала, для компенсации создаваемых IQ-модулятором погрешностей амплитуды; второй итеративно обновляемый цифровой фильтр, имеющий первый и второй отводы (cQI0, cQI1) фильтра для фильтрации интермодуляции от квадратурной к синфазной компоненте сигнала, перекрестно соединенный от одной из ветвей к другой ветви, для компенсации создаваемой IQ-модулятором интермодуляции между ветвями; и первый компенсатор (dcI) сдвига для компенсации погрешности сдвига синфазной компоненты сигнала и второй компенсатор (dcQ) сдвига для компенсации погрешности сдвига квадратурной компоненты сигнала, причем выходные значения первого и второго компенсатора итеративно вычисляются на основе синфазной компоненты и квадратурной компоненты сигнала соответственно для компенсации погрешностей сдвига, создаваемых IQ-модулятором; цифроаналоговый преобразователь (ЦАП) для преобразования предыскаженного цифрового IQ-сигнала в предыскаженный аналоговый IQ-сигнал; IQ-модулятор для преобразования аналогового предыскаженного IQ-сигнала с повышением частоты; усилитель мощности для усиления радиочастотного сигнала; антенну для передачи радиочастотного сигнала, смеситель, соединенный с выходом IQ-модулятора, для преобразования радиочастотного сигнала с понижением частоты на промежуточную частоту (ПЧ); аналого-цифровой преобразователь (АЦП) для оцифровывания ПЧ-сигнала; IQ-демодулятор для преобразования ПЧ-сигнала с понижением частоты и преобразования его в IQ-сигнал; и блок определения значения предыскажения для определения текущего предыскажения, направляющий сигналы отводов фильтров в упомянутое устройство предыскажений IQ-модулятора.

8. Базовая станция по п.7, включающая в себя два итеративно обновляемых цифровых фильтра (gQ0, gQ1, gI0, gI1) для фильтрации каждой ветви IQ-сигнала для компенсации создаваемых IQ-модулятором погрешностей амплитуды в каждой ветви.

9. Базовая станция по п.7 или 8, включающая в себя два итеративно обновляемых цифровых фильтра (cQI0, cQI1, cIQ0, cIQ1), перекрестно соединенных от одной из ветвей к другой ветви, для фильтрации обеих компонент IQ-сигнала для компенсации создаваемой IQ-модулятором интермодуляции между ветвями.

10. Базовая станция по п.7 или 8, в которой каждый отвод каждого фильтра реализован как таблица поиска, значение отвода фильтра которой зависит от значения компоненты сигнала, которая на него умножается.

11. Базовая станция, включающая в себя объединенное устройство предыскажений усилителя мощности и IQ-модулятора, причем упомянутое объединенное устройство предыскажений включает в себя устройство предыскажений усилителя мощности, соединенное с устройством предыскажений IQ-модулятора по п.5.

12. Базовая станция по п.11, в которой устройство предыскажений усилителя мощности включает в себя итеративно обновляемые комплексные фильтры (Tq), каждый из отводов каждого из которых реализован как таблица поиска, при этом каждое значение отвода фильтра зависит от амплитуды компоненты сигнала, которая на него умножается.

| Дж.Спилкер | |||

| Цифровая спутниковая связь | |||

| Перевод с английского под редакцией В.В.Маркова | |||

| - М.: Связь | |||

| Дверной замок, автоматически запирающийся на ригель, удерживаемый в крайних своих положениях помощью серии парных, симметрично расположенных цугальт | 1914 |

|

SU1979A1 |

| RU 2003104983/09, 20.06.2004 | |||

| УСИЛИТЕЛЬ МОЩНОСТИ, ОБЪЕДИНЕННЫЙ С КОНТРОЛЛЕРОМ АМПЛИТУДНОЙ МОДУЛЯЦИИ И КОНТРОЛЛЕРОМ ФАЗОВОЙ МОДУЛЯЦИИ | 1994 |

|

RU2121755C1 |

| УСТРОЙСТВО И СПОСОБ ЛИНЕАРИЗАЦИИ УСИЛИТЕЛЯ МОЩНОСТИ В СИСТЕМЕ ПОДВИЖНОЙ РАДИОСВЯЗИ | 1999 |

|

RU2172552C1 |

| Бесколесный шариковый ход для железнодорожных вагонов | 1917 |

|

SU97A1 |

| US 3739277, 12.07.1973. | |||

Авторы

Даты

2010-01-27—Публикация

2005-02-24—Подача