Родственная заявка

Настоящая заявка заявляет преимущество предварительной заявки, озаглавленной «Fast In-phase and Quadrature imbalance calibration», поданной 6 июня 2006 г., порядковый номер 60/811 579.

Уровень техники

Область техники, к которой относится изобретение

Варианты осуществления изобретения относятся к области связи, и более конкретно к калибровке синфазно-квадратурного дисбаланса.

Описание предшествующего уровня техники

Радиочастотные (РЧ) приемники или передатчики, применяющие архитектуры прямого преобразования, генерируют синфазные и квадратурные (I-Q) аналоговые сигналы. Эти сигналы обычно имеют искажения, которые ограничивают рабочие характеристики демодулятора или модулятора. Эти искажения, называемые квадратурными ошибками, вызываются дисбалансом коэффициента усиления и фазы между I-Q составляющими сигнала. Дисбаланс I-Q сигналов может наводить зеркальную частоту и смещение постоянного тока (DC), которые создают помехи процессу демодуляции или модуляции. Для корректировки дисбаланса I-Q сигналов необходимо калибровать подсистему связи. Существующие способы калибровки обычно используют итеративные подходы. Эти методы корректируют ошибку фаз, затем ошибку коэффициента усиления многократно при итеративных развертках.

Существующие методы калибровки имеют ряд недостатков. Во-первых, итеративный подход требует многочисленных проходов обработки, приводя к длительному времени обработки. Это длительное время обработки может вызывать перерыв связи связного приемника или передатчика. Для услуг связи, требующих постоянных скоростей передачи битов, таких как телефония или видео в реальном времени, перерыв связи может вызывать нежелательные рабочие характеристики. Во-вторых, итеративная сущность метода не является точной и достигает плохих результатов, приводя к ухудшенным рабочим характеристикам.

Краткое описание чертежей

Варианты осуществления изобретения могут быть лучше поняты в результате ссылки на последующее описание и прилагаемые чертежи, которые используются для иллюстрации вариантов осуществления изобретения. На чертежах:

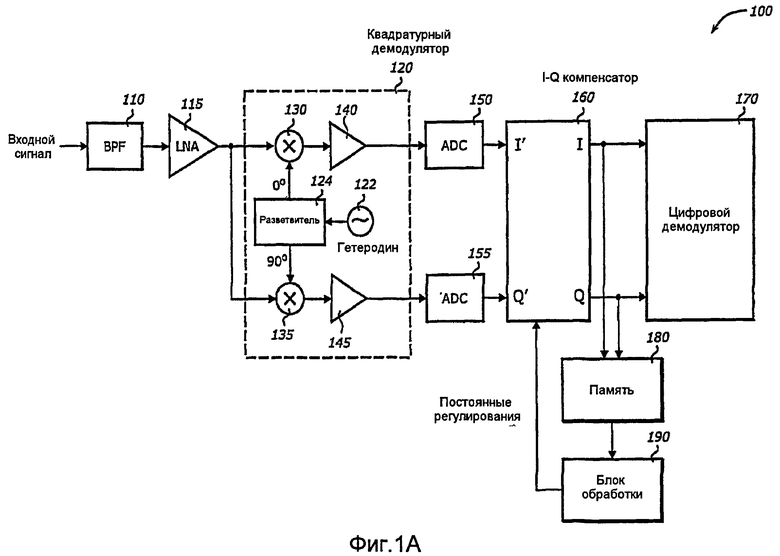

Фиг.1А представляет собой диаграмму, иллюстрирующую подсистему приемника согласно одному варианту осуществления изобретения.

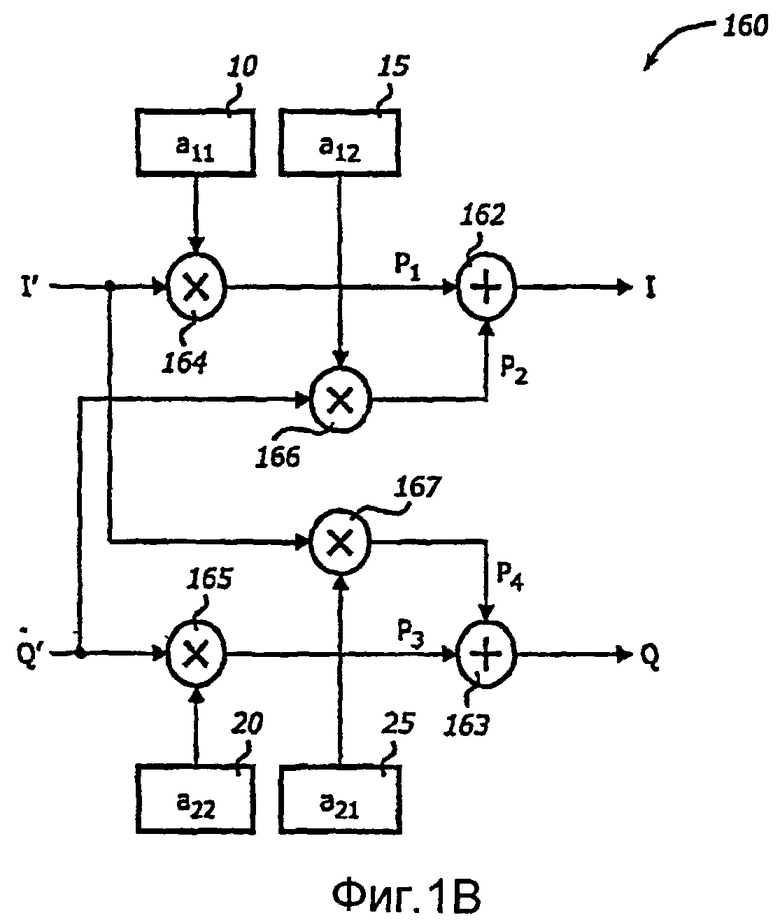

Фиг.1В представляет собой диаграмму, иллюстрирующую компенсатор для подсистемы приемника согласно одному варианту осуществления изобретения.

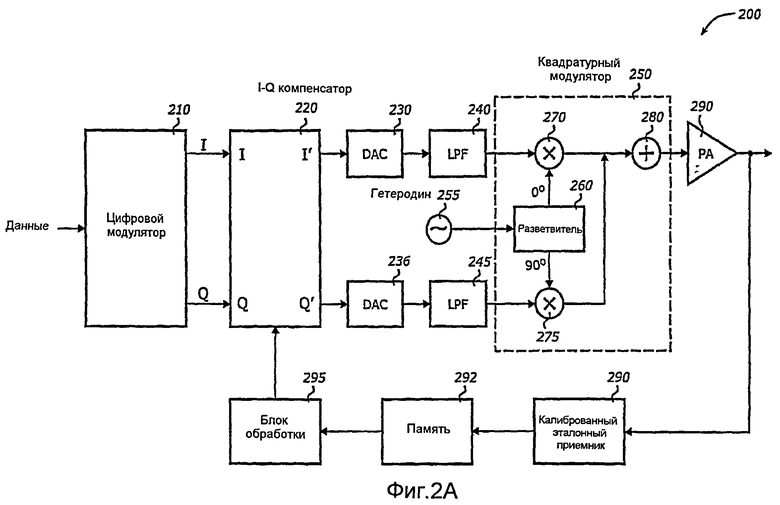

Фиг.2А представляет собой диаграмму, иллюстрирующую подсистему передатчика для калибровки, используя калиброванный эталонный приемник, согласно одному варианту осуществления изобретения.

Фиг.2В представляет собой диаграмму, иллюстрирующую компенсатор для подсистемы передатчика согласно одному варианту осуществления изобретения.

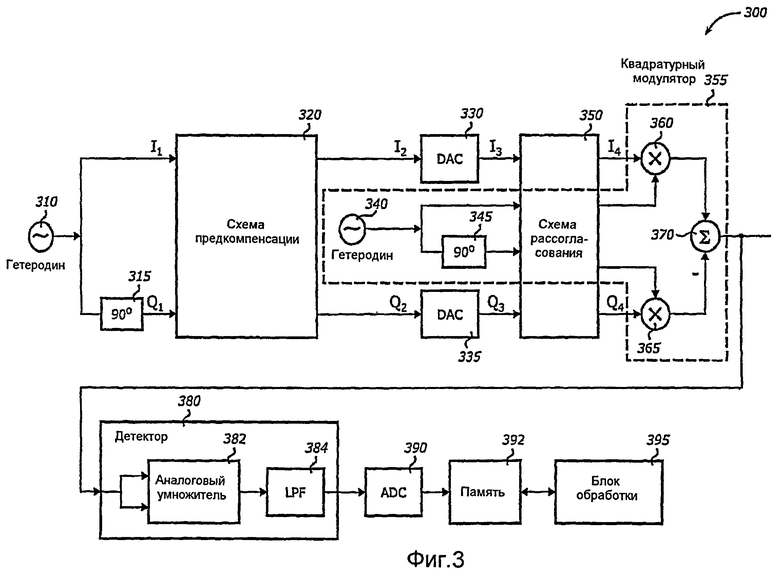

Фиг.3 представляет собой диаграмму, иллюстрирующую подсистему передатчика для калибровки без использования калиброванного эталонного приемника согласно одному варианту осуществления изобретения.

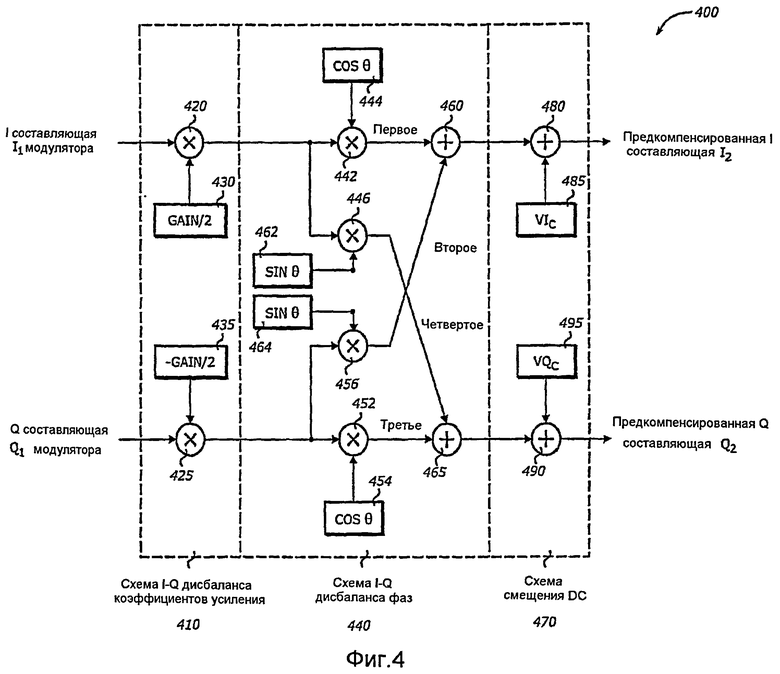

Фиг.4 представляет собой диаграмму, иллюстрирующую схему предкомпенсации согласно одному варианту осуществления изобретения.

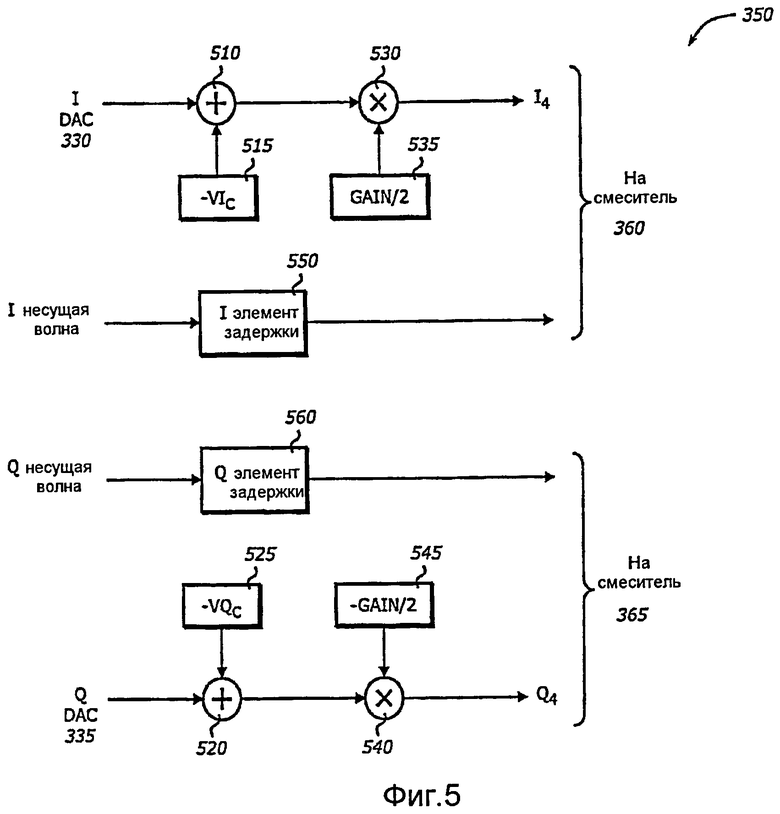

Фиг.5 представляет собой диаграмму, иллюстрирующую схему рассогласования согласно одному варианту осуществления изобретения.

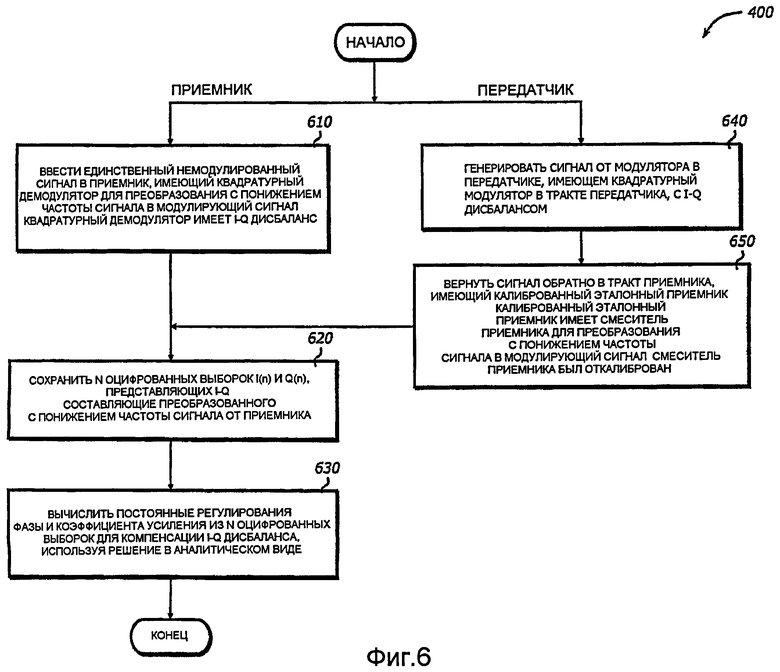

Фиг.6 представляет собой блок-схему последовательности операций, иллюстрирующую процесс выполнения калибровки согласно одному варианту осуществления изобретения.

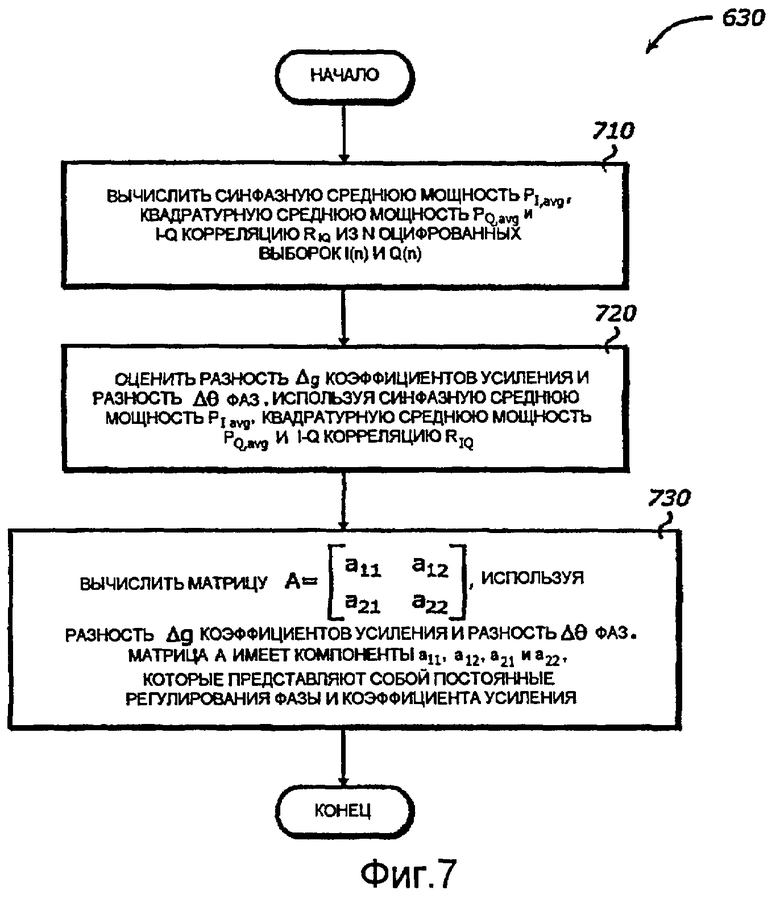

Фиг.7 представляет собой блок-схему последовательности операций, иллюстрирующую процесс вычисления постоянных регулирования фазы и коэффициента усиления согласно одному варианту осуществления изобретения.

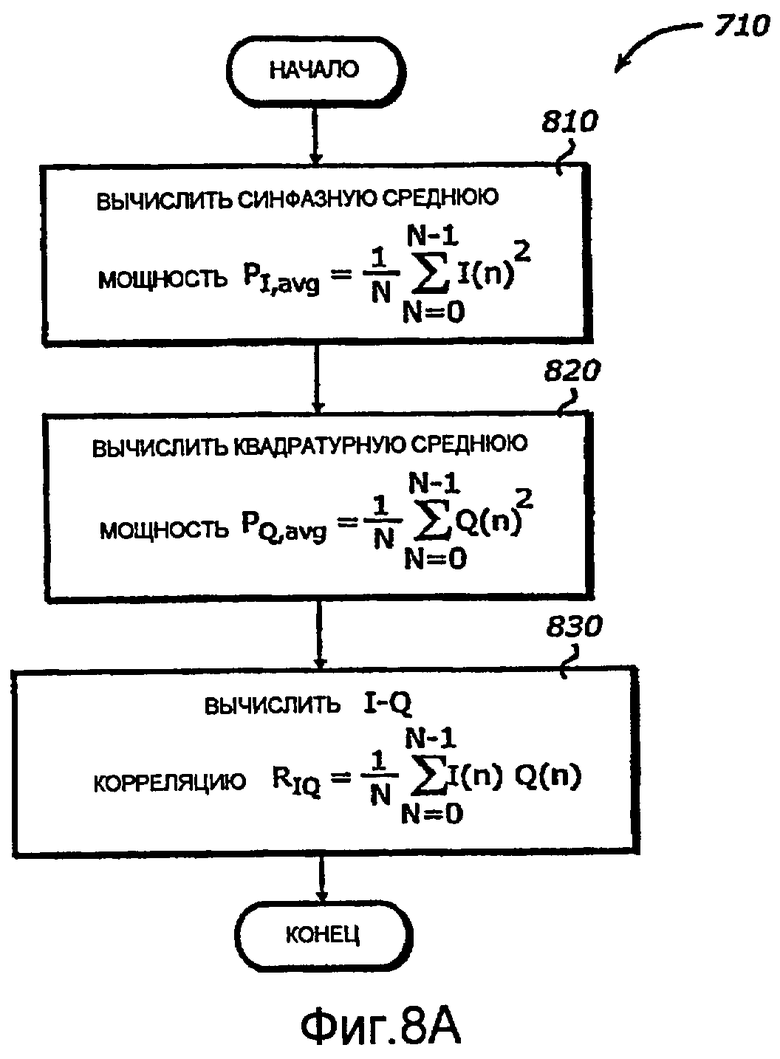

Фиг.8А представляет собой блок-схему последовательности операций, иллюстрирующую процесс вычисления средней I-Q мощности и I-Q корреляции согласно одному варианту осуществления изобретения.

Фиг.8В представляет собой блок-схему последовательности операций, иллюстрирующую процесс оценки разности коэффициентов усиления и фаз согласно одному варианту осуществления изобретения.

Фиг.8С представляет собой блок-схему последовательности операций, иллюстрирующую процесс вычисления матрицы А постоянных регулирования согласно одному варианту осуществления изобретения.

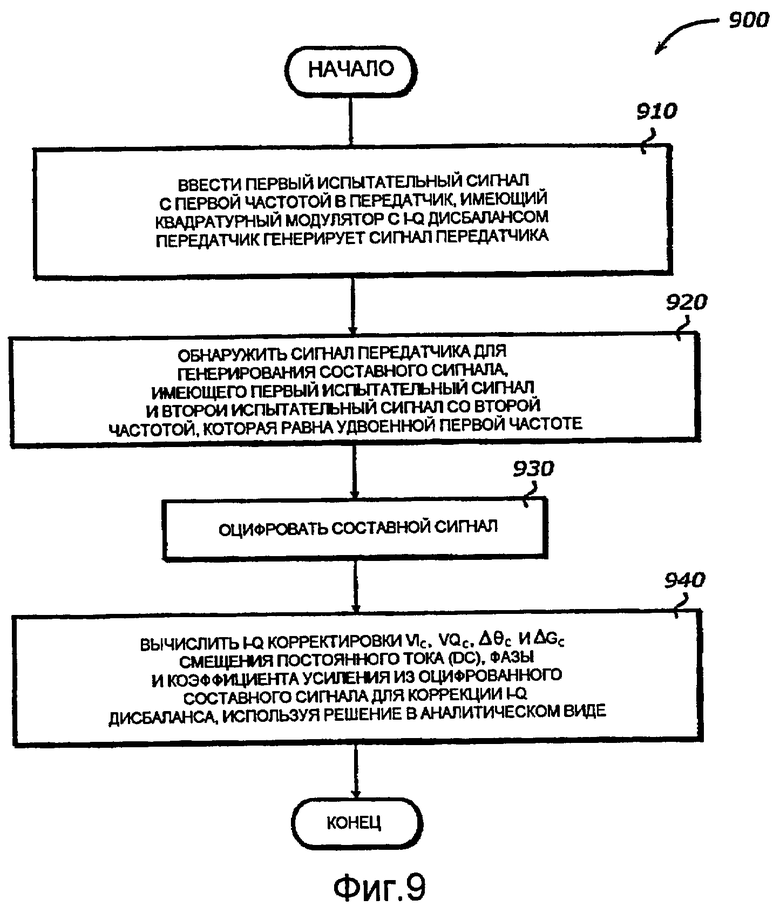

Фиг.9 представляет собой блок-схему последовательности операций, иллюстрирующую процесс калибровки передатчика без использования калиброванного эталонного приемника согласно одному варианту осуществления изобретения.

Фиг.10А представляет собой блок-схему последовательности операций, иллюстрирующую процесс обнаружения сигнала передатчика согласно одному варианту осуществления изобретения.

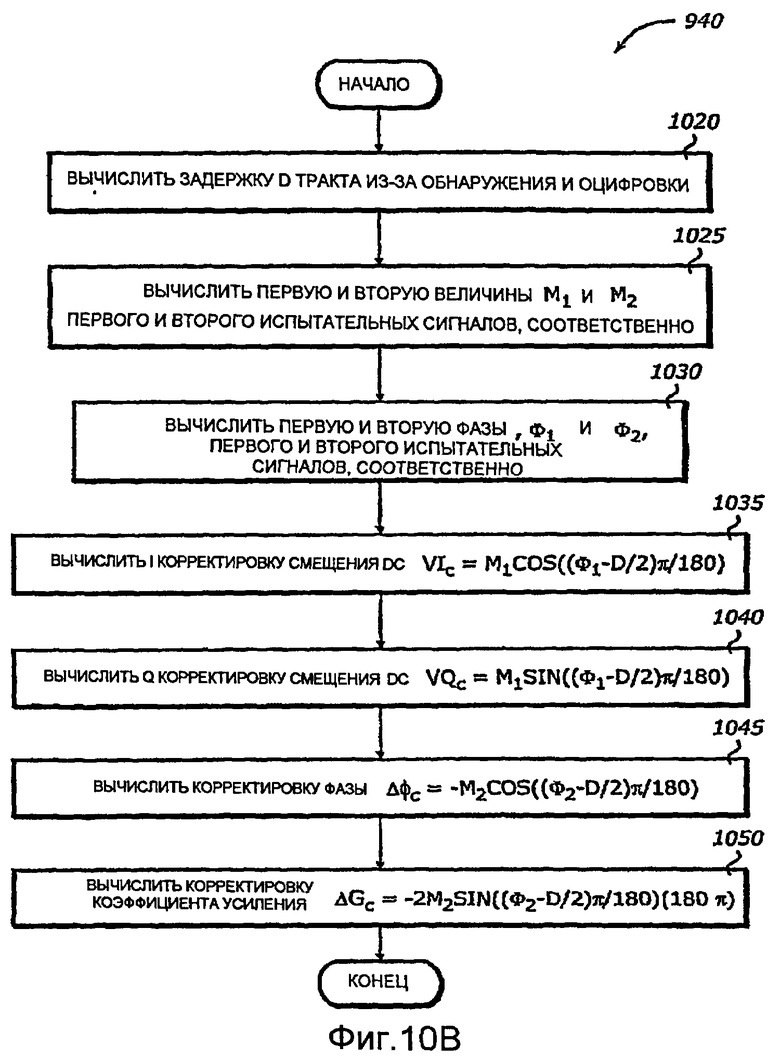

Фиг.10В представляет собой блок-схему последовательности операций, иллюстрирующую процесс вычисления I-Q корректировок смещения DC, фазы и коэффициента усиления согласно одному варианту осуществления изобретения.

Фиг.11 представляет собой диаграмму, иллюстрирующую блок обработки согласно одному варианту осуществления изобретения.

Описание

Вариант осуществления настоящего изобретения включает в себя метод калибровки приемника и передатчика в системе связи. Сохраняют N оцифрованных выборок I(n) и Q(n). N оцифрованных выборок представляют синфазную и квадратурную (I-Q) составляющие соответственно преобразованного с понижением частоты сигнала от приемника. I-Q составляющие генерируются квадратурным модулятором или демодулятором, имеющим I-Q дисбаланс. Вычисляют постоянные регулирования фазы и коэффициента усиления из N оцифрованных выборок для компенсации I-Q дисбаланса, используя решение в аналитическом виде.

Другой вариант осуществления настоящего изобретения включает в себя метод калибровки приемопередатчика в системе связи без использования калиброванного эталонного приемника. Первый испытательный сигнал с первой частотой вводят в передатчик, имеющий квадратурный модулятор с I-Q дисбалансом. Квадратурный модулятор имеет несущую частоту. Передатчик генерирует сигнал передатчика. Сигнал передатчика обнаруживают для генерирования составного сигнала, имеющего первый испытательный сигнал и второй испытательный сигнал со второй частотой, равной удвоенной первой частоте. Составной сигнал оцифровывают. Вычисляют I-Q корректировки смещения постоянного тока (DC), фазы и коэффициента усиления из оцифрованного составного сигнала для корректировки I-Q дисбаланса, используя решение в аналитическом виде.

В нижеследующем описании излагаются многочисленные конкретные подробности. Однако понятно, что варианты осуществления изобретения могут быть осуществлены на практике без этих конкретных подробностей. В других случаях общеизвестные схемы, конструкции и методы не были показаны, чтобы не затруднять понимание данного описания.

Один вариант осуществления изобретения может описываться как процесс, который обычно изображается в виде блок-схемы последовательности операций, схемы технологического процесса, структурной схемы или блок-схемы. Хотя блок-схема последовательности операций может описывать операции в виде последовательного процесса, многие операции могут выполняться параллельно или одновременно. Кроме того, порядок операций может переупорядочиваться. Процесс завершается, когда будут завершены его операции. Процесс может соответствовать способу, программе, процедуре, способу производства или изготовления и т.д.

Варианты осуществления изобретения включают в себя метод калибровки приемника или передатчика в системе связи для компенсации I-Q дисбаланса в схеме квадратурного демодулятора или модулятора. Калибровка выполняется в цифровой области, используя решение в аналитическом виде для обеспечения быстрой калибровки. Решение в аналитическом виде включает в себя применение формул или уравнений для вычисления постоянных регулирования или корректировок дисбаланса. После калибровки постоянные регулирования или корректировки дисбаланса могут применяться в схеме компенсатора для компенсации I-Q дисбаланса. Компенсацию выполняют в цифровой области.

В одном варианте осуществления используется метод калибровки приемника. Входной сигнал вводят на вход РЧ приемника. Сигнал проходит через процесс смешивания в схеме квадратурного демодулятора для его преобразования с понижением частоты в модулирующий сигнал. Модулирующий сигнал затем преобразуют в цифровые выборки. Оцифрованные выборки сохраняют в памяти для обработки блоком обработки. Блок обработки вычисляет постоянные регулирования из сохраненных оцифрованных выборок, используя решение в аналитическом виде. Таким образом, вычисление постоянных регулирования происходит за один единственный проход, включающий в себя непосредственные вычисления постоянных, используя формулы. Следовательно, калибровка является быстрой, эффективной и точной.

Эта же самая процедура может использоваться для калибровки передатчика. Для этой схемы требуется калиброванный эталонный приемник для обеспечения тракта приемника для сигнала. Эталонный испытательный сигнал пропускают через квадратурный модулятор передатчика, который имеет I-Q дисбаланс, который требует компенсации. Генерируемый передаваемый сигнал возвращается обратно на калиброванный эталонный приемник. Так как калиброванный эталонный приемник не вносит искажений, искажения в принимаемом сигнале вызываются квадратурным модулятором передатчика. Используют ту же процедуру вычисления постоянных регулирования фазы и коэффициента усиления для калибровки приемника.

После вычисления постоянных регулирования они могут применяться к приемнику или передатчику для компенсации I-Q дисбаланса в квадратурном демодуляторе или модуляторе. Для приемника эти постоянные применяют после преобразования с понижением частоты квадратурным РЧ демодулятором I-Q сигналов. Для передатчика эти постоянные применяют перед преобразованием с повышением частоты квадратурным РЧ модулятором I-Q сигналов для предкомпенсации I-Q дисбаланса. В обоих случаях компенсацию выполняют в цифровой области.

Альтернативным способом является калибровка передатчика без использования калиброванного эталонного приемника. Этот метод использует детектор мощности передатчика, встроенный в схему РЧ приемопередатчика. Первый испытательный сигнал генерируют для пропускания через квадратурный модулятор в передатчике. Сигнал передатчика проходит через детектор. Детектор включает в себя схему возведения в квадрат и фильтр нижних частот. Фильтр нижних частот удаляет несущую частоту квадратурного модулятора. Детектор генерирует составной сигнал, имеющий первый сигнал и второй сигнал на второй частоте, равной удвоенной первой частоте. Составной сигнал затем оцифровывают аналого-цифровым преобразователем. Оцифрованные выборки составного сигнала сохраняют. Блок обработки вычисляет I-Q корректировки смещения DC, фазы и коэффициента усиления из оцифрованного составного сигнала, используя решение в аналитическом виде. I-Q корректировки смещения DC, фазы и коэффициента усиления используют для предкомпенсации I-Q баланса в схеме предкомпенсации перед схемой квадратурного модулятора. Таким образом, вычисление корректировок происходит за один единственный проход, включающий в себя непосредственное вычисление корректировок, используя формулы. Следовательно, калибровка является быстрой, эффективной и точной.

Фиг.1А представляет собой диаграмму, иллюстрирующую подсистему 100 приемника согласно одному варианту осуществления изобретения. Подсистема 100 приемника включает в себя полосовой фильтр (BPF) 110, малошумящий усилитель (LNA) 115, схему 120 квадратурного демодулятора, аналого-цифровые I-Q преобразователи 150 и 155, компенсатор 160 I-Q дисбаланса, цифровой демодулятор 170, память 180 и блок 190 обработки. Подсистема 100 приемника может включать в себя больше или меньше вышеуказанных компонентов.

Входной сигнал принимают от РЧ антенны. BPF 110 удаляет нежелательные частоты из представляющей интерес полосы частот. LNA 115 усиливает отфильтрованный сигнал с надлежащим коэффициентом усиления.

Квадратурный демодулятор 120 преобразует с понижением частоты принятый сигнал до модулирующего сигнала. Квадратурный демодулятор 120 включает в себя гетеродин 125, разветвитель 127, два смесителя 130 и 135 и два буфера 140 и 145. Гетеродин 125 генерирует сигнал несущей, имеющий несущую частоту. Разветвитель 127 разветвляет сигнал несущей на две формы волны, которые сдвинуты по фазе на 90°. Смесители 130 и 135 смешивают, или умножают, принятый сигнал с сигналами со сдвинутой фазой для получения двух каналов: синфазного (I) канала и квадратурного (Q) канала. Два буфера 140 и 145 буферизуют результирующие I-Q составляющие квадратурно-демодулированного сигнала. Квадратурный демодулятор 120 может иметь I-Q дисбаланс, который вызывает искажения сигнала.

Аналого-цифровые I-Q преобразователи 150 и 155 преобразуют соответствующие I-Q составляющие из квадратурного демодулятора 120 в цифровые данные. I-Q компенсатор 160 компенсирует I-Q дисбаланс в квадратурном демодуляторе 120 для получения скорректированных I-Q составляющих. I-Q компенсатор 160 использует постоянные регулирования, вычисленные блоком 190 обработки, для выполнения компенсации. Во время калибровки I-Q компенсатор 160 может находиться в режиме калибровки, который пропускает оцифрованные I-Q составляющие без изменения. После калибровки I-Q компенсатор 160 может загружаться постоянными регулирования и активизироваться для выполнения функции компенсации. Цифровой демодулятор 170 применяет цифровую демодуляцию к скорректированным I-Q составляющим в соответствии с функциями приемника.

Память 180 хранит N оцифрованных выборок I-Q для обработки. Это может быть любое запоминающее устройство (например, быстрое статическое оперативное запоминающее устройство), которое может хранить оцифрованные выборки I-Q с передачей в реальном времени. Размер памяти выбирают в соответствии с требуемым количеством оцифрованных выборок, подлежащих хранению.

Блок 190 обработки включает в себя программируемый процессор, который исполняет программы или инструкции для вычисления постоянных регулирования для компенсации I-Q дисбаланса. Блок 190 обработки обеспечивает постоянные регулирования для I-Q компенсатора 160.

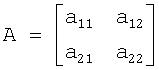

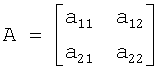

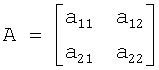

Фиг.1В представляет собой диаграмму, иллюстрирующую компенсатор 160 для подсистемы приемника на фиг.1А согласно одному варианту осуществления изобретения. Компенсатор 160 включает в себя постоянные a 11, a 12, a 21 и a 22 10, 15, 20 и 25 регулирования, два сумматора 162 и 163 и четыре умножителя 164, 165, 166 и 167.

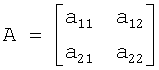

Постоянные a 11, a 12, a 21 и a 22 10, 15, 20 и 25 регулирования представляют собой постоянные или корректировки регулирования коэффициента усиления и фазы для компенсации I-Q дисбаланса, вычисленные в решении в аналитическом виде блоком 190 обработки во время процедуры калибровки. Они могут сохраняться в запоминающих элементах, таких как регистры, буферная память или любые другие запоминающие элементы, включая аппаратно-реализованные данные. Они представляют собой компоненты матрицы А, вычисленной блоком 190 обработки, описанные в процессе 730, показанном на фиг.8С.

Сумматор 162 суммирует первое произведение Р1 со вторым произведением Р2 для получения I составляющей в тракте связи подсистемы 100 приемника. Как описано выше, тракт связи имеет квадратурный демодулятор для преобразования частоты принятого сигнала. Квадратурный демодулятор имеет I-Q дисбаланс или искажение, которое может компенсироваться или корректироваться постоянными a 11, a 12, a 21 и a 22 регулирования коэффициента усиления и фазы. Сумматор 163 суммирует третье произведение Р3 с четвертым произведением Р4 для получения Q составляющей в тракте связи.

Умножители 164 и 166 умножают входные I' и Q' составляющие в тракте связи на постоянные a 11 и a 12 10 и 15 регулирования соответственно для получения первого и второго произведения Р1 и Р2 соответственно для сумматора 162. Умножители 165 и 167 умножают входные Q' и I' составляющие в тракте связи на постоянные a 22 и a 21 20 и 25 регулирования соответственно для получения третьего и четвертого произведения Р3 и Р4 соответственно.

Фиг.2А представляет собой диаграмму, иллюстрирующую подсистему 200 передатчика для калибровки, используя калиброванный эталонный приемник согласно одному варианту осуществления изобретения. Подсистема 200 передатчика включает в себя цифровой модулятор 210, I-Q компенсатор 220, цифроаналоговые I-Q преобразователи 230 и 235, полосовые I-Q фильтры (LPF) 240 и 245, квадратурный модулятор 250, усилитель 285 мощности (PA), калиброванный эталонный приемник 290, память 292 и блок 295 обработки. Подсистема 200 передатчика может включать в себя больше или меньше вышеупомянутых компонентов. Во время калибровки калиброванный эталонный приемник 290, память 292 и блок 295 обработки используют для вычисления постоянных регулирования, используемых в I-Q компенсаторе 220. После вычисления постоянных регулирования блок 295 обработки загружает эти постоянные в компенсатор 220. После этого калиброванный эталонный приемник 290, память 292 и блок 295 обработки могут быть удалены.

Цифровой модулятор 210 выполняет цифровую модуляцию в соответствии с функцией передатчика. Она может включать в себя различные функции кодирования, такие как кодирование ошибок и т.д. I-Q компенсатор 220 применяет постоянные регулирования или корректировки дисбаланса для предкомпенсации I-Q дисбаланса или искажений в квадратурном модуляторе 250. I-Q DAC 230 и 235 преобразуют цифровые данные I-Q в аналоговые модулирующие сигналы. LPF 240 и 245 фильтруют нижние частоты аналоговых модулирующих сигналов на соответствующих I-Q каналах для удаления нежелательных частот.

Квадратурный модулятор 250 преобразует с повышением частоты модулирующие сигналы до требуемой частоты. Квадратурный модулятор 250 включает в себя гетеродин 255, разветвитель 260, два смесителя 270 и 275 и объединитель 280. Гетеродин 255 генерирует сигнал несущей, имеющий несущую частоту. Разветвитель 260 разветвляет сигнал несущей на две формы волны, которые сдвинуты по фазе на 90°. Смесители 270 и 275 смешивают, или умножают, модулирующие сигналы со сдвинутыми по фазе сигналами для получения I-Q составляющих РЧ сигнала, подлежащего передаче. Квадратурный модулятор 250 может иметь I-Q дисбаланс, который вызывает искажения сигнала. Объединитель 280 объединяет, или суммирует, I-Q составляющие РЧ сигнала в составной выходной РЧ сигнал.

PA 285 усиливает составной РЧ сигнал для передачи на РЧ антенну. Калиброванный эталонный приемник 290 представляет собой подсистему приемника, которая была откалибрована для компенсации I-Q дисбаланса в ее квадратурном демодуляторе. Она подобна подсистеме 100 приемника. Память 292 и блок 295 обработки подобны памяти 180 и блоку 190 обработки соответственно, показанным на фиг.1А. Память 292 хранит оцифрованные выборки принятого сигнала. Блок 295 обработки вычисляет постоянные регулирования для использования в I-Q компенсаторе 220.

Фиг.2В представляет собой диаграмму, иллюстрирующую компенсатор 220 для подсистемы передатчика согласно одному варианту осуществления изобретения. Компенсатор 220 включает в себя постоянные a 11, a 12, a 21 и a 22 10, 15, 20 и 25 регулирования, два сумматора 222 и 223 и четыре умножителя 224, 225, 226 и 227.

Постоянные a 11, a 12, a 21 и a 22 10, 15, 20 и 25 регулирования представляют собой постоянные или корректировки регулирования коэффициента усиления и фазы для компенсации I-Q дисбаланса, вычисленные в решении в аналитическом виде блоком 295 обработки во время процедуры калибровки. Они подобны постоянным, показанным на фиг.1В. Они могут храниться в запоминающих элементах, таких как регистры, буферная память или любые другие запоминающие элементы, включая аппаратно-реализованные данные. Они представляют собой компоненты матрицы А, вычисляемой блоком 295 обработки, как описано в процессе 730, показанном на фиг.8С.

Сумматор 222 суммирует первое произведение Р1 со вторым произведением Р2 для получения I' составляющей в тракте связи подсистемы 200 передатчика. Как описано выше, тракт связи имеет квадратурный модулятор для переноса частоты модулирующего сигнала. Квадратурный модулятор имеет I-Q дисбаланс или искажение, которое может предкомпенсироваться или корректироваться постоянными a 11, a 12, a 21 и a 22 регулирования коэффициента усиления и фазы. Сумматор 223 суммирует третье произведение Р3 с четвертым произведением Р4 для получения Q' составляющей в тракте связи.

Умножители 224 и 226 умножают входные I и Q составляющие в тракте связи на постоянные a 11 и a 12 10 и 15 регулирования соответственно для получения первого и второго произведения Р1 и Р2 соответственно для сумматора 222. Умножители 225 и 227 умножают входные Q и I составляющие в тракте связи на постоянные a 22 и a 21 20 и 25 регулирования соответственно для получения третьего и четвертого произведения Р3 и Р4 соответственно.

Калибровка подсистемы 200 передатчика выполняется с использованием калиброванного эталонного приемника 290. Когда такой приемник недоступен, может применяться альтернативный метод калибровки. Этот метод может иллюстрироваться на фиг.3.

Фиг.3 представляет собой диаграмму, иллюстрирующую подсистему 300 передатчика для калибровки без использования калиброванного эталонного приемника согласно одному варианту осуществления изобретения. Подсистема 300 передатчика включает в себя генератор 310 сигналов, фазовращатель 315, схему 320 предкомпенсации, два I-Q DAC 330 и 335, схему 350 рассогласования, квадратурный модулятор 355, детектор 380, аналого-цифровой преобразователь 390, память 392 и блок 395 обработки. Подсистема 300 передатчика может включать в себя больше или меньше вышеупомянутых компонентов.

Генератор 310 сигналов генерирует испытательный сигнал с предварительно определенной частотой. Испытательный сигнал становится I составляющей, т.е. I1 в тракте связи. Фазовращатель 315 сдвигает фазу испытательного сигнала на 90° для получения Q составляющей, например Q1. Генератор 310 сигналов и фазовращатель 315 могут использоваться для эмулирования цифрового модулятора, обычно используемого в передатчике. Генератор 310 сигналов поэтому может быть реализован в виде генератора цифрового сигнала, который генерирует цифровые данные. Испытательный сигнал может быть однотонным сигналом, который имеет единственную частоту. Другими словами, он может генерироваться в виде синусоидальной волны с предварительно определенной частотой.

Схема 320 предкомпенсации принимает I-Q составляющие I1 и Q1 модулятора, эмулированные генератором 310 сигналов и фазовращателем 315, и генерирует предкомпенсированные I-Q составляющие I2 и Q2 для I-Q DAC 330 и 335 соответственно. Схема 320 предкомпенсации использует постоянные компенсации для компенсации I-Q дисбаланса в квадратурном модуляторе 355. Постоянные компенсации вычисляются с использованием решения в аналитическом виде в процедуре калибровки.

I-Q DAC2 330 и 335 преобразуют соответствующие цифровые I-Q данные I2 и Q2 от схемы 320 предкомпенсации в аналоговые модулирующие I-Q сигналы I3 и Q3 соответственно. Схема 350 рассогласования моделирует I-Q дисбаланс в виде смещения DC, ошибки коэффициента усиления и ошибки фазы.

Квадратурный модулятор 355 преобразует с повышением частоты модулирующие сигналы до требуемой частоты. Квадратурный модулятор 355 включает в себя гетеродин 340, фазовращатель 345, два смесителя 360 и 365 и объединитель 370. Гетеродин 340 генерирует сигнал несущей, имеющий несущую частоту. Исходный сигнал несущей соответствует I составляющей. Фазовращатель 345 сдвигает фазу сигнала несущей на 90°, чтобы соответствовать Q составляющей. Смесители 360 и 365 смешивают, или умножают, модулирующие сигналы, пропущенные схемой 350 рассогласования, с исходными и сдвинутыми по фазе сигналами для обеспечения I-Q составляющих РЧ сигнала, подлежащего передаче. Квадратурный модулятор 355 может иметь I-Q дисбаланс, который вызывает искажения сигнала. Объединитель 370 объединяет, или суммирует, I-Q составляющие РЧ сигнала в сигнал передатчика.

Во время калибровки сигнал передатчика из квадратурного модулятора 355 подается на детектор 380. Детектор 380 генерирует составной сигнал, имеющий первый сигнал в виде первой и второй частот испытательного сигнала из сигнала передатчика, причем вторая частота в два раза больше первой частоты. Детектор 380 включает в себя аналоговый умножитель 382 и фильтр 384 нижних частот (LPF). Аналоговый умножитель 382 умножает сигнал передатчика на самого себя или возводит в квадрат сигнал передатчика. Если сигнал передатчика содержит испытательный сигнал, который представляет собой однотонный синусоидальный сигнал, возведение в квадрат вводит дополнительный второй испытательный сигнал, имеющий вторую частоту, которая в два раза больше частоты испытательного сигнала. LPF 384 имеет частоту излома примерно выше второй частоты. Так как первая частота существенно ниже несущей частоты, вторая частота также значительно меньше несущей частоты. LPF 384 поэтому удаляет несущую частоту при пропускании первого и второго сигналов. Величины и фазы первого и второго сигналов обеспечивают зависимость со смещением DC, ошибками фазы и коэффициента усиления из-за I-Q дисбаланса. ADC 390 преобразует аналоговый сигнал из детектора в цифровые данные для обеспечения оцифрованных выборок составного сигнала. Оцифрованные выборки используются для вычисления постоянных компенсации.

Память 392 и блок 395 обработки подобны памяти 292 и блоку 295 обработки соответственно, показанным на фиг.2А. Память 392 хранит оцифрованные выборки составного сигнала. Блок 395 обработки вычисляет постоянные компенсации для использования в предкомпенсаторе 320.

Фиг.4 представляет собой диаграмму, иллюстрирующую схему 320 предкомпенсации, показанную на фиг.3, согласно одному варианту осуществления изобретения. Она включает в себя схему 410 I-Q дисбаланса коэффициента усиления, схему 440 I-Q дисбаланса фазы и схему 470 смещения DC.

Схема 410 I-Q дисбаланса коэффициента усиления генерирует предкомпенсированные I-Q составляющие коэффициента усиления. Она включает в себя I-Q умножители 420 и 425 коэффициента усиления для умножения I-Q составляющих I1 и Q1 модулятора на I-Q постоянные 430 и 435 компенсации коэффициента усиления для получения предкомпенсированных I-Q составляющих коэффициента усиления. I-Q постоянные 430 и 435 компенсации коэффициента усиления представляют собой GAIN/2 и -GAIN/2 соответственно. Значением GAIN является ΔGc, показанное на фиг.10В и вычисляемое так, как описано в относящемся к нему описании.

Схема 440 I-Q дисбаланса фазы генерирует I-Q составляющие с предварительно скомпенсированным коэффициентом усиления и фазой из I-Q составляющих с предварительно скомпенсированным коэффициентом усиления. Она включает в себя умножители 442, 446, 452 и 456 и два сумматора 460 и 465.

Умножители 442 и 456 умножают I-Q составляющие с предскомпенсированным коэффициентом усиления на I-Q постоянные 444 и 464 компенсации фазы соответственно для получения первого и второго произведения соответственно. I-Q постоянные 444 и 464 компенсации фазы представляют собой cosθ и sinθ соответственно. Значением фазы θ является Δϕ с, показанное на фиг.10В и вычисляемое так, как описано в относящемся к нему описании.

Умножители 452 и 446 умножают Q-I составляющие на Q-I постоянные 454 и 462 компенсации фазы соответственно для получения третьего и четвертого произведений соответственно. Q-I постоянными 454 и 462 компенсации фазы являются cosθ и sinθ соответственно. Значением фазы θ является Δϕ с, показанное на фиг.10В и вычисляемое так, как описано в относящемся к нему описании.

Сумматор 460 суммирует первое произведение со вторым произведением для получения I составляющей с предварительно компенсированным коэффициентом усиления и фазой. Сумматор 465 суммирует третье произведение с четвертым произведением для получения Q составляющей с предварительно компенсированным коэффициентом усиления и фазой.

Схема 470 смещения DC генерирует I-Q составляющие с предварительно компенсированным дисбалансом. Она включает в себя I-Q сумматоры 480 и 490 смещения DC для суммирования предкомпенсированных I-Q составляющих коэффициента усиления и фазы с I-Q постоянными 485 и 495 компенсации смещения DC соответственно для получения предкомпенсированных I-Q составляющих. I-Q постоянными 485 и 495 компенсации смещения DC являются VIc и VQc соответственно. VIc и VQc являются VIc и VQc соответственно, показанные на фиг.10В и вычисляемые так, как описано в относящемся к ним описании.

Фиг.5 представляет собой диаграмму, иллюстрирующую схему 350 рассогласования, показанную на фиг.3, согласно одному варианту осуществления изобретения. Схема 340 рассогласования включает в себя два сумматора 510 и 520, два умножителя 530 и 540 и два I-Q элемента 550 и 560 задержки.

Сумматоры вычитают I-Q постоянные 515 и 525 компенсации смещения DC из соответствующих выходных сигналов I-Q DAC 330 и 335 для генерирования первой и второй разности соответственно. I-Q постоянными 515 и 525 компенсации смещения DC являются VIc и VQc соответственно.

Умножители 530 и 540 умножают первую и вторую разности на отрицательные величины I-Q постоянных 535 и 545 компенсации коэффициента усиления соответственно для получения входных I-Q сигналов I4 и Q4 для схемы смесителя в квадратурном модуляторе 355. I-Q постоянными 535 и 545 компенсации коэффициента усиления являются GAIN/2 и -GAIN/2 соответственно. I-Q элементы 550 и 560 задержки обеспечивают I-Q ошибки фаз для I-Q составляющих сигнала несущей от гетеродина 340.

Фиг.6 представляет собой блок-схему последовательности операций, иллюстрирующую процесс 600 для выполнения калибровки согласно одному варианту осуществления изобретения.

После выполнения операции Начало процесс 600 определяет, имеется ли калибровка для приемника или передатчика. Если имеется калибровка для приемника, процесс 600 вводит единственный немодулированный сигнал в приемник (блок 610). Приемник имеет квадратурный демодулятор для преобразования с понижением частоты сигнала в модулирующий сигнал. Квадратурный демодулятор имеет I-Q дисбаланс, который может быть необходимо компенсировать или регулировать. Затем процесс 600 сохраняет N оцифрованных выборок I(n) и Q(n), где n представляет собой индекс выборки, представляющий I-Q составляющие соответственно преобразованного с понижением частоты сигнала от приемника (блок 620). I-Q составляющие генерируются из квадратурного демодулятора.

Затем процесс 600 вычисляет постоянные регулирования фазы и коэффициента усиления из N оцифрованных выборок для компенсации I-Q дисбаланса, используя решение в аналитическом виде (блок 630). Процесс 630 объясняется на фиг.7. Затем процесс 600 завершается.

Если имеется калибровка для передатчика, процесс 600 генерирует сигнал из модулятора в передатчике (блок 640). Передатчик имеет квадратурный модулятор в тракте передатчика с I-Q дисбалансом. Затем процесс 600 возвращает сигнал обратно в тракт приемника, имеющий калиброванный эталонный приемник (блок 650). Калиброванный эталонный приемник имеет смеситель приемника для преобразования с понижением частоты сигнала в модулирующий сигнал. Смеситель приемника был откалиброван, так что он не имеет I-Q дисбаланс. I-Q дисбаланс, введенный в сигнал, поэтому происходит от передатчика, который калибруется. Затем процесс 600 переходит к блоку 620 для вычисления постоянных регулирования для передатчика, используя решение в аналитическом виде таким же образом, что и решение для калибровки приемника, за исключением того, что постоянные регулирования теперь используются для передатчика.

Фиг.7 представляет собой блок-схему последовательности операций, иллюстрирующую процесс 630, показанный на фиг.6, для вычисления постоянных регулирования фазы и коэффициента усиления согласно одному варианту осуществления изобретения.

После выполнения операции Начало процесс 630 вычисляет синфазную среднюю мощность P

I,avg, квадратурную среднюю мощность P

Q,avg и I-Q корреляцию R

IQ из N оцифрованных выборок I(n) и Q(n) (блок 710). Затем процесс 630 оценивает разность Δg коэффициентов усиления и разность Δϕ фаз, используя синфазную среднюю мощность P

I,avg , квадратурную среднюю мощность P

Q,avg и I-Q корреляцию R

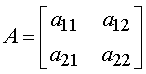

IQ (блок 720). Затем процесс 630 вычисляет матрицу  , используя разность Δg коэффициентов усиления и разность Δϕ фаз (блок 730). Матрица А имеет компоненты a

11, a

12, a

21 и a

22, которые являются постоянными регулирования фазы и коэффициента усиления. Затем процесс 630 завершается.

, используя разность Δg коэффициентов усиления и разность Δϕ фаз (блок 730). Матрица А имеет компоненты a

11, a

12, a

21 и a

22, которые являются постоянными регулирования фазы и коэффициента усиления. Затем процесс 630 завершается.

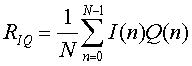

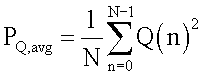

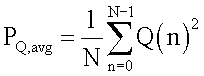

Фиг.8А представляет собой блок-схему последовательности операций, иллюстрирующую процесс 710, показанный на фиг.7, для вычисления средних I-Q мощностей и I-Q корреляции согласно одному варианту осуществления изобретения.

После выполнения операции Начало процесс 710 вычисляет синфазную среднюю мощность P I,avg (блок 810), квадратурную среднюю мощность P Q,avg (блок 820) и I-Q корреляцию R IQ (блок 830) в соответствии со следующими уравнениями:

(1)

(1)

(2)

(2)

(3)

(3)

Затем процесс 710 завершается.

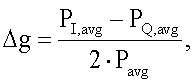

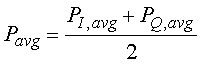

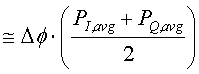

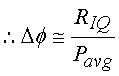

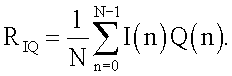

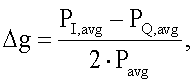

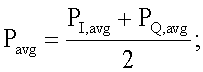

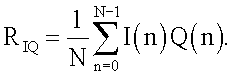

Фиг.8В представляет собой блок-схему последовательности операций, иллюстрирующую процесс 720, для оценки разностей коэффициентов усиления и фаз согласно одному варианту осуществления изобретения.

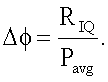

После выполнения операции Начало процесс 720 оценивает разность Δg коэффициентов усиления следующим образом:

где

где

(4)

(4)

Дифференцирование уравнения (4) приведено ниже. Затем процесс 720 оценивает разность Δϕ фаз следующим образом:

(5)

(5)

Дифференцирование уравнения (5) приведено ниже. Затем процесс 720 завершается.

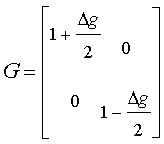

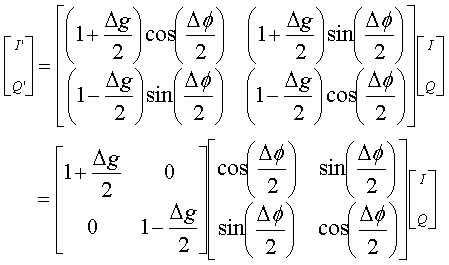

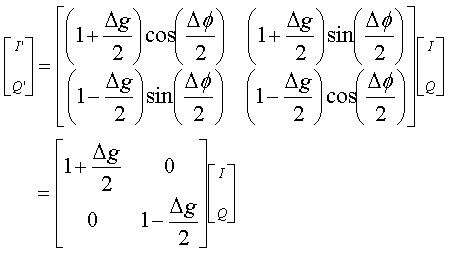

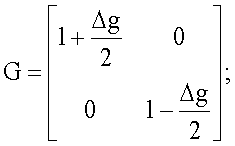

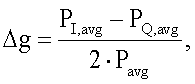

Фиг.8С представляет собой блок-схему последовательности операций, иллюстрирующую процесс 730, изображенный на фиг.7, для вычисления матрицы А постоянных регулирования согласно одному варианту осуществления изобретения.

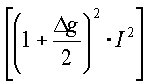

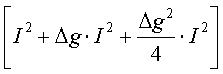

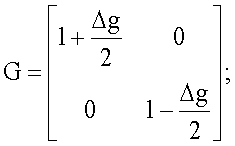

После выполнения операции Начало процесс 730 вычисляет матрицу G коэффициента усиления следующим образом, используя разность Δg коэффициентов усиления, вычисленную в уравнении (4).

(6)

(6)

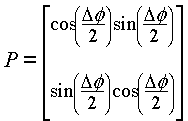

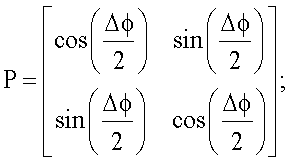

Затем процесс 730 вычисляет матрицу Р фазы следующим образом, используя разность Δϕ фаз, вычисленную в уравнении (5).

(7)

(7)

Затем процесс 730 вычисляет матрицу М произведений посредством перемножения матриц G и P следующим образом:

М = GP

(8)

(8)

Затем процесс 730 вычисляет матрицу А в виде обратной матрицы М произведений, вычисленной в уравнении (8), следующим образом:

A = M

-1

(9)

(9)

Матрица  , таким образом, содержит составляющие a

11, a

12, a

21 и a

22, которые представляют собой постоянные регулирования фазы и коэффициента усиления или корректировки дисбаланса, подлежащие использованию в компенсаторе 160 приемника (фиг.1А) или компенсаторе 220 передатчика (фиг.2А).

, таким образом, содержит составляющие a

11, a

12, a

21 и a

22, которые представляют собой постоянные регулирования фазы и коэффициента усиления или корректировки дисбаланса, подлежащие использованию в компенсаторе 160 приемника (фиг.1А) или компенсаторе 220 передатчика (фиг.2А).

Процесс 730 также может необязательно обновлять матрицу А посредством повторения вышеупомянутого вычисления и обновления матрицы А следующим образом:

B(n)=A·B(n-1) (10)

(10)

где В(0)=I, I представляет собой единичную матрицу.

Затем процесс 730 завершается.

Уравнения (4) и (5) обеспечивают выражения для вычисления постоянных регулирования фазы и коэффициента усиления. Эти выражения могут выводиться следующим образом.

I-Q дисбаланс моделируется с использованием следующего уравнения

(11)

(11)

Дифференцирование постоянной Δg регулирования коэффициента усиления, показанной в уравнении (4)

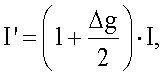

Предположив Δϕ=0, I-Q дисбаланс определяется следующим образом:

(12)

(12)

(13)

(13)

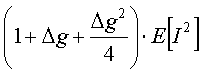

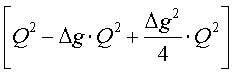

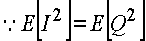

С этими уравнениями дифференцирование выполняется следующим образом:

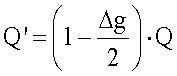

PI,avg=E[I'2]

E

=E

(14)

(14)

=

PQ,avg=E[Q'2]

=E

=E

(15)

(15)

=

PI,avg - PQ,avg =∆g·E +∆g·E

+∆g·E

=2·∆g·E

(16)

(16)

=2·∆g·Pavg

Из уравнения (16) может быть получено Δg:

(17)

(17)

Дифференцирование постоянной Δϕ регулирования фазы, показанной в уравнении (5)

Предположив Δg=0 и Δϕ<<1, I-Q дисбаланс определяется следующим образом:

(18)

(18)

что дает: I' = I+ ,

, Q' =

Q' =

(19)

(19)

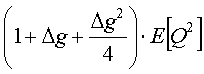

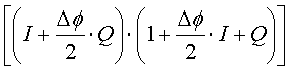

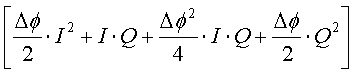

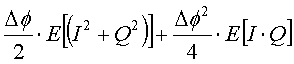

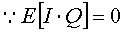

R IQ может быть выражено следующим образом:

RIQ = E[I′·Q′]

=E

=E

=

(20)

(20)

=

=

=

что дает

(21)

(21)

Фиг.9 представляет собой блок-схему последовательности операций, иллюстрирующую процесс 900 калибровки передатчика без использования калиброванного эталонного приемника согласно одному варианту осуществления изобретения.

После выполнения операции Начало процесс 900 вводит первый испытательный сигнал с первой частотой в передатчик, имеющий квадратурный модулятор с I-Q дисбалансом (блок 910). Квадратурный модулятор имеет несущую частоту. Передатчик генерирует сигнал передатчика. Затем процесс 900 детектирует сигнал передатчика и генерирует составной сигнал, имеющий первый испытательный сигнал и второй испытательный сигнал со второй частотой, которая равна удвоенной первой частоте (блок 920).

Затем процесс 900 оцифровывает составной сигнал (блок 930). Это может выполняться при помощи подходящего ADC с надлежащей частотой fs выборки. Затем процесс 900 вычисляет I-Q корректировки VIc, VQc, Δϕс и ΔGc смещения DC, фазы и коэффициента усиления из оцифрованного составного сигнала для корректировки I-Q дисбаланса, используя решение в аналитическом виде (блок 940). Затем процесс 900 завершается.

Фиг.10А представляет собой блок-схему последовательности операций, иллюстрирующую процесс 920, показанный на фиг.9, для обнаружения сигнала передатчика согласно одному варианту осуществления изобретения.

После выполнения операции Начало процесс 920 возводит в квадрат сигнал передатчика, используя аналоговый умножитель (блок 1010). Возведение в квадрат фактически вводит второй сигнал или тон, образующийся с частотой, которая в два раза больше частоты первого тона в первом испытательном сигнале. Затем процесс 920 фильтрует возведенный в квадрат сигнал при помощи фильтра нижних частот, имеющего частоту излома примерно на второй частоте (блок 1015). Фильтр нижних частот удаляет несущую частоту и пропускает первый и второй испытательные сигналы. Затем процесс 920 завершается.

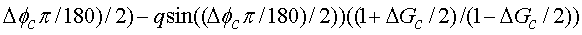

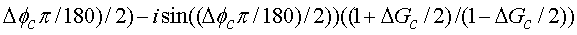

Фиг.10В представляет собой блок-схему последовательности операций, иллюстрирующую процесс 940 вычисления I-Q корректировок смещения DC, фазы и коэффициента усиления согласно одному варианту осуществления изобретения.

После выполнения операции Начало процесс 940 вычисляет задержку D тракта из-за обнаружения и оцифровки, т.е. от детектора 380 до ADC 390 (блок 1020). Задержка D тракта измеряется в градусах. Это может выполняться посредством установки входного сигнала Q канала на нуль, т.е. установки на нуль входного сигнала Q1 после фазовращателя 315 на фиг.3, и выполнения калибровки. Выходной сигнал фазы второго испытательного сигнала, т.е. второй тон, равен задержке D тракта.

Затем процесс 940 вычисляет первую и вторую величины М1 и М2 первого и второго испытательных сигналов соответственно (блок 1025). Затем процесс 940 вычисляет первую и вторую фазы Ф1 и Ф2 первого и второго испытательных сигналов соответственно (блок 1030). Затем процесс 940 вычисляет I корректировку смещения DC VIc=М1cos((Ф1-D/2)π/180) (блок 1035). Затем процесс 940 вычисляет Q корректировку смещения DC VQc=-М1sin((Ф1-D/2)π/180) (блок 1040). Затем процесс 940 вычисляет корректировку фазы Δϕс=-М2cos((Ф2-D/2)π/180) (блок 1045). Затем процесс 940 вычисляет корректировку коэффициента усиления ΔGc=-2М2sin((Ф2-D/2)π/180)(180/π) (блок 1050). Затем процесс 940 завершается.

Вычисление I-Q корректировок VIc, VQc, Δϕс и ΔGc смещения DC, фазы и коэффициента усиления основывается на модели передатчика и схемы рассогласования, как показано на фиг.4. Из модели схемы, показанной на фиг.4, получают уравнения I-Q составляющих для получения выражений для I-Q корректировок VIc, VQc, Δϕс и ΔGc смещения DC, фазы и коэффициента усиления.

Пусть

i - тон I канала в вольтах

q - тон Q канала в вольтах

I - I канал после смесителя в вольтах

Q - Q канал после смесителя в вольтах

V - выход передатчика в вольтах

fm - частота модуляции

fc - несущая частота

fs - частота выборки в единицах 100 пс

Δt - время в единицах 100 пс

ΔS - задержка тракта в единицах Δt

VIc - I корректировка смещения DC в вольтах

VQc - Q корректировка смещения DC в вольтах

ΔGc - корректировка дисбаланса коэффициентов усиления в вольтах

Δϕс - корректировка дисбаланса фаз в градусах

VIP - реальная I величина смещения DC в вольтах

VQP - реальная Q величина смещения DC в вольтах

ΔGP - реальная величина дисбаланса коэффициентов усиления в вольтах

ΔϕP - реальная величина дисбаланса фаз в градусах

Уравнения для различных величин в передатчике, показанных на фиг.3

i=cos((2 )(

)( ))

)) (22a)

(22a)

q=sin((2 )(

)( ))

)) (22b)

(22b)

I=(icos(( (23a)

(23a)

Q=(qcos(( (23b)

(23b)

V=(I-VIc+VIp)(1-∆Gp)cos((2 )(

)( )+(

)+(

-(Q-VQc+VQp)(1+∆Gp)sin((2 )(

)( )-(Δϕ

Pπ/180)/2)

)-(Δϕ

Pπ/180)/2) (24)

(24)

Уравнения для корректировок:

VIc=M1cos((Ф1-D/2)π/180) (25)

(25)

VQc=-M1sin((Ф1-D/2)π/180)

(26)

(26)

∆ϕc=-M2cos((Ф2-D/2)π/180)

(27)

(27)

∆Gc=-2M2sin((Ф2-D/2)π/180)(180/π)

(28)

(28)

где М1 - величина первого испытательного сигнала, или тона, в вольтах,

Ф1 - фаза первого испытательного сигнала, или тона, в градусах,

М2 - величина второго испытательного сигнала, или тона, в вольтах,

Ф2 - фаза второго испытательного сигнала, или тона, в градусах,

D - задержка тракта в градусах.

Фиг.11 представляет схему, иллюстрирующую блоки 190, 295 или 395 обработки, показанные на фиг.1А, 2А и 3 соответственно, согласно одному варианту осуществления изобретения. Блок 190/295/395 обработки включает в себя блок 1110 процессора, контроллер 1120 памяти (MC), основную память 1130, графический процессор 1140, контроллер 1150 ввода-вывода (IOC), межсоединение 1155, интерфейс 1170 запоминающего устройства большой емкости и устройства 11801-1180K ввода-вывода (IO). Блок 190/295/395 обработки может содержать больше или меньше вышеупомянутых компонентов.

Блок 1110 процессора представляет центральный процессор с архитектурой любого типа, такой как процессоры, использующие гиперпотоковые технологии, технологии обеспечения безопасности, цифровые мультимедийные технологии, одноядерные процессоры, многоядерные процессоры, встроенные процессоры, мобильные процессоры, микроконтроллеры, процессоры цифровой обработки сигналов, суперскалярные компьютеры, векторные процессоры, компьютеры с одним потоком команд и множеством потоков данных (SIMD), компьютеры со сложным набором команд (CISC), компьютеры с сокращенным набором команд (RISC), архитектуру с командными словами очень большой длины или гибридную архитектуру.

MC 1120 обеспечивает управление и конфигурирование памяти и устройств ввода-вывода, таких как основная память 1130 и IOC 1140. MC 1120 может быть интегрирован в микропроцессорный набор, который интегрирует многочисленные функциональные возможности, такие как графика, мультимедиа, режим изолированного выполнения, интерфейс шины хоста с периферийными устройствами, управление памятью, управление питанием и т.д. КП 1120 или функциональная возможность контроллера памяти в MC 1120 может интегрироваться в блок 1110 процессора. В некоторых вариантах осуществления контроллер памяти, или внутренний, или внешний по отношению к блоку 1110 процессора, может работать для всех ядер или процессоров в блоке 1110 процессора. В других вариантах осуществления он может включать в себя различные части, которые могут работать отдельно для различных ядер или процессоров в блоке 1110 процессора.

Основная память 1130 хранит системный код и данные. Основная память 1130 обычно реализуется при помощи динамического оперативного запоминающего устройства (DRAM), статического оперативного запоминающего устройства (SRAM) или любых других типов памяти, включая те, которые не требуют регенерации. Основная память 1130 может включать в себя многочисленные каналы запоминающих устройств, таких как DRAM. Основная память 1130 может включать в себя модуль 1135 калибровки. Модуль 1135 калибровки включает в себя программные инструкции и данные для выполнения функций калибровки, как описано выше. Модуль 1135 калибровки может включать в себя или взаимодействовать с соответствующими математическими программными пакетами или программными пакетами обработки сигналов (например, MathLab) для выполнения вычислений постоянных или корректировок регулирования.

Графический процессор 1140 представляет собой любой процессор, который обеспечивает графические функциональные возможности. Графический процессор 1140 также может быть интегрирован в MC 1120, формируя контроллер графики и памяти (GMC). Графический процессор 1140 может представлять собой графическую плату, такую как плата ускорителя рабочих характеристик графики (AGP), обеспечивающая сопряжение с MC 1120 при помощи графического порта, такого как ускоренный графический порт (AGP) или межсоединения PCI (межсоединение периферийных компонентов) Express. Графический процессор 1140 обеспечивает интерфейс с внешним устройством отображения, таким как стандартный монитор с построчной разверткой, телевизионное (TV) устройство и контроллер дифференциальной передачи сигналов с минимизацией перепадов уровня (TMDS).

IOC 1150 имеет ряд функциональных возможностей, которые предназначены для поддержки функций ввода-вывода. IOC 1150 также может интегрироваться в микропроцессорный набор вместе или отдельно от MC 1120 для выполнения функций ввода-вывода. IOC 1150 может включать в себя несколько интерфейсных функций и функций ввода-вывода, таких как интерфейс шины межсоединения периферийных компонентов (PCI), интерфейс процессора, контроллер прерываний, контроллер прямого доступа к памяти (DMA), логика управления питанием, таймер, системная управляющая шина (SMBus), интерфейс универсальной последовательной шины (USB), интерфейс запоминающего устройства большой емкости, интерфейс ввода-вывода с небольшим числом контактов (LPC), беспроводное межсоединение, интерфейс прямых средств информации (DMI) и т.д.

Межсоединение или шина 1155 обеспечивает интерфейс для периферийных устройств. Межсоединение 1155 может быть типа точка-точка или может подключаться к многочисленным устройствам. Для ясности, не все межсоединения показаны. Предполагается, что межсоединение 1155 может включать в себя любое межсоединение или шину, такую как межсоединение периферийных компонентов (PCI), PCI Express, универсальную последовательную шину (USB), интерфейс малых вычислительных систем (SCSI), последовательный SCSI, интерфейс Direct Media (DMI) и т.д.

Интерфейс 1170 запоминающего устройства большой емкости выполняет сопряжение с запоминающими устройствами большой емкости для хранения архивной информации, такой как код, программы, файлы, данные и приложения. Интерфейс запоминающего устройства большой емкости может включать в себя SCSI, последовательный SCSI, присоединение по новейшей технологии (ATA) (параллельное и/или последовательное), встроенный интерфейс накопителей (IDE), улучшенный IDE, пакетный интерфейс АТА (АТАPI) и т.д. Запоминающее устройство большой емкости может включать в себя постоянное запоминающее устройство (ROM) 1172 на компакт-диске (CD), цифровой многофункциональный диск (DVD) 1173, гибкий диск 1174, накопитель 1175 на жестком диске, накопитель 1176 на лентах и любые другие магнитные или оптические запоминающие устройства. Запоминающее устройство большой емкости обеспечивает механизм для считывания доступной для машины мультимедиа.

Устройства 11801-1180K ввода-вывода могут включать в себя любые I/O устройства для выполнения функций I/O. Примеры устройств 11801-1180К ввода-вывода включают в себя контроллер для устройств ввода (например, клавиатура, мышь, шаровой манипулятор, указательное устройство и блок дистанционного управления), медиакарту (например, аудио, видео и графика), сетевую карту и любые другие периферийные контроллеры.

Элементы одного варианта осуществления изобретения могут быть реализованы аппаратными средствами, аппаратно-программными средствами, программными средствами или любой их комбинацией. Термин «аппаратные средства» ссылается в основном на элемент, имеющий физическую конструкцию, такой как электронные, электромагнитные, оптические, электрооптические, механические, электромеханические детали и т.д. Термин «программные средства» ссылается в основном на логическую структуру, способ, процедуру, программу, подпрограмму, процесс, алгоритм, формулу, функцию, выражение и т.д. Термин «аппаратно-программные средства» ссылается в основном на логическую структуру, способ, процедуру, программу, подпрограмму, процесс, алгоритм, формулу, функцию, выражение и т.д., которые реализованы или воплощены аппаратной конструкцией (например, флеш-памятью, ROM, EPROM). Примеры аппаратно-программных средств могут включать в себя микрокод, записываемую управляющую память, микропрограммную структуру. Когда элементы реализованы программными или аппаратно-программными средствами, элементы варианта осуществления настоящего изобретения представляют собой, по существу, сегменты кода для выполнения необходимых задач. Программные/аппаратно-программные средства могут включать в себя фактический код для выполнения операций, описанных в одном варианте осуществления изобретения, или код, который эмулирует или моделирует операции. Программа или сегменты кода могут храниться на доступной для процессора или машины среде или передаваться сигналом компьютерных данных, внедренным в несущую волну, или сигналом, модулированным несущей, по среде передачи. «Считываемая процессором или доступная для процессора среда» или «считываемая машиной или доступная для машины среда» может включать в себя любую среду, которая может хранить, передавать или пересылать информацию. Примеры считываемой процессором или доступной для машины среды включают в себя электронную схему, полупроводниковое запоминающее устройство, постоянное запоминающее устройство (ROM), флеш-память, стираемое программируемое ROM (EPROM), дискету, компакт-диск только для чтения (CD-ROM), оптический диск, жесткий диск, волоконно-оптическую среду, радиочастотную (RF) линию связи и т.д. Сигнал компьютерных данных может включать в себя любой сигнал, который может распространяться по среде передачи, такой как электронные сетевые каналы, оптоволоконные, воздушные, электромагнитные, РЧ линии связи и т.д. Сегменты кода могут загружаться по компьютерным сетям, таким как Интернет, интрасеть и т.д. Доступная для машины среда может воплощаться в изделии. Доступная для машины среда может включать в себя информацию или данные, которые, когда к ним обращается машина, вызывают выполнение машиной операций или действий, описанных выше. Доступная для машины среда также может включать в себя программный код, внедренный в нее. Программный код может включать в себя считываемый машиной код для выполнения операций, описанных выше. Термин «информация» или «данные» ссылается в данном случае на любой тип информации, которая кодируется для считываемых машиной целей. Поэтому она может включать в себя программу, код, данные, файл и т.д.

Весь или часть варианта осуществления изобретения может быть реализована аппаратными средствами, программными средствами или аппаратно-программными средствами или любой их комбинацией. Аппаратный, программный или аппаратно-программный элемент может иметь несколько модулей, соединенных друг с другом. Аппаратный модуль соединяется с другим модулем механическими, электрическими, оптическими, электромагнитными или любыми физическими соединениями. Программный модуль связывается с другим модулем посредством вызова функции, процедуры, метода, части программы или подпрограммы, перехода, ссылки, параметра, переменной и передачи аргументов, возврата из функции и т.д. Программный модуль связывается с другим модулем для приема переменных, параметров, аргументов, указателей и т.д. и/или генерирования или передачи результатов, обновленных переменных, указателей и т.д. Аппаратно-программный модуль связывается с другим модулем любой комбинацией способов связывания аппаратных и программных средств выше. Аппаратный, программный или аппаратно-программный модуль может связываться с любым другим аппаратным, программным или аппаратно-программным модулем. Модуль также может представлять собой программный драйвер или интерфейс для взаимодействия с операционной системой, выполняющейся на платформе. Модуль также может представлять собой аппаратный драйвер для конфигурирования, установки, инициализации, посылки и приема данных на аппаратное устройство и от него. Устройство может включать в себя любую комбинацию аппаратных, программных и аппаратно-программных модулей.

Хотя изобретение было описано в виде нескольких вариантов осуществления, для специалиста в данной области техники понятно, что изобретение не ограничивается описанными вариантами осуществления, но может быть осуществлено на практике с модификацией и изменением в пределах сущности и объема прилагаемой формулы изобретения. Описание, таким образом, должно рассматриваться как иллюстративное вместо ограничительного.

Изобретение относится к технике связи и может использоваться для калибровки приемника и передатчика в системе связи. Технический результат состоит в снижении времени обработки и повышении точности рабочих характеристик. Для этого сохраняют оцифрованные выборки, представляющие синфазную и квадратурную составляющие преобразованного с понижением частоты сигнала от приемника. Выборки генерируют из квадратурного демодулятора или модулятора, имеющего I-Q дисбаланс. Вычисляют постоянные регулирования фазы и коэффициента усиления из оцифрованных выборок для компенсации I-Q дисбаланса, используя решение в аналитическом виде. Испытательный сигнал с первой частотой вводится в передатчик, имеющий квадратурный модулятор с I-Q дисбалансом. Квадратурный модулятор имеет несущую частоту. Передатчик генерирует сигнал передатчика. Сигнал передатчика обнаруживают для генерирования составного сигнала, имеющего первый испытательный сигнал и второй испытательный сигнал со второй частотой, равной удвоенной первой частоте. Составной сигнал оцифровывают. Корректировки смещения постоянного тока, фазы и коэффициента усиления вычисляют из оцифрованного составного сигнала для коррекции I-Q дисбаланса, используя решение в аналитическом виде. 8 н. и 28 з.п. ф-лы, 11 ил.

1. Способ компенсации синфазно-квадратурного дисбаланса, содержащий этапы, на которых:

сохраняют N оцифрованных выборок I(n) и Q(n), представляющих синфазную и квадратурную (I-Q) составляющие соответственно преобразованного с понижением частоты сигнала от приемника, причем I-Q составляющие генерируются из квадратурного демодулятора или модулятора, имеющего I-Q дисбаланс; и

вычисляют постоянные регулирования фазы и коэффициента усиления из N оцифрованных выборок для компенсации I-Q дисбаланса, используя решение в аналитическом виде.

2. Способ по п.1, в котором этап вычисления постоянных регулирования фазы и коэффициента усиления содержит этапы, на которых:

вычисляют синфазную среднюю мощность PI,avg, квадратурную среднюю мощность PQ,avg и I-Q корреляцию RIQ из N оцифрованных выборок I(n) и Q(n);

производят оценку разности Δg коэффициентов усиления и разности Δϕ фаз, используя синфазную среднюю мощность PI,avg, квадратурную среднюю мощность PQ,avg и I-Q корреляцию RIQ; и

вычисляют матрицу  , используя разность Δg коэффициентов усиления и разность Δϕ фаз, причем матрица А имеет компоненты а11, а12, а21 и a22, которыми являются постоянные регулирования фазы и коэффициента усиления.

, используя разность Δg коэффициентов усиления и разность Δϕ фаз, причем матрица А имеет компоненты а11, а12, а21 и a22, которыми являются постоянные регулирования фазы и коэффициента усиления.

3. Способ по п.2, в котором этап вычисления синфазной средней мощности PI,avg, квадратурной средней мощности PQ,avg и I-Q корреляции RIQ содержит этапы, на которых:

вычисляют синфазную среднюю мощность

вычисляют квадратурную среднюю мощность  и

и

вычисляют I-Q корреляцию

4. Способ по п.2, в котором этап оценки разности Δg коэффициентов усиления и разности Δϕ фаз содержит этапы, на которых:

производят оценку разности коэффициентов усиления

где  и

и

производят оценку разности фаз

5. Способ по п.2, в котором этап вычисления матрицы  содержит этапы, на которых:

содержит этапы, на которых:

вычисляют матрицу коэффициента усиления

вычисляют матрицу фазы

вычисляют матрицу произведений M=GP и

вычисляют матрицу А в виде обратной величины матрицы произведений М, А=М-1.

6. Способ по п.5, в котором этап вычисления матрицы А в виде обратной величины матрицы произведений содержит этап, на котором

обновляют матрицу А, используя В(n)=А·В(n-1) при В(0)=I.

7. Способ по п.1, дополнительно содержащий этап, на котором:

вводят единственный немодулированный сигнал в приемник, имеющий квадратурный демодулятор, для преобразования сигнала с понижением частоты в модулирующий сигнал, причем квадратурный демодулятор имеет I-Q дисбаланс.

8. Способ по п.1, дополнительно содержащий этапы, на которых:

генерируют сигнал в передатчике, имеющем квадратурный модулятор в тракте передатчика с I-Q дисбалансом;

производят возврат сигнала обратно в тракт приемника калиброванного эталонного приемника, причем калиброванный эталонный приемник имеет смеситель приемника для преобразования сигнала с понижением частоты в модулирующий сигнал, при этом смеситель приемника был откалиброван.

9. Способ компенсации синфазно-квадратурного дисбаланса, содержащий этапы, на которых:

вводят первый сигнал с первой частотой в передатчик, имеющий квадратурный модулятор с синфазным и квадратурным (I-Q) дисбалансом, причем квадратурный модулятор имеет несущую частоту, передатчик генерирует сигнал передатчика;

обнаруживают сигнал передатчика для генерирования составного сигнала, имеющего первый сигнал и второй сигнал на второй частоте, равной удвоенной первой частоте;

оцифровывают составной сигнал и

вычисляют I-Q корректировки VIc, VQc, Δϕс и ΔGc смещения постоянного тока (DC), фазы и коэффициента усиления из оцифрованного составного сигнала для корректировки I-Q дисбаланса, используя решение в аналитическом виде.

10. Способ по п.9, в котором этап обнаружения сигнала передатчика содержит этапы, на которых:

возводят в квадрат сигнал передатчика, используя аналоговый умножитель; и

фильтруют возведенный в квадрат сигнал при помощи фильтра нижних частот, имеющего частоту излома примерно на второй частоте, причем фильтр нижних частот удаляет несущую частоту и пропускает первый и второй сигналы.

11. Способ по п.9, в котором этап вычисления I-Q корректировок смещения DC, фазы и коэффициента усиления содержит этапы, на которых:

вычисляют задержку D тракта из-за обнаружения и оцифровки;

вычисляют первую и вторую величины M1 и М2 первого и второго сигналов соответственно;

вычисляют первую и вторую фазы Ф1 и Ф2 первого и второго сигналов соответственно и

вычисляют I-Q корректировки VIc, VQc, Δϕс и ΔGс смещения DC, фазы и коэффициента усиления, используя задержку D тракта, первую и вторую величины M1 и М2 и первую и вторую фазы Ф1 и Ф2.

12. Способ по п.11, в котором этап вычисления I-Q корректировок VIc, VQc, Δϕс и ΔGc смещения DC, фазы и коэффициента усиления содержит этапы, на которых:

вычисляют I корректировку смещения DC VIc=M1cos((Ф1-D/2)π/180);

вычисляют Q корректировку смещения DC VQc=-M1sin((Ф1-D/2)π/180);

вычисляют корректировку фазы Δϕс=-М2cos((Ф2-D/2)π/180) и

вычисляют корректировку коэффициента усиления ΔGс=-2М2sin((Ф2-D/2)π/180)(180/π).

13. Устройство компенсации синфазно-квадратурного дисбаланса, содержащее:

первый сумматор для суммирования первого произведения со вторым произведением для получения первой синфазной (I) составляющей в тракте связи устройства связи, причем тракт связи имеет квадратурный демодулятор или модулятор для переноса частоты сигнала, квадратурный демодулятор или модулятор имеет I и квадратурный (Q) дисбаланс;

второй сумматор для суммирования третьего произведения с четвертым произведением для получения первой квадратурной (Q) составляющей в тракте связи;

первый и второй умножители, подсоединенные к первому сумматору для умножения вторых I и Q составляющих в тракте связи на первую и вторую постоянные регулирования соответственно для получения первого и второго произведений, соответственно; и

третий и четвертый умножители, подсоединенные ко второму сумматору, для умножения вторых I и Q составляющих в тракте связи на третью и четвертую постоянные регулирования соответственно для получения третьего и четвертого произведений соответственно;

причем первая, вторая, третья и четвертая постоянные регулирования вычисляются с использованием решения в аналитическом виде для компенсации I-Q дисбаланса.

14. Устройство по п.13, в котором тракт связи представляет собой тракт приемника, при этом первые I и Q составляющие корректируются в отношении I-Q дисбаланса и вторые I и Q составляющие искажаются I-Q дисбалансом.

15. Устройство по п.13, в котором тракт связи представляет собой тракт передатчика, при этом первые I и Q составляющие предварительно искажаются в отношении I-Q дисбаланса и вторые I и Q составляющие корректируются.

16. Устройство компенсации синфазно-квадратурного дисбаланса, содержащее:

схему квадратурного модулятора в передатчике для генерирования сигнала передатчика, причем схема квадратурного модулятора имеет синфазный и квадратурный (I-Q) дисбалансы;

схему рассогласования, соединенную со схемой квадратурного модулятора и с I-Q цифроаналоговыми преобразователями (DAC) для моделирования I-Q дисбаланса; и

схему предкомпенсации, соединенную с синфазной и квадратурной (I-Q) составляющими модулятора в модуляторе передатчика для генерирования предкомпенсированных I-Q составляющих для I-Q DAC соответственно, используя постоянные компенсации для компенсации I-Q дисбаланса, причем постоянные компенсации вычисляются с использованием решения в аналитическом виде в процедуре калибровки.

17. Устройство по п.16, дополнительно содержащее:

детектор, соединенный со схемой квадратурного модулятора для генерирования составного сигнала, имеющего первую и вторую частоты, из сигнала передатчика, причем вторая частота равна удвоенной первой частоте; и

аналого-цифровой преобразователь (ADC), соединенный с детектором для получения оцифрованных выборок составного сигнала, причем оцифрованные выборки используются для вычисления постоянных компенсации.

18. Устройство по п.16, в котором схема квадратурного модулятора содержит:

I-Q смесители для смешивания I-Q составляющих с I-Q составляющими несущей волны сигнала несущей волны для генерирования компенсированных I-Q составляющих и

объединитель, соединенный с I-Q смесителем для объединения компенсированных I-Q составляющих в сигнал передатчика.

19. Устройство по п.18, в котором схема рассогласования содержит:

первый и второй сумматоры для вычитания I-Q постоянных компенсации смещения DC из соответствующих выходов DAC для генерирования первой и второй разностей соответственно;

первый и второй умножители, соединенные с первым и вторым сумматорами для умножения первой и второй разностей на отрицательные величины I-Q постоянных компенсации коэффициента усиления для получения I-Q входов для схемы квадратурного модулятора; и

I-Q элементы задержки для получения I-Q рассогласований фаз для I-Q составляющих несущей волны.

20. Устройство по п.16, в котором схема предкомпенсации содержит:

схему I-Q дисбаланса коэффициентов усиления для генерирования предкомпенсированных I-Q составляющих коэффициента усиления, причем схема I-Q дисбаланса коэффициентов усиления включает в себя I-Q умножители коэффициентов усиления для умножения I-Q составляющих модулятора на I-Q постоянные компенсации коэффициента усиления для получения предкомпенсированных I-Q составляющих коэффициента усиления;

схему I-Q дисбаланса фаз, соединенную со схемой I-Q дисбаланса коэффициентов усиления для генерирования предкомпенсированных I-Q составляющих коэффициента усиления и фазы; и

схему смещения постоянного тока (DC), соединенную со схемой I-Q дисбаланса фаз для генерирования предкомпенсированных I-Q составляющих дисбаланса, причем схема смещения DC включает в себя I-Q сумматоры смещения DC для добавления предкомпенсированных I-Q составляющих коэффициента усиления и фазы к I-Q постоянным компенсации смещения DC для получения предкомпенсированных I-Q составляющих дисбаланса.

21. Устройство по п.18, в котором схема I-Q дисбаланса фаз содержит:

первый сумматор для суммирования первого произведения со вторым произведением для получения предкомпенсированной I составляющей коэффициента усиления и фазы;

второй сумматор для суммирования третьего произведения с четвертым произведением для получения предкомпенсированной Q составляющей коэффициента усиления и фазы;

первый и второй умножители, соединенные с первым сумматором для умножения предкомпенсированных I-Q составляющих коэффициента усиления на I-Q постоянные компенсации фазы соответственно для получения первого и второго произведений соответственно и

третий и четвертый умножители, соединенные со вторым сумматором для умножения Q-I составляющих на I-Q постоянные компенсации фазы соответственно для получения третьего и четвертого произведений соответственно.

22. Изделие компенсации синфазно-квадратурного дисбаланса, содержащее:

доступную для машины среду хранения, включающую в себя информацию, которая, когда к ней обращается машина, вызывает выполнение машиной операций, содержащих:

сохранение N оцифрованных выборок I(n) и Q(n), представляющих синфазную и квадратурную (I-Q) составляющие соответственно преобразованного с понижением частоты сигнала от приемника, причем I-Q составляющие генерируются из квадратурного демодулятора или модулятора, имеющего I-Q дисбаланс; и

вычисление постоянных регулирования фазы и коэффициента усиления из N оцифрованных выборок для компенсации I-Q дисбаланса, используя решение в аналитическом виде.

23. Изделие по п.22, в котором информация, вызывающая выполнение машиной вычисления постоянных регулирования фазы и коэффициента усиления, содержит информацию, которая, когда к ней обращается машина, вызывает выполнение машиной операций, содержащих:

вычисление синфазной средней мощности PI,avg, квадратурной средней мощности PQ,avg и I-Q корреляции RIQ из N оцифрованных выборок I(n) и Q(n);

оценку разности Δg коэффициентов усиления и разности Δϕ фаз, используя синфазную среднюю мощность PI,avg, квадратурную среднюю мощность PQ,avg и I-Q корреляцию RIQ; и

вычисление матрицы  , используя разность Δg коэффициентов усиления и разность Δϕ фаз, причем матрица А имеет компоненты а11, а12, а21 и a22, которыми являются постоянные регулирования фазы и коэффициента усиления.

, используя разность Δg коэффициентов усиления и разность Δϕ фаз, причем матрица А имеет компоненты а11, а12, а21 и a22, которыми являются постоянные регулирования фазы и коэффициента усиления.

24. Изделие по п.23, в котором информация, вызывающая выполнение машиной вычисления синфазной средней мощности PI,avg, квадратурной средней мощности PQ,avg и I-Q корреляции RIQ содержит информацию, которая, когда к ней обращается машина, вызывает выполнение машиной операций, содержащих:

вычисление синфазной средней мощности

вычисление квадратурной средней мощности  и

и

вычисление I-Q корреляции

25. Изделие по п.23, в котором информация, вызывающая выполнение машиной оценки разности Δg коэффициентов усиления и разности Δϕ фаз, содержит информацию, которая, когда к ней обращается машина, вызывает выполнение машиной операций, содержащих:

оценку разности коэффициентов усиления

где  и

и

оценку разности фаз

26. Изделие по п.23, в котором информация, вызывающая выполнение машиной вычисления матрицы  , содержит информацию, которая, когда к ней обращается машина, вызывает выполнение машиной операций, содержащих:

, содержит информацию, которая, когда к ней обращается машина, вызывает выполнение машиной операций, содержащих:

вычисление матрицы коэффициента усиления

вычисление матрицы фазы

вычисление матрицы произведений M=GP и

вычисление матрицы А в виде обратной величины матрицы произведений М, А=М-1.

27. Изделие по п.26, в котором информация, вызывающая выполнение машиной вычисления матрицы А в виде обратной величины матрицы произведений, содержит информацию, которая, когда к ней обращается машина, вызывает выполнение машиной операций, содержащих

обновление матрицы А, используя В(n)=А·В(n-1) при В(0)=I.

28. Изделие по п.22, в котором информация дополнительно содержит информацию, которая, когда к ней обращается машина, вызывает выполнение машиной операций, содержащих:

введение единственного немодулированного сигнала в приемник, имеющий квадратурный демодулятор, для преобразования сигнала с понижением частоты в модулирующий сигнал, причем квадратурный демодулятор имеет I-Q дисбаланс.

29. Изделие по п.22, в котором информация дополнительно содержит информацию, которая, когда к ней обращается машина, вызывает выполнение машиной операций, содержащих:

генерирование сигнала в передатчике, имеющем квадратурный модулятор в тракте передатчика с I-Q дисбалансом;

возврат сигнала обратно в тракт приемника калиброванного эталонного приемника, причем калиброванный эталонный приемник имеет смеситель приемника для преобразования сигнала с понижением частоты в модулирующий сигнал, при этом смеситель приемника был откалиброван.

30. Изделие компенсации синфазно-квадратурного дисбаланса, содержащее:

доступную для машины среду хранения, включающую в себя информацию, которая, когда к ней обращается машина, вызывает выполнение машиной операций, содержащих:

введение первого сигнала с первой частотой в передатчик, имеющий квадратурный модулятор с синфазным и квадратурным (I-Q) дисбалансами, причем квадратурный модулятор имеет несущую частоту, передатчик генерирует сигнал передатчика;

обнаружение сигнала передатчика для генерирования составного сигнала, имеющего первый сигнал и второй сигнал на второй частоте, равной удвоенной первой частоте;

оцифровку составного сигнала и

вычисление I-Q корректировок VIc, VQc, Δϕc и ΔGc смещения постоянного тока (DC), фазы и коэффициента усиления из оцифрованного составного сигнала для корректировки I-Q дисбаланса, используя решение в аналитическом виде.

31. Изделие по п.30, в котором информация, вызывающая выполнение машиной детектирования сигнала передатчика, содержит информацию, которая, когда к ней обращается машина, вызывает выполнение машиной операций, содержащих:

возведение в квадрат сигнала передатчика, используя аналоговый умножитель; и

фильтрацию возведенного в квадрат сигнала при помощи фильтра нижних частот, имеющего частоту излома примерно на второй частоте, причем фильтр нижних частот удаляет несущую частоту и пропускает первый и второй сигналы.

32. Изделие по п.30, в котором информация, вызывающая выполнение машиной вычисления I-Q корректировок смещения DC, фазы и коэффициента усиления, содержит информацию, которая, когда к ней обращается машина, вызывает выполнение машиной операций, содержащих:

вычисление задержки D тракта из-за обнаружения и оцифровки;

вычисление первой и второй величин M1 и М2 первого и второго сигналов соответственно;

вычисление первой и второй фаз Ф1 и Ф2 первого и второго сигналов соответственно и

вычисление I-Q корректировок VIc, VQc, Δϕс и ΔGс смещения DC, фазы и коэффициента усиления, используя задержку D тракта, первую и вторую величины M1 и М2 и первую и вторую фазы Ф1 и Ф2.

33. Изделие по п.32, в котором информация, вызывающая выполнение машиной вычисления I-Q корректировок VIc, VQc, Δϕс и ΔGc смещения DC, фазы и коэффициента усиления, содержит информацию, которая, когда к ней обращается машина, вызывает выполнение машиной операций, содержащих:

вычисление I корректировки смещения DC VIc=M1cos((Ф1-D/2)π/180);

вычисление Q корректировки смещения DC VQc=-M1sin((Ф1-D/2)π/180);

вычисление корректировки фазы Δϕс=-М2cos((Ф2-D/2)π/180) и

вычисление корректировки коэффициента усиления ΔGс=-2М2sin((Ф2-D/2)π/180)(180/π).

34. Система компенсации синфазно-квадратурного дисбаланса, содержащая:

квадратурный демодулятор для преобразования с понижением частоты радиочастотного (RF) сигнала, принимаемого подсистемой приемника, причем квадратурный демодулятор обеспечивает аналоговые синфазную и квадратурную (I-Q) составляющие, которые имеют I-Q дисбаланс, квадратурный демодулятор имеет смесители;

аналого-цифровые преобразователи (ADC), соединенные с квадратурным демодулятором для преобразования I-Q составляющих в цифровые I-Q составляющие; и

компенсатор, соединенный с ADC для компенсации I-Q дисбаланса, причем компенсатор содержит:

первый сумматор для суммирования первого произведения со вторым произведением для получения выходной I составляющей,

второй сумматор для суммирования третьего произведения с четвертым произведением для получения выходной Q составляющей,

первый и второй умножители, соединенные с первым сумматором, для умножения цифровых I и Q составляющих на первую и вторую постоянные регулирования соответственно для получения первого и второго произведений соответственно, и

третий и четвертый умножители, соединенные со вторым сумматором, для умножения цифровых I и Q составляющих на третью и четвертую постоянные регулирования соответственно для получения третьего и четвертого произведений соответственно;

в котором первая, вторая, третья и четвертая постоянные регулирования вычисляются с использованием решения в аналитическом виде для компенсации I-Q дисбаланса.

35. Система компенсации синфазно-квадратурного дисбаланса, содержащая:

квадратурный модулятор для преобразования с повышением частоты аналоговых синфазной и квадратурной (I-Q) составляющих модулирующего сигнала в сигнал передачи, причем квадратурный модулятор имеет смесители, которые генерируют I-Q дисбаланс;

цифроаналоговые преобразователи (DAC), соединенные с квадратурным модулятором, для преобразования предкомпенсированных I-Q составляющих в аналоговые I-Q составляющие и

компенсатор, соединенный с DAC, для компенсации I-Q дисбаланса из I-Q составляющих модулятора, причем компенсатор содержит:

первый сумматор для суммирования первого произведения со вторым произведением для получения предкомпенсированной I составляющей,

второй сумматор для суммирования третьего произведения с четвертым произведением для получения предкомпенсированной Q составляющей,

первый и второй умножители, соединенные с первым сумматором для умножения I и Q составляющих модулятора на первую и вторую постоянные регулирования соответственно, для получения первого и второго произведений соответственно, и

третий и четвертый умножители, соединенные со вторым сумматором для умножения I и Q составляющих модулятора на третью и четвертую постоянные регулирования соответственно, для получения третьего и четвертого произведений соответственно;

в котором первая, вторая, третья и четвертая постоянные регулирования вычисляются с использованием решения в аналитическом виде для компенсации I-Q дисбаланса.

36. Система по п.35, дополнительно содержащая

калиброванный эталонный приемник, соединенный с квадратурным модулятором для обеспечения обратного тракта для вычисления I-Q дисбаланса.

| Способ обработки целлюлозных материалов, с целью тонкого измельчения или переведения в коллоидальный раствор | 1923 |

|

SU2005A1 |

| ПЕРЕКОНФИГУРИРОВАНИЕ СИСТЕМ, РАБОТАЮЩИХ В СИСТЕМАХ РАДИОСВЯЗИ | 1996 |

|

RU2191477C2 |

| US 6253066 B1, 26.06.2001 | |||

| Способ обработки целлюлозных материалов, с целью тонкого измельчения или переведения в коллоидальный раствор | 1923 |

|

SU2005A1 |

| WO 9709833 A1, 13.03.1997. | |||

Авторы

Даты

2010-12-20—Публикация

2007-06-06—Подача