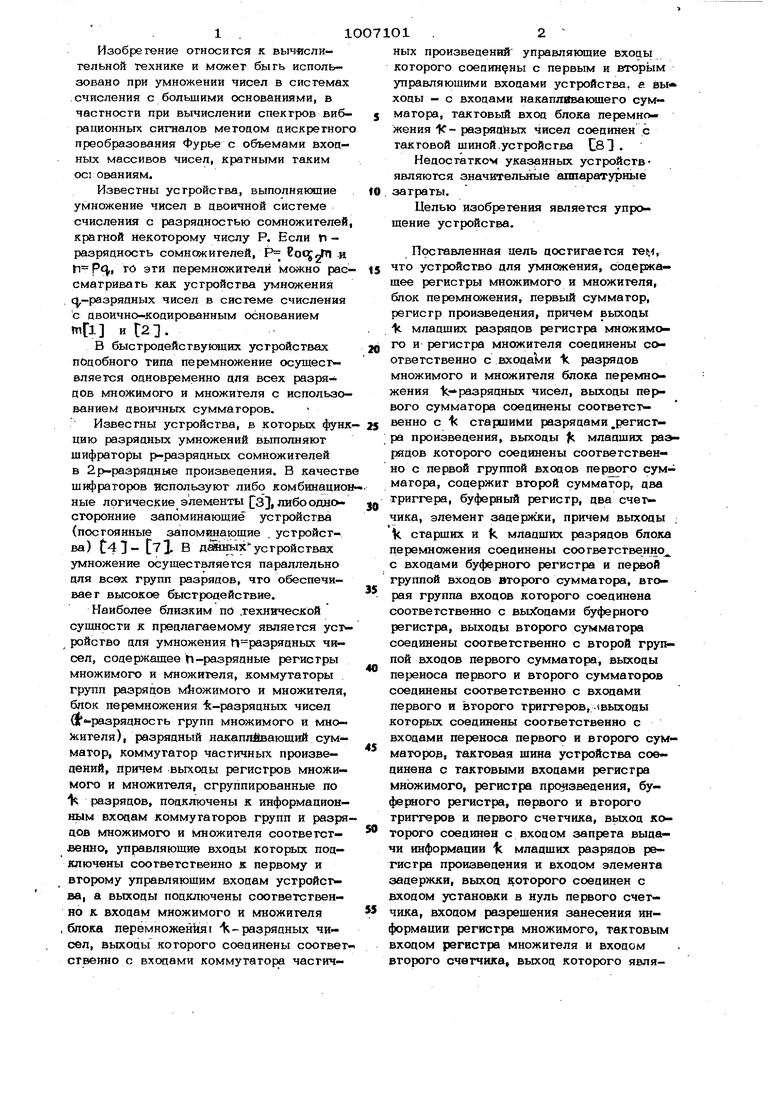

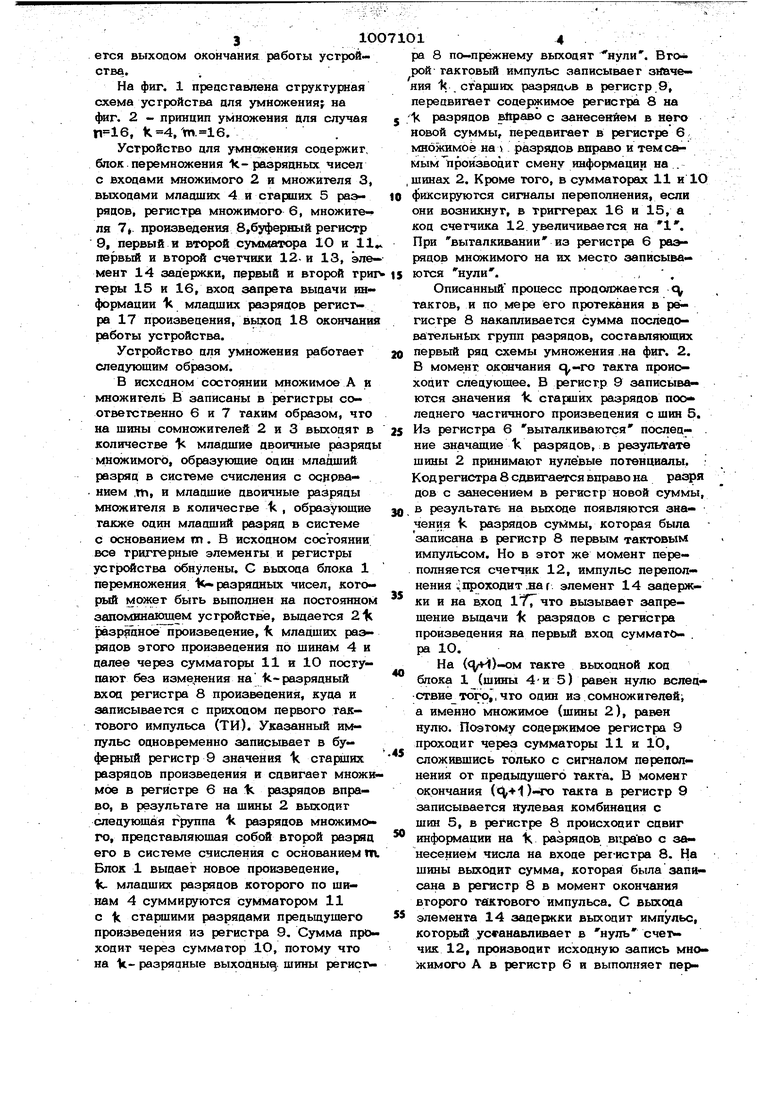

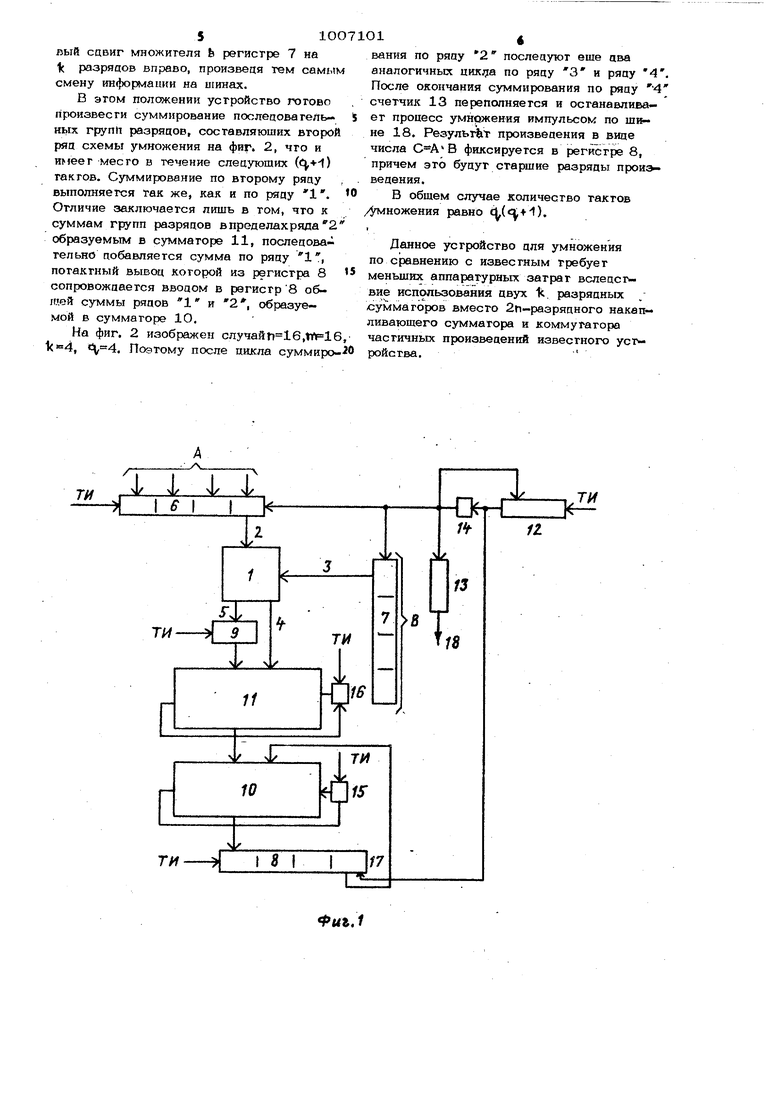

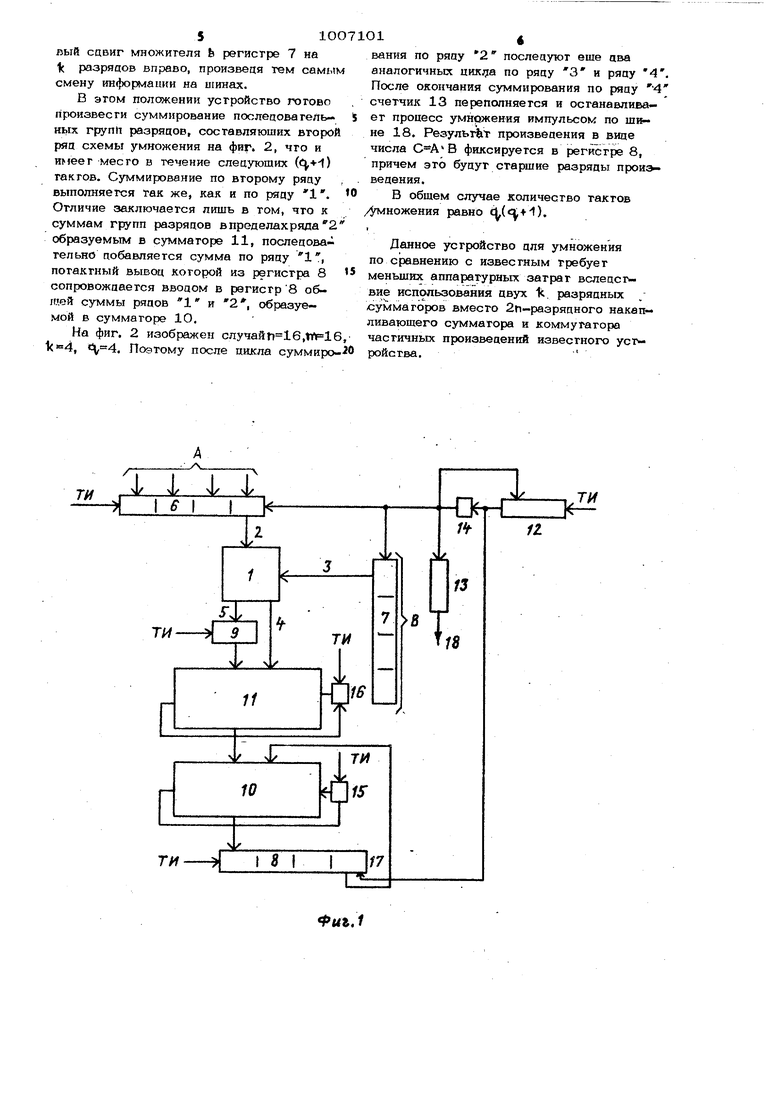

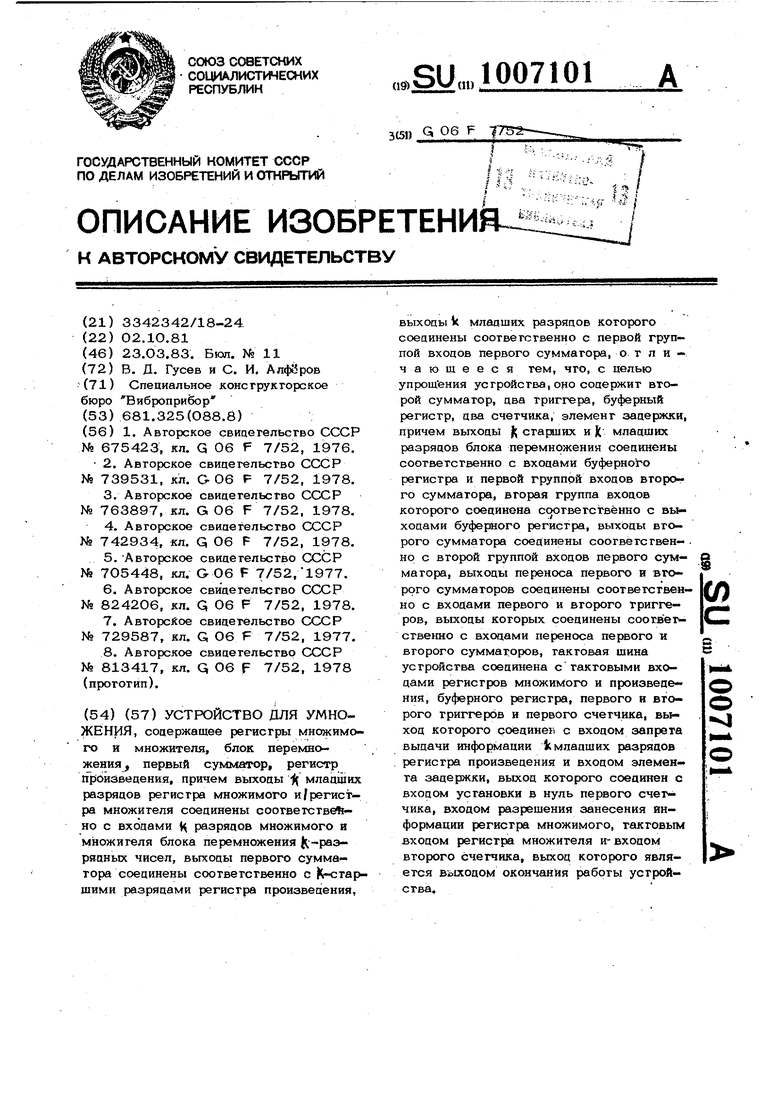

Изобретение огносигся к вычисли- гельной технике и может быть использовано при умножении чисел в системах счисления с большими основаниями, в частности при вычислении спектров виб рационных сигналов методом дискретног преобразования Фурье с объемами входных массивов чисел, кратными таким OCI ованиям. Известны устройства, выполнякидие умножение чисел в двоичной системе счисления с разрядностью сомножителей кратной некоторому числу Р. Если ti разрядность сомножителей, KoojJn и П р, то эти перемножителй можно рас сматривать как устройства умножения q,-разрядных чисел в системе счисления с двоично-кодирюванным основанием mCl и t2l. в быстродействующих устройствах подобного типа перемножение осуществляется одновременно для всех разря- дов множимого и множителя с использо ванием двоичных сумматоров. Известны устройства, в которых фун цию разрядных умножений выполняют шифраторы р-разрядных сомножителей в 2р-разрядные произведения. В качест ши({)раторов используют либо комбинацио ные логические элементы либо односторонние запоминающие устройства (постоянные запоминающие , устройства) ,7l В дайшьхх ус тройствах умножение осуществляется параллельно для всех групп разрядов, что обеспечивает высокое быстродействие. Наиболее близким по .технической сущности к предлагаемому является уст ройство для умножения п разрядных чисел, содержащее п-разрядные регистры множимого и множителя, коммутаторы групп разрядов множимого и множителя блок перемножения -Ь-разрядных чисел Ог-разрядность групп множимого и мно кителя), разрядный накапливающий сумматор, коммутатор частичных произведений, причем выходы регистров множимого и множителя, сгруппированные по разрядов, подключены к информационным входам коммутаторов групп и разря дов множимого и множителя соответственно, управляющие входы которых подключены соответственно к первому и второму управляющим входам устройства, а выходы подключены соответственНО к входам множимого и множителя блока перемноженМя Ч-разрядных чисел, выходы которого соединены соотве ственно с входами коммутатора частичных произведений управляющие входы которого соединены с первым и вторым управляющими входами устройства, а вы ходы - с входами накапливающего сумматора, тактовый вход блока перемножения 1C- разрядных чисел соединен с тактовой шиной.устройства СвЗ . Недостатком указанных устройствявляются значительные аппаратурные затраты. Целью изобретения является упрощение устройства. Поставленная цель достигается те%, что устройство для умножения, содержа- шее регистры множимого и множителя, блок перемножения, первый сумматор, регистр произведения, причем выходы 1t младших разрядов регистра множимого и- регистра множителя соединены соответственно с входами It разрядов множимого и множителя блока перемножения К-разрядных чисел, выходы пе| вого сумматора соединены соответственно с 1с старшими разрядами ,регистра произведения, выходы ft младших разрядов которого соединены соответственно с первой группой входов первого сумматора, содержит второй сумматор, два триггера, буферный регистр, два счетчика, элемент задерзкки, причем выходы Н старших и К младших разрядов блока перемножения соединены соответственно с входами буферного регистра и первой группой входов второго сумматора, вторая группа входов которого соединена соответственно с выходами буферного регистра, выходы второго сумматора соединены соответственно с второй группой входов первого сумматора, выходы переноса первого и второго сумматоров соединены соответственно с входами первого и второго триггеров, .«выходы которых соединены соответственно с входами переноса первого и второго сумма то роэ, тактовая шина устройства соединена с тактовыми входами регистра множимого, регистра про 1зведения, буферного регистра, первого и второго триггеров и первого счетчика, вь1ход которого соединен с входом запрета выдачи информации 1( младших разрядов регистра произведения и входом элемента задержки, выход которого соединен с входом установки в нуль первого счетчика, входом разрешения занесения информации регистра множимого, тактовым входом регистра множителя и входом второго счетчика, выход которого является выходом окончания работы усгрой- ства.. На фиг. 1 преасгавлена структурная схема устройства для умножения на фиг. 2 - принцип умножения Для случая , ,т.16. Устройство для умножения содержит, блок. перемножения 1с-разрядных чисел с входами множимого 2 и множителя 3, выходами младших 4 и старших 5 разрядов, регистра множимого 6, множителя 7j. произведения 8,буферный регистр 9, первый и второй сумматора 10 и 11 первый и второй счетчики 12- и 13, эле мент 14 задержки, первый и второй три геры 15 и 16, вход запрета выдачи информации 1( младших разрядов регистра 17 произведения, вьосод 18 окончани работы устройства. Устройство для умножения работает следующим образом. В исходном состоянии множимое А и множитель В записаны в регистры соответственно 6 и 7 таким образом, что на шины сомножителей 2 и 3 выходят в количестве 1 младшие двоичные разряды множимого, образующие один младший разряд в системе счисления с осррва нием ,т, н младшие двоичные разряды множителя в количестве It , образующие также один младший разряд в системе с Основанием m. В исходном состоянии все триггерные элементы и регистры устройства обнулены. G выхода блока 1 перемножения Поразрядных чисел, который может быть выполнен на постоянном запокшнаюшем устройстве, вьщается 21с произведение, fc младших ра; рядов этого произведения по шинам 4 и далее через сумматоры 11 и 10 поступают без изменения на ft-разрядный вход регистра 8 произведения, куда и записывается с приходом первого тактового импульса (ТИ). Указанный импульс одновременно записывает в буферный регистр 9 значения 1. старших. разрядов произведения и сдвигает множимое в регистре 6 на К разрядов вправо, в результате на шины 2 выходит следующая группа Ic разрядов множимого, представляюшая собой второй разряд его в системе счисления с основанием т Блок 1 выдает новое произведение, 1с- младших разрядов которого по шинам 4 суммируются сумматором 11 с It старшими разрядами предьщушего произведения из регистра 9. Сумма проходит через сумматор 1О, потому что на It- разрядные выходныд. шины регис ра 8 по-прежнему вьсходят нули . Вто рой тактовый импульс записывает значе ния Ц старших разрядов в регистр 9, передвигает содержимое регистра 8 на К разрядов вйраво с занесением в него новой суммы, передвигает в регистре 6 множимое на V разрядов вправо и темсамымпроизводит смену инфо г1ации на . шинах 2. Кроме того, в сумматорах 11 и 1О ({Фиксируются сигналы перепотшения, если они возникнут, в триггерах 16 и 15, а код счетчика 12 увеличивается на I. При выталкивании из регистра 6 разрядов множимого на их место записыва- ются нули ., Описанный процесс продолжается тактов, и по мере его протекания в регистре 8 накапливается сумма последовательньрс групп разрядов, составляющих первый ряд схемы умножения .на фиг. 2. В момент окончания cj,-ro такта происходит следуюшее. В регистр 9 записыва- ются значения 1с старших разрядов поо леднего частичного произведения с шин 5. Из регистра 6 выталкиваются последние значащие k разрядов, в результате шины 2 принимают нулевые потенциалы. од регистра 8 сдвигается вправо на раэря дов с занесением в регистр новой С5гммы, в результате на выходе появляются значения (. разрядов суммы, которая была записана в регистр 8 первым тактовым импульсом. Но в этот же момент переполняется счетчик 12, импульс переполнения ; проходит .наг. элемент 14 задержки и на вход вызывает запрешение выдачи fc разрядов с регистра произведения на первый вход суммато- . ра 10. На ()-ом такте выходной код блока 1 (шины 4 и 5) равен нулю вслед ствие того,, что один из сомножителейi а именно множимое (шины 2), равен нулю. Позртому содержимое регистра 9 проходит через сумматоры 11 и 10, сложившись только с сигналом переполнения от предыдущего такта. В момент окончания (Ц,+1)-го такта в регистр 9 записывается нулевая комбинация с шин 5, в регистре 8 происходит сдвиг инфо{илации на k разрядов В1траво с занесением числа на входе рег-истра 8. На шины выходит сумма, которая записана в регистр 8 в момент окончания второго тактового импульса. С выхода элемента 14 задержки выходит импульс, который устанавливает в нуль счет чик 12, производит исходную запись множимого А в регистр 6 и выполняет сдвиг множителя fe регистре 7 на 1( разрядов вправо, произведя тем самы смену информации на шинах. В этом положении устройство готово произвести суммирование послецоватеяь- ных групп разрядов, составляющих второ ряд схемы умножения на фиг. 2, что и имеет место в течение слеауюших (f) тактов. Суммирование по второму ряцу выполняется так же, как и по ряду 1. Отличие заключается лишь в том, что к суммам групп разрядов впределахряда2 образуемым в сумматоре 11, последовательно добавляется сумма по ряду 1, потактный вывод которой из регистра 8 сопровождается вводом в регистр 8 обшей суммы рядов I и 2, образуемой в сумматоре 10. На фиг. 2 изображен cny4aftti 16, , . Поэтому после цикла суммиро вания по ряду 2 последуют еше два аналогичных по ряду 3 и ряду 4. После окончания суммирования по ряду 4 счетчик 13 переполняется и останавлива.ет процесс умножения импульсом по ш№не 18. Результат произведения в виде числа фиксируется в регистре 8, причем это будут старшие разряды произведения. В общем случае количество тактов $гмножения равно t(+). Данное устройство для умножения по сравнению с известным требует меньших аппаратурных затрат вследствие использования двух k. разрядных :умматоров вместо 2п-разрядного накапливающего сумматора и коммутатора частичных произведений известного устройства.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для умножения | 1984 |

|

SU1233136A1 |

| Устройство для умножения | 1984 |

|

SU1185328A1 |

| Устройство для умножения | 1985 |

|

SU1254473A1 |

| Устройство для умножения | 1982 |

|

SU1038937A1 |

| Устройство для умножения последовательного действия | 1983 |

|

SU1157541A1 |

| Устройство для умножения | 1978 |

|

SU888109A1 |

| Устройство для умножения | 1985 |

|

SU1322265A1 |

| Устройство для умножения | 1981 |

|

SU1032453A1 |

| Устройство для умножения | 1982 |

|

SU1038936A1 |

| Устройство для умножения на коэффициенты | 1984 |

|

SU1242925A1 |

УСТРОЙСТВО ДЛЯ УМНОЖЕНИЯ, содержащее регистры множимого и множителя, блок перемно жения, первый сумматор, регистр 1Гроизвеаения, причем выходы i( младщих разрядов регистра множимого и/регистра множителя соединены соответственно с входами Ц разрядов множимого и множителя блока перемножения | -разрядных чисел, выходы первого сумматора соединены соответственно с К-старьшими разрядами регистра произведения. выходы k младших разрядов которого соединены соответственно с первой группой входов первого сумматора, от л и - чающееся тем, что, с целью упрошения устройства, оно содержит второй сумматор, два триппера, буферный регистр, два счетчика, элемент задержки, причем выходы старших и ( младших разрядов блока перемножения соединены соответственно с входами буферного регистра и первой группой входов второго сумматора, вторая группа входов которого соединена ссхэтветсгвённо с выходами буферного регистра, выходы второго сумматора соединены соответствен- . но с второй группой входов первого сумматора, выходы переноса первого и вто(Л рого сумматоров соединены соответственно с входами первого и второго триггеров, выходы которых соединены соответ- ственно с входами переноса первого и S е второго сумматоров, тактовая шина устройства соединена с тактовыми входами регистров множимого и произведения, буферного регистра, первого и второго триггеров и первого счетчика, выход которого соединен с входом запрета выдачи информации i младших разрядов , регистра произведения и входом элемента задержки, выход которого соединен с входом установки в нуль первого счетчика, входом разрешения занесения информации регистра множимого, тактовым входом регистра множителя и-входом второго счетчика, выход которого является выходом окончания работы устройства.

. /

« JtfaeyCffC CjsettCatjtCyeyteCMCaC

fr)gggagffg)gjgfgyg/ fj jgia,aj

Авторы

Даты

1983-03-23—Публикация

1981-10-02—Подача