Изобретение относится к электротехнике и предназначено для управления тиристорными импульсными преобразователями переменного напряжения при их групповом применении, например для нагревательных установок в энергосистемах как с самостоятельным применением только преобразователей, так и при их параллельной работе с потребителями-источниками с резко переменной нагрузкой (прокатные станы, дуговые печи, ветроэлектростанции, солнечные батареи).

Цель изобретения повышение энергетических показателей и динамической устойчивости энергосистемы при параллельной работе произвольных потребителей-источников с резко переменными электрическими нагрузками и группы преобразователей с различными изменяющимися амплитудами электрических нагрузок.

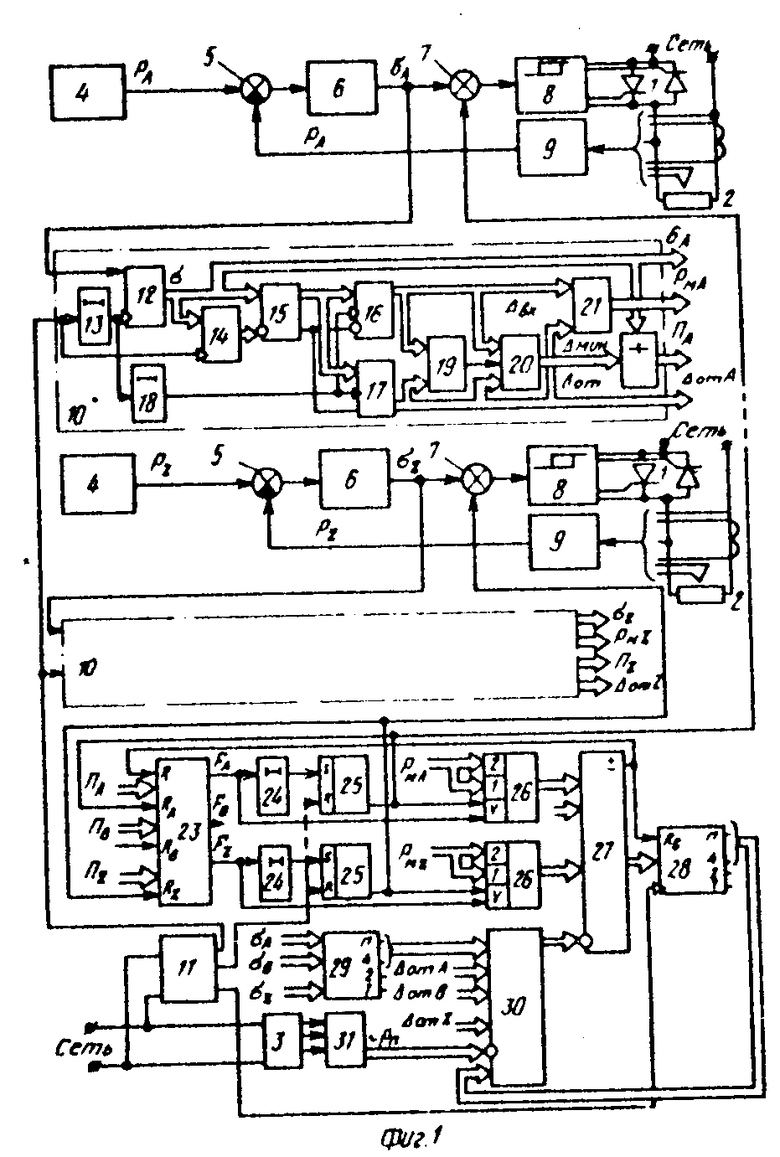

На фиг.1 показана схема устройства для осуществления способа; на фиг.2 - схема логического устройства формирования приоритетного сигнала включения только одного преобразователя; на фиг. 3 и 4 диаграммы сигналов работы устройства.

Устройство для осуществления способа состоит из произвольного числа преобразователей, условно пронумерованных буквами от A до Z. Соответствующие буквы использованы для индексации одинаковых переменных в разных преобразователях. Силовая часть каждого преобразователя состоит из встречно включенных вентилей 1 в цепи нагрузки 2, которые совместно с произвольными потребителями-источниками 3 питаются от одной и той же сети. Схема управления каждого преобразователя содержит функционально последовательно включенные в прямом канале задающий блок 4, первый суммирующий элемент 5, фильтр низших частот 6, представляющий собой интегратор, или в общем случае динамическое звено с передаточной функцией W(P), второй суммирующий элемент 7, релейный элемент 8 с формирователем импульсов и управляемые вентили в цепи нагрузки, а в канале обратной связи датчик 9 регулируемой величины (мощности, тока, температуры), выход которого подключен к входу вычитания первого суммирующего элемента 5, и вне каналов тактируемый аналого-цифровой измерительный блок 10, аналоговый информационный вход которого подключен к выходу фильтра низших частот 6, тактовый вход к одному из выходов синхронизированного сетью генератора 11 тактовых импульсов, общего для всей группы, а четыре цифровых выхода к общей части схемы управления группой преобразователей. На фиг.1 цифровые каналы передачи сигналов, представляющие собой системы проводников (шины), показаны широкими линиями.

Цифровой измерительный блок 10 имеет на информационном входе аналого-цифровой преобразователь 12, тактовой вход которого через первый элемент задержки 13 подключен к генератору 11, а выход к регистру 14 памяти, сумматору 15 и выходу сигнала результата интегрирования σ всего измерительного блока. Тактовый вход регистра 14 прямо подключен к генератору 11, выход регистра 14 к инвертирующему входу сумматора 15, выход модуля которого подключен к информационным входам двух регистров 16, 17 памяти, а выход знака (±) к противофазным входам управления V регистров 16,17, тактовые входы которых через второй элемент задержки 18 подключены к выходу первого элемента задержки 13. Выходы регистров 16,17 подключены к входам элемента сравнения 19, мультиплексора 20 и сумматора 21, выход которого подключен к выходу сигнала амплитуды электрической нагрузки преобразователя Pм всего измерительного блока. Выход элемента сравнения 19 и вход управления V мультиплексора 20 объединены, а выход регистра 17 с прямым входом управления подключен к выходу сигнала модуля приращения интеграла отключенного состояния Dот всего измерительного блока, выход мультиплексора 20 подключен к входу делителя блока 22 деления, вход делимого которого подключен к выходу аналого-цифрового преобразователя 12, а выход к выходу сигналов функций П результатов интегрирования всего измерительного блока.

Выходы сигналов функций П всех измерительных блоков группы преобразователей подключены к информационным входам логического блока 23 формирования приоритетного сигнала включения общей части схемы управления, выходы этого устройства подключены через элементы задержки 24 к входам установки единицы триггеров 25 и к одним из входов управления V мультиплексоров 26. Выходы триггеров 25 подключены к другим входам управления мультиплексоров 26, входам установки нулей R раздельно по каналам логического блока 23 и входам суммирования сумматоров 7. К одним из информационных входов указанных мультиплексоров 26 подключены выходы сигналов амплитуд Pм измерительных блоков прямо, а к другим со сдвигом на один шаг, выходы мультиплексоров 26 подключены к входам сумматора 27, выход которого подключен к информационному входу регистра 28, тактовый вход которого подключен к генератору 11, а выход знака (±) сумматора 27 помимо регистра 28 подключен к входу общей установки нуля R логического блока 23. Выходы сигналов результата интегрирования σ всех измерительных блоков подключены к сумматору 29, старшие разряды выходов которого подключены к входам сумматора 30, к другим входам которого подключены выходы сигналов модулей приращения интегралов отключенного состояния Dот всех измерительных блоков, выходы старших разрядов регистра 28 и с инверсией выход датчика 31 колебаний электрической нагрузки произвольных потребителей источников 3, а выход сумматора подключен к инвертирующему входу сумматора 27.

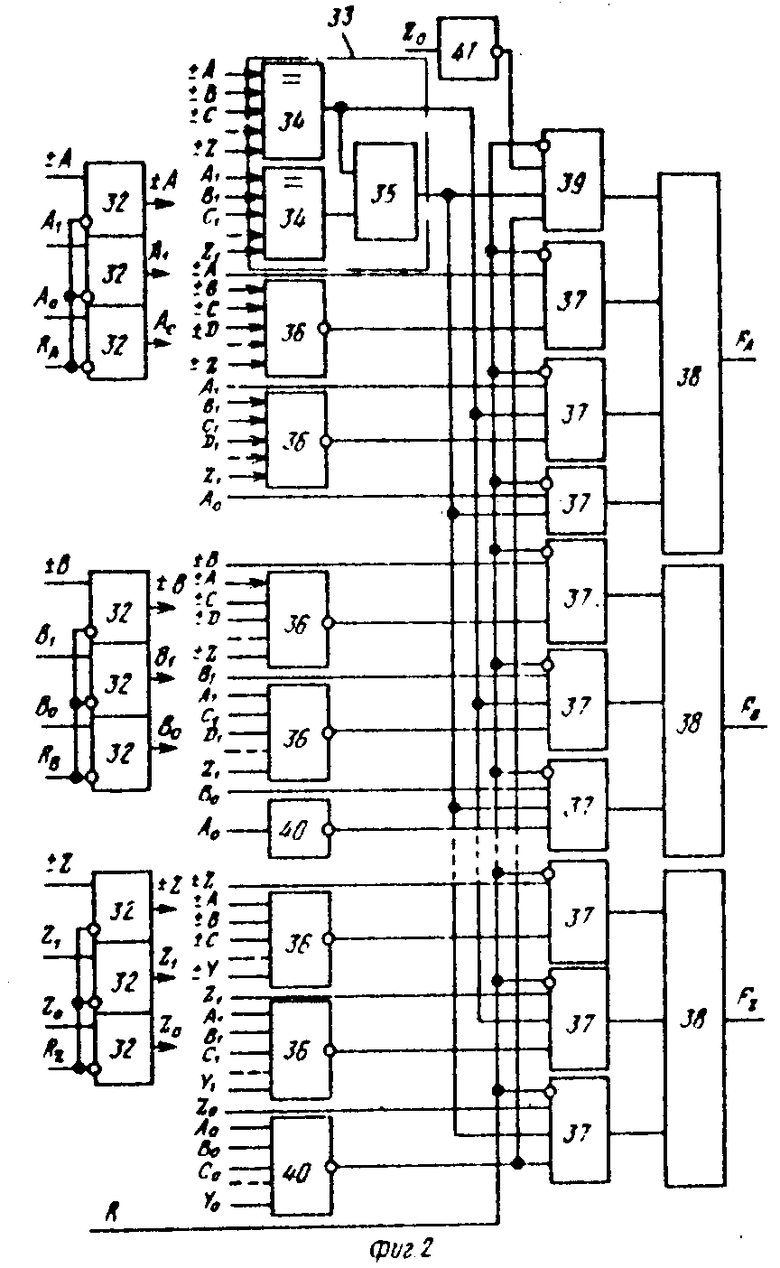

Логический блок 23 формирования приоритетного сигнала включения имеет (фиг. 2) N двоичных M-разрядных информационных входов, подключенных к элементам И 32, при этом первый разряд кода и соответствующий ему проводник является знаковым, остальные представлены для положительных чисел прямым кодом, для отрицательных обратным. На фиг. 2 М=3 и код, например для сигнала ПВ, условно обозначен ±ВВ1 В0. Инвертирующие входы элементов И 32 поканально (на фиг. 2 показаны элементы каналов А, В и Z) объединены с входами RA.RZ раздельной установки нулей. Выходы элементов соединены с входами фиксатора 33 последовательного равенства старших разрядов с (М-1) выходами равенства соответственно знаков; знаков и старших разрядов; знаков, старших разрядов и следующих разрядов и т.д. который состоит из (М-1) элементов сравнения 34 и (М-2) элементов И 35, а также соединены с входами (N-1) входовых элементов ИЛИ-НЕ 36 и соединены с неинвертирующими входами верхних в каждом канале элементов И 37, число которых в каждом канале определяется числом разрядов М. К неинвертирующим входам вторых по каналам элементов И 37 подключен первый выход фиксатора 33, к выходам третьих второй выход и т.д. единственные инвертирующие входы всех элементов И 37 объединены с R-входом общей установки нуля, а выходы элементов ИЛИ-НЕ 36 соединены по одному с соответствующими свободными входами элементов И 37. Выходы последних элементов поканально соединены с входами M-входовых выходных элементов ИЛИ 38, из которых первый с выходом FA имеет дополнительный вход с элементом И 39 в его цепи. К входам последних по каналам элементам И 37, начиная с канала В, подключены выходы элементов ИЛИ-НЕ 40 с числом входов 1 в канале В и с линейным нарастанием до N-1 в канале Z. Самый младший разряд Z0 последнего канала через инвертор 41 подключен к входу элемента И 39, остальные входы которого соединены соответственно с выходом последнего элемента ИЛИ-НЕ 40 и последним выходом фиксатора 33.

Электрические нагрузки преобразователей и потребителей-источников измеряются однотипными датчиками 9,31 (фиг.1) с одинаковыми коэффициентами передачи, поэтому их выходные сигналы PA.PZ, Pп пропорциональны мгновенным значениям соответствующих входных величин и получаются приведенными в масштаб сигналов задания PA.PZ. Принято, что используются датчики мощности, хотя в равной мере могут быть использованы датчики тока или другого типа. Для упрощения графических построений импульсы мощности синусоидального напряжения заменены прямоугольными с амплитудой Pм при условии равенства средних за период напряжения сети значений

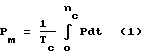

При отключенных тиристорах 1 на вход интегратора 6 поступает сигнал задания P>0 и за период сети выходной сигнал σ увеличивается с начального значения s0 на величину Δот а при включенных сигнал (P-Pм)<0 и выходной сигнал уменьшается на величину Δвк

где Т постоянная времени интегрирования интегратора 6. С генератора 11 тактовый импульс на измерительный блок 10 поступает в конце импульсного интервала, оттуда без задержки на тактовый вход регистра 14, который записывает и сразу же передает на свой выход кодовый сигнал с выхода регистра памяти тактируемого аналого-цифрового преобразователя 12, который все еще хранит значение σo выхода интегратора 6 в начале данного импульса интервала. Чуть позже тактовый импульс, задержанный элементом задержки 13, фиксирует на выходе аналого-цифрового преобразователя 12 значение σ1 выхода интегратора 6 в конце этого же импульсного интервала, и на выходе сумматора 15 с одним инвертирующим входом формируется сигнал приращения выходного сигнала 6 за последний импульсный интервал

Знаковый выход сумматора 15 подключен к противофазным входам управления V регистров 16, 17 так, что при положительном выходе сумматора разрешается запись модуля приращения Δот в регистр 17, что и осуществляется тактовым импульсом после его некоторой задержки элементом задержки 18, а при отрицательном модуля приращения Δвк в регистр 16. На выходе сумматора 21 суммируются оба модуля и формируется выходной сигнал всего измерительного блока 10, пропорциональный амплитуде электрической нагрузки преобразователя

С выхода регистра 17 снимается сигнал модуля приращения Δот выходного интегратора, который, как следует из формулы (2), пропорционален сигналу P задания всего преобразователя. Интегрирующая релейная обратная связь с замкнутым контуром из элементов 6,8,9 стабилизирует среднее значение мощности преобразователя на заданном уровне, что осуществляется изменением скважности импульсного регулирования.

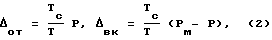

где Тц время цикла повторения диаграммы электрической нагрузки преобразователя, tвк время включенного состояния тиристоров 1 за цикл. При несоответствии электрической нагрузки преобразователя заданию на входе интегратора 6 появляется постоянная составляющая ошибки регулирования (Р-р), которая интегрируется и накапливается в выходном сигнале интегратора σ (фиг.3). Поэтому этот сигнал пропорционален избытку или недостатку электроэнергии нагрузки преобразователя к любому рассматриваемому промежутку времени. Когда сигнал s на выходе интегратора 6 и входе релейного элемента 8 достигает порогов переключения последнего, то он переключается и соответственно включает или отключает тиристоры 1. Ширина петли гистерезиса релейного элемента 8 задана достаточно большой, что делает период собственного цикла работы преобразователя достаточно большим (десятки и сотни периодов Тс). Однако внутри этой петли гистерезиса положительными и отрицательными импульсами, подаваемыми на второй вход суммирующего элемента 7, можно переключать релейный элемент 8 и тиристоры 1 с гораздо большей частотой, что и осуществляется общей частью схемы управления.

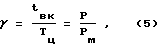

Для повышения энергетических показателей энергосистемы при параллельной работе произвольных потребителей-источников 3 и группы преобразователей с различными изменяющимися амплитудами электрических нагрузок Pм [измерение которых в виде сигнала (4) на выходе сумматора 21 описано выше] с помощью специального датчика 31 формируют сигнал Pп колебаний его электрической нагрузки на ближайшем импульсном интервале работы и определяют для этого интервала пороговое значение согласно рекуррентной формуле

где К1, К2 первый и второй коэффициенты ослаблений; S0 пороговое значение для последнего интервала, Iмi(icвкл0) амплитуды электрических нагрузок, включенных на последнем интервале.

Выполнение датчика 31 не принципиально. Он может быть выполнен в виде любого дифференцирующего звена (RC-цепь). В схеме на фиг.1 сигнал, пропорциональный пороговому значению (6), формируется на выходе сумматора 30. Действительно, сигналы Δот и Pп непосредственно поступают на его входы с измерительных блоков 10 и датчика 31, с выхода старших разрядов сумматора 29 поступает сигнал Σσ умножение которого на коэффициент ослабления К, осуществляется недоиспользованием младших разрядов и соответствующим сдвигом (1 разряд К=-1/2, 2 разряда К1=1/4, 3 разряда К11/8 и т.д.). Аналогичным способом путем использования только старших разрядов выхода регистра 28 осуществляется умножение на коэффициент К2 сигнала, подаваемого на нижний вход сумматора 30, этот сигнал пропорционален величине последнего двучлена формулы (6), что объясняется ниже.

Пороговое значение S1 (6) определяет рекомендуемую величину суммарной амплитуды электрической нагрузки всей группы преобразователей на ближайшем интервале. Действительно, сигнал SDот определяет среднюю электрическую нагрузку всей группы, так как каждое значение Δот пропорционально средней нагрузке каждого преобразователя (Z), сигналы Pп определяют колебания электрической нагрузки прочих потребителей, которые надо компенсировать или повторить (в случае источников), сигнал Σσ определяет общую пере- или недополученную энергию всей группы, потому что это же определяет сигнал s каждого преобразователя, и эту накопленную ошибку надо скомпенсировать, последний член представляет собой ошибку выполнения аналогичной рекомендации на последнем импульсном интервале и ее надо также скомпенсировать на ближайшем импульсном интервале. При К1 > 1 и К2 >1 в схеме на фиг.1 возникают неустойчивые режимы, поэтому принимается, что К1≅ 1, К2≅1.

В функции сигналов s интеграторов 6 логическим блоком 23 формируются последовательно приоритетные сигналы F включения преобразователей. Если, например, первоначально высший приоритет имеет преобразователь А, то появляется сигнал "1" только на выходе FA логического блока 23, который сразу поступает на нижний вход управления V мультиплексора 26 при сигнале "0" на верхнем входе управления. При этом мультиплексор 26 подключает на выход сигнал амплитуды электрической нагрузки PМА преобразователя А с верхнего входа "2", в котором не использован один младший разряд, что эквивалентно делению сигнала на два. На все входы управления остальных мультиплексоров 26 поступают нулевые сигналы и выходы их отключены. В сумматоре 27 происходит сравнение половины указанной амплитуды с сигналом порогового значения S1, который поступает на инвертирующий вход. Если пороговое значение больше, то на знаковом выходе (±) сумматора 27 сигнал "0", который поступает на вход общей установки нуля R логического блока 23, что никак не влияет на его работу. Через интервал задержки элемента 24 импульс с выхода логического блока 23 поступает на S-вход установки единицы триггера 25, что приводит к появлению сигнала "1" на втором верхнем входе управления V мультиплексора 26. При этом его выход подключается к его нижнему входу "1" и сигнал PМА поступает на выход мультиплексора 26 и вход сумматора 27 без ослабления. Одновременно с формированием сигнала "1" на выходе триггера 25 этот сигнал поступает на второй вход сумматора 7 преобразователя А, включая этим его релейный элемент 8 и тиристоры 1 на ближайшем интервале, и на вход RА раздельной установки нуля в канале А логического блока 23. При этом формируется сигнал FА=0 и появляется "1" на выходе следующего по приоритету канала, например FZ1 и т.д. При поступлении на вход сумматора 27 очередного сигнала половины амплитуды электрической нагрузки PМ какого-то преобразователя на знаковом выходе (±) появится сигнал "1", и из-за поступления его на вход R логического блока 23 все его выходы будут обнулены и описанный процесс остановится. При этом рекомендуемое значение электрической нагрузки на ближайшем импульсном интервале S, будет выполнено с точностью до половины амплитуды последнего по приоритету преобразователя в большую или меньшую сторону. На выходе сумматора 27 после этого будет сформирован сигнал ошибки выполнения рекомендации на ближайшем интервале. При поступлении тактового импульса с генератора 11 этот сигнал записывается в регистре 28 и хранится до конца интервала, где будет использован при формировании нового сигнала порогового значения (6). Перед началом этого нового процесса импульсом со среднего выхода генератора 11 происходит установка в "0" всех триггеров 25.

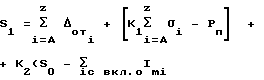

Устройство может работать при различных функциях формирования приоритетных сигналов включения. В конкретной схеме (фиг.1) это определяется выполнением элементов 19, 20, 22, 23. Здесь на входах элемента сравнения 19 сравниваются величины Dот и Δвк, выходной сигнал в виде "0" или "1" поступает на вход управления мультиплексора 20, который таким образом подключает к своему выходу меньшее из двух значений Δот и Δвк Полученный сигнал Δмин вместе с сигналом σ аналого-цифрового преобразователя поступает на входы делителя и делимого блока 22, на выходе которого и формируется сигнал данной функции

где i= A,B,C,Z, K3i K3A, K3B, K3Z - индивидуальный для каждого преобразователя коэффициент, задаваемый однажды в зависимости от динамических свойств нагревательных установок с нагрузками 2 (у малоинерционных установок коэффициент больше, чем у инерционных). Сигналы поступают на информационные входы логического блока 23 в виде соответствующих кодов.

Логический блок 23 формирования приоритетного сигнала включения (фиг. 2) формирует на своем одном выходе, например, сигнал 1, если либо код ПВ±ВВ1В0 самый большой из ПА, ПВ, ПZ, либо больше ПА± АА1А0 и больше или равен ПС, ПD,ПZ (в соответствии с порядковой нумерацией преобразователей). С учетом того, что для отрицательных чисел применен обратный код, а знаку + соответствует 1, при десятичном представлении доприоритетных сигналов 3.-0, +0.+3, на вход устройства (фиг.2) поступают двоичные коды 000,001,010,011,100,101,110,111 с линейной возрастающим модулем независимо от знака. Код может быть самым большим, либо когда ± B=1, ±А=±С=±Z=0, тогда формируются сигналы 1 на выходе первого верхнего элемента ИЛИ-НЕ 36 в канале В, на выходе соответствующего элемента И 37 и на выходе FB, либо когда ±A= ±B ±Z= 0, В11,А1=С1Z1=0, тогда сигналы "1" формируются на выходах вторых элементов 36 и 37 в канале В при сигнале "1" на первом выходе фиксатора 33 и на выходе FB, либо при ±A=±B±Z, A1=B1=Z1, A0=0, B0=1 и произвольных оставшихся младших разрядов в других каналах, тогда сигналы "1" формируются на выходах третьих элементов 36 и 37 в канале В при сигнале "1" на втором выходе фиксатора 33 и на выходе FB. Когда во всех каналах все разряды равны нулю формируется сигнал "1" на выходе элемента И 39 и соответственно на выходе FA. При сигнале R=1 на выходах всех элементов И 37 и И 39 формируются нулевые сигналы и такое же значение принимают все выходные сигналы. При подаче сигнала 1 на какой-то вход раздельной установки нуля, например RB,соответствующий входной код обнуляется на выходах элементов И 32 этого канала и, если до подачи было FВ=1, то после подачи получается FВ=0, а сигнал "1" появляется на выходе канала со следующим меньшим по величине кодом.

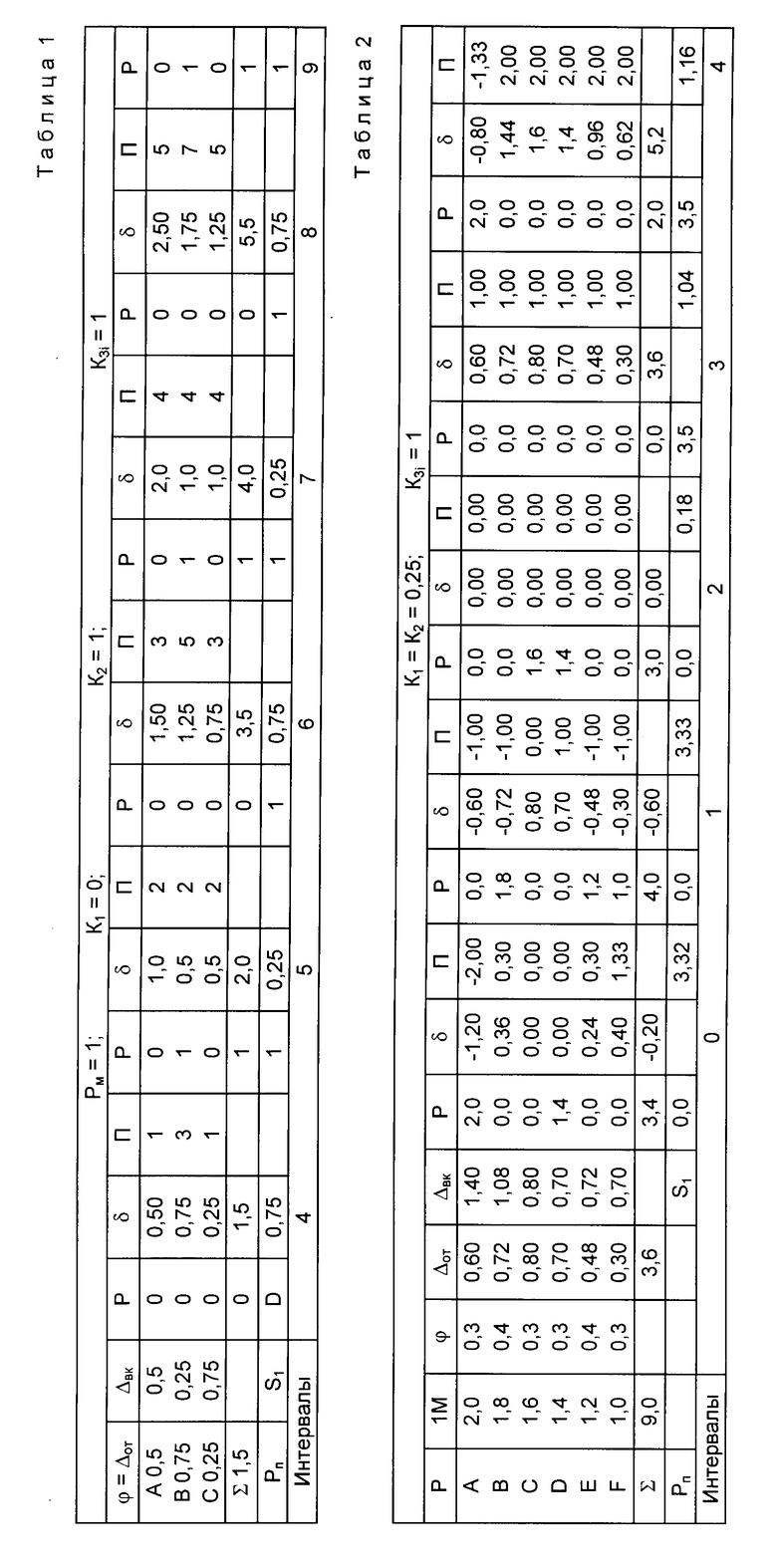

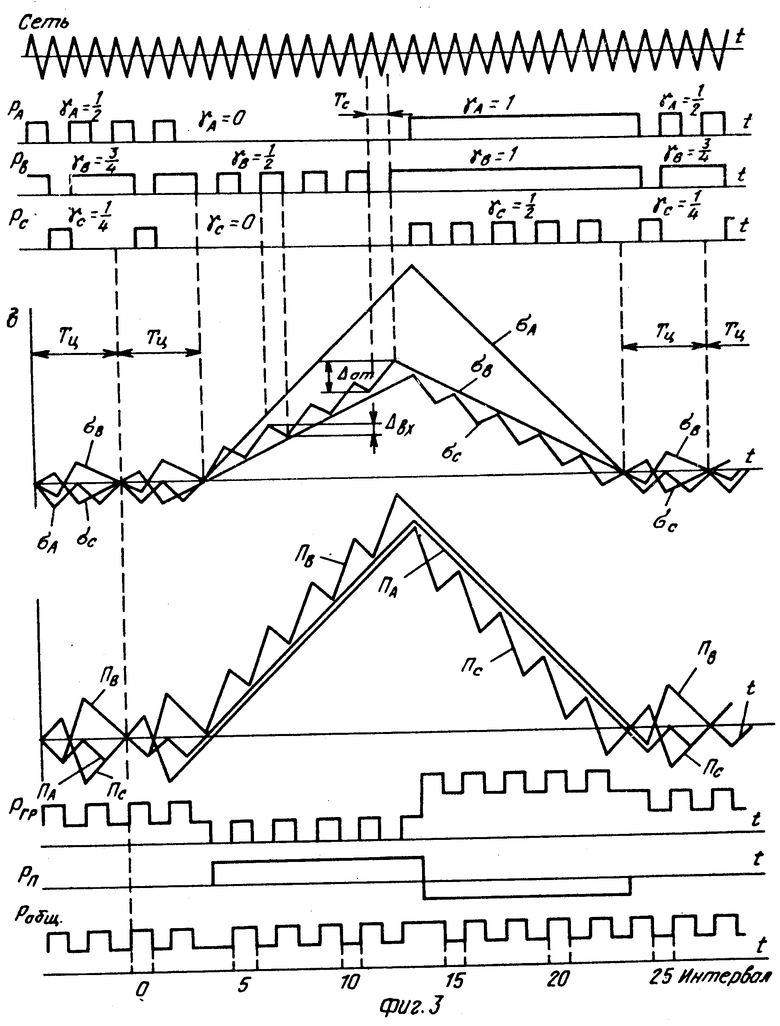

В табл. 1 и на фиг.3 приведен пример управления группой из трех преобразователей (фиг.1) при одинаковых амплитудах, когда параллельно работающий потребитель-источник 3 с графиком Pп является потребителем электроэнергии и для энергосистемы необходимо сгладить график общего потребления мощности Pобщ.

Например, в конце 4-го интервала по формуле (6)

S=(0,5+0,75+0,25) + [0(0,5+0,75+0,25)-1]+1•(0,25-0)=0,75

Первым на 5-м интервале проверяется на включение преобразователь В, имеющий старшее значение функции приоритета, равное 3. Половина амплитуды равна 0,5 и разность с пороговым значением 0,5-0,75 <0, значит преобразователь В включается на 5-м интервале. Следующий по приоритету идет преобразователь А, приоритет при равенстве с C приоритетных функций определяется порядковой нумерацией преобразователей. На этот раз результат сравнения амплитуды преобразователя А 1,5-0,75 >0, и преобразователь А и остальные не включается на 5-м интервале.

Согласно данному способу при любой приоритетной функции П все сигналы этих функций всех преобразователей изменяются одновременно и с погрешностью, определяемой только дискретностью регулирования, всегда совпадают (фиг.3), тогда как графики сигналов σ расходятся. Однако скорости изменения последних не могут превышать скоростей, определяемых приращениями Dот и Δвк, соответствующих режимам полного отключения и включения (2). В средней части графиков σ на фиг. 3 этим граничным режимам соответствуют прямые линии на большом временном интервале. Как видно из фиг.3, показанный на этом примере режим является предельным для компенсации выбранной амплитуды сигнала Pn. При большей амплитуде на участке нарастания графиков s при набросе нагрузки Pп преобразователи А и С уже полностью отключились, а кривую графика общего тока группы Pгр можно было бы еще понизить за счет уменьшения нагрузки преобразователя В до его полного отключения. Но тогда кривая sв поднимается слишком высоко и на втором участке компенсации (при сбросе нагрузки Pп и снижении кривой графиков σ, преобразователь может только полностью включиться, темп спада кривой графика sв получается небольшим и невозможно будет одновременное пересечение нулевой линии всеми кривыми σA...σC как это получилось на фиг. 3 при ограничении снизу мощности PВ на участке нарастания графика σв Таким образом, предложенная функция (7) определения приоритета по результатам интегрирования σ обеспечивает равномерно возможное участие всех преобразователей в компенсации колебаний нагрузки произвольных потребителей во всех режимах. Более интенсивная компенсация на каком-то участке режима возможна, но при этом могут возникнуть трудности в компенсации на других участках. Из предельного режима работы на фиг.3 можно определить также допустимые ограничения на амплитуду сигнала Pп в формуле (6)

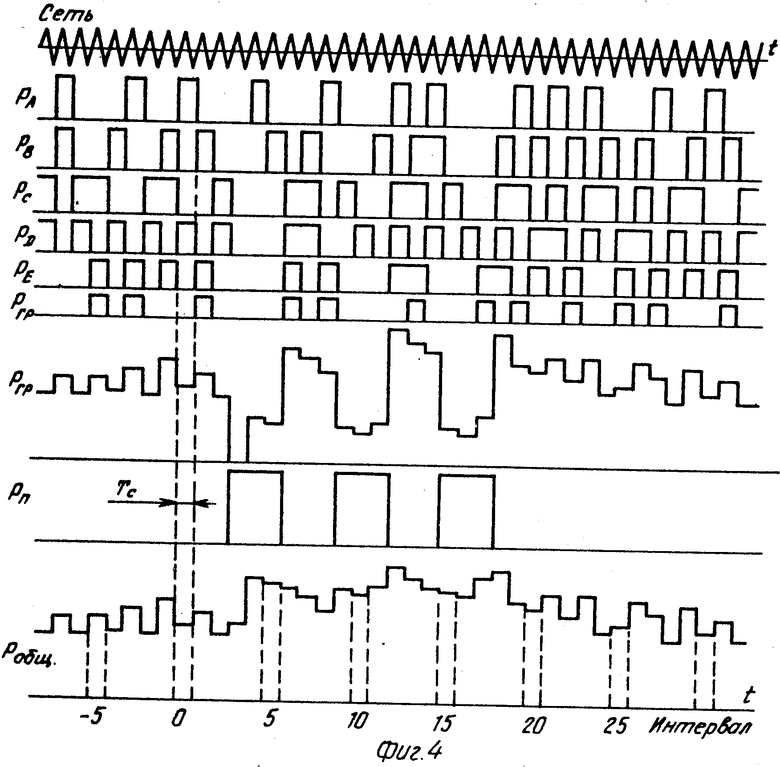

В табл. 2 и на фиг.4 приведен пример управления группой из шести преобразователей с разными амплитудами при работе потребителя-источника 3 в режиме потребителя, когда требуется сгладить график общей нагрузки Pобщ колебаниями нагрузки всей группы Pгр.

Тогда потребитель-источник является специальным источником электроэнергии и требует сложного графика потребителя энергии (ветроэлектростанции, солнечные батареи), датчик 31 (фиг. 1) формирует сигнал Pп требуемой формы и колебания электрической нагрузки всей группы Pгр повторяют форму этого сигнала. Например, в случае солнечных батарей снижает нагрузку, когда солнце ненадолго закрывается облаком, и компенсирует недополученную энергию, когда облако уйдет. При этом сама система (фиг.1) поддерживает среднее потребление энергии каждым преобразователем на заданном уровне. В мощных энергосистемах при возникновении колебательных перетоков мощностей датчик 31 (фиг.1) может формировать стабилизирующий сигнал, который по форме будет повторяться общей нагрузкой всех преобразователей, повышая этим динамическую устойчивость энергосистемы.

Таким образом, предлагаемый способ может быть применен в устройствах управления группами импульсных преобразователей как при их самостоятельной работе, так и при параллельной работе с потребителями-источниками с резко переменной нагрузкой, обеспечивая высокие энергетические показатели и динамическую устойчивость всей энергосистемы при удовлетворении технологическим требованиям нагрузки каждого преобразователя.

| название | год | авторы | номер документа |

|---|---|---|---|

| РАДИОЛОКАЦИОННАЯ СТАНЦИЯ | 1993 |

|

RU2037842C1 |

| МНОГОФАЗНЫЙ СЧЕТЧИК ЭЛЕКТРИЧЕСКОЙ ЭНЕРГИИ | 1994 |

|

RU2099718C1 |

| Линейное устройство коррекции межсимвольной интерференции | 1984 |

|

SU1256213A1 |

| Способ управления группой импульсных преобразователей | 1981 |

|

SU1020958A1 |

| Функциональный преобразователь | 1985 |

|

SU1249547A1 |

| БЫСТРОДЕЙСТВУЮЩИЙ МНОГОФУНКЦИОНАЛЬНЫЙ ПРЕОБРАЗОВАТЕЛЬ УГЛА В КОД ДЛЯ УСТРОЙСТВ ЭЛЕКТРОМЕХАНОТРОНИКИ | 1994 |

|

RU2094945C1 |

| РЕВЕРСИВНЫЙ ЧИСЛО-ИМПУЛЬСНЫЙ АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ | 2009 |

|

RU2429563C1 |

| Устройство для отображения информации | 1987 |

|

SU1513507A1 |

| Устройство для определения коэффициентов разложения корреляционной функции по системе ортонормированных базисных функций | 1985 |

|

SU1287196A1 |

| ЦИФРОВОЙ СИНТЕЗАТОР ЧАСТОТ | 1991 |

|

RU2030092C1 |

Изобретение относится к электротехнике и предназначено для управления тиристорными импульсными преобразователями переменного напряжения при их групповом применении.

Целью изобретения является повышение энергетических показателей и динамической устойчивости. Электрические нагрузки преобразователей и потребителей измеряются датчиками 9 и 31. С генератора 11 тактовый импульс поступает на измерительный блок 10. При несоответствии электрической нагрузки преобразователя заданию на входе интегратора 6 появляется постоянная составляющая ошибка регулирования, которая интегрируется и накапливается в выходном сигнале интегратора фильтра низших частот 6. Когда сигнал на выходе интегратора и входе релейного элемента 8 достигает порога переключения последнего, то он переключается и соответственно включает или отключает тиристоры 1. Для повышения энергетических показателей с помощью датчика 31 формируют сигнал колебаний его электрической нагрузки и ближайшем импульсном интервале работы и определяют для этого интервала порога все значение, пропорционально которому формируется сигнал на выходе сумматора 30. В функции сигналов интеграторов, логическим блоком 23 формируются приоритетные сигналы включения преобразователей, которые поступают на вход мультиплексора 26. С выходов мультиплексоров сигналы поступают в сумматор 27, где происходит их сравнение с пороговым сигналом. С выхода сумматора 27 сигнал поступает в регистр 28 и хранится до конца интервала, где будет использован при формировании нового сигнала. 1 з.с.п. ф-лы, 4 ил.

| СПОСОБ УПРАВЛЕНИЯ ГРУППОЙ ИМПУЛЬСНЫХ РЕГУЛЯТОРОВ | 0 |

|

SU377752A1 |

| Кипятильник для воды | 1921 |

|

SU5A1 |

| СПОСОБ СИНХРОНИЗИРОВАННОГО УПРАВЛЕНИЯ ШИРОТНО- ИМПУЛЬСНЫМ РЕГУЛЯТОРОМ | 0 |

|

SU395826A1 |

| Кипятильник для воды | 1921 |

|

SU5A1 |

| Способ управления группой импульсных преобразователей | 1981 |

|

SU1020958A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

Авторы

Даты

1997-12-10—Публикация

1983-09-27—Подача