Изобретение относится к радиотехнике, импульсной и вычислительной технике и может быть использовано в синтезаторах частот приемопередающей и измерительной аппаратуры.

Цель изобретения повышение верхней рабочей частоты при одновременном увеличении точности детектирования.

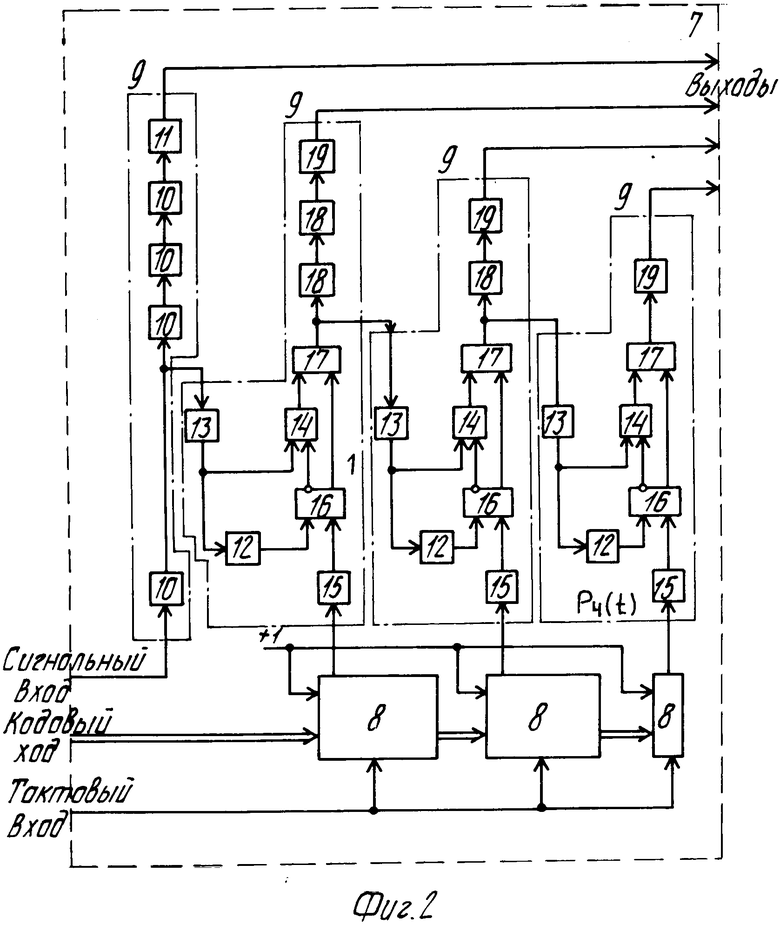

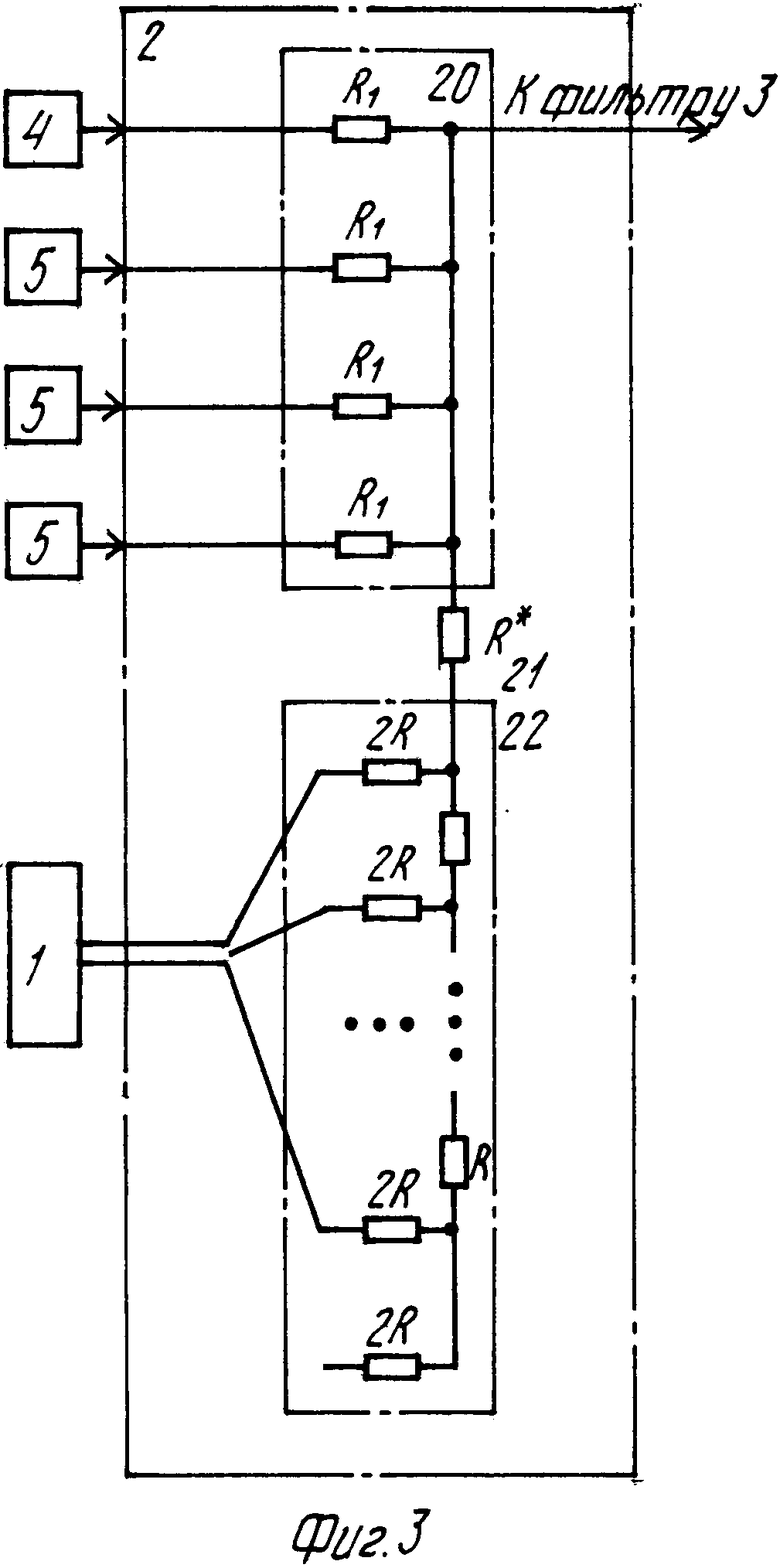

На фиг. 1 представлена функциональная блок-схема предлагаемого многочастотного фазоцифрового детектора; на фиг. 2 функциональная схема одного из фазорасщепителей, входящих в состав многочастотного фазоцифрового детектора; на фиг. 3 принципиальная электрическая схема цифроаналогового преобразователя, входящего в состав многочастотного фазоцифрового детектора.

Предлагаемый многочастотный фазоцифровой детектор содержит первый тактируемый сумматор 1, цифроаналоговый преобразователь 2, фильтр 3 нижних частот, первый RS-триггер 4, К-1 дополнительных RS-триггеров 5, первый 6 и второй 7 фазорасщепители. При этом второй фазорасщепитель 7 содержит К-1 последовательно соединенных тактируемых сумматоров 8, К последовательно соединенных цепей 9 потактовой задержки импульсов переполнения, первая из которых содержит К последовательно соединенных элементов 10 потактовой задержки и первый формирователь 11 импульсов с задержкой на один такт. А каждая последующая i-я цепь 9 потактовой задержки импульсов переполнения содержит первый 12, второй 15 и третий 19 формирователи импульсов с задержкой на один такт, первый элемент 13 потактовой задержки, элемент И 14, RS-триггер 16, элемент ИЛИ 17, K-i элементов 18 потактовой задержки. Цифроаналоговый преобразователь 2 содержит резистивную матрицу 2N-R 20, резистор связи 21 и резистивную матрицу R-2R 22.

Детектор работает следующим образом. В результате тактирования сумматора 1 опорной последовательностью импульсов он формирует ступенчатую пилообразную функцию. Выходы старших разрядов тактируемого сумматора 1 соединены с входами второго фазорасщепителя 7, а выходы младших разрядов тактируемого сумматора соединены со входами цифроаналогового преобразователя 2. Импульс переполнения с выхода тактируемого сумматора 1 поступает на сигнальный вход второго фазорасщепителя 7. Первый выход второго фазорасщепителя 7 соединен с S-входом RS-триггера 4, поэтому сформированный на этом выходе импульс устанавливает данный триггер в состояние "1". На R-вход триггера поступают импульсы с одного из выходов первого фазорасщепителя 6, который может быть выполнен в виде кольцевого счетчика импульсов. Кольцевой счетчик импульсов осуществляет также деление частоты сигнальной последовательности импульсов. Импульсы, поступающие на кодовый вход второго фазорасщепителя 7, т.е. на последовательно соединенные тактируемые сумматоры 8, сдвигаются по фазе путем суммирования с единицей. Цепи потактовой задержки импульсов переполнения необходимы для формирования импульсов, задержанных на определенное время.

Резистивная матрица 2N-R 20 преобразует поступающие на ее вход импульсы в аналоговый эквивалент, к которому через резистор связи 21 добавляется другой аналоговый эквивалент, получаемый от импульсов младших разрядов накапливающего сумматора 1 с помощью резистивной матрицы R-2R 22. Фильтр 3 нижних частот подавляет аналоги пилообразных составляющих, а аналог постоянной составляющей, пропорциональный эквивалентной разности фаз опорной и сигнальной импульсных последовательностей, проходит на выход детектора и может быть использован для управления частотой генератора, работающего, например, в кольце ФАПЧ. По сравнению с прототипом аналоги импульсов передаются на вход фильтра 3 нижних частот с весовым отношением 1/K. С помощью резистора связи 21 такой же уровень устанавливается для аналогового эквивалента функции младших разрядов. Эффект деления частоты в устройстве не проявляется, поскольку каждый из импульсов исходной импульсной последовательности проходит на соответствующий триггер, выполняющий роль фазового детектора. Благодаря этому в К раз повышается частота помехи, а уровень ее в К раз уменьшается, т.е. улучшаются условия фильтрации этой помехи фильтром 3 нижних частот. За счет этого может быть расширена полоса пропускания петли автоподстройки того устройства, в котором используется настоящий многочастотный фазоцифровой детектор. В принципе не обязательно выбирать К равным 2N. Оно может быть любым целым числом. При этом необходимо выполнить условие, чтобы на одном из входов каждого дополнительного тактируемого сумматора число, с помощью которого производится сдвиг по времени всех процессов, было равно q/K. Случай К= 2N предпочтителен как наиболее простой в реализации. В качестве элементов 10, 13, 18 потактовой задержки могут быть использованы D-триггеры, а в качестве формирователей 11, 12, 15 и 19 импульсов с задержкой на один такт могут быть использованы D-триггеры, у которых выход связан со входом установки в "0" через цепочку из четного числа инверторов, суммарное время задержки которых и составляет длительность сформированных импульсов. В этом случае каждый из упомянутых элементов потактовой задержки и формирователей импульсов должен иметь тактовый вход, соединенный с опорным входом детектора.

Число "а", поступающее на вход детектора (фиг. 1), является по существу сигналом управления, необходимым для перестройки частоты настройки фазового детектора. Достоинство предлагаемого детектора заключается в увеличении в К раз верхней рабочей частоты.

В отличие от прототипа, который рассчитан на работу с двоичным ЦАП, использующим резистивную матрицу R-2R и для которого реализация линейности при удовлетворительном быстродействии затруднительна, в настоящем детекторе используется цифроаналоговый преобразователь, имеющий в своем составе две резистивные матрицы 20 и 22. Старшие разряды преобразователя построены таким образом, что вес каждого из разрядов составляет 1/K от раствора амплитудно-кодовой характеристики преобразователя. Младшие двоичные разряды сопряжены со старшими так, чтобы их суммарный вклад равнялся весу одного старшего разряда. При увеличении числа К повышается линейность цифроаналогового преобразователя 2, а следовательно, повышается точность детектирования и снижается уровень помех дробности.

В случае использования другого второго фазорасщепителя 7, например кольцевого счетчика импульсов, удается лишь повысить точность детектирования при соответствующем снижении помех дробности. Повысить же верхнюю рабочую частоту фазоцифрового детектора нельзя, так как при таком упрощении второго фазорасщепителя 7 он будет расщеплять фазу на целые периоды следования импульсов переполнения. Предложенное выполнение фазорасщепителя позволяет расщеплять фазу импульсов переполнения без снижения их средней частоты следования, т. е. в этом более сложном блоке фазa расщепляется на доли периода следования импульсов переполнения.

(56) Авторское свидетельство CCCР N 1109872 А, кл. H 03 D 13/00, 05.12.81.

| название | год | авторы | номер документа |

|---|---|---|---|

| Синтезатор частот | 1987 |

|

SU1431034A1 |

| Цифровой фазовый детектор | 1982 |

|

SU1149394A1 |

| Устройство фазовой подстройки частоты | 1982 |

|

SU1251322A1 |

| Цифровой фазовый детектор для синтезаторов частот | 1988 |

|

SU1539677A1 |

| Цифровой фазовый детектор | 1982 |

|

SU1068838A1 |

| Цифровой фазовый детектор | 1985 |

|

SU1352638A2 |

| Устройство для цифрового фазового детектирования импульсных последовательностей на неравных частотах | 1981 |

|

SU1109872A1 |

| Синтезатор частот | 1986 |

|

SU1337990A1 |

| Цифровой фазовый детектор | 1980 |

|

SU875303A1 |

| Синтезатор частот | 1982 |

|

SU1117839A1 |

Изобретение относится к радиотехнике. Цель изобретения повышение верхней рабочей частоты при одновременном увеличении точности детектирования. Детектор содержит тактируемый сумматор 1, ЦАП 2, фильтр 3 нижних частот, RS-триггеры 4 и 5 и фазорасщепители 6 и 7. Опорная последовательность импульсов преобразуется сумматором 1 и фазорасщепителем 7 и поступает на RS-триггеры 4 и 5, куда поступает также преобразованная фазорасщепителем 6 сигнальная последовательность импульсов. Полученные сигналы поступают через ЦАП 2 на фильтр 3. Он подавляет аналоги пилообразных составляющих, а аналог постоянной составляющей, пропорциональный эквивалентной разности фаз опорной и сигнальной импульсных последовательностей, проходит на выход детектора и может быть использован для управления частотой генератора. Цель достигается за счет улучшения условий фильтрации помехи фильтром 3 путем повышения частоты помехи в K раз и уменьшения ее уровня в K раз. Детектор по пп. 2 4 ф-лы отличается выполнением фазорасщепителей 6 и 7, ЦАП 2. 3 з.п. ф-лы, 3 ил.

| Устройство для цифрового фазового детектирования импульсных последовательностей на неравных частотах | 1981 |

|

SU1109872A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1995-07-25—Публикация

1988-05-10—Подача