Изобретение относится к импульсной технике, может быть использован в устройствах кодирования, передачи данных и технике связи. В частности устройство может быть использовано в сис.темах цифровой компрессии стан дартного телевизионного видеосигнала методами адаптивной дельта-модуляции ДАДМ) и дифференциальной импульсно-кодовой модуляции ( ДИКМ. Известны устройства, содержащие сумматор-вычитатель и регистр, поразрядные входы которогоподключены к гГоразрядным выходам сумматора-вычитателя, а его первые и вторые входы соединены соответственно с входом устройства и выходом регистра 1.

; В данных устройствах на регистре с помощью сумматора-вычитателя накапливается последовательность положительных и отрицательных кодовых приращений. Однако эти устройства не обеспечивают экспоненциального преобразования накапливаемой суммы, что приводит к ухудшению помехоус тойчивости при использовании устройства в качестве петли обратной связ В системах передачи с адаптивной дельта-модуляцией и дифференциально импульсно-кодовой модуляцией.

Известен преобразователь кода, обеспечивающий экспоненциальное преобразование накапливаемой последовательности различных по знаку и амплитуде параллельных кодовых приращений, причем экспоненциальный :спад стремится к среднему значению UOP 2.

Однако быстродействия устройства недостаточно для работы в системах -цифровой компрессии стандартного телевизионного видеосигнала.

Целью изобретения является повышение быстродействия преобразования кода за счет сокращения времени экспоненциальной обработки накапливаемой суммы параллельных кодовых приращений.

Указанная цель достигается тем, что в преобразователь кода, содержащий сумматор-вычитатель, триггер, первый и второй управляемые инверторы, управляющие входы которых подключены к выходу триггера, первый вход которого подключен к шине тактовых импульсов, а второй - к выходу старшего разряда сумматора-вычитателя, поразрядные выходы которого подключены к поразрядным входам первого управ1ляемого инвертора, а первые поразрядные.входы подключены к поразрядным выходам второго управляемого инвертора и Выходам устройства, а- вторые поразрядные входы к входам устройства, введены регистй элемент задержки, дополнительный

сумматор-вычитатель и постоянное запоминающее устройство, входы которого подключены к выходам первого управляемого инвертора и вторым входам дополнительного сумматора-вычитателя, первые входы которого подключены к выходам постоянного запоминающего устройстйа, управляющий вход первого управляемого инвертора подключен к управляющему входу дополнительного сумматора-вычитателя и к входу старшего разряда регистра, остальные поразрядные входы которого подключены к выходам дополнительного сумматора-вычитателя а стробирующий

вход через элемент задержки - к шине тактовых импульсов, выход старшего разряда регистра соединен с входом старшего разряда сумматора-вычитателя, остальные выходы регистра

с входами второго управляемого инвертора.

Существенное повышение быстродей-, ствия устройства образуется за счет сокращения времени экспоненциальной обработки накапливаемой суммы поступающих кодовых приращений. В известном преобразователе для экспоненциальной обработки требуются сотни импульсов высокой частоты f, поступающих на суммирующий и вычитающий счетчики до момента совпадения их выходных кодов (окончание цикла обработки) . В предлагаемом устройстве нет необходимости в высокой частоте

5 fy, поскольку введение указанных новых элементов и их определенная . взаимосвязь позволяет производить обработку за один такт. Указанное в известном устройстве ограничение

0 частоты поступления кодовых приращений устранено. Поэтому частота поступления кодовых приращений может быть значительно повышена и она определяется лишь задержкой

5 в элементах схемы, для компенсации которой в устройство введен элемент задержки.

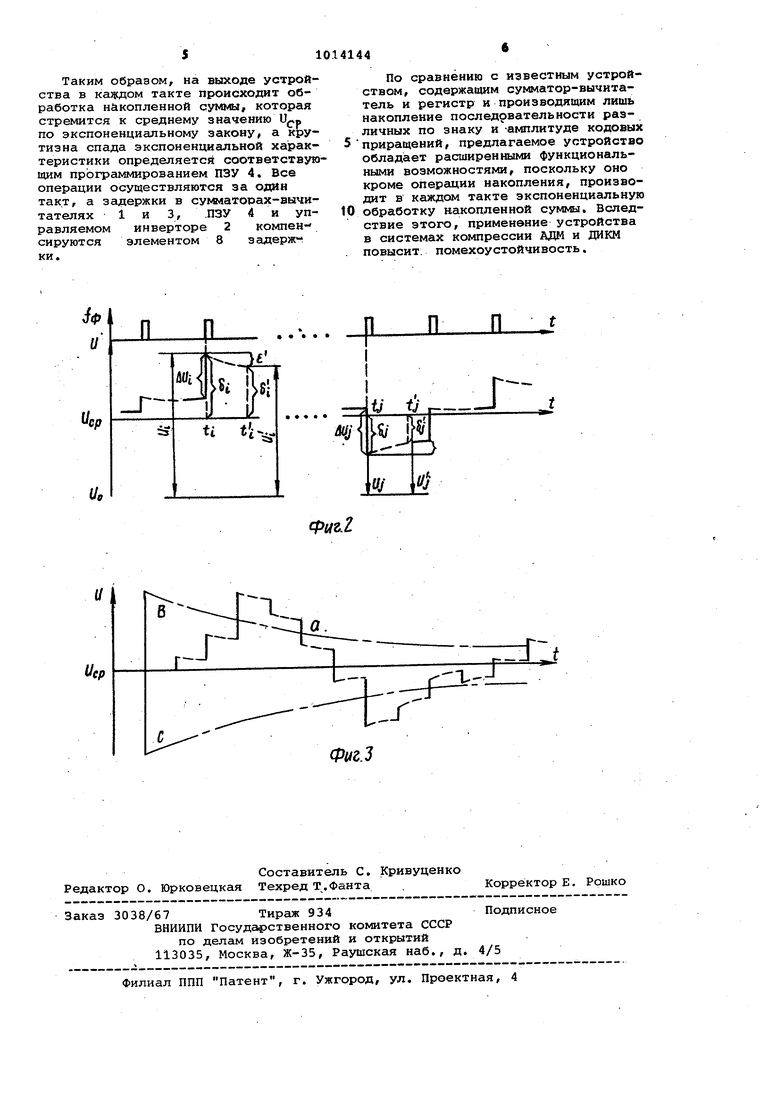

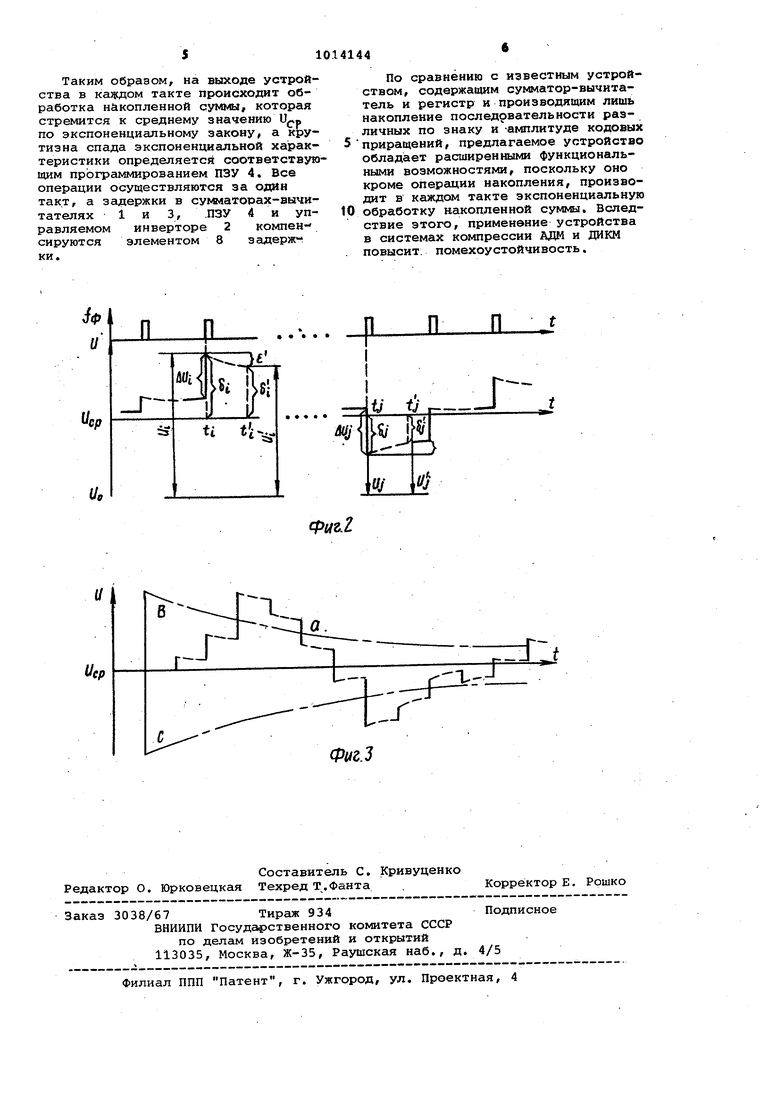

На фиг. 1 представлена структурная схема преобразователя кода; на фиг. 2 и 3 - временные диаграммы его работы.

Преобразователь кода содержит сумматор-вычитатель 1, выходда младших разрядов которого подключены к входам управляемого инвертора 2, а

выхо.цы последнего соединены с вторыми входами дополнительного сумматоравычитателя 3 и входами постоянного запоминающего устройства (ПЗУ 4, а его выходы подключены к первым входгш

0 сумматора-вычитателя 3, управляющий вход которого соединен с входом старшего разряда регистра 5, управляющими входами управляемых инверторов 2 и 6 и выходом триггера 7, инфрр5 мацириный вход которого подключен к выходу старшего разряда сумматора вычитателя 1, а первые и вторые вхо ды сумматора-вычитателя подключены соответственно к входу устройства н выходу управляемого инвертора 6, а входы последнего подсоединены к выходам регистра 5, поразрядные и стробирующий входы которого соедине соответственно с выходаг ш дополните ного сумматора-вычитателя 3 и через элемент 8 задержки - с стробирукщим входом триггера 7, на который подан сигнал тактовой частоты. Устройство работает следующим образом. На первые входы сумматора-вычиталеля 1 поступают параллельные код вые приращения с частотой . Сумматор-вычитатель представляет собой обычный сумматор с комбинационной логической схемой для выполнения операции сложения или вычитания. В каждом такте в зависимости от знака кодового приращения, т.е. 1 или О в знаковом разряде, происходит суммирование или вычитание его из остатка суммы, подающегося на вто рые входы сумматора-вычитателя 1 с выхода устройства. После суммирования осуществляется экспоненциаль:ная обработка с помощью постоянного Запоминающего устройства ( ПЗУ 4, в котором записана экспоненциальная характеристика с заданной крутизной дополнительного сумматора-вычитател 3, элемента 8 задержки регистра 5. На выходе устройства образуется ноиай остаток суммы, обработанный по экспоненциальному закону, причем .экспоненциальный спад стремится к некоторому среднему значению Ц;р . В момент времени ti (фиг. 2) кодово приращение ЛШ суммируется с ранее образованным остатком накопленных приращений. Если новая сумма прев лшает средний уровень Ucp , то высокий потенциал на выходе старшего разряда сумматора-вычитателя 1 .фиксируется триггером 7 и выключает управляемые инверторы 2 и б, и выходы младших разрядов в прямом коде поступают на ПЗУ 4, Триггер 7 и управляемый инвертор 2 подают на ПЗУ 4 абсолютную величину разности К-| |ui - , где Ui - кодовое значение необработанной суммы в момент времени :ti J и - кодовое значение среднего уровня. Указанная величина, поступает на первые входы дополнительного cyvsuaтора-вычитателя 3, а на его вторые входы из ПЗУ 4, в соответствии с входным кодом IdJI, поступает код раз ности i , зависящий от крутизны спада экспоненциальной кривой и представлякхций собой величину, на которую необходимо уменьшить в со- , ответствии с записанным в ПЗУ 4 экс«поненциальнйм .законом обработки. : В соответствии с высоким потенциалом на выходе триггера 7 дополнительный сумматор-вычитатель 3 производит операцию вычитания Idlfl ; (интервал времени tl - ti на фиг.2). Задержанный во время включения вы- ; шеуказанных элементов устройства с помощью элемента 8 задержки импульс тактовой частоты f вписывает в регистр 5 код и высокий потенциал три ггера 7 (старший разряд кода обработанной суммы). В соответствии суправляющим сигналом триггера 7 ; инвертор б пропускает обработанный ; код младших разрядов суммы на выход устройства в неинвертированном виде, а старший разряд снимается непосредственно с соответствующего выхода регистра 5, т.е. на выходе устройства формируется обработанное кодо-. вое значение суммы Ui. Если в момент времени ,-. отрицательное приращение uU.j приведет к тому, что на выходе сумматора-вычитателя 1 новая сумма U; станет меньше среднего уровня (j-p , то низкий потенциал старшего разряда сумматора-вычитателя 1 зафиксируется триггером 7 и включит управляемые инверторы 2 и б.Вследствие этого на ПЗУ 4 и первые входы дополнительного сумматора-вычитателя 3 подается инвертированный код младших разрядов необработанной . суммы, что соответствует абсолютной величине разности )(/j ( |Uj - Uj В соответствии с поданным на вход ПЗУ 4 кодом I cTj ( , на его выходе образуется код , необходимый для получения обработанной по экспоненциальному закону величины I tf} f . Дополнительный сумматор-вычитатель 3 производит операцию сложения-j(/jf + + j I f так как на его управляю- щий вход подан низкий потенциал с триггера 7, Далее указанна величина и низкий потенциал триггера 7 вписываются в регистр 5 и, .пройдя вклюг ченный управляемый инвертор б, на выходе устройства в момент времени t- образуется обработанное значение суммы и/ (фиг. 2) , На фиг, 3 показаны примеры функционирования устройства. Кривая с( отображает пример работы при поступлении на вход устройствапоследовательности различных положительных и отрицательных кодовых приращений. Кривые В и С показывают экспоненциальный характер изменения амплитуды за несколько тактов в случае подачи e ц нoвpeмeнныx положительного и отрицательного приращений, соответст венно.

Таким образом, на выходе устройства в каз4сдом такте происходит обработка накопленной суммы, которая стремится к среднему значению U-p по экспоненциальному закону, а крутизна спада экспоненциальной характеристики определяется соответствующим программированием ПЗУ 4. Все операции осуществляются за один такт, а задержки в су «латорах-вычитателях 1 и 3, .ПЗУ 4 и управляемом инверторе 2 компенсируются элементом 8 задержки.

По сравнению с известным устройством, содержащим сумматор-вычитатель и регистр и производящим лишь накопление последрвательности различных по знаку и -амплитуде кодовых

приращений, предлагаемое устройство обладает расширенными функциональными возможностямиf поскольку оно кроме операции накопления, производит в каждом такте экспоненциальную

обработку накопленной суммы. Вследствие этого, применение устройства в системах компрессии АДМ и ДИКМ

повысит: помехоустойчивость.

| название | год | авторы | номер документа |

|---|---|---|---|

| Преобразователь кода | 1981 |

|

SU945987A1 |

| Параллельно-последовательный аналого-цифровой преобразователь | 1985 |

|

SU1305851A1 |

| ЦИФРОВОЕ ПРОГНОЗИРУЮЩЕЕ УСТРОЙСТВО | 2011 |

|

RU2446454C1 |

| ЦИФРОВОЕ ПРОГНОЗИРУЮЩЕЕ И ДИФФЕРЕНЦИРУЮЩЕЕ УСТРОЙСТВО | 2011 |

|

RU2449350C1 |

| ЦИФРОВОЕ ПРОГНОЗИРУЮЩЕЕ УСТРОЙСТВО | 2010 |

|

RU2446461C2 |

| МОНОИМПУЛЬСНАЯ РАДИОЛОКАЦИОННАЯ СИСТЕМА | 2000 |

|

RU2178896C1 |

| АДАПТИВНОЕ ЦИФРОВОЕ СГЛАЖИВАЮЩЕЕ И ПРОГНОЗИРУЮЩЕЕ УСТРОЙСТВО | 2016 |

|

RU2622852C1 |

| Устройство для преобразования контролируемых параметров | 1986 |

|

SU1320816A1 |

| ЦИФРОВОЕ ПРОГНОЗИРУЮЩЕЕ И ДИФФЕРЕНЦИРУЮЩЕЕ УСТРОЙСТВО | 2011 |

|

RU2450343C1 |

| Устройство для реализации алгоритма Волдера | 1983 |

|

SU1115049A1 |

ПРЕОБРАЗОВАТЕЛЬ КОДА, содержащий сумматор-.вычитатель,, триггер, первый и второй управляемЕ е инверторы, управляющие входы котоРЫЗ{ подключены к вырсоду триггера, первый вход которого подключен к шине тактовых импульсрв, а второй к выходу старшего разряда сумматоравычитателя, поразрядные выходы которого подключены к поразрядным входам первого управляемого инвертора, а первые поразрядные входы подключены к поразрядным выходам второго управляемого инвертора и выходам iустройства, а вторые пс азрядные входы - к входам устройства, отличающийся тем, что, с , целью повышения быстродействия, в него введены регистр, элемент за- : держки, дополнительный сумматор-вычитатель и постоянное запоминающее устройство, входы которого подключены к выходам первого управляемого инвертора и вторым входам дополнительного сумматора-вычит.ателя, первые входы которого подключены к выходам постоянного запоминающего устройства, управлякяций первого управляемого инвертора подключен к управляющему входу дополнитель- ного сумматора-вычитателя и к входу старшего разряда регистра, остальные поразрядные входы которого подключены к выходам дополнительного сумматора- вычитателяу а стробйрующий вход через элемент задержки - к шине так- 2 товЦх импульсов, выход старшего раз- ряда регистра соединен с входом старшего разряда сумматора-шачитателя, остальные выходы регистра с входами второго управляемого ин- вертора.

Фиг2 Фиг.З rlLi

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Букреев И.Н., Иансуров Б,М | |||

| и Горячев В.И | |||

| Микроэл ктронные схемы цифровых устройств | |||

| М.f Советское радио, 1975, с | |||

| Ручной ткацкий станок | 1922 |

|

SU339A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Авторское свидетельство СССР ; по заявке 3231939, кл | |||

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1983-04-23—Публикация

1981-12-29—Подача