Предпосылки изобретения

Процессоры данных используются в электронном устройстве почти каждого типа, включая бытовую электронику, устройства промышленного назначения, научную аппаратуру и сети связи. Однако эффективность и сложность процессоров данных (или микропроцессоров), используемых в различных приложениях, могут варьироваться в широком диапазоне. Требования по скорости и мощности для конкретного приложения важны при определении типа используемого процессора данных.

Тип используемого процессора данных, в частности, важен в реализациях радиосвязи, определяемых программным обеспечением (SDR). Устройство SDR использует аппаратные средства с изменяемой конфигурацией, которые могут программироваться по радиоканалу для работы в рамках различных протоколов беспроводной связи. Например, приемопередатчик SDR в беспроводном портативном компьютере может конфигурироваться с помощью загрузки первого программного обеспечения для работы в беспроводной сети стандарта IEE-802.11x, и его конфигурация может изменяться с помощью загрузки второго программного обеспечения для работы в беспроводной сети стандарта CDMA2000.

Имеются шесть основных типов процессоров данных обычного использования: 1) цифровые процессоры сигналов, 2) компьютеры с сокращённым набором команд, 3) компьютеры с комплексным набором команд, 4) программируемые пользователем вентильные матрицы, 5) специализированные интегральные схемы и 6) процессоры с набором специфических для приложения команд. Каждый из этих типов процессоров данных имеет конкретные преимущества и конкретные недостатки.

Цифровой процессор сигналов (ЦПС, DSP) представляет собой универсальный процессор, оптимизированный для эффективного выполнения операций обработки цифровых сигналов, таких как операция умножения-суммирования для операций фильтрации с конечным импульсным откликом (КИО) и быстрого преобразования Фурье (БПФ). ЦПС реализует многие усложненные режимы адресации для удовлетворения многих из требований вычислений ЦПС, такие как режим адресации с реверсированием битов для БПФ, индексная адресация для устройств FIFO («первым пришел - первым обслужен») и т.д. Примеры ЦПС включают следующее: 1) процессоры Motorola 56000, 56300, SC81xx и MRC6011; 2) Texas Instruments (TI) C55, C6203, C6416 и C67xx; 3) процессоры ADI Share и TigerSharc; 4) ЦПС с изменяемой конфигурацией Morpho MSI-64.

Компьютер с сокращённым набором команд (RISC) является универсальным компьютером (GPP), который главным образом нацелен на приложения управления, такие как приложения управления доступом к среде передачи (МАС). Основным достоинством машины типа RISC является ее простота. Как следует из определения, процессор RISC имеет малый набор команд, который обеспечивает большую плотность кода, а также более быструю реакцию на изменение потока. Примерами устройств RISC являются следующие: 1) процессоры ARM (например, ARM926, ARM1136J); 2) процессоры MIPS (например, MIPS32, MIPS64); 3) IBM PowerPC 405 и 750FX; и 4) Motorola PowerPC603).

Компьютер с комплексным набором команд (CISC) является универсальным процессором (GPP), нацеленным на приложения общего назначения, занимающие диапазон от мультимедийных приложений до приложений персональных компьютеров (РС). Примеры процессоров CISC включают в себя следующие: 1) Intel Pentium и 2) Motorola 68000.

Программируемая пользователем вентильная матрица (FPGA) является устройством с изменяемой конфигурацией, основанным на матрице элементов аппаратных средств, соединенных через длинные шины и локальные шины. Устройства на FPGA по существу повсеместно используются в приложениях и реализациях базовых станций беспроводной сети. Примеры устройств на FPGA включают в себя: 1) Xilinx Virtex IV и 2) Altera Stratix II.

Специализированная интегральная схема (ASIC) является аппаратным средством, специально спроектированным для конкретного приложения. Схема ASIC является очень эффективной по мощности. Устройства на ASIC используются во многих беспроводных устройствах (например, в сотовых телефонах и т.д.). Процессор с набором специфических для приложения команд (ASIP) является улучшенной версией устройства на ASIC, которая добавляет больше программируемости к аппаратным средствам на ASIC.

Каждый из вышеописанных процессоров имеет определенные преимущества и конкретные недостатки. Цифровые процессоры сигналов являются наиболее гибким типом процессора, с точки зрения аппаратных средств, чтобы удовлетворить требования радиосвязи, определяемой программным обеспечением (SDR). Однако устройства на DSP не имеют достаточной эффективности MIPS и архитектуры манипулирования битами для удовлетворения требований обработки с битовой скоростью стандартов 3G и 4G. Процессоры на RISC нацелены на приложения управления, но не адекватны вне приложений базовой полосы для реализаций беспроводных сетей. Процессоры CISC могут иметь гибкость и эффективность MIPS для обработки приложений базовой полосы, но их низкая мощность по существу делает их неподходящими в случае ограничений по мощности, свойственных телефонным трубкам. Устройства на FPGA, такие как процессоры CISC, могут соответствовать эффективности MIPS, но их низкая эффективность по мощности делает их непригодными для конструкций телефонных трубок.

Устройства на ASIC хорошо согласованы с ограничениями по мощности и стоимости конструкций телефонных трубок. Однако их гибкость весьма ограничена для того, чтобы сделать их пригодными для реализаций SDR. Устройства на ASIP позволяют достичь более высокой гибкости, чем устройства на ASIC, путем добавления большей степени программируемости к специализированным аппаратным средствам и путем введения процессоров на наборе команд в аппаратные средства. Однако поскольку ASIP являются универсальными устройствами, их эффективность процессорного ядра зависит от обрабатываемого приложения. Чем больше управляющего кода в приложении, тем менее эффективным будет процессор ASIP. Результатом является низкая эффективность и высокое потребление энергии.

Дополнительными недостатками известных процессоров являются масштабируемость и модульность. Метод радиосвязи, определяемой программным обеспечением (SDR), был создан для минимизации затрат (времени проектирования, TTM) и потребляемой мощности для максимизации гибкости. Известные реализации процессоров не обеспечивают оптимизированной комбинации масштабируемости и модульности.

Проектирование процессора данных для использования в мобильных станциях объективно затруднено ввиду компромиссов, которые должны всегда делаться между конкурирующими факторами, включая эффективность по энергии, вычислительную мощность и гибкость. Большинство современных, соответствующих множеству стандартов беспроводных устройств, содержат блоки из отдельных и во многом независимых устройств на ASIC, каждое из которых относится к отдельному стандарту беспроводной связи. Отдельные устройства на ASIC компонуются вместе, чтобы одновременно обеспечить поддержку различных стандартов беспроводной связи. Этот метод решения «в лоб» вызывает различные проблемы ввиду увеличения размеров, увеличения мощности и отсутствия гибкости. С другой стороны, универсальные процессоры DSP и сходные архитектуры обеспечивают значительную гибкость. Однако эти устройства характеризуются высокой потребляемой мощностью и в типовом случае не могут удовлетворить требования вычислений в реальном времени для большинства стандартов беспроводной связи.

Современные мобильные станции (или беспроводные терминалы) основаны на устройствах с множеством ASIC, что обусловлено факторами мощности и эффективности. Как отмечено, такие устройства на ASIC обычно являются специализированными только для выполнения конкретных функций в системе. Например, в большинстве традиционных мобильных станций широкополосного множественного доступа с кодовым разделением каналов (WCDMA) отдельные блоки ASIC в типовом случае используются для функции коррелятора и для функции поиска сотовой ячейки, несмотря на то, что оба блока во многом весьма сходны. Если бы обе функции можно было реализовать на одном и том же аппаратном средстве с изменяемой конфигурацией в максимально возможной степени, то такое решение было бы намного более эффективным и позволило бы использовать кристаллы с меньшими размерами.

Поэтому в технике имеется потребность в усовершенствованной архитектуре радиосвязи, определяемой программным обеспечением (SDR), которая минимизирует затраты и потребляемую мощность при сохранении гибкости. В частности, имеется необходимость в реконфигурируемом блоке корреляции для использования в беспроводных устройствах SDR.

Сущность изобретения

Настоящее изобретение обеспечивает реконфигурируемый блок корреляции, который может быть реализован в процессоре с набором команд, реконфигурируемым для основанных на контексте операций. Блок корреляции, соответствующий принципам настоящего изобретения, согласует архитектуру с областью приложения и совместно оптимизирует эффективность и мощность. Таким образом, настоящее изобретение одновременно удовлетворяет требованиям обработки реального времени и требованиям низкой мощности беспроводных мобильных станций. Предпочтительным образом, блок корреляции является в высокой степени реконфигурируемым и может быть использован для различных функциональных блоков, работающих в соответствии с различными стандартами в процессоре CRISP, включая функциональные блоки сжатия в системе CDMA, демодуляции в IEEE-802.11b CCK, сжатия в WCDMA, поиска ячейки, сжатия в HSDPA и т.п.

Для преодоления вышеуказанных недостатков предшествующего уровня техники, основной целью настоящего изобретения является создание реконфигурируемого блока корреляции для корреляционной обработки последовательности выборок кодовых элементов. В соответствии с предпочтительным вариантом осуществления настоящего изобретения реконфигурируемый блок корреляции содержит: 1) память для хранения последовательности выборок кодовых элементов, 2) множество элементов сложения-вычитания, причем каждый из элементов сложения-вычитания может принимать множество действительных битов а из первой выборки кодовых элементов в памяти и множество мнимых битов b из первой выборки кодовых элементов; и 3) блок обработки, содержащий множество блоков выбора знака. Каждый из множества блоков выбора знака принимает из одного из множества элементов сложения-вычитания первый входной сигнал, равный сумме (а+b), множества действительных битов а и множества мнимых битов b, и второй выходной сигнал, равный разности (а-b), множества действительных битов а и множества мнимых битов b. Каждый блок выбора знака генерирует действительный выходной сигнал и мнимый выходной сигнал, причем каждый из указанных действительного выходного сигнала и мнимого выходного сигнала является одним из следующих: 1) суммой (а+b), умноженной на +1 или -1, и 2) разностью (а-b), умноженной на +1 или -1.

Согласно варианту осуществления настоящего изобретения блок корреляции дополнительно содержит генератор кода для генерации последовательности кодовых битов, причем каждый блок выбора знака получает действительный кодовый бит и мнимый кодовый бит из последовательности, и при этом действительный и мнимый кодовые биты определяют значение действительного выходного сигнала и значение мнимого выходного сигнала каждого блока выбора знака.

Согласно другому варианту осуществления настоящего изобретения блок обработки дополнительно содержит первый каскад сумматоров, содержащий первое множество действительных сумматоров и первое множество мнимых сумматоров.

Согласно еще одному варианту осуществления настоящего изобретения каждый из первого множества действительных сумматоров принимает первый действительный выходной сигнал с одного из множества блоков выбора знака и второй действительный выходной сигнал с другого из множества блоков выбора знака и формирует действительный суммарный выходной сигнал.

Согласно еще одному варианту осуществления настоящего изобретения каждый из первого множества мнимых сумматоров принимает первый мнимый выходной сигнал с одного из множества блоков выбора знака и второй мнимый выходной сигнал с другого из множества блоков выбора знака и формирует мнимый суммарный выходной сигнал.

Согласно другому варианту осуществления настоящего изобретения блок обработки дополнительно содержит второй каскад сумматоров, содержащий, по меньшей мере, один действительный сумматор и, по меньшей мере, один мнимый сумматор.

Согласно еще одному варианту осуществления настоящего изобретения каждый из, по меньшей мере, одного действительного сумматора во втором каскаде принимает первый действительный суммарный выходной сигнал с одного из первого множества действительных сумматоров и второй действительный выходной сигнал с другого одного из первого множества действительных сумматоров и формирует действительный суммарный выходной сигнал.

Согласно еще одному варианту осуществления настоящего изобретения каждый из, по меньшей мере, одного сумматора во втором каскаде принимает первый мнимый суммарный выходной сигнал с одного из первого множества мнимых сумматоров и второй мнимый суммарный выходной сигнал с другого из первого множества мнимых сумматоров и формирует мнимый суммарный выходной сигнал.

Согласно еще одному варианту осуществления настоящего изобретения реконфигурируемый блок для обработки множества контекстных команд содержит множество процессоров для исполнения каждой из предварительно определенных команд конкретного контекста; память программы для хранения управляющей программы из внешней линии управления; контроллер последовательности для извлечения программных команд из памяти программы, упорядочивания контекстов и посылки упорядоченных контекстов в виде реконфигурируемых битов на соответствующий процессор из упомянутого множества процессоров; и коммутатор межсоединений, подсоединенный между каждым из множества процессоров и внешней шиной данных, для посылки данных из шины данных на соответствующий процессор из множества процессоров.

Перед переходом к детальному описанию изобретения, приведенному ниже, было бы полезным привести определения некоторых терминов и выражений, используемых по всему тексту данного документа. Термины «включать в себя» и «содержать», а также производные от них термины означают включение без ограничения; термин «или» употребляется в смысле «включая», то есть означает и/или; выражения «ассоциирован (связан) с» и «ассоциированный (связанный) с указанным» и производные от них могут интерпретироваться как включать, включать в состав, взаимно соединять, содержать, содержаться, присоединять к чему-либо или соединять с чем-либо, связывать с чем-либо, сообщаться с чем-либо, взаимодействовать с чем-либо, перемежать, располагать рядом, находиться вблизи чего-либо, связываться с чем-либо, иметь, иметь свойство чего-либо и т.п. Термин «контроллер» означает любое устройство, систему или их часть, которое(ая) управляет, по меньшей мере, одной операцией, причем такое устройство может быть реализовано аппаратными средствами, программно-аппаратными средствами или программным обеспечением, или некоторой комбинацией, по меньшей мере, двух из указанных объектов. Следует отметить, что функциональность, ассоциированная с любым контроллером, может быть централизованной или распределенной как локально, так и дистанционно. Определения некоторых терминов и выражений приведены по всему описанию, и специалистам должно быть понятно, что во многих, если не во всех случаях, такие определения применимы как к предшествующему, так и к будущему использованию определенных таким образом терминов и выражений.

Краткое описание чертежей

Настоящее изобретение и его преимущества поясняются в нижеследующем описании, иллюстрируемом чертежами, на которых одинаковыми ссылочными позициями обозначены сходные элементы и на которых показано следующее:

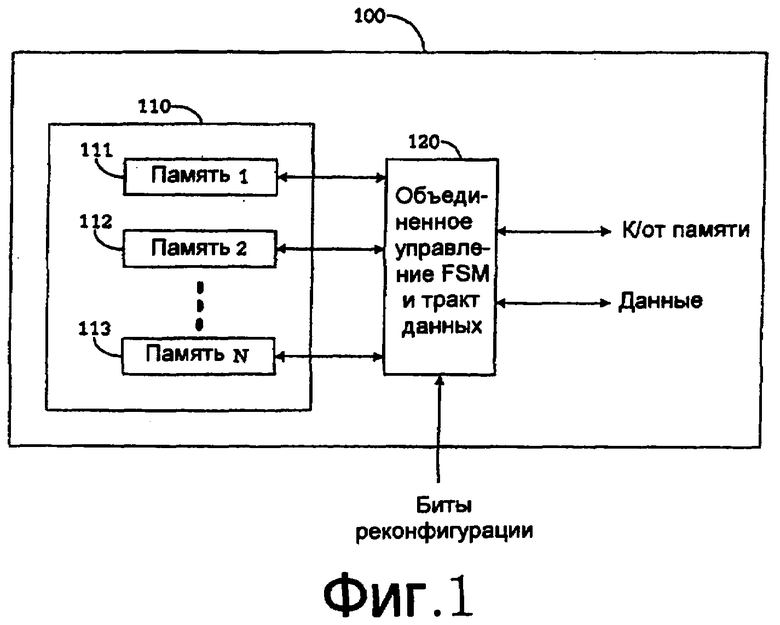

Фиг.1 - блок-схема обычного процессора данных согласно примерному варианту осуществления согласно предшествующему уровню техники;

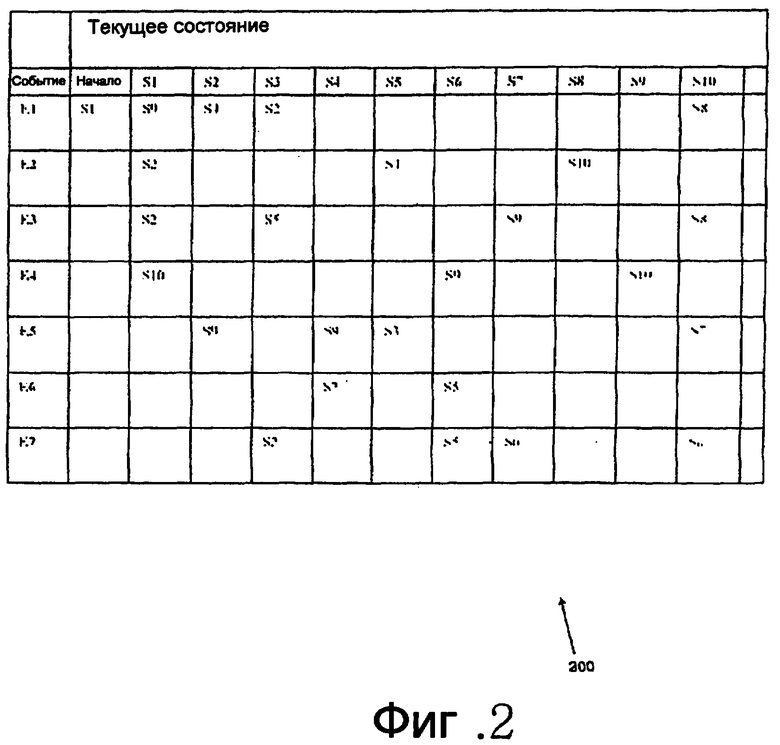

Фиг.2 - таблица состояний конечного автомата (FSM) для процессора данных;

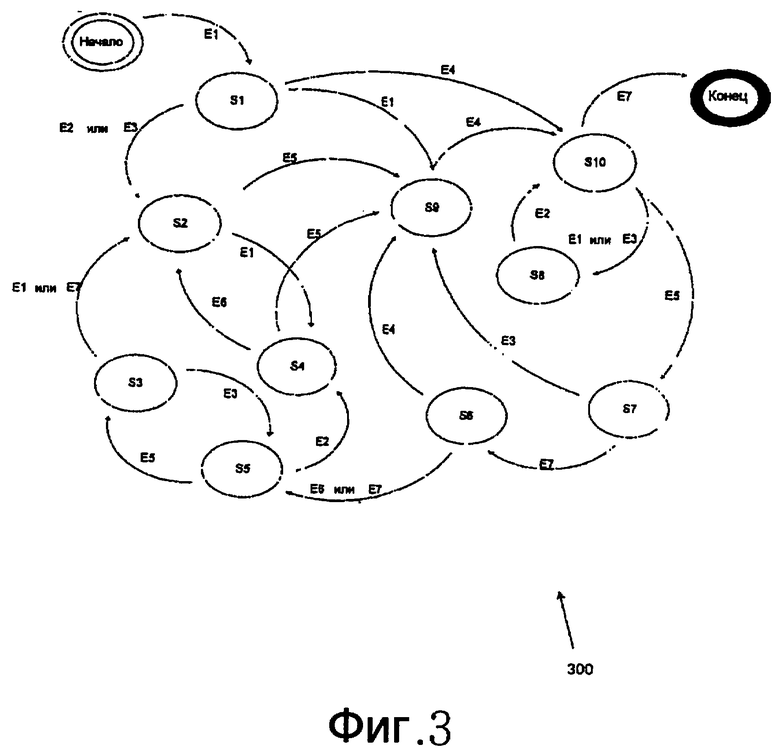

Фиг.3 - диаграмма состояний, соответствующая таблице состояний конечного автомата на фиг.2;

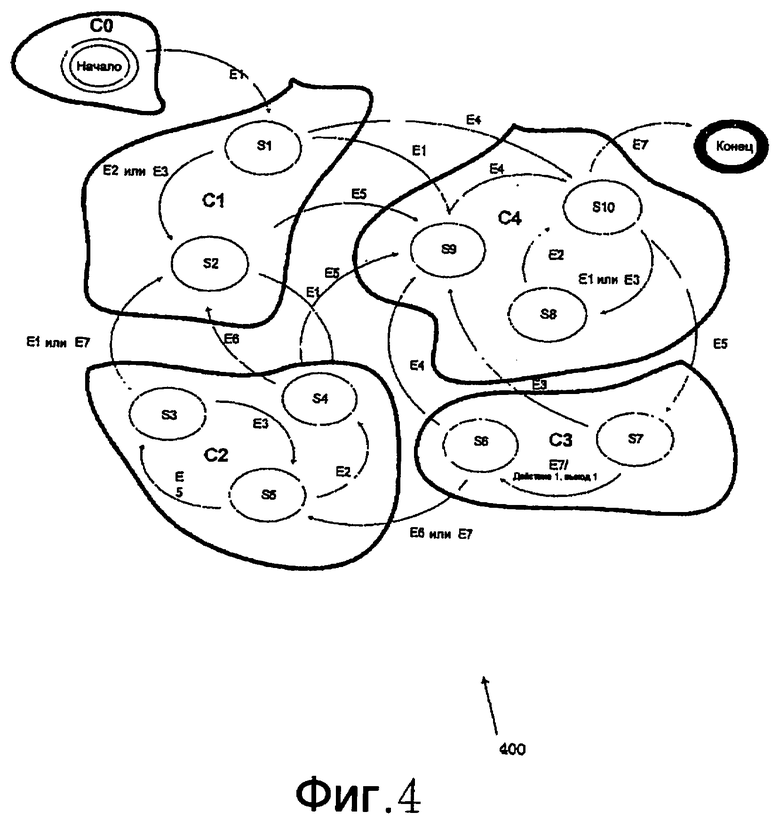

Фиг.4 - диаграмма состояний, показывающая основанные на контексте группирования состояний в таблице состояний конечного автомата по фиг.2, согласно приведенному для примера варианту осуществления настоящего изобретения;

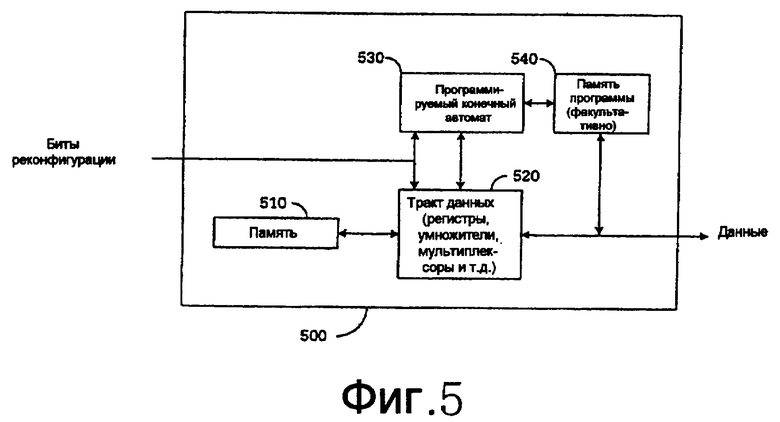

Фиг.5 - высокоуровневая блок-схема процессора с набором команд, реконфигурируемым для основанных на контексте операций, согласно приведенному для примера варианту осуществления настоящего изобретения;

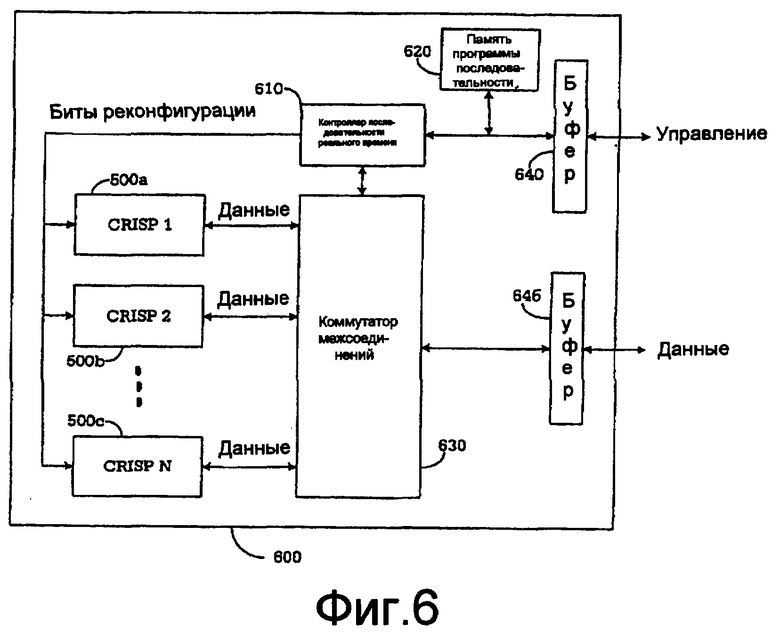

Фиг.6 - высокоуровневая блок-схема реконфигурируемой системы обработки, содержащей множество процессоров с набором команд, реконфигурируемым для основанных на контексте операций, согласно приведенному для примера варианту осуществления настоящего изобретения;

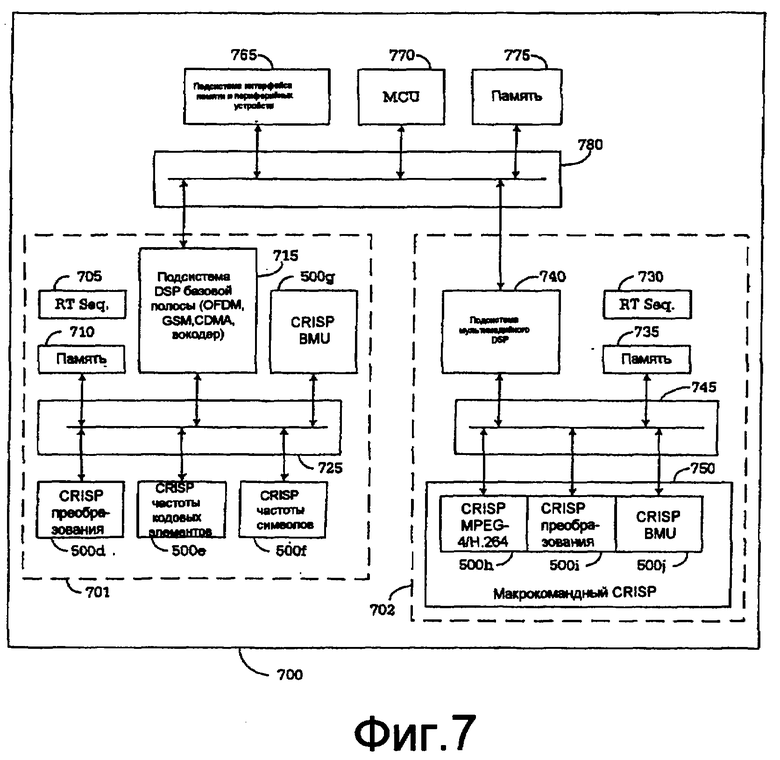

Фиг.7 - высокоуровневая блок-схема соответствующей множеству стандартов системы радиосвязи, определяемой программным обеспечением (SDR), содержащей множество процессоров с набором команд, реконфигурируемым для основанных на контексте операций, согласно приведенному для примера варианту осуществления настоящего изобретения;

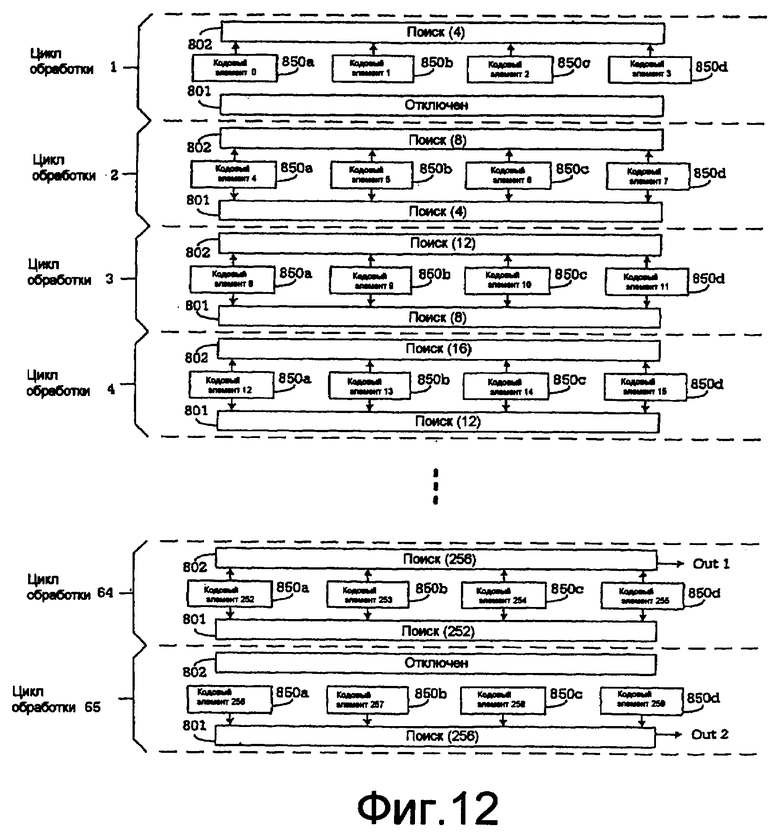

Фиг.8 - блок-схема блока корреляции согласно варианту осуществления настоящего изобретения;

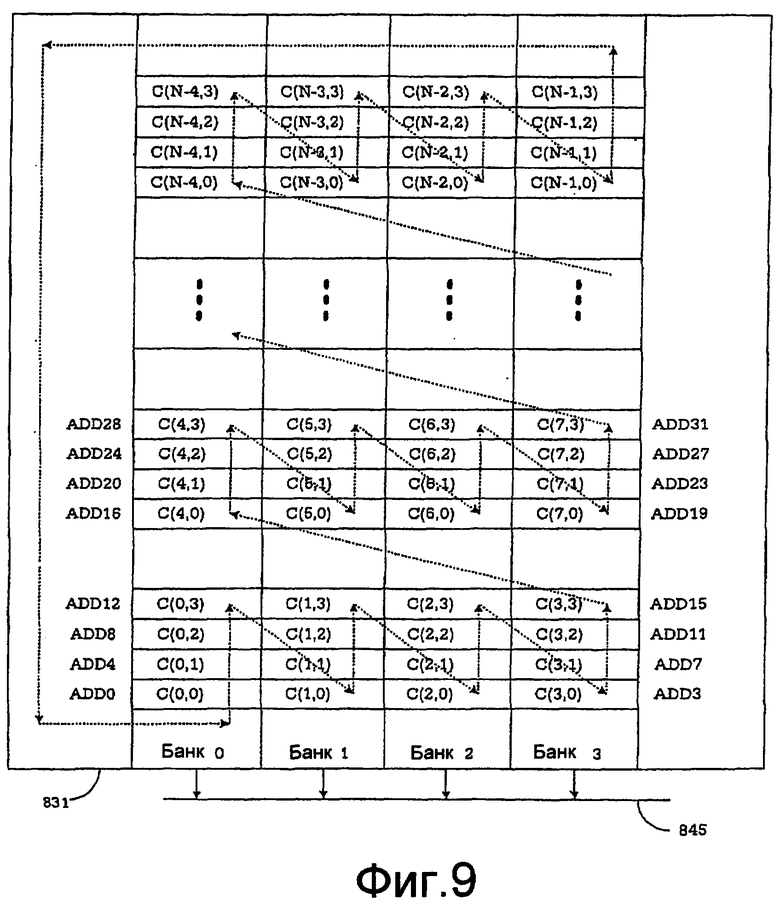

Фиг.9 - блок-схема блока памяти в блоке корреляции согласно варианту осуществления настоящего изобретения;

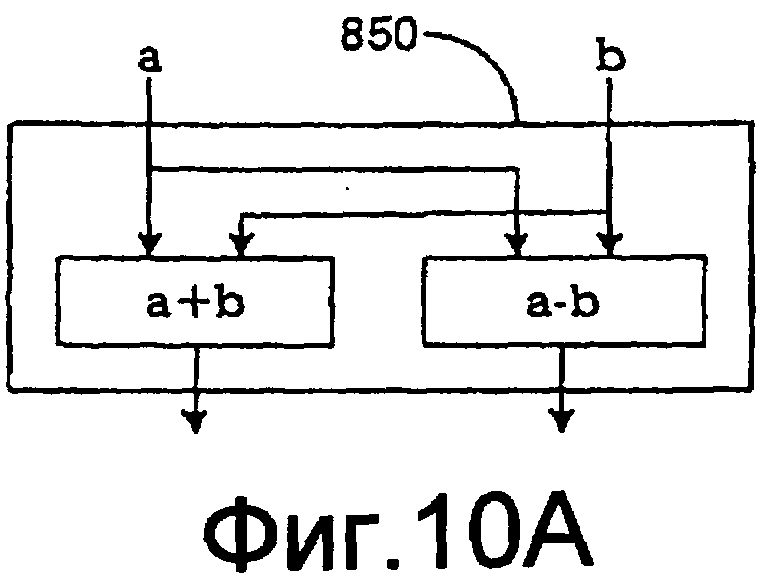

Фиг.10А - более детальное представление элемента сложения-вычитания согласно приведенному для примера варианту осуществления настоящего изобретения;

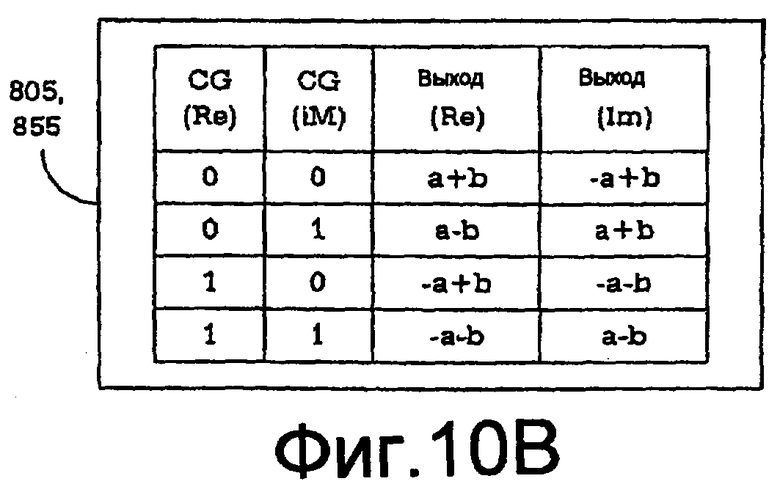

Фиг.10В - более детальное представление блока выбора знака согласно приведенному для примера варианту осуществления настоящего изобретения;

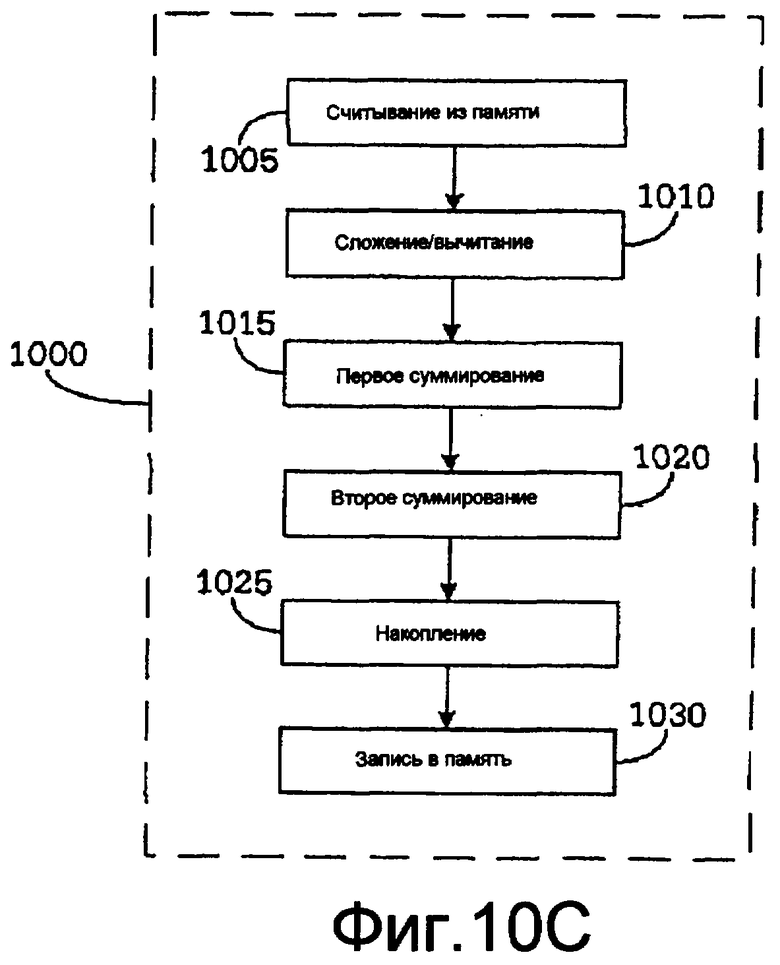

Фиг.10С - блок-схема, иллюстрирующая работу блока корреляции согласно принципам настоящего изобретения;

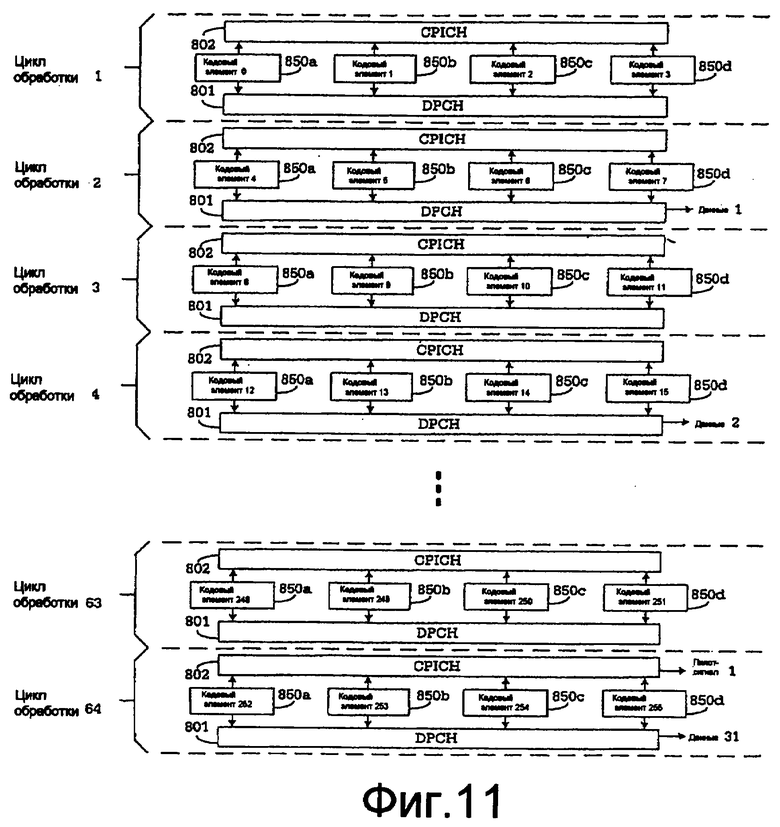

Фиг.11 - представление вывода данных блока корреляции по фиг.8 в течение выбранных циклов операции согласно варианту осуществления настоящего изобретения;

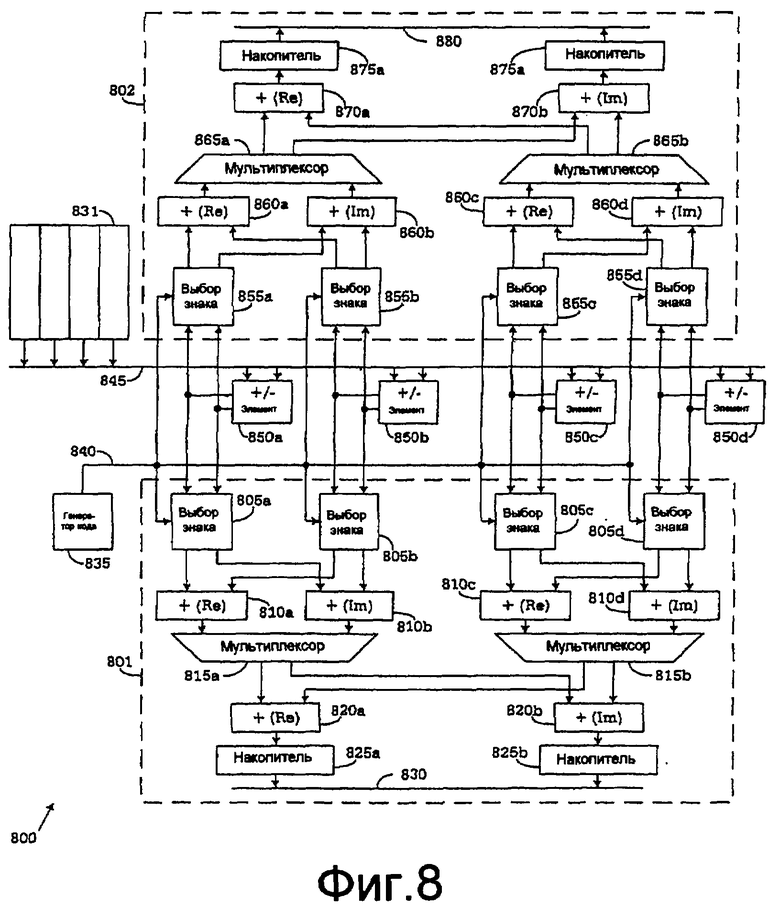

Фиг. 12 - представление вывода данных блока корреляции по фиг.8 в течение операции поиска ячейки WCDMA согласно варианту осуществления настоящего изобретения.

Детальное описание изобретения

Фиг.1-12, описанные ниже, и различные используемые варианты осуществления, используемые для описания принципов настоящего изобретения в настоящем патентном документе, приведены только для иллюстрации и не должны толковаться как ограничивающие объем изобретения. Специалистам в данной области техники должно быть понятно, что принципы настоящего изобретения могут быть реализованы в любой соответственно реализованной системе обработки.

На фиг.1 показана блок-схема обычного процессора данных согласно примерному варианту осуществления согласно предшествующему уровню техники. Фиг.1 представляет обобщенное выполнение приложения в аппаратных средствах и программном обеспечении. Процессор 100 данных содержит память 110 и схемы 120 управления. Схемы 120 управления включают в себя объединенные схемы конечного автомата (FSM) и схемы тракта данных. Память 110 содержит N блоков памяти, включая приведенные для примера блоки 111-113 памяти, которые произвольно обозначены как память 1, память 2 и память N.

Любое приложение процессора данных может рассматриваться как набор трактов данных, управляемых и координируемых конечным автоматом FSM, как показано на фиг.1. Конечный автомат принимает входные события и в ответ выполняет переходы между состояниями и/или генерирует выходные результаты. Конечный автомат FSM принимает решение, в какие состояния следует переходить, на основе текущего состояния и принимаемых входных событий.

На фиг.2 показана таблица 200 состояний конечного автомата для приведенного для примера процессора данных. Таблица 200 состояний конечного автомата представляет переходы в следующее состояние, выполняемые конечным автоматом, на основе текущего состояния (то есть одного из состояний S1-S10) и принятого входного события (то есть одного из событий Е1-Е7). Первоначально конечный автомат находится в состоянии S1. Столбец для состояния S1 указывает переходы состояний для состояния S1 в ответ на события Е1-Е4.

В ответ на событие Е1, принятое в состоянии S1, конечный автомат переходит из состояния S1 в состояние S9. В ответ на событие Е2, принятое в состоянии S1, конечный автомат переходит из состояния S1 в состояние S2. В ответ на событие Е3, принятое в состоянии S1, конечный автомат переходит из состояния S1 в состояние S2. В ответ на событие Е4, принятое в состоянии S1, конечный автомат переходит из состояния S1 в состояние S10.

Как видно из фиг.2, в таблице 200 состояний конечного автомата имеется множество пропусков, для которых не указаны значения. Например, для состояния S1 не приведены значения для событий Е5-Е7. В процессорах, известных из предшествующего уровня техники, эти пропуски, хотя и не вносят вклада в поток операций конечного автомата, однако они должны быть предусмотрены, так как в противном случае конечный автомат не будет работать корректным образом. В процессорах, известных из предшествующего уровня техники, конечные автоматы не могли быть оптимизированы далее, чтобы устранить эти пропуски.

Фиг.3 иллюстрирует диаграмму состояний, соответствующую таблице состояний конечного автомата на фиг.2. Каждое из состояний S1-S10 представлено кружком, а события Е1-Е7 вызывают переходы между состояниями. Эти переходы представлены линиями со стрелками, соединяющими кружки состояний. Стрелка определяет направление перехода.

Следует отметить, что на диаграмме 300 состояний можно сгруппировать состояния в соответствии с контекстом исполнительных блоков. Для целей настоящего описания контекстом является группа операций и/или инструкций, которые связаны с одной и той же функцией. Фиг.4 иллюстрирует диаграмму 400 состояний, в которой состояния показанной на фиг.2 таблицы состояний конечного автомата, которые относятся к тому же самому контексту, сгруппированы вместе согласно принципам настоящего изобретения. Группирования состояний образуют контексты С0, С1, С2, С3 и С4.

Каждое из группирований состояний, показанных на фиг.4, может быть использовано для создания процессора с набором команд, реконфигурируемым для основанных на контексте операций (CRISP), согласно принципам настоящего изобретения. Каждый из контекстов С0-С4 содержит минимальное число входных событий и набор вероятных операций. Каждый контекст, таким образом, имеет свой собственный тракт данных, который может содержать блоки параллельного исполнения, в то время как исполнение набора команд может быть осуществлено в VLIP (процессор с командами очень большой длины), SIMD (один поток команд - много потоков данных), микрокоде или другими известными способами реализации, чтобы повысить эффективность в целом.

На фиг.5 показана высокоуровневая блок-схема процессора 500 с набором команд, реконфигурируемым для основанных на контексте операций (CRISP), согласно приведенному для примера варианту осуществления настоящего изобретения. Процессор CRISP 500 содержит память 510, программируемые схемы 520 трактов данных, программируемый конечный автомат 530 и, факультативно, память 540 программы. Процессор CRISP 500 предназначен для реализации только поднабора контекстно-связанных команд по фиг.4 оптимальным способом. Каждый из контекстов С0-С4 на фиг.4 может быть реализован отдельным процессором CRISP, подобным процессору CRISP 500. Процессор 500 с набором команд, реконфигурируемым для основанных на контексте операций (CRISP), определяет общеизвестный блок аппаратных средств, который обычно состоит из процессорных блоков аппаратных средств более высокого уровня. Принципиальное преимущество процессора CRISP 500 заключается в том, что процессор CRISP 500 разбивает требуемое приложение на две основные области: область управления и область трактов данных, и оптимизирует каждую область отдельно. При реализации приложения процессора данных, такой как трубка мобильной станции (например, сотовый телефон, беспроводный портативный компьютер), с использованием процессора CRISP 500, настоящее изобретение, по меньшей мере частично, преодолевает проблемы зависимости гибкости от производительности, которые оказывают отрицательное влияние на традиционные приложения процессора данных.

Область управления реализуется с помощью программируемого конечного автомата 530, который может содержать DSP (цифровой процессор сигналов), MCU (модуль микроконтроллера) или другое устройство известного типа. Программируемый конечный автомат 530 конфигурируется посредством битов реконфигурации, принятых от внешнего контроллера (не показан). Программируемый конечный автомат 530 может исполнять программу, сохраненную в ассоциированной факультативной памяти 540 программы. Программа может быть сохранена в памяти 540 программы через линию данных от внешнего контроллера (не показан). Память 510 используется для хранения данных приложения, используемых схемами 530 трактов данных.

Схемы 520 программируемых трактов данных делятся на набор структурных блоков, которые выполняют конкретные функции (например, регистры, мультиплексоры, умножители и т.п.). Каждый из структурных блоков является как реконфигурируемым, так и программируемым для обеспечения максимальной гибкости. Критерии для разделения программируемых схем 520 трактов данных на функциональные блоки зависят от уровня реконфигурируемости и программируемости, требуемого для конкретного приложения.

Поскольку каждый из контекстов С0-С4 на фиг.4 реализуется посредством отдельного процессора CRISP 500, который работает независимо от других процессоров CRISP, настоящее изобретение обеспечивает эффективную схему управления производительностью, которая обеспечивает возможность отключения процессора CRISP, если процессор CRISP не требуется для исполнения. Это гарантирует, что активными являются только те процессоры CRISP, которые необходимы в данный момент времени, в то время как другие неработающие процессоры CRISP не потребляют значительной мощности.

Процессор CRISP согласно принципам настоящего изобретения может быть нацелен на несколько приложений, включая, но без ограничения указанным, приложения базовой полосы в беспроводных устройствах и мультимедийные приложения. Во многих приложениях эти контексты могут представлять собой слабо связанные контексты, которые могут исполняться одновременно при минимальной зависимости или в ее отсутствие.

На фиг.6 показана высокоуровневая блок-схема реконфигурируемой системы 600 обработки согласно приведенному для примера варианту осуществления настоящего изобретения. Реконфигурируемая система 600 обработки содержит N процессоров с набором команд, реконфигурируемым для основных на контексте операций (CRISP), включая приведенные для примера процессоры CRISP 500а, 500b и 500с, которые произвольно обозначены как CRISP1, CRISP2 и CRISPN. Реконфигурируемая система 600 обработки также содержит контроллер 610 последовательности команд реального времени, память 620 программы последовательности, программируемый переключатель 630 межсоединений и буферы 640 и 645.

Биты реконфигурации могут быть загружены в процессоры CRISP 500а, 500b и 500с из линии управления посредством контроллера 610 последовательности команд реального времени и буфера 640. Программа управления может быть также загружена в память 620 программы последовательности из линии управления через буфер 640. Контроллер последовательности команд реального времени упорядочивает контексты для исполнения каждым из процессоров CRISP 500а-с путем извлечения команд программы из памяти 620 программы и посылки битов реконфигурации на процессоры CRISP 500а-с. В приведенном для примера варианте осуществления, контроллер 610 последовательности команд реального времени может содержать процессор стека, который может работать как планировщик реального времени ввиду его низкого запаздывания и простоты.

Программируемый переключатель 630 межсоединений обеспечивает связанность между каждым из процессоров CRISP 500а-с и внешней шиной данных посредством двунаправленного буфера 645. В приведенном для примера варианте осуществления настоящего изобретения каждый из процессоров CRISP 500а-с может действовать как задающий блок реконфигурируемого переключателя 630 межсоединений и может инициировать адресный доступ. Арбитр шины для программируемого переключателя 630 межсоединений может быть внутренним для контроллера 610 последовательности команд реального времени.

В приведенном для примера варианте осуществления реконфигурируемая система 600 обработки может представлять собой, например, сотовый телефон или подобное беспроводное устройство, или процессор данных для использования в портативном компьютере. В среде беспроводного устройства, реализованной в соответствии с принципами радиосвязи, определенными программным обеспечением (SDR), каждый из процессоров CRISP 500а-с обеспечивает исполнение поднабора контекстно-связанных команд, которые ассоциированы с конкретной реконфигурируемой функцией. Например, процессор CRISP 500а может быть конфигурирован для исполнения контекстно-связанных команд, которые обрабатывают сигналы базовой полосы CDMA или сигналы базовой полосы OFDMA. Процессор CRISP 500b может быть конфигурирован для исполнения контекстно-связанных команд, которые действуют как контроллер памяти. Процессор CRISP 500с может быть конфигурирован для исполнения контекстно-связанных команд, которые выполняют обработку MPEG-4 для мультимедийных приложений.

Процессор CRISP согласно принципам настоящего изобретения обеспечивает новый способ реализации методов ускорения реконфигурируемых аппаратных средств. Настоящее изобретение обеспечивает реконфигурируемость и программируемость при минимальном снижении эффективности по мощности. Поскольку процессоры CRISP в сильной степени независимы и могут работать одновременно, настоящее изобретение имеет преимущество по эффективности, заключающееся в параллелизме, не влекущем за собой проблемы полной мощности, связанной с выполнением параллельных операций. Слабая связь и независимость процессоров CRISP позволяет конфигурировать их для различных систем и функций, которые могут отключаться независимым образом.

На фиг.7 представлена высокоуровневая блок-схема соответствующей множеству стандартов системы 700 радиосвязи, определяемой программным обеспечением (SDR), содержащей множество процессоров с набором команд, реконфигурируемым для основанных на контексте операций, согласно приведенному для примера варианту осуществления настоящего изобретения. Система SDR 700 может содержать беспроводный терминал (или мобильную станцию), который получает доступ к беспроводной сети, например, сотовый телефон GSM или CDMA, PDA с функциями согласно WCDMA или IEEE-802.11x и т.п.

Мультистандартная система SDR 700 содержит подсистему 701 базовой полосы, подсистемы 702 приложений, подсистему 765 интерфейса памяти и периферийных устройств, основной блок управления (MCU) 770, память 775 и средство 780 межсоединений. Блок MCU 770 может содержать, например, обычный микроконтроллер или микропроцессор (например, x86, ARM, RISC, DSP и т.д.). Подсистема 765 интерфейса памяти и периферийных устройств может соединять систему SDR 700 с внешней памятью (не показана) и с внешними периферийными устройствами (не показаны). Память 775 сохраняет данные от других компонентов в системе SDR 700 и от внешних устройств (не показаны). Например, память 775 может сохранять поток выборок входящих данных, принимаемых от внешней антенной системы и РЧ преобразователя с понижением частоты, связанных с системой SDR 700. Средство 780 межсоединений обеспечивает перенос данных между подсистемами 701 и 702, подсистемой 765 интерфейса памяти и периферийных устройств, блоком MCU 770 и памятью 775.

Подсистема 701 базовой полосы содержит контроллер 705 последовательности реального времени (RT Seq.), подсистему 715 DSP базовой полосы, средство 725 межсоединений и множество специализированных процессоров CRISP, включая процессор CRISP 500d преобразования, процессор CRISP 500е частоты следования кодовых элементов, процессор CRISP 500f частоты следования символов и процессор CRISP 500g блока манипулирования битами (BMU). Например, процессор CRISP 500d преобразования может реализовывать функцию быстрого преобразования Фурье (БПФ), процессор CRISP 500е частоты следования кодовых элементов может реализовывать корреляционную функцию для сигнала CDMA, и процессор CRISP 500f частоты следования символов может реализовывать функцию декодера Витерби.

В таком приведенном для примера варианте осуществления настоящего изобретения процессор CRISP 500d преобразования может получать выборки сигнала промежуточной частоты (ПЧ), сохраненные в памяти 775, и выполнять функцию БПФ, которая генерирует последовательность выборок кодовых элементов с частотой в базовой полосе. Затем процессор CRISP 500е частоты следования кодовых элементов получает выборки кодовых элементов из процессора CRISP 500d преобразования и выполняет корреляционную функцию, которая генерирует последовательность символов данных. Затем процессор CRISP 500f частоты следования символов получает данные символов от процессора CRISP 500е частоты следования кодовых элементов и выполняет декодирование Витерби для восстановления пользовательских данных в базовой полосе. Пользовательские данные базовой полосы могут затем использоваться подсистемой 702 приложений.

В приведенном для примера варианте осуществления настоящего изобретения процессор CRISP 500f частоты следования символов может содержать два или более процессора CRISP, которые работают параллельно. Также, например, процессор CRISP 500g блока манипулирования битами (BMU) может реализовывать такие функции, как кодирование переменной длины, проверка циклическим избыточным кодом (СRC), сверточное кодирование и т.п. Средство 725 межсоединений обеспечивает перенос данных между контроллером 705 последовательности реального времени, памятью 710, подсистемой 715 DSP базовой полосы и процессорами CRISP 500d-500g.

Подсистема 702 приложений содержит контроллер 730 последовательности команд реального времени (RT Seq.), память 735, подсистему 740 DSP мультимедийных данных, средство 745 межсоединений и макрокомандный процессор CRISP 750 мультимедийных данных. Макрокомандный процессор CRISP 750 мультимедийных данных содержит множество специализированных процессоров CRISP, включая процессор CRISP 500h MPEG-4/H.264, процессор CRISP 500i преобразования и процессор CRISP 500j BMU. В приведенном для примера варианте осуществления настоящего изобретения процессор CRISP 500h MPEG-4/H.264 выполняет функции оценивания движения, а процессор CRISP 500i преобразования выполняет функцию дискретного косинусного преобразования (ДКП). Средство 745 межсоединений обеспечивает перенос данных между контроллером 730 последовательности команд реального времени (RT Seq.), памятью 735, подсистемой 740 DSP мультимедийных данных и макрокомандным процессором CRISP 750 мультимедийных данных.

В приведенном для примера варианте осуществления, показанном на фиг.7, использование процессоров CRISP позволяет изменять конфигурацию подсистемы 702 приложений мультистандартной системы SDR 700 для поддержки множества стандартов видео с множеством профилей и размеров. Дополнительно использование устройств CRISP позволяет изменять конфигурацию подсистемы 701 базовой полосы мультистандартной системы SDR 700 для поддержки множества стандартов радиоинтерфейсов. Таким образом, система SDR 700 может работать в беспроводных сетях различных типов (например, CDMA, GSM, 802.11x и т.д.) и может воспроизводить видео- и аудиоформаты различных типов. Однако использование процессоров CRISP в соответствии с принципами настоящего изобретения позволяет системе SDR 700 выполнять эти функции при существенно меньшем потреблении мощности, чем в обычных беспроводных устройствах, имеющих сопоставимые возможности.

Более конкретно, настоящее изобретение обеспечивает блок корреляции с изменяемой конфигурацией, который может быть реализован в процессоре с набором команд, реконфигурируемым для основанных на контексте операций. Предпочтительным образом, блок корреляции, соответствующий принципам настоящего изобретения, является в высокой степени реконфигурируемым и может использоваться для различных функциональных блоков, работающих в соответствии с различными стандартами, включая функциональные блоки сжатия в системе CDMA, демодуляции в IEEE-802.11b CCK, сжатия в WCDMA, поиска ячейки, сжатия в HSDPA и т.п.

На фиг.8 показана блок-схема блока 800 корреляции согласно варианту осуществления настоящего изобретения. Блок 800 корреляции может быть реализован, например, как часть процессора CRISP 500е частоты следования кодовых элементов. Блок 800 корреляции содержит три основные части: память 831 данных, генератор кода (CG) 835 и блок обработки. В варианте осуществления настоящего изобретения блок обработки реализован как два по существу идентичных подблока обработки, а именно: нижний блок обработки (PU) 801 и верхний блок обработки (PU) 802. Блок 800 корреляции также содержит шину 840 кода, шину 845 данных и четыре элемента сложения-вычитания (+/-), в частности, элементы сложения-вычитания 850а-850d.

Нижний 801 блок обработки содержит четыре блока выбора знака, а именно: блоки 805а-805d выбора знака, четыре сумматора первого каскада, а именно: сумматоры 810а-810d, мультиплексоры 815а и 815b, два сумматора второго каскада, а именно: сумматоры 820а и 820b, накопители 825а и 825b и выходную шину 830. Верхний 802 блок обработки содержит четыре блока выбора знака, а именно: блоки 855а-855d выбора знака, четыре сумматора первого каскада, а именно: сумматоры 860а-860d, мультиплексоры 865а и 865b, два сумматора второго каскада, а именно: сумматоры 870а и 870b, накопители 875а и 875b и выходную шину 880.

Нижний 801 блок обработки и верхний 802 блок обработки работают независимо. Соответственно приведенному для примера варианту осуществления настоящего изобретения, шина 840 кода, шина 845 данных и выходные шины 830 и 880 являются однонаправленными шинами. Кроме того, в предпочтительном варианте осуществления настоящего изобретения выходная шина 830 и выходная шина 880 смогут представлять собой одну и ту же шину. По этой причине выходная шина 830 и выходная шина 880 далее упоминаются как «выходная шина 830». Выходная шина 845 посылает данные выборок кодовых элементов из памяти 831 данных на блоки 801 и 802 обработки через элементы 850а-850d. Выходная шина 830 записывает выходные данные с накопителей 825а и 825b и с накопителей 875а и 875b в память 831 данных. Шина 840 кода передает кодовые данные, генерируемые в генераторе 835 кода, на блоки 801 и 802 обработки.

Следует отметить, что блоки 801 и 802 обработки, память 831, генератор 835 кода и шины 830, 840, 845 и 880 могут быть конфигурированы в соответствии с различными стандартами и функциями, включая функции сжатия в системе CDMA, демодуляции в IEEE-802.11b CCK, сжатия в WCDMA, поиска ячейки, сжатия в HSDPA и т.п. Кроме того, каждый из функциональных компонентов и каждая из шин могут быть отключены независимо. Количество элементов 850, объем памяти 831 данных и количество блоков 805 и 855 выбора знака, показанных на фиг.8, приведены только для примера. Как показано ниже, количество блоков 801 и 802 обработки и количество элементов 850, объем памяти 831 данных и количество блоков 805 и 855 выбора знака могут изменяться (например, увеличиваться или уменьшаться) без отклонения от объема изобретения.

На фиг.9 показана блок-схема блока 831 памяти в блоке 800 корреляции согласно варианту осуществления настоящего изобретения. Выборки кодовых элементов подаются из преобразованного с понижением частоты РЧ сигнала во входной каскад приемника (не показан) и сохраняются в четырех банках памяти, в частности, в банке 0, банке 1, банке 2 и банке 3 в памяти 831. Порядок и последовательность, в соответствии с которыми выборки кодовых элементов сохраняются в памяти 831, показаны пунктирной линией со стрелками. Порядок и последовательность могут изменяться в соответствии со степенью передискретизации (дискретизации с повышенной частотой) данных кодовых элементов.

На фиг.9 предполагается, что каждый элемент кода Уолша CDMA дискретизируется четыре раза, и четыре выборки записываются по порядку в памяти 831. Таким образом, 4хN выборок кодовых элементов из общего числа N кодовых элементов, от С(0) до С(N-1) должны быть записаны в память 831. Первый кодовый элемент С(0) дискретизируется четыре раза, и четыре выборки С(0,0), С(0,1), С(0,2) и С(0,3) записываются в адреса ADD0, ADD4, ADD8 и ADD12, соответственно, в банк 0 памяти 831 данных. Аналогичным образом, второй кодовый элемент С(1) дискретизируется четыре раза, и четыре выборки С(1,0), С(1,1), С(1,2) и С(1,3) записываются в адреса ADD1, ADD5, ADD9 и ADD13, соответственно, в банк 1 памяти 831 данных. Третий кодовый элемент С(2) дискретизируется четыре раза, и четыре выборки С(2,0), С(2,1), С(2,2) и С(2,3) записываются в адреса ADD2, ADD6, ADD10 и ADD14, соответственно, в банк 2 памяти 831 данных. И, наконец, четвертый кодовый элемент С(3) дискретизируется четыре раза, и четыре выборки С(3,0), С(3,1), С(3,2) и С(3,3) записываются в адреса ADD3, ADD7, ADD11 и ADD15, соответственно, в банк 3 памяти 831 данных.

Таким способом шестнадцать выборок первых четырех кодовых элементов С(0), С(1), С(2) и С(3) записываются в шестнадцать адресов с ADD0 до ADD15. Этот процесс повторяется, когда шестнадцать выборок следующих четырех кодовых элементов С(4), С(5), С(6) и С(7) записываются в шестнадцать адресов с ADD16 до ADD31. Этот процесс продолжается до тех пор, пока шестнадцать выборок последних четырех кодовых элементов С(N-4), С(N-3), С(N-2) и С(N-1) не будут записаны в память 831 данных.

В приведенном выше примере предполагается, что частота передискретизации равна четырем. Однако частота дискретизации может изменяться для различных беспроводных стандартов. В другой конфигурации частота передискретизации может быть равна восьми, и в этом случае восемь выборок из каждого кодового элемента записываются на глубину восьми адресов в память 831, аналогично показанному на фиг.9. В другой конфигурации частота передискретизации может быть равна двум, и в этом случае две выборки из каждого кодового элемента записываются на глубину двух адресов в память 831, аналогично показанному на фиг.9. В еще одной конфигурации частота дискретизации может быть равна единице на кодовый элемент, и в этом случае одна выборка из каждого кодового элемента записывается в память 831, аналогично показанному на фиг.9.

Длительность каждой выборки кодового элемента может изменяться в соответствии с используемым беспроводным стандартом (например, QPSK, 16QAM), и каждая из выборок кодового элемента может содержать как действительные, так и мнимые биты данных. Например, в первом варианте осуществления настоящего изобретения каждая выборка кодового элемента может иметь восемь битов, включая четыре действительных бита и четыре мнимых бита. Во втором варианте осуществления настоящего изобретения каждая выборка кодового элемента может иметь четыре бита, включая два действительных бита и два мнимых бита.

Когда выборки кодовых элементов должны обрабатываться в блоках 801 и 802 обработки, четыре выборки кодового элемента одновременно считываются из памяти 831 в шину 845 данных. Например, в течение первого цикла считывания, выборки С(0,0), С(1,0), С(2,0) и С(3,0) считываются параллельно из адресов ADD0-ADD3, соответственно, в банк 0, банк 1, банк 2 и банк 3. В течение второго цикла считывания, выборки С(0,1), С(1,1), С(2,1) и С(3,1) считываются параллельно из адресов ADD4-ADD7, соответственно, в банк 0, банк 1, банк 2 и банк 3. Таким образом, четыре выборки кодового элемента одновременно выводятся в шину 845 до тех пор, пока все выборки кодовых элементов не будут считаны.

Когда каждая выборка кодового элемента считана из памяти 831, она загружается в один из элементов 850а-850d сложения-вычитания. Например, в течение первого цикла считывания выборка С(0,0) кодового элемента вводится в элемент 850а сложения-вычитания, выборка С(1,0) кодового элемента вводится в элемент 850b сложения-вычитания, выборка С(2,0) кодового элемента вводится в элемент 850c сложения-вычитания, и выборка С(3,0) кодового элемента вводится в элемент 850d сложения-вычитания. В течение второго цикла считывания выборка С(0,1) кодового элемента вводится в элемент 850а сложения-вычитания, выборка С(1,1) кодового элемента вводится в элемент 850b сложения-вычитания, выборка С(2,1) кодового элемента вводится в элемент 850c сложения-вычитания, и выборка С(3,1) кодового элемента вводится в элемент 850d сложения-вычитания. Таким образом, четыре выборки кодового элемента одновременно вводятся в элементы 850а-850d сложения-вычитания до тех пор, пока все выборки кодовых элементов не будут загружены.

Фиг.10А иллюстрирует более детально элемент сложения-вычитания согласно приведенному для примера варианту осуществления настоящего изобретения. Элемент 850 сложения-вычитания содержит блок сложения и блок вычитания. Элемент 850 сложения-вычитания принимает два входных сигнала a и b и формирует сумму (a+b) и разность (a-b) двух входных сигналов. На фиг.10a на вход а каждого из элементов 850а-850d сложения-вычитания поступают действительные биты выборки кодового элемента, а на вход b каждого из элементов 850а-850d сложения-вычитания поступают мнимые биты выборки кодового элемента.

Суммарный выходной сигнал (a+b) и разностный выходной сигнал (a-b) с каждого из элементов 850а-850d сложения-вычитания затем подаются на входы первого блока 805 выбора знака в нижнем блоке 801 обработки и второго блока 855 выбора знака в верхнем блоке 802 обработки. Например, суммарный выходной сигнал (a+b) и разностный выходной сигнал (a-b) с элемента 850а сложения-вычитания подаются на входы блока 805а выбора знака в нижнем блоке 801 обработки и блока 855а выбора знака в верхнем блоке 802 обработки. Каждый блок выбора знака также получает из шины 840 кода два кодовых бита, генерируемых генератором 835 кода. Последовательность кодовых битов может изменяться в соответствии со стандартом беспроводной связи, в соответствии с которым конфигурирован блок 800 корреляции.

В приведенном для примера варианте осуществления настоящего изобретения генератор 835 кода может содержать два компонента: 1) генератор кода скремблирования и 2) две локальных кольцевых памяти. Генератор кода скремблирования используется для некоторых систем, подобных CDMA. Локальные кольцевые памяти хранят коды расширения в системах CDMA. Эти компоненты могут быть использованы для хранения некоторых предварительно определенных шаблонов, как в случае поиска ячейки в системе WCDMA. Генератор кода скремблирования может отключаться, если он не используется. Например, в соответствии с приведенным для примера вариантом осуществления настоящего изобретения шестнадцать кодовых битов с генератора 835 кода могут подаваться на восемь блоков 805а-d и 855а-d выбора знака следующим образом:

Ur0 Ui0 Lr0 Li0 Ur1 Ui1 Lr1 Li1 Ur2 Ui2 Lr2 Li2 Ur3 Ui3 Lr3 Li3

где Urj - j-й действительный кодовый бит для верхнего блока 802 обработки, Uij - j-й мнимый кодовый бит для верхнего блока 802 обработки, Lrj - j-й действительный кодовый бит для нижнего блока 801 обработки, Lij - j-й мнимый кодовый бит для нижнего блока 801 обработки. Таким образом, например, первые два кодовых бита Ur0 и Ui0 подаются на блок 855а выбора знака, и следующие два кодовых бита Lr0 и Li0 подаются на блок 805а выбора знака.

Фиг.10В изображает таблицу истинности, иллюстрирующую более детально работу блоков 805а-d и 855а-d выбора знака согласно приведенному для примера варианту осуществления настоящего изобретения. Каждый из блоков 805а-d и 855а-d выбора знака получает суммарный входной сигнал (a+b) и разностный входной сигнал (a-b) с одного из элементов 850а-d сложения-вычитания. Каждый из блоков 805а-d и 855а-d выбора знака также получает действительный бит CG(Re) генератора кода и мнимый бит CG(Im) генератора кода. В ответ каждый из блоков 805а-d и 855а-d выбора знака формирует действительный выходной сигнал Output(Re) и мнимый выходной сигнал Output(Im), в соответствии со значением действительного и мнимого битов генератора кода.

Например, если блок 855а выбора знака получает входной сигнал CG(Re)=Ur0=1 и входной сигнал CG(Im)=Ui0=0, то действительный и мнимый выходные сигналы блока 855а выбора знака будут Output(Re)=(-a+b) и Output(Im)=(-a-b). По существу, каждый из элементов 850а-d формирует суммарное и разностное значение (a+b) и (a-b), и затем каждый из блоков 805а-d и 855а-d выбора знака умножает (a+b) и (a-b) на +1 или -1, в зависимости от значений соответствующих действительного и мнимого битов генератора кода CG(Re) и CG(Im).

Каждый из действительного и мнимого выходных сигналов Output(Re) и Output(Im) с каждого из блоков 805 и 855 выбора знака затем подается на сумматоры 810а-d и 860a-d первого каскада. Например, действительный выходной сигнал Output(Re) с блока 805а выбора знака подается на первый вход действительного (Re) сумматора 810а, а мнимый выходной сигнал Output(Im) с блока 805а выбора знака подается на первый вход мнимого (Im) сумматора 810b. Аналогичным образом, действительный выходной сигнал Output(Re) с блока 805b выбора знака подается на второй вход действительного (Re) сумматора 810а, а мнимый выходной сигнал Output(Im) с блока 805b выбора знака подается на второй вход мнимого (Im) сумматора 810b.

Действительный и мнимый суммарные сигналы, сформированные сумматорами 810а-d и 860a-d первого каскада, затем подаются на мультиплексоры 815а-b и 865a-b. Например, мультиплексор 815а получает действительный суммарный сигнал, сформированный сумматором 810а, и получает мнимый суммарный сигнал, сформированный сумматором 810b. Мультиплексоры 815а и 815b, 865a и 865b подают затем либо действительные суммарные сигналы, либо мнимые суммарные сигналы на сумматоры 820а-b и 870a-b второго каскада. Например, действительный (Re) сумматор 820а получает действительный суммарный сигнал, сформированный сумматором 810а, в качестве первого входного сигнала с мультиплексора 815а и получает действительный суммарный сигнал, сформированный сумматором 810с, в качестве второго входного сигнала с мультиплексора 815b. Аналогичным образом, мнимый (Im) сумматор 820b получает мнимый суммарный сигнал, сформированный сумматором 810b, в качестве первого входного сигнала с мультиплексора 815а и получает мнимый суммарный сигнал, сформированный сумматором 810d, в качестве второго входного сигнала с мультиплексора 815b.

В нижнем блоке 801 обработки суммарный сигнал, сформированный действительным сумматором 820а, суммируется со значением в действительном накопителе 825а, и суммарный сигнал, сформированный мнимым сумматором 820b, суммируется со значением в мнимом накопителе 825b. В верхнем блоке 802 обработки суммарный сигнал, сформированный действительным сумматором 870а, суммируется со значением в действительном накопителе 875а, и суммарный сигнал, сформированный мнимым сумматором 870b, суммируется со значением в мнимом накопителе 875b.

На фиг.10С представлена блок-схема 1000, иллюстрирующая работу блоков 801 и 802 обработки в блоке 800 корреляции согласно принципам настоящего изобретения. Для простоты предполагается, что со ссылкой на фиг.10С описывается нижний блок 801 обработки. Сначала четыре выборки кодового элемента считываются из памяти 831 в блок 801 обработки (этап обработки 1005). Затем элементы 850а-850d сложения-вычитания формируют суммарные значения (а+b) и разностные значения (a-b) (этап обработки 1010). Знаки суммарных и разностных значений изменяются в соответствии кодовыми битами с генератора 835 кода. Затем осуществляется суммирование первого каскада (этап обработки 1015). Суммирование первого каскада сокращает четыре действительных входных сигнала с блоков 810а-810d выбора знака до двух действительных суммарных значений и сокращает четыре мнимых входных сигнала с блоков 810а-810d выбора знака до двух мнимых суммарных значений.

Затем осуществляется суммирование второго этапа (этап обработки 1020). Суммирование второго каскада сокращает два действительных суммарных сигнала с сумматоров первого каскада до одного действительного суммарного значения и сокращает два мнимых суммарных сигнала с сумматоров первого каскада до одного мнимого суммарного значения. Действительные и мнимые суммарные значения, сформированные сумматорами второго каскада, затем отдельно накапливаются (этап обработки 1025). Наконец, если все кодовые элементы в символе просуммированы в накопителях 825а и 825b, значения в накопителях 825а и 825b записываются в память 831 по шине 830.

Следует отметить, что будут иметь место различные коэффициенты расширения в соответствии с используемыми стандартами беспроводной связи и типом обрабатываемого сигнала. Например, если нижний блок 801 обработки обрабатывает сигнал из выделенного физического канала (DPCH) в среде WCDMA, то будет иметься 8 кодовых элементов в символе. В этом случае данные записываются из накопителей 825а и 825b однократно на каждые 8 кодовых элементов. В то же время, верхний блок 802 обработки может обрабатывать общий канал пилот-сигнала (СРICH), используемый в среде WCDMA. Сигнал канала CPICH использует код расширения 0, который имеет 256 кодовых элементов на символ. В таком случае данные записываются из накопителей 875а и 875b однократно на каждые 256 кодовых элементов. Этот сценарий изображен на фиг.11.

На фиг.11 представлены выводы данных блока 800 корреляции в процессе сжатия сигнала WCDMA согласно варианту осуществления настоящего изобретения. На фиг.11 нижний блок 801 обработки обрабатывает сигнал выделенного физического канала (DPCH), который использует 8-элементные символы, а верхний блок 802 обработки обрабатывает сигнал общего канала пилот-сигнала (CPICH), который использует 256-элементные символы. В течение цикла 1 обработки нижний блок 801 обработки и верхний блок 802 обработки обрабатывают каждый первые четыре кодовых элемента от элемента 0 до элемента 3.

Если одна выборка берется на каждый кодовый элемент, то цикл 1 обработки требует только одного цикла считывания из памяти 831. Если две выборки берутся на каждый кодовый элемент (частота передискретизации равна 2), то цикл 1 обработки требует двух циклов считывания из памяти 831. Если четыре выборки берутся на каждый кодовый элемент (частота передискретизации равна 4), то цикл 1 обработки требует четырех циклов считывания из памяти 831. В конце цикла обработки 1 блок 801 обработки сохраняет результаты в накопителях 825а и 825b, но еще не обеспечивает выходной сигнал, поскольку полный 8-элементный символ еще не обработан. Аналогичным образом, в конце цикла обработки 1 блок 802 обработки сохраняет результаты в накопителях 875а и 875b, но еще не обеспечивает выходной сигнал, поскольку полный 256-элементный символ еще не обработан.

В течение цикла 2 обработки нижний блок 801 обработки и верхний блок 802 обработки обрабатывают каждый следующие четыре кодовых элемента от элемента 4 до элемента 7. В конце цикла 2 обработки блок 801 обработки выводит результаты в накопителях 825а и 825b как данные 1, поскольку полный 8-элементный символ обработан. В конце цикла обработки 2 блок 802 обработки продолжает сохранять результаты в накопителях 875а и 875b, но еще не обеспечивает выходной сигнал, поскольку полный 256-элементный символ еще не обработан.

Этот процесс продолжается для всех 64 циклов обработки, причем блок 801 обработки выдает результат каждые два цикла как группы из восьми кодовых элементов. Блок 802 обработки выводит один результат - пилот-сигнал 1 в цикле обработки 64, после того как все 256 кодовых элементов обработаны.

Фиг.12 представляет вывод данных блока корреляции по фиг.8 в течение операции поиска ячейки WCDMA согласно варианту осуществления настоящего изобретения. Блок 801 обработки отстает от блока 802 обработки на 4 кодовых элемента. Иными словами, блок 802 обработки начинает обработку, а блок 801 обработки следует за блоком 801 обработки с отставанием, по меньшей мере, на предварительно заданный цикл обработки, в частности 4 кодовых элемента. В конце цикла обработки 1 блок 802 обработки обработал первые четыре кодовых элемента, от элемента 90 до элемента 3, в то время как блок 801 обработки был отключен (неактивен). В конце цикла обработки 2 блок 802 обработки обработал всего 8 кодовых элементов, а блок 801 обработки обработал всего 4 кодовых элемента. В конце цикла обработки 3 блок 802 обработки обработал всего 12 кодовых элементов, а блок 801 обработки обработал всего 8 кодовых элементов. В конце цикла обработки 4 блок 802 обработки обработал всего 16 кодовых элементов, а блок 801 обработки обработал всего 12 кодовых элементов.

В конце цикла обработки 64 блок 802 обработки обработал всего 256 кодовых элементов и выводит результат Out 1. В то же самое время блок 801 обработки обработал всего 252 кодовых элемента. В конце цикла обработки 65 блок 801 обработки обработал всего 256 кодовых элементов и выводит результат Out 2. В конце цикла обработки 65 блок 802 обработки отключен (неактивен). Иными словами, блок 802 обработки, который начинает операции обработки с опережением, по меньшей мере, на предварительно заданный цикл обработки, в частности 4 кодовых элемента, становится неактивным до тех пор, пока другой подблок обработки, в частности, блок 801 обработки не закончит операции обработки после завершения операций обработки работающего подблока, в частности блока 802 обработки.

Предпочтительным образом, поскольку память 831, генератор 835 кода и блоки 801 и 802 обработки слабо связаны, эти компоненты могут конфигурироваться для различных систем и/или функций. Таким образом, память 831, генератор 835 кода и блоки 801 и 802 обработки могут отключаться по отдельности, если они не используются, для экономии мощности питания. Кроме того, архитектура блока корреляции, описанного выше, легко масштабируется и может легко дублироваться для достижения требуемых рабочих характеристик.

Хотя настоящее изобретение описано на примере конкретного варианта осуществления, специалисты в данной области техники смогут предложить различные изменения и модификации. Предусматривается, что настоящее изобретение охватывает все такие изменения и модификации, которые находятся в пределах объема пунктов формулы изобретения.

Изобретение относится к системе связи и может быть использовано в устройствах бытовой электронике, устройствах промышленного назначения, научной аппаратуре и сети связи. Технический результат - повышение скорости передачи. Блок корреляции для корреляционной обработки последовательности выборок кодовых элементов содержит: 1) память для хранения последовательности выборок кодовых элементов; 2) множество элементов сложения-вычитания, причем каждый из элементов сложения-вычитания может принимать множество действительных битов а из первой выборки кодовых элементов в памяти и множество мнимых битов b из первой выборки кодовых элементов; и 3) множество блоков выбора знака. Каждый из множества блоков выбора знака принимает из одного множества элементов сложения-вычитания первый входной сигнал, равный сумме (a+b), множества действительных битов а и множества мнимых битов b, и второй выходной сигнал, равный разности (a-b), множества действительных битов а и множества мнимых битов b. Каждый блок выбора знака генерирует действительный выходной сигнал и мнимый выходной сигнал, которые соответственно равны одному из следующих: 1) сумме (a+b), умноженной на +1 или -1, и 2) разности (a-b), умноженной на +1 или -1. 4 н. и 21 з.п. ф-лы, 14 ил.

1. Реконфигурируемый блок корреляции для корреляционной обработки последовательности выборок кодовых элементов, причем упомянутый реконфигурируемый блок корреляции содержит:

память для хранения последовательности выборок кодовых элементов;

генератор кода для генерации последовательности кодовых битов;

множество элементов сложения-вычитания, причем каждый из элементов сложения-вычитания может принимать множество действительных битов a из первой выборки кодовых элементов в памяти и множество мнимых битов b из первой выборки кодовых элементов; и

блок обработки, содержащий:

множество блоков выбора знака, причем каждый из множества блоков выбора знака принимает из одного из множества элементов сложения-вычитания первый входной сигнал, равный сумме (a+b) множества действительных битов a и множества мнимых битов b, и второй выходной сигнал, равный разности (a-b) множества действительных битов a и множества мнимых битов b, и каждый блок выбора знака генерирует действительный выходной сигнал и мнимый выходной сигнал, причем каждый из указанных действительного выходного сигнала и мнимого выходного сигнала равен одному из следующих: 1) сумме (a+b), умноженной на +1 или -1, и 2) разности (a-b), умноженной на +1 или -1.

2. Блок корреляции по п.1, в котором каждый блок выбора знака получает действительный кодовый бит и мнимый кодовый бит из последовательности, и при этом действительный и мнимый кодовые биты определяют значение действительного выходного сигнала и значение мнимого выходного сигнала каждого блока выбора знака.

3. Блок корреляции по п.2, в котором блок обработки дополнительно содержит первый каскад сумматоров, содержащий первое множество действительных сумматоров и первое множество мнимых сумматоров.

4. Блок корреляции по п.3, в котором каждый из первого множества действительных сумматоров принимает первый действительный выходной сигнал с одного из множества блоков выбора знака и второй действительный выходной сигнал с другого из множества блоков выбора знака и формирует действительный суммарный выходной сигнал.

5. Блок корреляции по п.4, в котором каждый из первого множества мнимых сумматоров принимает первый мнимый выходной сигнал с одного из множества блоков выбора знака и второй мнимый выходной сигнал с другого из множества блоков выбора знака и формирует мнимый суммарный выходной сигнал.

6. Блок корреляции по п.5, в котором блок обработки дополнительно содержит второй каскад сумматоров, содержащий, по меньшей мере, один действительный сумматор и, по меньшей мере, один мнимый сумматор.

7. Блок корреляции по п.6, в котором каждый из, по меньшей мере, одного действительного сумматора во втором каскаде принимает первый действительный суммарный выходной сигнал с одного из первого множества действительных сумматоров и второй действительный выходной сигнал с другого из первого множества действительных сумматоров и формирует действительный суммарный выходной сигнал.

8. Блок корреляции по п.7, в котором каждый из, по меньшей мере, одного мнимого сумматора во втором каскаде принимает первый мнимый суммарный выходной сигнал с одного из первого множества мнимых сумматоров и второй мнимый суммарный выходной сигнал с другого из первого множества мнимых сумматоров и формирует мнимый суммарный выходной сигнал.

9. Блок корреляции по п.8, в котором блок обработки дополнительно содержит первый накопитель, выполненный с возможностью приема и накопления действительных суммарных выходных сигналов с упомянутого, по меньшей мере, одного действительного сумматора в упомянутом втором каскаде.

10. Блок корреляции по п.9, в котором блок обработки дополнительно содержит второй накопитель, выполненный с возможностью приема и накопления действительных суммарных выходных сигналов с упомянутого, по меньшей мере, одного мнимого сумматора в упомянутом втором каскаде.

11. Блок корреляции по любому из пп.1-10, в котором реконфигурируемый блок корреляции для корреляционной обработки последовательности выборок кодовых элементов применяется в системе радиосвязи, определяемой программным обеспечением (SDR), содержащей реконфигурируемый процессор данных.

12. Реконфигурируемый блок корреляции для корреляционной обработки последовательности выборок кодовых элементов, причем упомянутый реконфигурируемый блок корреляции содержит:

память для хранения последовательности выборок кодовых элементов;

множество элементов сложения-вычитания, причем каждый из элементов сложения-вычитания может принимать множество действительных битов a из первой выборки кодовых элементов в памяти и множество мнимых битов b из первой выборки кодовых элементов; и

блок обработки, содержащий верхний блок обработки и нижний блок обработки, причем упомянутые верхний и нижний блоки обработки являются по существу идентичными и каждый из них содержит:

множество блоков выбора знака, причем каждый из множества блоков выбора знака принимает из одного из множества элементов сложения-вычитания первый входной сигнал, равный сумме (a+b) множества действительных битов a и множества мнимых битов b, и второй выходной сигнал, равный разности (a-b) множества действительных битов а и множества мнимых битов b, и каждый блок выбора знака генерирует действительный выходной сигнал и мнимый выходной сигнал, причем каждый из указанных действительного выходного сигнала и мнимого выходного сигнала равен одному из следующих: 1) сумме (a+b), умноженной на +1 или -1, и 2) разности (a-b), умноженной на +1 или -1.

13. Блок корреляции по п.12, в котором один из двух подблоков обработки инициирует операции обработки, а другой подблок обработки следует за ним с отставанием, по меньшей мере, на предварительно заданный цикл обработки.

14. Блок корреляции по п.13, в котором упомянутый один подблок обработки, который инициирует операции обработки, до упомянутого предварительно заданного цикла обработки, становится неактивным до тех пор, пока другой блок обработки не завершит операции обработки после завершения операций обработки упомянутого, по меньшей мере, одного подблока обработки.

15. Реконфигурируемый блок для обработки множества контекстных команд, содержащий

множество процессоров для исполнения каждой из предварительно определенных команд конкретного контекста;

память программы для хранения управляющей программы из внешней линии управления;

контроллер последовательности команд для извлечения программных команд из памяти программы, упорядочивания контекстов и посылки упорядоченных контекстов в виде битов реконфигурирования на соответствующий процессор из упомянутого множества процессоров; и

коммутатор межсоединений, подсоединенный между каждым из множества процессоров и внешней шиной данных, для посылки данных из шины данных на соответствующий процессор из множества процессоров.

16. Реконфигурируемый блок по п.15, дополнительно содержащий буфер, который находится между упомянутой линией управления и памятью программы и между упомянутой линией управления и контроллером последовательности команд.

17. Реконфигурируемый блок по п.15, дополнительно содержащий буфер, который находится между шиной данных и коммутатором межсоединений.

18. Реконфигурируемый блок по п.15, в котором реконфигурируемый блок выполняется в системах радиосвязи, определяемой программным обеспечением (SDR).

19. Реконфигурируемый блок по п.18, в котором один из упомянутого множества процессоров исполняет контекстно-связанные команды, которые обрабатывают сигналы базовой полосы.

20. Реконфигурируемый блок по п.18, в котором один из упомянутого множества процессоров исполняет контекстно-связанные команды, которые действуют как контроллер памяти.

21. Реконфигурируемый блок по п.18, в котором один из упомянутого множества процессоров исполняет контекстно-связанные команды, которые выполняют обработку MPEG-4 для мультимедийных приложений.

22. Способ корреляционной обработки последовательности выборок кодовых элементов в системах радиосвязи, определяемых программным обеспечением (SDR), содержащий:

считывание множества действительных битов а из первой выборки кодовых элементов, сохраненной в памяти, и множества мнимых битов b из упомянутой первой выборки кодовых элементов;

формирование посредством множества элементов сложения-вычитания суммы (a+b) множества действительных битов a и множества мнимых битов b и разности (a-b) множества действительных битов а и множества мнимых битов b;

формирование посредством множества элементов сложения-вычитания действительного выходного сигнала, равного сумме (a+b), умноженной на один из кодовых битов +1 и -1, генерируемых генератором кода, и мнимого выходного сигнала, равного разности (a-b), умноженной на один из кодовых битов +1 и -1;

в первом каскаде суммирования, суммирование первых действительных выходных сигналов из действительных выходных сигналов, сформированных каждым из упомянутого множества элементов сложения-вычитания, суммирование первых мнимых выходных сигналов из мнимых выходных сигналов, сформированных каждым из упомянутого множества элементов сложения-вычитания, суммирование вторых действительных выходных сигналов из действительных сигналов, сформированных каждым из упомянутого множества элементов сложения-вычитания, и суммирование вторых мнимых выходных сигналов из множества мнимых выходных сигналов, сформированных каждый из упомянутого множества элементов сложения-вычитания,

во втором каскаде суммирования, суммирование суммарных первых действительных выходных сигналов и суммарных вторых действительных выходных сигналов и формирование окончательного действительного выходного сигнала и суммирование суммарных первых мнимых выходных сигналов и суммарных вторых мнимых выходных сигналов и формирование окончательного мнимого выходного сигнала, и

отдельное накопление каждого из окончательного действительного выходного сигнала и окончательного мнимого выходного сигнала для всех выборок кодовых элементов для формирования предварительно заданного символа и вывод накопленных результатов в качестве результатов корреляции.

23. Способ по п.22, в котором выборки кодового элемента представляют собой 8-элементные выборки для формирования символа, принимаемого посредством выделенного физического канала (DPCH).

24. Способ по п.22, в котором выборки кодового элемента представляют собой 256-элементные выборки для формирования символа, принимаемого посредством общего канала пилот-сигнала (CPICH).

25. Способ по п.23 или 24, в котором множество элементов сложения-вычитания составляет 4 элемента.

| Lie-Liang; Hanzo, L | |||

| "Software-defined-radio-assisted adaptive broadband freguency hopping multicarrier DS-CDMA" Communications Magazine, IEEE Volume 40, Issue 3, March, 2002, page(s): 174-183 | |||

| СПОСОБЫ И УСТРОЙСТВО СВЯЗИ, ОСНОВАННЫЕ НА ОРТОГОНАЛЬНЫХ ПОСЛЕДОВАТЕЛЬНОСТЯХ АДАМАРА, ИМЕЮЩИХ ВЫБРАННЫЕ КОРРЕЛЯЦИОННЫЕ СВОЙСТВА | 1999 |

|

RU2234196C2 |

| УСТРОЙСТВО ДЛЯ ПРЕОБРАЗОВАНИЯ ЭНЕРГИИ ТЕКУЧЕЙ СРЕДЫ | 1998 |

|

RU2142572C1 |

| СПОСОБ ПЕРЕДАЧИ ДАННЫХ И УСТРОЙСТВО ДЛЯ КОДИРОВАНИЯ СИГНАЛА | 1997 |

|

RU2191470C2 |

| Способ и приспособление для нагревания хлебопекарных камер | 1923 |

|

SU2003A1 |

Авторы

Даты

2009-12-20—Публикация

2006-02-17—Подача