Предлагаемое изобретение относится к технике связи и может быть использовано в различных устройствах, реализованных на основе систем фазовой автоподстройки частоты (ФАПЧ).

Системы ФАПЧ широко применяются в приемниках фазоманипулированных сигналов для создания опорного напряжения при синхронном детектировании.

Если время появления сигнала предсказать заранее нельзя, то очень важной технологической операцией в процессе приема является обнаружение появившегося сигнала. По факту его появления автоматически принимается ряд решений, в том числе:

- прекращение ввода целеуказаний по частоте или прекращение поиска;

- подготовка дальнейшего тракта для приема и обработки выделенной информации;

- введение признака достоверности информации и т.п.

Под термином «обнаружение сигнала» здесь понимается не только определение факта его физического появления, но и факт вхождения в синхронизм системы ФАПЧ, как завершающей этап подготовки к выделению информации.

Если в сигнале присутствует несущая частота, то классическим методом обнаружения сигнала (захвата ФАПЧ) является когерентное накопление сигнала в квадратурном канале В на некотором интервале Тобн. Интервал, вообще говоря, может быть любым и не связан с циклом регулирования. Накопленное число Вобн сравнивается с некоторым порогом. В случае превышения порога принимается решение о наличии сигнала и захвате ФАПЧ.

В современной технике связи часто используются сигналы с манипуляцией несущей частоты на 180° последовательностью двоичных символов. Если чередование символов носит случайный характер, то в результате такой манипуляции несущая подавляется. Для восстановления несущей при приеме сигнала используются системы фазовой автоподстройки частоты, нечувствительные к перевороту фазы на 180° (в качестве ближайшего аналога предлагаемого изобретения выбрано техническое решение, описанное в книге Банкет В.Л., Мельник A.M. «Системы восстановления несущей при когерентном приеме дискретных сигналов», «Зарубежная радиоэлектроника», 12/83, стр.28-49, М.: Радио и связь).

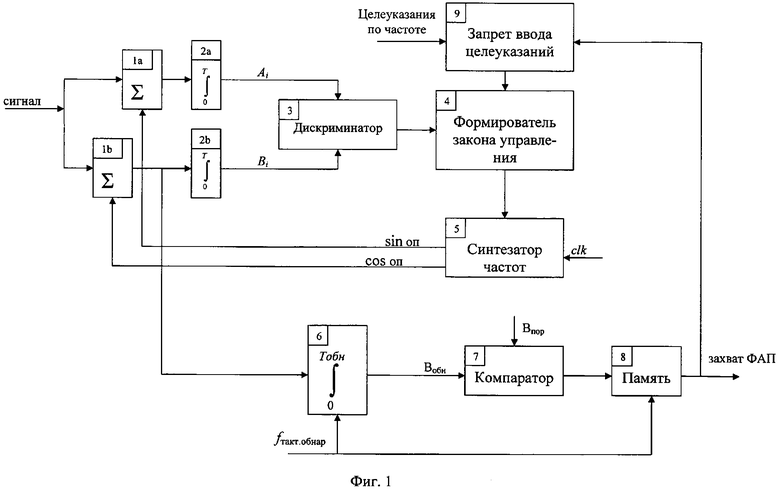

Известная система ФАПЧ (фигура 1) содержит квадратурные смесители 1а и 1b, накопители сигнала 2а и 2b на интервале 0…Т, дискриминатор 3, формирователь закона регулирования 4, синтезатор частот 5 с двумя квадратурными выходами (со сдвигом на 90°), которые в качестве гетеродинов подключены ко вторым входам смесителей 1а и 1b.

Если частота принимаемого сигнала неизвестна и выходит за границы полосы захвата, то для вхождения ФАПЧ в синхронизм в общем случае требуется поиск или ввод целеуказаний по частоте в формирователь закона управления 5. По завершении вхождения ФАПЧ в синхронизм поиск или ввод целеуказаний должен быть остановлен по команде «захват ФАП».

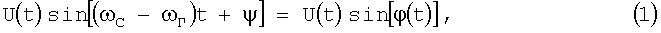

На выходе смесителей 1а и 1б существуют две компоненты разностного сигнала, первые гармоники которых могут быть записаны:

и

Накопители 2а и 2b циклически производят первичное когерентное накопление (интегрирование) первого (1) и второго (2) процессов в пределах 0…Т. Время интегрирования Т (цикл регулирования) выбирается исходя из скорости передачи информации полосы ФАПЧ и энергетики в канале связи. Время Т не может превышать длительность информационного бита. При вхождении в связь, когда границы символов неизвестны, приходится это время уменьшать еще, по крайней мере, вдвое.

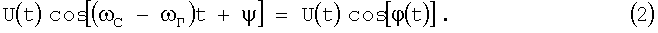

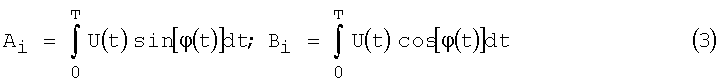

В результате накопления в каждом i-том цикле на выходе интеграторов формируются отсчеты Ai и Bi:

Если пренебречь изменением фазы за время накопления, то отсчеты Ai и Bi представляют собой проекции вектора сигнала на две ортогональные оси системы координат, задаваемой опорным сигналом (гетеродином). Поскольку опорный сигнал перестраивается в петле ФАПЧ, то в процессе подстройки один из отсчетов (Ai) стремится к нулю, а другой (Bi) - к максимуму.

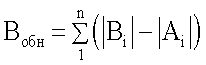

В системе, рассчитанной на прием сигнала с подавленной несущей, нельзя с целью повышения надежности обнаружения производить когерентное накопление в канале В в течение времени, превышающего длительность информационного символа. В противном случае смена знаков числа Bi в процессе интегрирования приведет к тому, что число Вобн будет стремиться к нулю, и ситуация не будет отличаться от случая отсутствия сигнала. Если при слабом сигнале принимать решение о захвате ФАПЧ по единичной реализации Bi, то вероятность правильного решения будет недостаточной. Поэтому в прототипе используется вторичное (некогерентное) накопление - суммирование модулей чисел Bi (|Bi|).

где n - число суммируемых реализации;

Такой способ накопления имеет серьезный недостаток при обнаружении сильного сигнала. Если ФАПЧ в захвате, то Вобн будет иметь максимально возможное значение Вобн.max. Однако при отсутствии захвата будут биения.

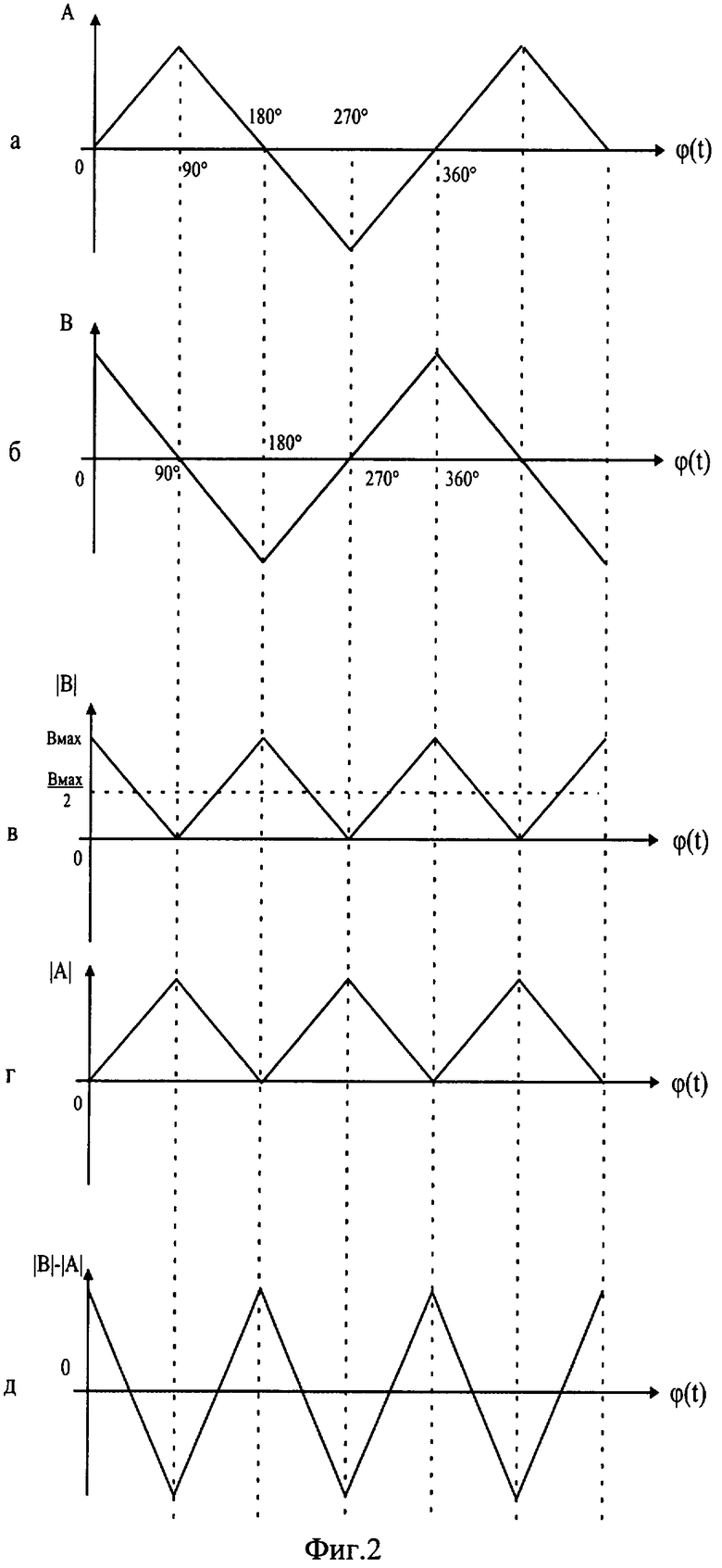

На фигуре 2 показаны эпюры процессов в двух квадратурных каналах для бинарного квантования при наличии биений при чистом сигнале.

Эпюры 2а и 2б - исходные синусная и косинусная квадратурные составляющие;

Эпюра 2в - график модуля числа В т.е. (|В|). Все реализации |Bi| находятся в положительной области. Если при этом производится накопление по формуле 4, то

Это означает, что в системе, рассчитанной на прием и сильных и слабых сигналов, нельзя устанавливать порог ниже  . Но в этом случае слабые сигналы обнаруживаться не будут. И, наоборот, при установке низкого порога при сильном сигнале велика вероятность получения ложной информации о захвате, когда захвата нет (режим биений).

. Но в этом случае слабые сигналы обнаруживаться не будут. И, наоборот, при установке низкого порога при сильном сигнале велика вероятность получения ложной информации о захвате, когда захвата нет (режим биений).

Предлагаемое изобретение обеспечивает устранение указанного выше недостатка, что позволит четко различать в системе ФАПЧ захват и режим биений и, следовательно, устанавливать любой порог обнаружения.

Технический результат, ожидаемый от использования предлагаемого изобретения, достигается тем, что предложен способ определения захвата системы фазовой автоподстройки частоты при приеме сигнала, манипулированного на 180°, а также устройство определения захвата цифровой системы фазовой автоподстройки частоты для приема фазоманипулированных сигналов с подавленной несущей.

Система ФАПЧ устройства определения захвата включает в себя квадратурные каналы первичного накопления сигнала, на выходе которых формируются текущие значения Ai и Bi соответственно, дискриминатор, формирователь закона управления, синтезатор восстановленной несущей частоты с квадратурными выходами, а также устройство накопления сигнала в течение интервала обнаружения Тобн. Устройство накопления сигнала в течение интервала обнаружения Тобн обеспечивает определение захвата ФАПЧ, выход которого подключен к компаратору, сравнивающему накопленное число с порогом обнаружения сигнала. В качестве устройства накопления сигнала в течение интервала обнаружения Тобн используется устройство, обеспечивающее суммирование текущих разностей модулей

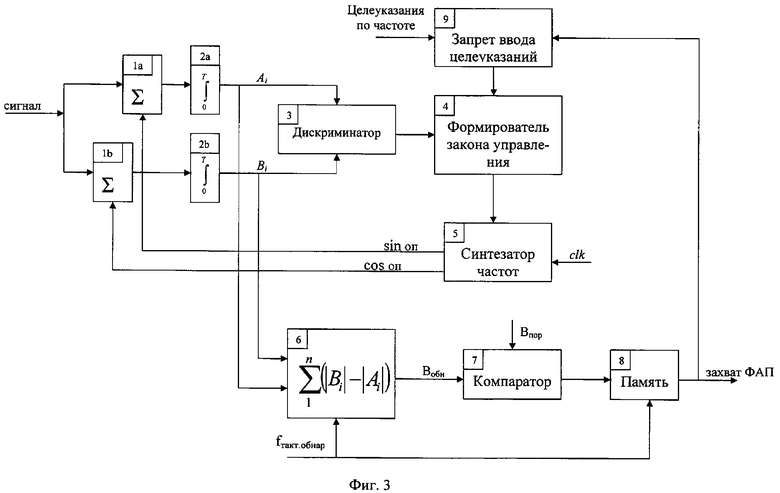

Структурная схема предлагаемого изобретения приведена на фигуре 3. Для обеспечения четкого различия в системе ФАПЧ захвата и режима биений предлагается накапливать не |Bi|, а |Bi|-|Ai|. Так как в режиме захвата ФАПЧ Ai стремится к нулю, результат накопления будет примерно такой же, как и при суммировании |Bi| в прототипе. В режиме биений выражение |Bi|-|Ai| будет знакопеременным, так как, если |Bi|=0, то |Ai| максимально, и наоборот (см. эпюры фиг.2в, г, д). Поэтому в режиме биений результат накопления |Bi|-|Ai| в среднем будет нулевым, как и при отсутствии сигнала, следовательно, в предложенном техническом решении отсутствуют ограничения на установку порога ниже  .

.

Система ФАПЧ включает квадратурные смесители 1а и 1b, накопители сигнала 2а и 2b на интервале 0…Т, дискриминатор 3, формирователь закона регулирования 4, синтезатор частот 5 с двумя квадратурными выходами (со сдвигом на 90°), которые в качестве гетеродинов подключены ко вторым входам смесителей 1а и 1b, устройство, обеспечивающее суммирование текущих разностей модулей

на интервале обнаружения

на интервале обнаружения  компаратор 7, элемент памяти 8, блок запрета ввода целеуказаний 9.

компаратор 7, элемент памяти 8, блок запрета ввода целеуказаний 9.

Сигнал поступает на вход первого 1а и второго 1b квадратурных смесителей и далее на вход первого 2а и второго 2b накопителей сигнала, на выходе которых формируются текущие числа Ai и Bi соответственно. Выходы первого 2а и второго 2b накопителей сигнала соединены с входом дискриминатора 3. Выход дискриминатора 3 соединен с входом формирователя закона управления 4. Другой вход формирователя закона управления 4 соединен с блоком 9 запрета ввода целеуказаний. Выход формирователя закона управления 4 соединен с входом синтезатора частот 5. Выходы sinоп и cosоп синтезатора частот 5 соединены с входами первого 1а и второго 1b квадратурных смесителей соответственно.

Значения текущих чисел Ai и Bi подаются также на вход устройства суммирования  6, на другой вход которого поступает тактовая частота

6, на другой вход которого поступает тактовая частота  Тактовая частота задает число n в формуле

Тактовая частота задает число n в формуле  а, следовательно, время обнаружения Тобн. Выход устройства суммирования 6 соединен с входом компаратора 7, на другой вход которого поступает значение порога обнаружения сигнала Впор, последовательно соединенного с элементом памяти, на вход которого поступает тактовая частота, выход которого соединен с входом блока запрета ввода целеуказаний. Полученное значение суммы Вобн сравнивают с порогом обнаружения сигнала Впор и производят выдачу сигнала на запрет ввода целеуказаний при превышении значением Вобн порога обнаружения сигнала, выход компаратора соединен с элементом памяти 8. По завершении вхождения ФАПЧ в синхронизм поиск или ввод целеуказаний должен быть остановлен по команде «захват ФАП».

а, следовательно, время обнаружения Тобн. Выход устройства суммирования 6 соединен с входом компаратора 7, на другой вход которого поступает значение порога обнаружения сигнала Впор, последовательно соединенного с элементом памяти, на вход которого поступает тактовая частота, выход которого соединен с входом блока запрета ввода целеуказаний. Полученное значение суммы Вобн сравнивают с порогом обнаружения сигнала Впор и производят выдачу сигнала на запрет ввода целеуказаний при превышении значением Вобн порога обнаружения сигнала, выход компаратора соединен с элементом памяти 8. По завершении вхождения ФАПЧ в синхронизм поиск или ввод целеуказаний должен быть остановлен по команде «захват ФАП».

Таким образом, предлагаемое техническое решение обеспечивает четкую селекцию захвата ФАПЧ от наличия биений при отсутствии захвата, что позволяет устанавливать любой порог обнаружения при приеме как слабых, так и сильных сигналов.

| название | год | авторы | номер документа |

|---|---|---|---|

| ЦИФРОВАЯ СИСТЕМА ФАЗОВОЙ АВТОПОДСТРОЙКИ ЧАСТОТЫ (ВАРИАНТЫ) | 2008 |

|

RU2383991C2 |

| УСТРОЙСТВО ВЫСОКОСКОРОСТНОГО РАДИОПРИЕМА БЛОКА ЧИСЕЛ | 2010 |

|

RU2419967C1 |

| СПОСОБ ФОРМИРОВАНИЯ КОГЕРЕНТНОГО ЧАСТОТНО-МОДУЛИРОВАННОГО СИГНАЛА ДЛЯ РЛС С ПЕРИОДИЧЕСКОЙ ЧМ МОДУЛЯЦИЕЙ И УСТРОЙСТВО, РЕАЛИЗУЮЩЕЕ СПОСОБ | 2006 |

|

RU2347235C2 |

| СПОСОБ УВЕЛИЧЕНИЯ ПОЛОСЫ ЗАХВАТА СИСТЕМЫ ФАЗОВОЙ АВТОПОДСТРОЙКИ ЧАСТОТЫ С ЗНАКОВЫМ ЛОГИЧЕСКИМ ФАЗОВЫМ ДИСКРИМИНАТОРОМ И УСТРОЙСТВО ДЛЯ ЕГО РЕАЛИЗАЦИИ | 2015 |

|

RU2582878C1 |

| УСТРОЙСТВО ФАЗОВОЙ АВТОПОДСТРОЙКИ ЧАСТОТЫ | 2014 |

|

RU2565526C1 |

| Устройство для автоподстройки частоты и цифровой обнаружитель-измеритель частоты | 1982 |

|

SU1092733A1 |

| СИСТЕМА ПЕРЕДАЧИ ИНФОРМАЦИИ | 2003 |

|

RU2248097C2 |

| УСТРОЙСТВО ДЛЯ СОЗДАНИЯ ПРИЦЕЛЬНЫХ ПОМЕХ РАДИОЛОКАЦИОННЫМ СТАНЦИЯМ | 2006 |

|

RU2329603C2 |

| МОНОИМПУЛЬСНАЯ РЛС | 2004 |

|

RU2267137C1 |

| Способ формирования периодических двуполярных колебаний с заданным фазовым сдвигом и устройство для его реализации | 2016 |

|

RU2625047C1 |

Изобретение относится к технике связи и может использоваться в различных устройствах, реализованных на основе систем фазовой автоподстройки частоты, в частности в приемниках фазоманипулированных сигналов для создания опорного напряжения при синхронном детектировании. Достигаемый технический результат - возможность устанавливать любой порог обнаружения. Устройство содержит систему фазовой автоподстройки частоты, которая включает в себя два квадратурных канала, каждый из которых содержит квадратурный смеситель и накопитель сигнала, на выходе которых формируются текущие соответствующие значения сигналов Аi и Вi, дискриминатор, формирователь закона управления, блок запрета ввода целеуказаний, синтезатор частоты, устройство вторичного накопления сигнала в течение интервала обнаружения Тобн, компаратор, элемент памяти, при этом устройство вторичного накопления сигнала в течение интервала обнаружения выполнено таким образом, что накопление осуществляют путем суммирования разности текущих значений модулей Аi и Вi с выходов накопителей сигнала соответственно. 3 ил.

Устройство определения захвата цифровой системы фазовой автоподстройки частоты (ФАПЧ) для приема фазоманипулированных сигналов с подавленной несущей, содержащее систему фазовой автоподстройки частоты, которая включает в себя два квадратурных канала, каждый из которых содержит последовательно соединенные квадратурный смеситель и накопитель сигнала, на выходе которых формируются текущие соответствующие значения сигналов Ai и Bi, дискриминатор, входы которого соединены с выходами соответствующих накопителей сигнала, выход дискриминатора соединен с входом формирователя закона управления, другой вход формирователя закона управления соединен с блоком запрета ввода целеуказаний, выход формирователя закона управления соединен с входом синтезатора частоты, квадратурные выходы которого соединены со вторыми входами первого и второго квадратурных смесителей соответственно, а также устройство вторичного накопления сигнала в течение интервала обнаружения Тобн, выход которого подключен к входу компаратора, последовательно соединенного с элементом памяти, при этом при превышении значением Вобн порога обнаружения сигнала компаратор производит выдачу сигнала на запрет ввода целеуказаний, отличающееся тем, что устройство вторичного накопления сигнала в течение интервала обнаружения Тобн выполнено таким образом, что накопление осуществляют путем суммирования разности текущих значений модулей сигналов Ai и Bi с выходов накопителей сигнала соответственно.

| БАНКЕТ В.Л., МЕЛЬНИК A.M | |||

| Системы восстановления несущей при когерентном приеме дискретных сигналов | |||

| - Зарубежная радиоэлектроника, №12, 1983 | |||

| - М.: Радио и Связь, с.31-41 | |||

| Устройство контроля исправности кольца фазовой автоподстройки частоты | 1975 |

|

SU663067A1 |

| Устройство для контроля исправностиСиСТЕМ фАзОВОй АВТОпОдСТРОйКи чАСТОТы | 1976 |

|

SU797055A1 |

| US 5939949 A, 17.08.1999 | |||

| WO 00/27033 A1, 11.05.2000. | |||

Авторы

Даты

2010-03-20—Публикация

2008-03-31—Подача