Предлагаемое изобретение относится к области радиотехники и связи и может быть использовано в устройствах автоматической регулировки усиления, фазовых детекторах и модуляторах, а также в системах фазовой автоподстройки и умножения частоты или в качестве усилителя, коэффициент передачи по напряжению которого зависит от уровня сигнала управления. Аналоговый перемножитель является базовым узлом современных систем приема и обработки сигналов аналоговой вычислительной и измерительной техники.

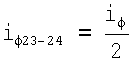

В настоящее время в аналоговой микросхемотехнике в составе перемножителей двух напряжений, систем электронной регулировки усиления широкое применение находит так называемая перемножающаяся ячейка Джильберта (фиг.1). Такая структура стала основой построения практически всех известных в настоящее время прецизионных аналоговых перемножителей сигналов на основе дифференциальных каскадов [1-36]. В этой связи задача улучшения параметров этого функционального узла относится к числу достаточно актуальных задач современной микроэлектроники.

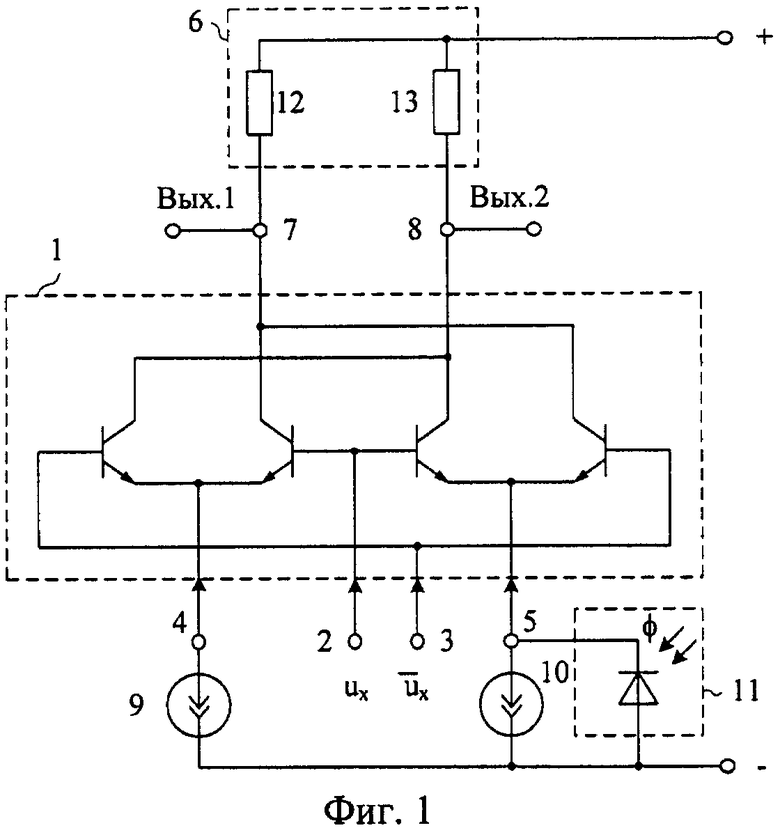

Ближайшим прототипом заявляемого устройства является аналоговый перемножитель двух сигналов (АПС, фиг.1), рассмотренный в патентной заявке США №20070194846 фиг.1, содержащий множительную ячейку 1 на основе двух дифференциальных каскадов, имеющую первый 2 и второй 3 потенциальные входы канала «X», первый 4 и второй 5 токовые входы канала «Y», цепь нагрузки 6, связанную с первым 7 и вторым 8 токовыми выходами множительной ячейки 1, первый 9 и второй 10 токостабилизирующие двухполюсники, соединенные с соответствующими первым 4 и вторым 5 токовыми входами канала «Y», двухполюсный преобразователь 11 сигнал канала «Y» - ток, связанный со вторым 5 токовым входом канала «Y».

В качестве двухполюсника преобразователя сигнал канала «Y» - ток в известной схеме используется фотодиод. В частных случаях это может быть также магниторезистор, тензодиод, датчик давления и т.п.

Существенный недостаток известного перемножителя состоит в том, что он не обеспечивает прямого четырехквадрантного перемножения первичной переменной канала «Y» (например, светового потока Ф, магнитного поля В, силы F, давления Р и т.п.) на входное напряжение канала «X» (ux). Это не позволяет создавать на его основе специальные системы обработки информации, содержащейся в электрических (ux) и неэлектрических (Ф, В, F, Р) сигналах и использующих недифференциальные двухполюсные преобразователи измеряемых параметров 11.

Основная цель предполагаемого изобретения состоит в создании условий для прямого четырехквадрантного перемножения измеряемой координаты канала «Y» (Ф, В, F, Р) на координату канала «X» (ux), которая также может быть функционально связана с неэлектрическим сигналом «X». Таким образом, основная цель изобретения состоит в решении задачи прямого перемножения двух, в общем случае неэлектрических сигналов «X» и «Y».

Поставленная цель достигается тем, что в АПС, содержащем множительную ячейку 1 на основе двух дифференциальных каскадов, имеющую первый 2 и второй 3 потенциальные входы канала «X», первый 4 и второй 5 токовые входы канала «Y», цепь нагрузки 6, связанную с первым 7 и вторым 8 токовыми выходами множительной ячейки 1, первый 9 и второй 10 токостабилизирующие двухполюсники, соединенные с соответствующими первым 4 и вторым 5 токовыми входами канала «Y», двухполюсный преобразователь 11 сигнал канала «Y» - ток, связанный со вторым 5 токовым входом канала «Y», предусмотрены новые элементы и связи - множительная ячейка 1 содержит первый 14 и второй 15 вспомогательные токовые выходы, выходные токи которых пропорциональны соответствующим входным токам первого 4 и второго 5 токовых входов канала «Y», причем первый 14 вспомогательный токовый выход соединен с источником питания, а второй 15 вспомогательный токовый выход связан со входом дополнительного усилителя тока 16, выход которого подключен к первому 4 токовому входу канала «Y».

На фиг.1 показана схема АПС-прототипа, а на фиг.2 - его функциональная схема.

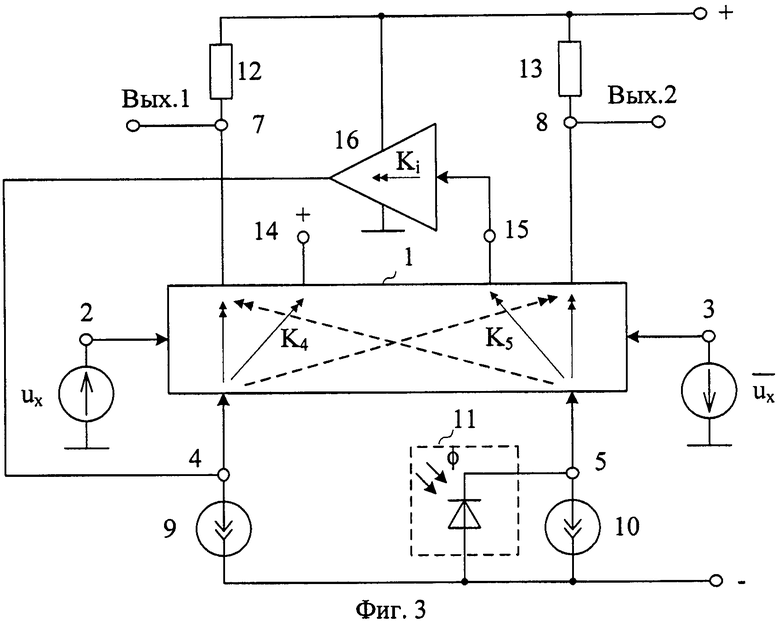

На фиг.3 приведена схема заявляемого АПС в соответствии с п.1 формулы изобретения.

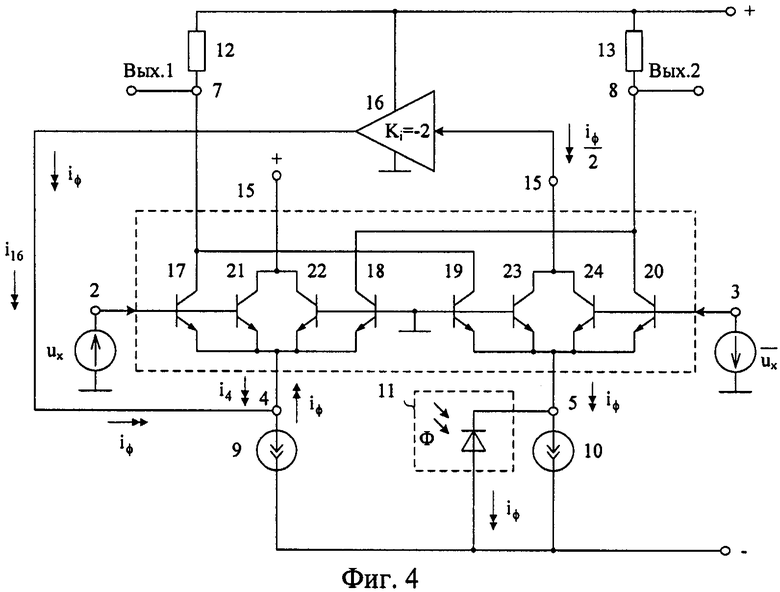

Схема фиг.4 соответствует п.2 формулы изобретения.

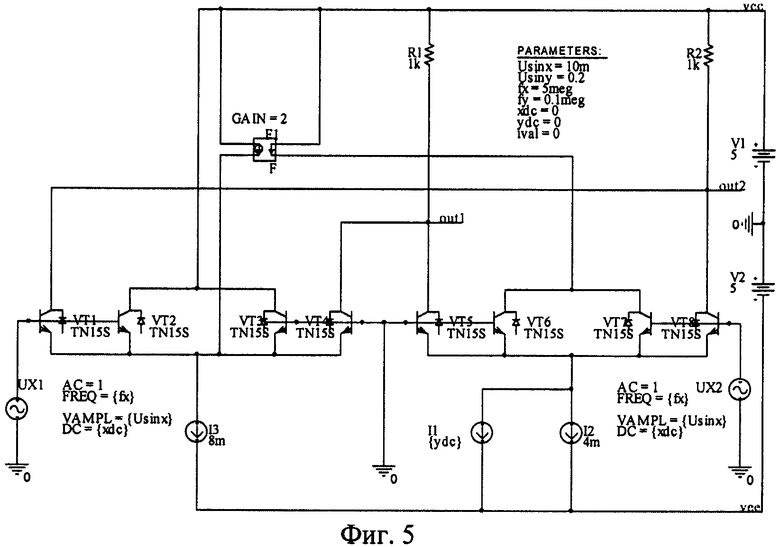

На фиг.5 приведена схема АПС фиг.4 в среде компьютерного моделирования PSpice на моделях интегральных транзисторов ФГУП НПП "Пульсар».

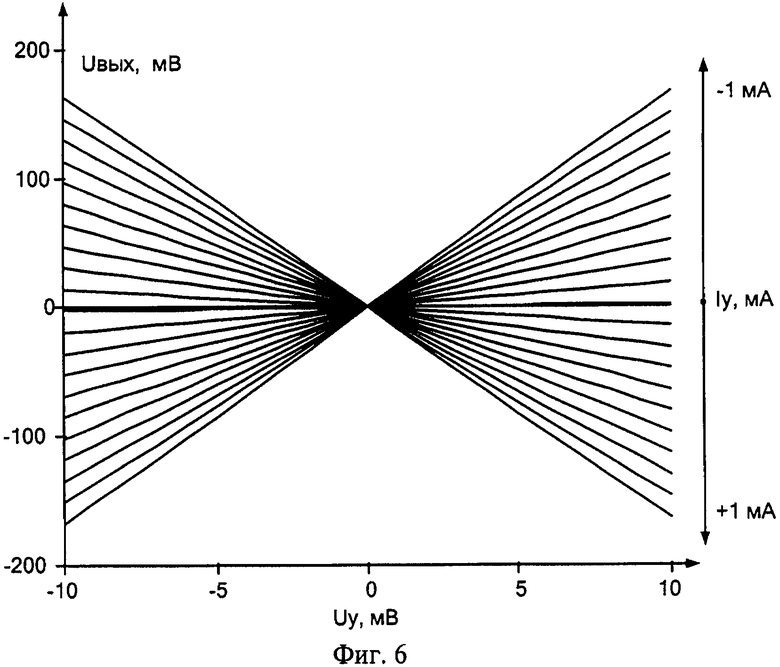

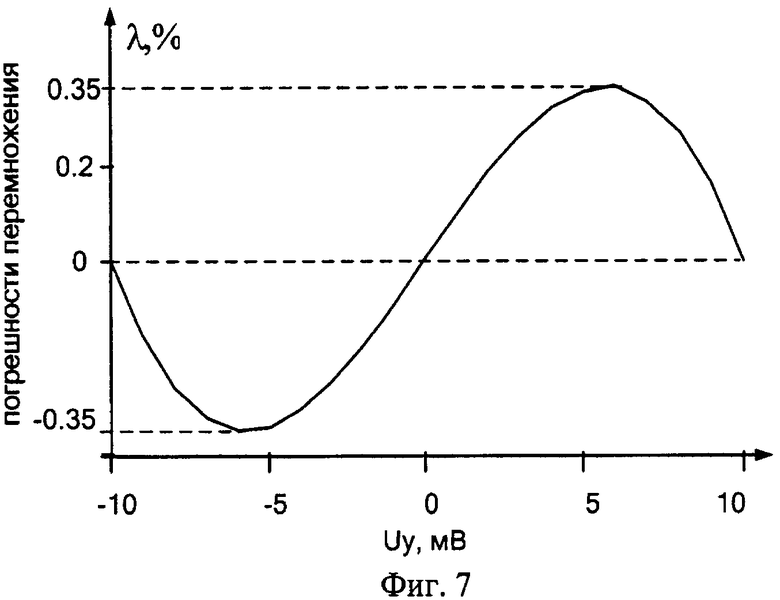

На фиг.6 приведены результаты компьютерного моделирования схемы фиг.5 для случая перемножения напряжения Ux и тока Iy, пропорционального неэлектрической величине (Ф, В, F, Р и т.п.). Эти графики показывают, что заявляемый АПС является четырехквадрантным перемножителем двух сигналов ux и Фу. При этом погрешности перемножения, характеризующиеся графиками фиг.7, могут быть достаточно малыми (<0,35%).

Заявляемый АПС фиг.3 содержит множительную ячейку 1 на основе двух дифференциальных каскадов, имеющую первый 2 и второй 3 потенциальные входы канала «X», первый 4 и второй 5 токовые входы канала «Y», цепь нагрузки 6, связанную с первым 7 и вторым 8 токовыми выходами множительной ячейки 1, первый 9 и второй 10 токостабилизирующие двухполюсники, соединенные с соответствующими первым 4 и вторым 5 токовыми входами канала «Y», двухполюсный преобразователь 11 сигнал канала «Y» - ток, связанный со вторым 5 токовым входом канала «Y». Множительная ячейка 1 содержит первый 14 и второй 15 вспомогательные токовые выходы, выходные токи которых пропорциональны соответствующим входным токам первого 4 и второго 5 токовых входов канала «Y», причем первый 14 вспомогательный токовый выход соединен с источником питания, а второй 15 вспомогательный токовый выход связан со входом дополнительного усилителя тока 16, выход которого подключен к первому 4 токовому входу канала «Y».

В схеме фиг.4, в соответствии с п.2 формулы изобретения, множительная ячейка 1 содержит в частном случае первый 17 и второй 18 входные транзисторы, эмиттеры которых соединены с первым 4 токовым входом канала «Y», третий 19 и четвертый 20 входные транзисторы, эмиттеры которых соединены со вторым 5 токовым входом канала «Y», пятый 21 и шестой 22 входные транзисторы, эмиттеры которых соединены с первым 4 входом канала «Y», седьмой 23 и восьмой 24 входные транзисторы, эмиттеры которые соединены со вторым 5 токовым входом канала «Y», причем базы первого 17 и пятого 21, второго 18 и шестого 22, третьего 19 и седьмого 23, восьмого 24 и четвертого 20 входных транзисторов попарно объединены, коллекторы пятого 21 и шестого 22 входных транзисторов подключены к первому 14 вспомогательному токовому выходу, коллекторы седьмого 23 и восьмого 24 входных транзисторов подключены ко второму 15 вспомогательному токовому выходу, коллекторы первого 17 и третьего 19 входных транзисторов соединены с первым 7 токовым выходом множительной ячейки 1, коллекторы второго 18 и четвертого 20 входных транзисторов соединены со вторым 8 токовым выходом множительной ячейки 1, базы первого 17 и второго 21 входных транзисторов соединены с первым 2 потенциальным входом канала «X», базы четвертого 20 и восьмого 24 входных транзисторов подключены ко второму 3 потенциальному входу канала «X», а базы второго 18, третьего 19, шестого 22 и седьмого 23 входных транзисторов связаны с общей шиной источников питания.

Рассмотрим работу АПС на примере анализа схемы фиг.4.

При отсутствии светового потока (Ф=0) суммарный ток общей эмиттерной цепи 5 транзисторов 19 и 20 равен току двухполюсника 10 (I10=I0). Этот ток I0 перераспределяется между транзисторами 19, 20, 23, 24. Поэтому ток в цепи второго 15 вспомогательного выхода равен

.

.

Это значение тока передается на вход дополнительного усилителя 16 и далее поступает в виде тока I16 в узел 4

I16=2I15=I0.

Для того чтобы выполнялось равенство I4=I0, необходимо обеспечить

I9=I4+I16=2I0.

Если под действием светового потока Ф двухполюсный преобразователь 11 сформирует выходной ток iф, то это создаст ток в цепи входа 5

iф=ФSф=i5,

где Sф - крутизна преобразования светового потока Ф в ток iф.

Данное приращение iф делится на четыре части между эмиттерами транзисторов 19 и 20, 23 и 24:

,

,  .

.

Как следствие, ток входа 15

iф15=0,5iф.

Поэтому составляющая тока iф19-20 уменьшает коэффициент усиления по напряжению каскада на транзисторах 19 и 20. Однако приращение iф передается через усилитель тока 16 в эмиттерную цепь 4 транзисторов 17-18 и 21-22 и вызывает увеличение суммарного тока эмиттерной цепи транзисторов 17-18 и 21-22, что является вторым дополнительным условием четырехквадрантного перемножения сигналов по каналам «X» и «Y»:

uвых=KxuxФY,

где Кх - коэффициент пропорциональности.

Предлагаемый АПС может эффективно использоваться в качестве «миксера» двух неэлектрических сигналов.

В качестве перемножающей ячейки 1 могут применяться и другие (по сравнению с фиг.1) модификации схемы Джильберта (например, фиг.4).

Замечательная особенность заявляемого АПС, в отличие от других вариантов его построения, состоит в том, что он может работать при экстремально низких напряжениях питания [Еп=±(1÷1,5 В)]. Это позволяет использовать в схеме АПС сверхбыстродействующие SiGe транзисторы с технологическими нормами 130 нм, для которых необходимо иметь Еп<±1,5 В.

Анализ свойств заявляемого АПС в режиме перемножения двух сигналов (фиг.6, фиг.7) показывает, что заявляемое техническое решение обеспечивает удовлетворительную для многих применений погрешность выполнения данной математической операции.

Таким образом, предлагаемая схема АПС обеспечивает четырехквадрантное перемножение, что позволяет использовать ее для построения различных измерительных систем, например в сфере оптической связи или обработки оптической информации и т.п.

Источники информации

1. Патент GB 2.318.470, H03f 3/45.

2. Патент ЕР 1.369.992.

3. Патент США №5.874.857.

4. Патент США №6.456.142, фиг.8.

5. Патент США №3.931.583, фиг.9.

6. Патентная заявка США №2007/0139114, фиг.1.

7. Патентная заявка США №2005/0073362, фиг.1.

8. Патент США №5.057.787.

9. Патентная заявка WO 2004/041298.

10. Патент США №5.389.840, фиг.1А.

11. Патент США №5.883.539, фиг.1.

12. Патентная заявка США №2005/0052239.

13. Патент США №5.151.625, фиг.1.

14. Патент США №4.458.211, фиг.5.

15. Патентная заявка США №2005/0030096, фиг.6.

16. Патентная заявка США №2007/0090876.

17. Патент США №6.727.755.

18. Патент США №5.552.734, фиг.13, фиг.16.

19. Патентная заявка США №2006/0232334.

20. Патент США №5.767.727.

21. Патент США №6.229.395, фиг.2.

22. Патент США №5.115.409.

23. Патентная заявка США №2005/0231283, фиг.1.

24. Патентная заявка США №2006/0066362, фиг.15.

25. Патент США №5.151.624, фиг.1, фиг.2.

26. Патент США №5.329.189, фиг.2.

27. Патент США №4.704.738.

28. Патент США №4.480.337.

29. Патент США №5.825.231.

30. Патент США №6.211.718, фиг.1, фиг.2.

31. Патент США №5.151.624.

32. Патент США №5.329.189.

33. Патент США №5.331.289.

34. Патент GB №2.323.728.

35. Патентная заявка США №2008/0122540, фиг.1.

36. Патент США №4.965.528.

| название | год | авторы | номер документа |

|---|---|---|---|

| АНАЛОГОВЫЙ ПЕРЕМНОЖИТЕЛЬ ДВУХ СИГНАЛОВ | 2008 |

|

RU2389072C1 |

| АНАЛОГОВЫЙ ПЕРЕМНОЖИТЕЛЬ НАПРЯЖЕНИЙ | 2008 |

|

RU2382484C1 |

| НИЗКОВОЛЬТНЫЙ АНАЛОГОВЫЙ ПЕРЕМНОЖИТЕЛЬ НАПРЯЖЕНИЙ | 2009 |

|

RU2394358C1 |

| АНАЛОГОВЫЙ ПЕРЕМНОЖИТЕЛЬ НАПРЯЖЕНИЙ | 2008 |

|

RU2382405C1 |

| АНАЛОГОВЫЙ ПЕРЕМНОЖИТЕЛЬ НАПРЯЖЕНИЙ | 2008 |

|

RU2382483C1 |

| АНАЛОГОВЫЙ ПЕРЕМНОЖИТЕЛЬ НАПРЯЖЕНИЙ | 2010 |

|

RU2439694C1 |

| АНАЛОГОВЫЙ ПЕРЕМНОЖИТЕЛЬ НАПРЯЖЕНИЙ | 2011 |

|

RU2439785C1 |

| АНАЛОГОВЫЙ ПЕРЕМНОЖИТЕЛЬ НАПРЯЖЕНИЙ | 2008 |

|

RU2389071C1 |

| АНАЛОГОВЫЙ ПЕРЕМНОЖИТЕЛЬ НАПРЯЖЕНИЙ С НИЗКОВОЛЬТНЫМ ПИТАНИЕМ | 2010 |

|

RU2419188C1 |

| АНАЛОГОВЫЙ ПЕРЕМНОЖИТЕЛЬ НАПРЯЖЕНИЙ | 2008 |

|

RU2396595C2 |

Изобретение относится к области радиотехники и связи и может быть использовано в устройствах автоматической регулировки усиления, фазовых детекторах и модуляторах, а также в системах фазовой автоподстройки и умножения частоты или в качестве усилителя, коэффициент передачи по напряжению которого зависит от уровня сигнала управления. Аналоговый перемножитель сигналов (АПС) является базовым узлом современных систем приема и обработки сигналов ВЧ и СВЧ-диапазонов, аналоговой вычислительной и измерительной техники. Технический результат: создание условий для прямого четырехквадрантного перемножения измеряемой координаты канала «Y» (Ф, В, F, Р) на координату канала «X» (ux), которая также может быть функционально связана с неэлектрическим сигналом «X», а также снижение напряжения питания и погрешности перемножения. АПС содержит множительную ячейку (1) на основе двух дифференциальных каскадов, имеющую первый (2) и второй (3) потенциальные входы канала «X», первый (4) и второй (5) токовые входы канала «Y», цепь нагрузки (6), связанную с первым (7) и вторым (8) токовыми выходами множительной ячейки (1), первый (9) и второй (10) токостабилизирующие двухполюсники, соединенные с соответствующими первым (4) и вторым (5) токовыми входами канала «Y», двухполюсный преобразователь (11) «сигнал канала «Y» - ток», связанный со вторым (5) токовым входом канала «Y». Множительная ячейка (1) содержит первый (14) и второй (15) вспомогательные токовые выходы, выходные токи которых пропорциональны соответствующим входным токам первого (4) и второго (5) токовых входов канала «Y», причем первый (14) вспомогательный токовый выход соединен с источником питания, а второй (15) вспомогательный токовый выход связан со входом дополнительного усилителя тока (16), выход которого подключен к первому (4) токовому входу канала «Y». 1 з.п. ф-лы. 7 ил.

1. Аналоговый перемножитель двух сигналов, содержащий множительную ячейку (1) на основе двух дифференциальных каскадов, имеющую первый (2) и второй (3) потенциальные входы канала «X», первый (4) и второй (5) токовые входы канала «Y», цепь нагрузки (6), связанную с первым (7) и вторым (8) токовыми выходами множительной ячейки (1), первый (9) и второй (10) токостабилизирующие двухполюсники, соединенные с соответствующими первым (4) и вторым (5) токовыми входами канала «Y», двухполюсный преобразователь (11) «сигнал канала «Y» - ток», связанный со вторым (5) токовым входом канала «Y», отличающийся тем, что множительная ячейка (1) содержит первый (14) и второй (15) вспомогательные токовые выходы, выходные токи которых пропорциональны соответствующим входным токам первого (4) и второго (5) токовых входов канала «Y», причем первый (14) вспомогательный токовый выход соединен с источником питания, а второй (15) вспомогательный токовый выход связан со входом дополнительного усилителя тока (16), выход которого подключен к первому (4) токовому входу канала «Y».

2. Устройство по п.1, отличающееся тем, что множительная ячейка (1) содержит первый (17) и второй (18) входные транзисторы, эмиттеры которых соединены с первым (4) токовым входом канала «Y», третий (19) и четвертый (20) входные транзисторы, эмиттеры которых соединены со вторым (5) токовым входом канала «Y», пятый (21) и шестой (22) входные транзисторы, эмиттеры которых соединены с первым (4) входом канала «Y», седьмой (23) и восьмой (24) входные транзисторы, эмиттеры которые соединены со вторым (5) токовым входом канала «Y», причем базы первого (17) и пятого (21), второго (18) и шестого (22), третьего (19) и седьмого (23), восьмого (24) и четвертого (20) входных транзисторов попарно объединены, коллекторы пятого (21) и шестого (22) входных транзисторов подключены к первому (14) вспомогательному токовому выходу, коллекторы седьмого (23) и восьмого (24) входных транзисторов подключены ко второму (15) вспомогательному токовому выходу, коллекторы первого (17) и третьего (19) входных транзисторов соединены с первым (7) токовым выходом множительной ячейки (1), коллекторы второго (18) и четвертого (20) входных транзисторов соединены со вторым (8) токовым выходом множительной ячейки (1), базы первого (17) и второго (21) входных транзисторов соединены с первым (2) потенциальным входом канала «X», базы четвертого (20) и восьмого (24) входных транзисторов подключены ко второму (3) потенциальному входу канала «X», а базы второго (18), третьего (19), шестого (22) и седьмого (23) входных транзисторов связаны с общей шиной источников питания.

| Пресс для выдавливания из деревянных дисков заготовок для ниточных катушек | 1923 |

|

SU2007A1 |

| Аналоговый умножитель | 1978 |

|

SU767780A1 |

| Аналоговый умножитель | 1978 |

|

SU742965A1 |

| US 6313458 B1, 06.11.2001. | |||

Авторы

Даты

2010-05-10—Публикация

2008-09-26—Подача