Предлагаемое изобретение относится к области радиотехники и связи и может быть использовано в устройствах автоматической регулировки усиления, фазовых детекторах и модуляторах, а также в системах фазовой автоподстройки и умножения частоты или в качестве усилителя, коэффициент передачи по напряжению которого зависит от уровня сигнала управления. Аналоговый перемножитель является базовым узлом современных систем приема и обработки сигналов ВЧ и СВЧ-диапазонов, аналоговой вычислительной и измерительной техники.

В настоящее время в аналоговой микросхемотехнике в составе перемножителей двух напряжений, систем электронной регулировки усиления широкое применение находит так называемая перемножающаяся ячейка Джильберта. Такая структура стала основой построения практически всех известных в настоящее время прецизионных аналоговых перемножителей сигналов на основе дифференциальных каскадов [1-36]. В этой связи задача улучшения параметров этого функционального узла относится к числу достаточно актуальных задач современной микроэлектроники.

В цифровых интегральных микросхемах результатом увеличения скорости обработки информации стали тенденции постоянного уменьшения напряжения питания, что не приемлемо в аналоговом проектировании с высокими характеристиками. При технологических нормах 350 нм (напряжение питания 3.3 В) по-прежнему достаточно схемотехнических возможностей для аналоговых проектирований с высокими характеристиками, хотя наличие 5 В питания было бы предпочтительнее. При нормах 180 нм (1.8 В) процесс усложняется и статические характеристики аналоговых устройств страдают. При 90-130 нм технологии необходимо развитие новых подходов к проектированию микросхем, ориентированных на обеспечение работоспособности при низковольтном питании.

Таким образом, последние несколько лет источники питания с напряжением 5В вытесняются более низковольтными. Требования к уменьшению рассеиваемой мощности и уменьшению числа батарей в таких приложениях, как беспроводные устройства связи и персональные компьютеры, привели к снижению напряжения питания до уровня 1,5 В. Эта тенденция реализована в современных SiGe транзисторах, которые сконструированы так, чтобы обеспечить максимальную частоту среза (f1) в компромиссе с напряжением пробоя (Uпр). Для кремниевых транзисторов существует следующее фундаментальное ограничение: f1×Uпр≈const, т.е. малые размеры транзисторов, обеспечивающие высокие значения f1 (до 200 ГГц), привели к снижению напряжения питания микросхем до 1,2-1,5 В.

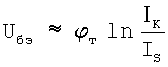

Уменьшение напряжения питания (Eп) в биполярных схемах приводит к появлению новых проблем, и некоторые из них становятся трудноразрешимыми при напряжении питания менее 2 В. Принципиальная сложность уменьшения напряжения Eп состоит в том, что биполярный транзистор имеет фиксированное напряжение база-эмиттер Uбэ, которое не уменьшается линейно с уменьшением технологических норм, так как

,

,

где φт=kT/q, Iк - ток коллектора и Is - обратный ток эмиттерного p-n перехода. При этом параметры транзистора и уровни тока оказывают слабое влияние на напряжение Uбэ. На практике плотность тока в биполярном транзисторе (Iк/Is), изменяя свое значение, также слабо влияет на напряжение Uбэ. Если в используемой технологии Uбэ=0,7÷0,8 В, то использование 1,5 В источника питания приводит к тому, что между «землей» и шиной Eп не может быть включено больше чем один p-n переход.

Учитывая вышесказанное, а также численные значения напряжения Uбэ≈700÷800 мВ, можно сделать вывод о том, что при напряжении питания 1,5 В запрещается использовать многоярусные дифференциальные пары или каскодные конфигурации (архитектуры).

Таким образом, отсутствие возможности масштабирования напряжения на переходе база-эмиттер обостряет проблему дальнейшего масштабирования напряжения питания интегральных схем на биполярных транзисторах.

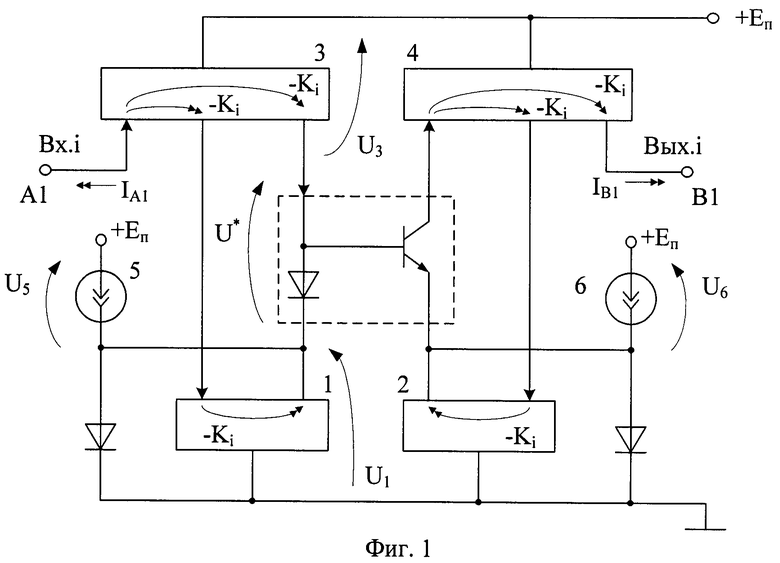

Ближайшим прототипом заявляемого устройства является аналоговый перемножитель АП (фиг.1), рассмотренный в патенте США №5.329.189, содержащий первое 1 токовое зеркало, общий вход которого соединен с общим входом второго 2 токового зеркала, третье токовое зеркало 3, общий вход которого связан с общим входом четвертого 4 токового зеркала, первый 5 и второй 6 противофазно управляемые входным сигналом по каналу «Y» источники тока. Его основное достоинство, как это отмечается в патенте №5.329.189, - возможность работы при напряжениях питания 3Uэб=2,1-2,3В.

Существенный недостаток известного перемножителя состоит в том, что он не может работать при более низких напряжениях питания, например Еп=1,5В, которые необходимо использовать для микросистем на базе перспективных SiGe технологий. Кроме этого, особенности архитектуры АП-прототипа создают проблемы с перемножением потенциальных сигналов - здесь обеспечивается перемножение токовых координат, а для перемножения двух напряжений необходимо обеспечить их предварительное преобразование в ток, что отрицательно сказывается на минимально возможных величинах Еп.

Основная цель предлагаемого изобретения состоит в уменьшении допустимого напряжения питания АП до уровня меньше чем 1,5 В.

Дополнительная цель - перемножение потенциальных входных сигналов как наиболее часто формируемых в различных устройствах связи.

Предлагаемое техническое решение является альтернативой широко распространенной перемножающей ячейки Джильберта [1-36] и характеризуется более высокими качественными параметрами по диапазону рабочих частот при низковольтном питании.

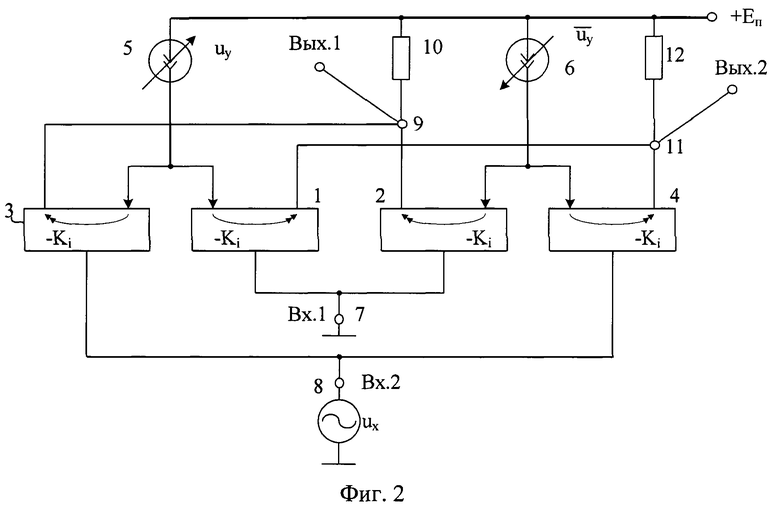

Поставленная цель достигается тем, что в АП фиг.1, содержащем первое 1 токовое зеркало, общий вход которого соединен с общим входом второго 2 токового зеркала, третье токовое зеркало 3, общий вход которого связан с общим входом четвертого 4 токового зеркала, первый 5 и второй 6 противофазно управляемые входным сигналом по каналу «Y» источники тока, предусмотрены новые элементы и связи - объединенные общие входы первого 1 и второго 2 токовых зеркал соединены с первым 7 потенциальным входом канала «X», объединенные общие входы третьего 3 и четвертого 4 токовых зеркал соединены со вторым потенциальным 8 входом канала «X», входы первого 1 и третьего токовых зеркал связаны с первым 5 управляемым входным сигналом по каналу «Y» источником тока, входы второго 2 и четвертого 4 токовых зеркал связаны со вторым 6 противофазно управляемым входным сигналом по каналу «Y» источником тока, выходы третьего 3 и второго 2 токовых зеркал соединены с первым 9 токовым выходом аналогового перемножителя напряжений и первой 10 цепью нагрузки, а выходы первого 1 и четвертого 4 токовых зеркал соединены со вторым 11 токовым выходом аналогового перемножителя напряжений и второй 12 цепью нагрузки.

На фиг.1 показана схема АП-прототипа, а на фиг.2 - схема заявляемого АП в соответствии с п.1 формулы изобретения.

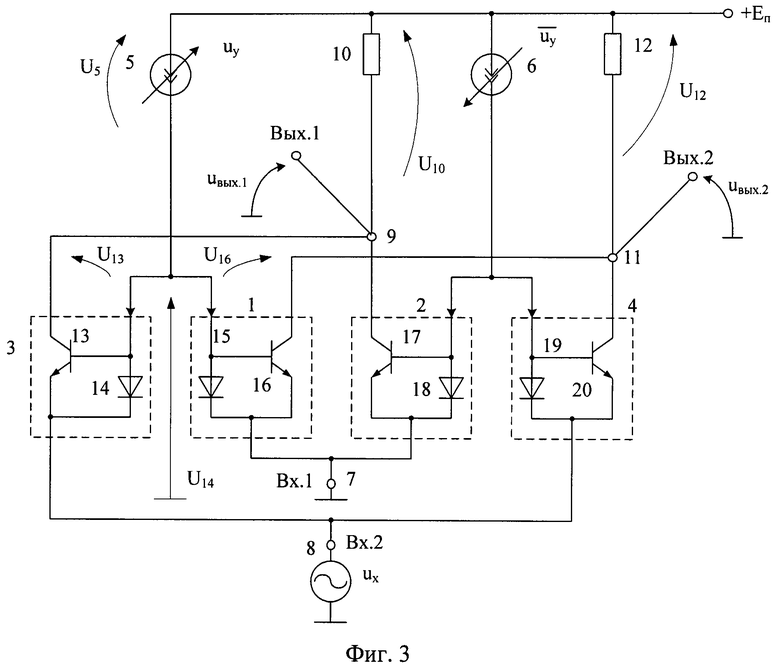

На фиг.3 приведена схема АП фиг.2 с конкретным выполнением токовых зеркал 1-4.

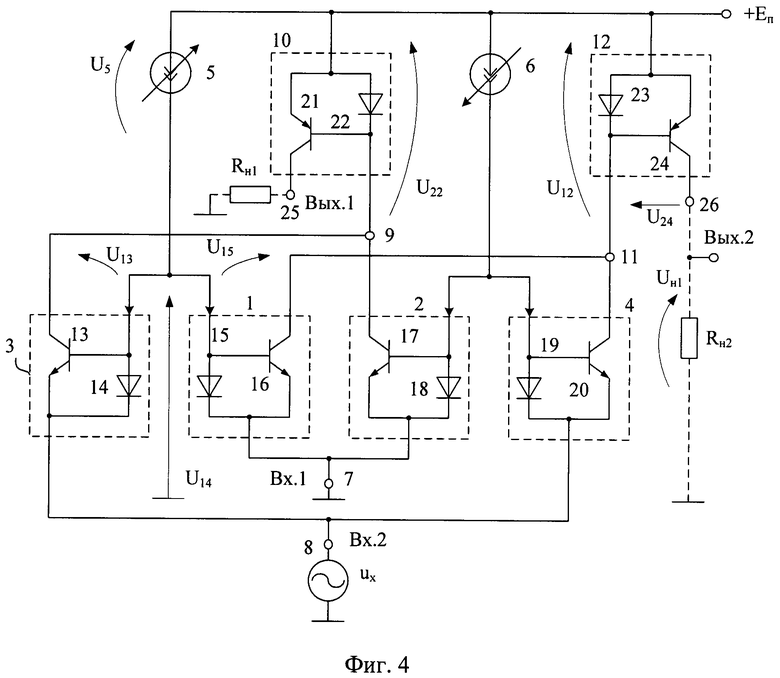

На фиг.4 показан другой частный пример реализации АП фиг.2 для случая, когда первая 10 и вторая 11 цепи нагрузки реализованы в виде токовых зеркал на p-n-p транзисторах.

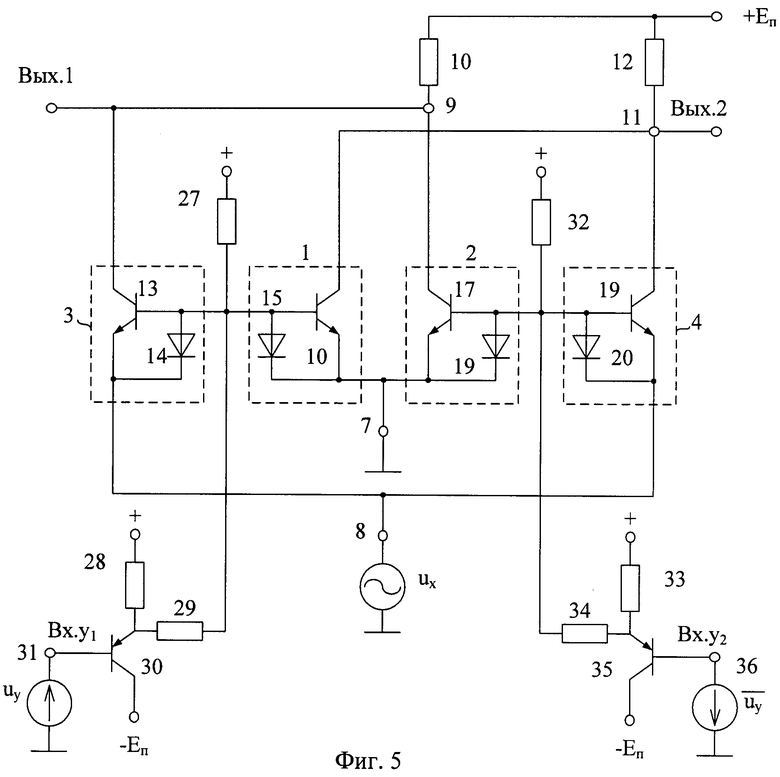

На фиг.5 изображен АП по п.2 формулы изобретения.

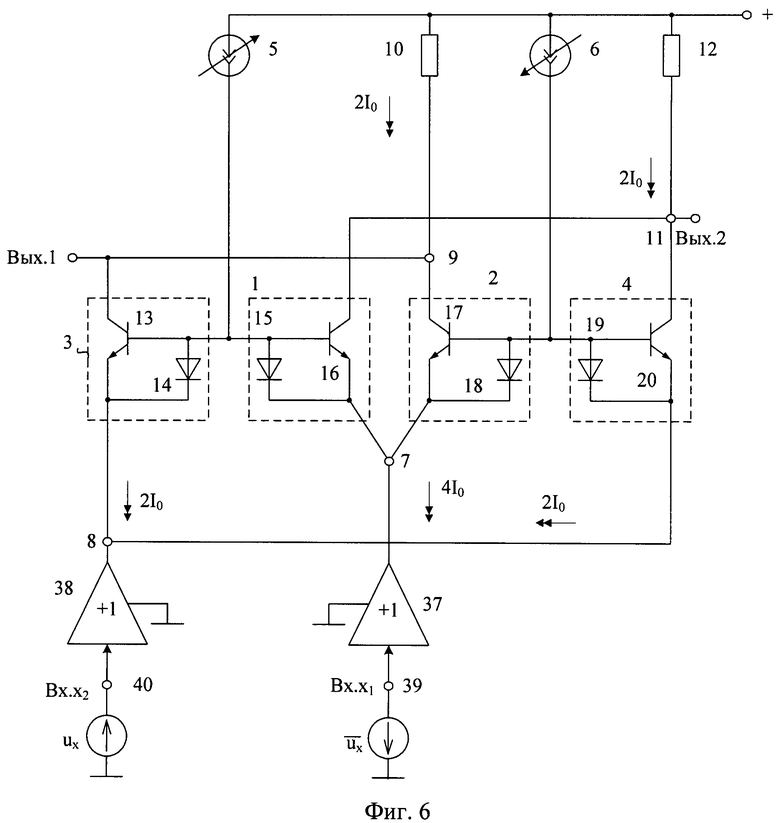

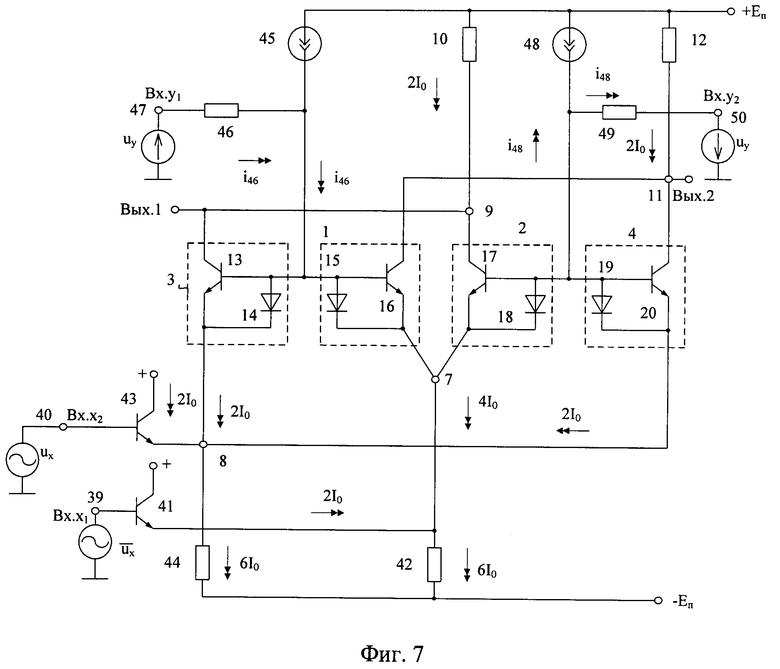

На фиг.6 показана схема АП фиг.2, соответствующая п.3 формулы изобретения, а на чертеже фиг.7 - п.4 формулы изобретения.

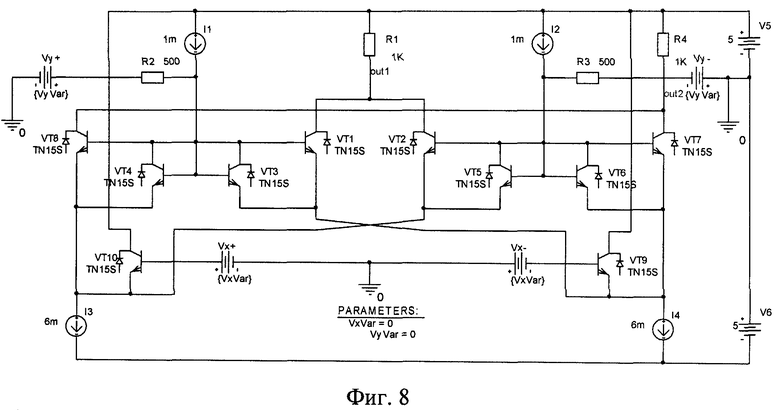

На фиг.8 приведена схема АП фиг.7 в среде компьютерного моделирования PSpice на моделях интегральных транзисторов ФГУП НПП "Пульсар».

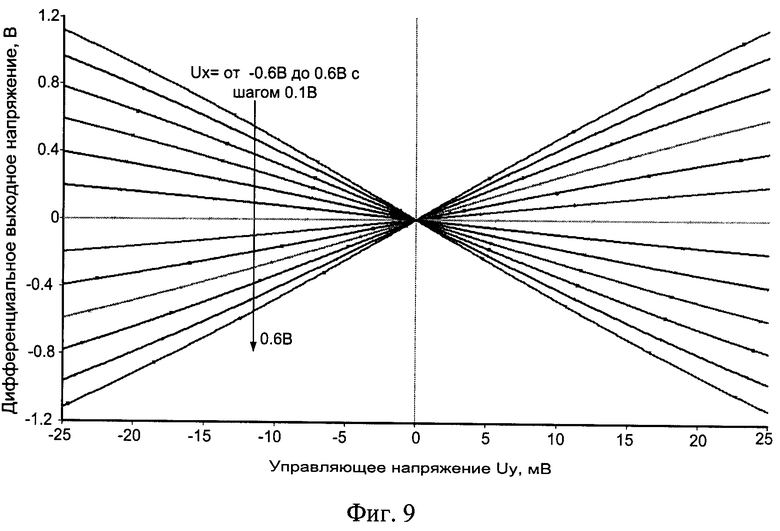

На фиг.9 приведены результаты компьютерного моделирования схемы фиг.8 для случая перемножения двух напряжений Ux и Uy. Эти графики показывают, что заявляемый АП является четырехквадрантным перемножителем. При этом погрешности перемножения могут быть достаточно малыми.

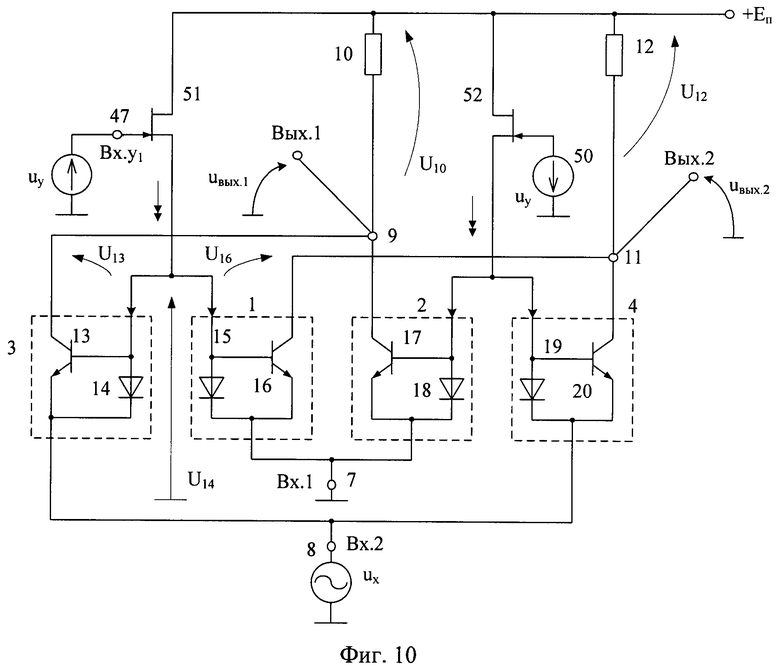

Схема фиг.10 показывает возможные варианты построения управляемых источников тока 5 и 6 в базисе BiFET-транзисторов.

Заявляемый по п.1 АП фиг.2 содержит первое 1 токовое зеркало, общий вход которого соединен с общим входом второго 2 токового зеркала, третье токовое зеркало 3, общий вход которого связан с общим входом четвертого 4 токового зеркала, первый 5 и второй 6 противофазно управляемые входным сигналом по каналу «Y» источники тока. Объединенные общие входы первого 1 и второго 2 токовых зеркал соединены с первым 7 потенциальным входом канала «X», объединенные общие входы третьего 3 и четвертого 4 токовых зеркал соединены со вторым потенциальным 8 входом канала «X», входы первого 1 и третьего токовых зеркал связаны с первым 5 управляемым входным сигналом по каналу «Y» источником тока, входы второго 2 и четвертого 4 токовых зеркал связаны со вторым 6 противофазно управляемым входным сигналом по каналу «Y» источником тока, выходы третьего 3 и второго 2 токовых зеркал соединены с первым 9 токовым выходом аналогового перемножителя напряжений и первой 10 цепью нагрузки, а выходы первого 1 и четвертого 4 токовых зеркал соединены со вторым 11 токовым выходом аналогового перемножителя напряжений и второй 12 цепью нагрузки.

В частном случае (фиг.3) токовое зеркало 3 содержит транзистор 13 и p-n переход 14, токовое зеркало 1 - p-n переход 15 и транзистор 16, токовое зеркало 2 - транзистор 17 и p-n переход 18, токовое зеркало 4 - p-n переход 19 и транзистор 20.

В качестве цепей нагрузки 10 и 12 могут применяться резисторы (фиг.3) или дополнительные токовые зеркала на p-n-p транзисторах (фиг.4), включающих полупроводниковые элементы 21, 22 и 23, 24. В этом случае выходы 25 и 26 дополнительных токовых зеркал 10 и 12 могут быть связаны с элементами нагрузки

Rн1 и Rн2. При таком построении схемы минимальное напряжение питания Eп.min остается достаточно малым (Еп.min=1,5В).

В схеме фиг.5, соответствующей п.2 формулы изобретения, первый 5 управляемый входным сигналом по каналу «Y» источник тока содержит первый 27 и второй 28 дополнительные токостабилизируюшие двухполюсники, между которыми включен первый 29 дополнительный резистор, первый 30 дополнительный транзистор, эмиттер которого соединен со вторым 28 дополнительным токостабилизируюшим двухполюсником и первым 29 дополнительным резистором, а база соединена с первым 31 входом по каналу «Y», второй 6 управляемый входным сигналом по каналу «Y» источник тока содержит третий 32 и четвертый 33 дополнительные токостабилизируюшие двухполюсники, между которыми включен второй 34 дополнительный резистор, второй 35 дополнительный транзистор, эмиттер которого соединен с четвертым 33 дополнительным токостабилизируюшим двухполюсником и вторым 34 дополнительным резистором, а база соединена со вторым 36 входом по каналу «Y».

Данная схема (фиг.5) иллюстрирует один из возможных вариантов построения управляемых источников тока 5 и 6 (фиг.2).

В схеме фиг.6, соответствующей п.3 формулы изобретения, противофазные источники входных напряжений по каналу «X» ux и  связаны с первым 7 и вторым 8 потенциальными входами канала «X» через первый 37 и второй 38 дополнительные повторители напряжений, на входы которых 39 и 40 подаются противофазные напряжения ux и

связаны с первым 7 и вторым 8 потенциальными входами канала «X» через первый 37 и второй 38 дополнительные повторители напряжений, на входы которых 39 и 40 подаются противофазные напряжения ux и  канала «X». Включение повторителей напряжения 37 и 38 повышает входное сопротивление, на которое «нагружаются» источники напряжения

канала «X». Включение повторителей напряжения 37 и 38 повышает входное сопротивление, на которое «нагружаются» источники напряжения

ux и  канала «X».

канала «X».

В частном случае (фиг.7) первый 37 дополнительный повторитель напряжения содержит первый 41 вспомогательный транзистор и первый 42 вспомогательный двухполюсник, связанный с первым 7 потенциальным входом канала «X» и эмиттером первого 41 вспомогательного транзистора, база которого соединена со входом 39 первого 37 дополнительного повторителя напряжения, а второй 38 дополнительный повторитель напряжения содержит второй 43 вспомогательный транзистор и второй 44 вспомогательный двухполюсник, связанный со вторым 8 потенциальным входом канала «X» и эмиттером второго 43 вспомогательного транзистора, база которого соединена со входом 40 второго дополнительного повторителя напряжения.

В схеме фиг.7, соответствующей также п.5 формулы изобретения, первый 5 управляемый входным сигналом по каналу «Y» источник тока содержит третий 45 вспомогательный двухполюсник и первый 46 вспомогательный резистор, включенный между первым 47 потенциальным входом по каналу «Y» и объединенными входами первого 1 и третьего 3 токовых зеркал, а второй 6 управляемый входным сигналом по каналу «Y» источник тока содержит четвертый 48 вспомогательный двухполюсник и второй 49 вспомогательный резистор, включенный между вторым 50 потенциальным входом по каналу «Y» и объединенными входами второго 2 и четвертого 4 токовых зеркал.

В схеме фиг.10 управляемые источники тока 5 и 6 реализованы на основе полевых транзисторов 51 и 52.

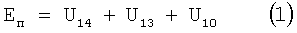

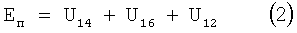

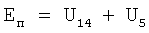

Рассмотрим факторы, ограничивающие уровень напряжения питания в АП фиг.3.

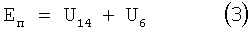

Величина минимального напряжения источника однополярного питания Eп зависит от статического падения напряжения на элементах схемы:

или

или

,

,

где U14≈0,7B - напряжение на входах токовых зеркал 1 и 3;

U13 - статическое напряжение коллектор-база транзистора 13 токового зеркала 3;

U16 - статическое напряжение коллектор-база транзистора 16 токового зеркала 1;

U10, U12 - статическое напряжение на элементах нагрузки 10 и 12;

U5, U6 - статическое напряжение на управляемых источниках тока 5 и 6.

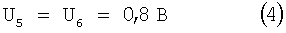

Из уравнений (1)-(3) следует, что схема фиг.3 сможет работать при Еп=1,5 В, если

Уравнение (4) реализуется при типовых вариантах построения управляемых источников тока 5 и 6.

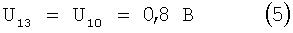

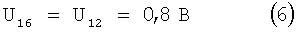

Уравнения (5) и (6) накладывают ограничения на диапазон изменения выходного напряжения перемножителя. Если выбрать U13=U10=U16=U12=0,4 В, то uвых.1 и uвых.2 могут изменяться от статического уровня 1,1 В на ±0,4 В, что вполне удовлетворяет многим применениям АП. Для дифференциального выхода изменения uвых.max= uвых.1- uвых.2 = 0,8 В при Еп=1,5 В.

Таким образом, заявляемый АП может иметь приемлемый для большинства применений диапазон изменения выходного напряжения при Еп=1,5 В.

Если в схеме фиг.3 используется токовый выход, т.е. сопротивление цепей нагрузки 10 и 12 мало, то в этом в этом случае возможно дальнейшее уменьшение напряжения питания (Еп=1,5 В).

Предельные Eп.min будут определяться схемотехникой управляемых источников тока 5 и 6. Возможный вариант построения АП с экстремально низким напряжением питания приведен на фиг.10.

Применение дополнительных токовых зеркал на p-n-p транзисторах (фиг.4) позволит при Еп=1,5 В получить диапазон изменения дифференциального выходного напряжения, близкий к 1,5 В, что характерно для схем с rail-to-rail выходом.

В схеме фиг.5 за счет введения повторителей напряжения на p-n-p транзисторах обеспечивается преобразование «привязанных» к общей шине источников питания сигналов uy и  во входные токи токовых зеркал 1 и 3, 2 и 4. В частном случае в схеме фиг.5 коллекторы транзисторов 30 и 35 могут подключаться к общей шине, что не потребует отрицательных источников питания.

во входные токи токовых зеркал 1 и 3, 2 и 4. В частном случае в схеме фиг.5 коллекторы транзисторов 30 и 35 могут подключаться к общей шине, что не потребует отрицательных источников питания.

Особенность схемы фиг.6 состоит в том, что повторители напряжений 37 и 38 не влияют на статические токи токовых зеркал 1-4, которые устанавливаются управляемыми источниками 5 и 6.

В схеме фиг.7 за счет введения транзисторов 41 и 43 существенно упрощается решение задачи преобразования напряжений uy и  во входные токи токовых зеркал 1 и 3, 2 и 4.

во входные токи токовых зеркал 1 и 3, 2 и 4.

Это объясняется тем, что при uy= =0 токи через резисторы 46 и 49 близки к нулю и данные резисторы непосредственно определяют крутизну преобразования этих напряжений во входные токи токовых зеркал

=0 токи через резисторы 46 и 49 близки к нулю и данные резисторы непосредственно определяют крутизну преобразования этих напряжений во входные токи токовых зеркал

При этом эмиттерные токи транзисторов 41 и 43 практически не зависят от сигнала по каналу «Y».

Применение заявляемого АП в качестве управляемого усилителя показывает, что в таком включении обеспечивается достаточно линейная характеристика управления Ku=f(Uvar), где Uvar=uy - напряжение на входе «Y».

Предлагаемый АПН может также эффективно использоваться в качестве «миксера» двух сигналов.

Анализ свойств заявляемого АП фиг.8 в режиме перемножения двух напряжений (фиг.9) показывает, что предлагаемое техническое решение обеспечивает удовлетворительную для многих применений погрешность выполнения данной математической операции.

Таким образом, предлагаемая схема АП имеет более низкие значения напряжений питания, что позволяет использовать для ее построения более высокочастотные SiGe транзисторы и расширить при этом диапазон рабочих частот.

Источники информации

1. Патент GB 2.318.470, H03f 3/45.

2. Патент ЕР 1.369.992.

3. Патент США №5.874.857.

4. Патент США №6.456.142, фиг.8.

5. Патент США №3.931.583, фиг.9.

6. Патентная заявка США №2007/0139114, фиг.1.

7. Патентная заявка США №2005/0073362, фиг.1.

8. Патент США №5.057.787.

9. Патентная заявка WO 2004/041298.

10. Патент США №5.389.840, фиг.1А.

11. Патент США №5.883.539, фиг.1.

12. Патентная заявка США №2005/0052239.

13. Патент США№5.151.625, фиг.1.

14. Патент США №4.458.211, фиг.5.

15. Патентная заявка США №2005/0030096, фиг.6.

16. Патентная заявка США №2007/0090876.

17. Патент США №6.727.755.

18. Патент США №5.552.734, фиг.13, фиг.16.

19. Патентная заявка США №2006/0232334.

20. Патент США №5.767.727.

21. Патент США №6.229.395, фиг.2.

22. Патент США №5.115.409.

23. Патентная заявка США №2005/0231283, фиг.1.

24. Патентная заявка США №2006/0066362, фиг.15.

25. Патент США №5.151.624, фиг.1, фиг.2.

26. Патент США №5.329.189, фиг.2.

27. Патент США №4.704.738.

28. Патент США №4.480.337.

29. Патент США №5.825.231.

30. Патент США №6.211.718, фиг.1, фиг.2.

31. Патент США №5.151.624.

32. Патент США №5.329.189.

33. Патент США №5.331.289.

34. Патент GB №2.323.728.

35. Патентная заявка США №2008/0122540, фиг.1.

36. Патент США №4.965.528.

| название | год | авторы | номер документа |

|---|---|---|---|

| УПРАВЛЯЕМЫЙ УСИЛИТЕЛЬ И АНАЛОГОВЫЙ ПЕРЕМНОЖИТЕЛЬ СИГНАЛОВ НА ЕГО ОСНОВЕ | 2009 |

|

RU2390922C1 |

| ФАЗОРАСЩЕПИТЕЛЬ ВЫСОКОЧАСТОТНОГО СИГНАЛА | 2011 |

|

RU2439782C1 |

| НИЗКОВОЛЬТНЫЙ АНАЛОГОВЫЙ ПЕРЕМНОЖИТЕЛЬ НАПРЯЖЕНИЙ | 2009 |

|

RU2394358C1 |

| АНАЛОГОВЫЙ ПЕРЕМНОЖИТЕЛЬ НАПРЯЖЕНИЙ | 2008 |

|

RU2396595C2 |

| ДВУХКАНАЛЬНЫЙ ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ | 2011 |

|

RU2452078C1 |

| АНАЛОГОВЫЙ ПЕРЕМНОЖИТЕЛЬ НАПРЯЖЕНИЙ | 2008 |

|

RU2382483C1 |

| УПРАВЛЯЕМЫЙ УСИЛИТЕЛЬ | 2010 |

|

RU2421883C1 |

| АНАЛОГОВЫЙ ПЕРЕМНОЖИТЕЛЬ НАПРЯЖЕНИЙ | 2008 |

|

RU2382405C1 |

| АНАЛОГОВЫЙ ПЕРЕМНОЖИТЕЛЬ НАПРЯЖЕНИЙ | 2010 |

|

RU2439694C1 |

| АНАЛОГОВЫЙ ПЕРЕМНОЖИТЕЛЬ ДВУХ СИГНАЛОВ | 2008 |

|

RU2389073C1 |

Изобретение относится к области радиотехники и связи. Технический результат заключается в уменьшении допустимого напряжения питания аналогового перемножителя до уровня меньше чем 1,5 В, также в перемножении потенциальных входных сигналов как наиболее часто формируемых в различных устройствах связи. Для этого устройство содержит первое токовое зеркало, общий вход которого соединен с общим входом второго токового зеркала, третье токовое зеркало, общий вход которого связан с общим входом четвертого токового зеркала, первый и второй противофазно управляемые входным сигналом по каналу «Y» источники тока. Объединенные общие входы первого и второго токовых зеркал соединены с первым потенциальным входом канала «X», объединенные общие входы третьего и четвертого токовых зеркал соединены со вторым потенциальным входом канала «X», входы первого и третьего токовых зеркал связаны с первым управляемым входным сигналом по каналу «Y» источником тока, входы второго и четвертого токовых зеркал связаны со вторым противофазно управляемым входным сигналом по каналу «Y» источником тока, выходы третьего и второго токовых зеркал соединены с первым токовым выходом аналогового перемножителя напряжений и первой цепью нагрузки, а выходы первого и четвертого токовых зеркал соединены со вторым токовым выходом аналогового перемножителя напряжений и второй цепью нагрузки. 4 з.п. ф-лы, 10 ил.

1. Аналоговый перемножитель напряжений, содержащий первое (1) токовое зеркало, общий вход которого соединен с общим входом второго (2) токового зеркала, третье токовое зеркало (3), общий вход которого связан с общим входом четвертого (4) токового зеркала, первый (5) и второй (6) противофазно управляемые входным сигналом по каналу «Y» источники тока, отличающийся тем, что объединенные общие входы первого (1) и второго (2) токовых зеркал соединены с первым (7) потенциальным входом канала «X», объединенные общие входы третьего (3) и четвертого (4) токовых зеркал соединены со вторым потенциальным (8) входом канала «X», входы первого (1) и третьего токовых зеркал связаны с первым (5) управляемым входным сигналом по каналу «Y» источником тока, входы второго (2) и четвертого (4) токовых зеркал связаны со вторым (6) противофазно управляемым входным сигналом по каналу «Y» источником тока, выходы третьего (3) и второго (2) токовых зеркал соединены с первым (9) токовым выходом аналогового перемножителя напряжений и первой (10) цепью нагрузки, а выходы первого (1) и четвертого (4) токовых зеркал соединены со вторым (11) токовым выходом аналогового перемножителя напряжений и второй (12) цепью нагрузки.

2. Устройство по п.1, отличающееся тем, что первый (5) управляемый входным сигналом по каналу «Y» источник тока содержит первый (27) и второй (28) дополнительные токостабилизируюшие двухполюсники, между которыми включен первый (29) дополнительный резистор, первый (30) дополнительный транзистор, эмиттер которого соединен со вторым (28) дополнительными токостабилизирующим двухполюсником и первым (29) дополнительным резистором, а база соединена с первым (31) входом по каналу «Y», второй (6) управляемый входным сигналом по каналу «Y» источник тока содержит третий (32) и четвертый (33) дополнительные токостабилизирующие двухполюсники, между которыми включен второй (34) дополнительный резистор, второй (35) дополнительный транзистор, эмиттер которого соединен с четвертым (33) дополнительными токостабилизирующим двухполюсником и вторым (34) дополнительным резистором, а база соединена со вторым (36) входом по каналу «Y».

3. Устройство по п.1, отличающееся тем, что противофазные источники входных напряжений по каналу «X» uх и  связаны с первым (7) и вторым (8) потенциальными входами канала «X» через первый (37) и второй (38) дополнительные повторители напряжений, на входы которых (39) и (40) подаются противофазные напряжения uх и

связаны с первым (7) и вторым (8) потенциальными входами канала «X» через первый (37) и второй (38) дополнительные повторители напряжений, на входы которых (39) и (40) подаются противофазные напряжения uх и  канала «X».

канала «X».

4. Устройство по п.3, отличающееся тем, что первый (37) дополнительный повторитель напряжения содержит первый (41) вспомогательный транзистор и первый (42) вспомогательный двухполюсник, связанный с первым (7) потенциальным входом канала «X» и эмиттером первого (41) вспомогательного транзистора, база которого соединена со входом (39) первого (37) дополнительного повторителя напряжения, а второй (38) дополнительный повторитель напряжения содержит второй (43) вспомогательный транзистор и второй (44) вспомогательный двухполюсник, связанный со вторым (8) потенциальным входом канала «X» и эмиттером второго (43) вспомогательного транзистора, база которого соединена со входом (40) второго дополнительного повторителя напряжения.

5. Устройство по п.4, отличающееся тем, что первый (5) управляемый входным сигналом по каналу «Y» источник тока содержит третий (45) вспомогательный двухполюсник и первый (46) вспомогательный резистор, включенный между первым (47) потенциальным входом по каналу «Y» и объединенными входами первого (1) и третьего (3) токовых зеркал, а второй (6) управляемый входным сигналом по каналу «Y» источник тока содержит четвертый (48) вспомогательный двухполюсник и второй (49) вспомогательный резистор, включенный между вторым (50) потенциальным входом по каналу «Y» и объединенными входами второго (2) и четвертого (4) токовых зеркал.

| US 5329189 А, 12.07.1994 | |||

| ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ С ПОВЫШЕННЫМ ОСЛАБЛЕНИЕМ СИНФАЗНОГО СИГНАЛА | 2005 |

|

RU2278466C1 |

| ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ | 2005 |

|

RU2284647C1 |

| Перемножитель электрических сигналов | 1990 |

|

SU1820396A1 |

| US 4462005 А, 24.07.1984. | |||

Авторы

Даты

2010-02-20—Публикация

2008-12-02—Подача