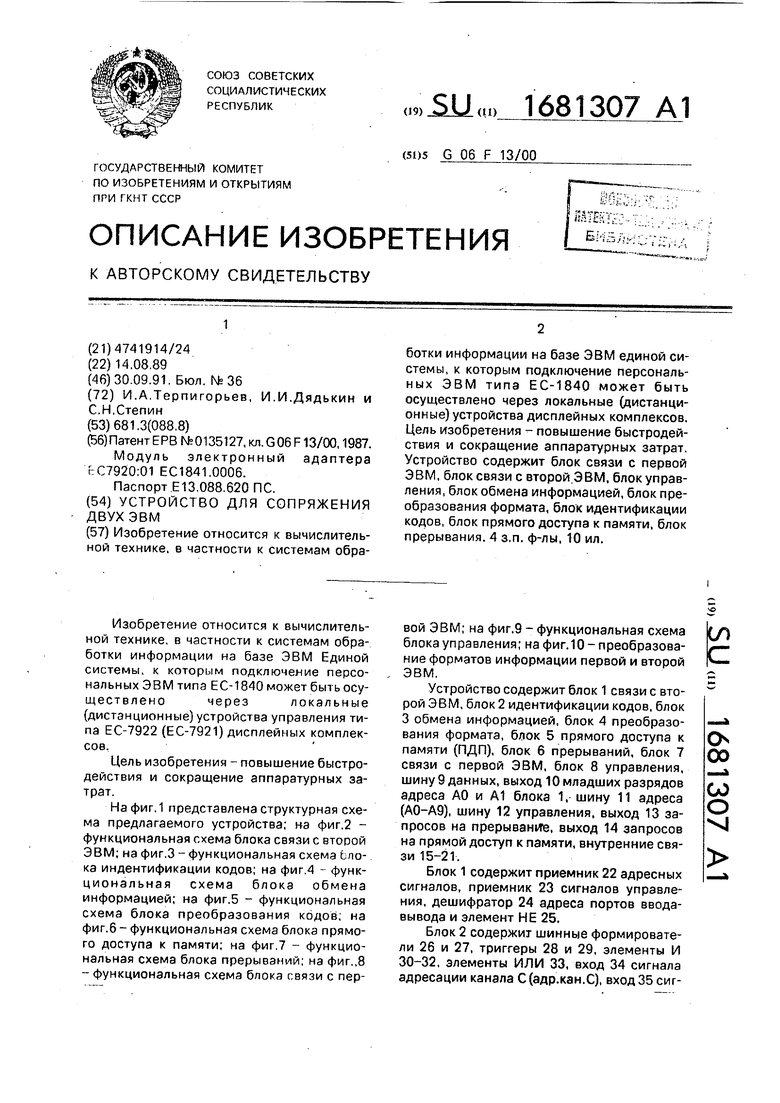

Изобретение относится к вычислительной технике в частности к системам обработки информации на базе ЭВМ Единой системы, к которым подключение персональных ЭВМ типа ЕС-1840 может быть осуществленочерезлокальные(дистанционные) устройства управления типа ЕС-7922 (ЕС-7921) дисплейных комплексов.

Цель изобретения - повышение быстродействия и сокращение аппаратурных затрат

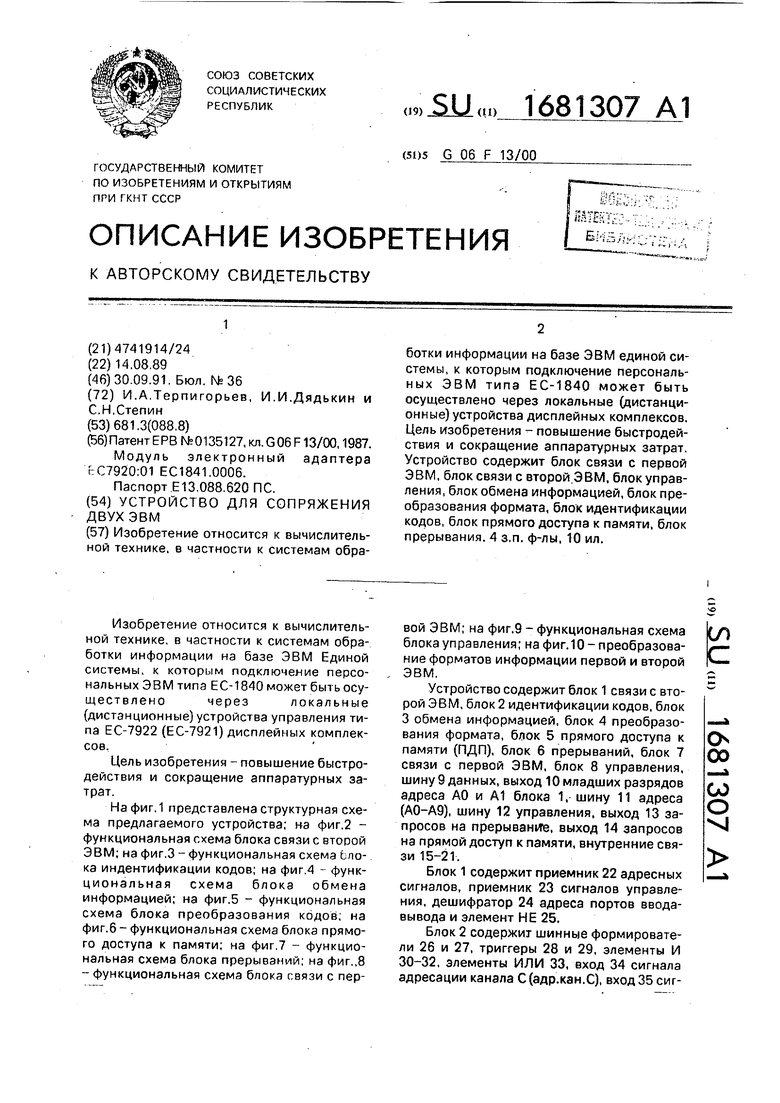

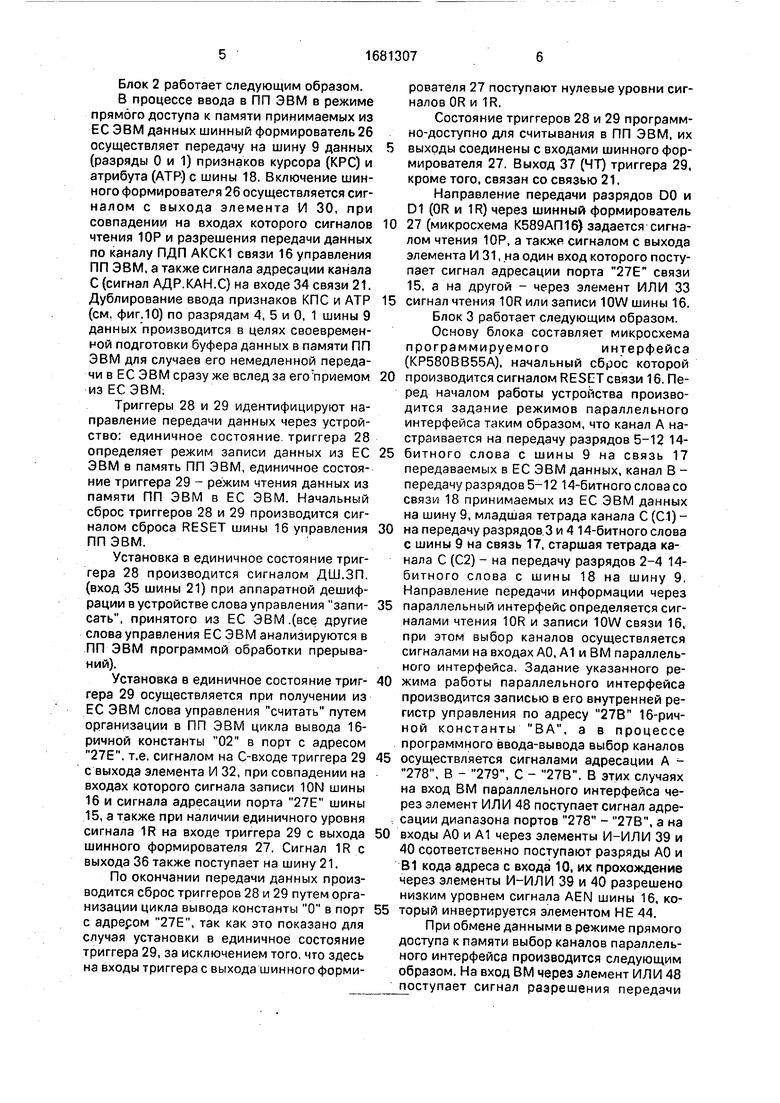

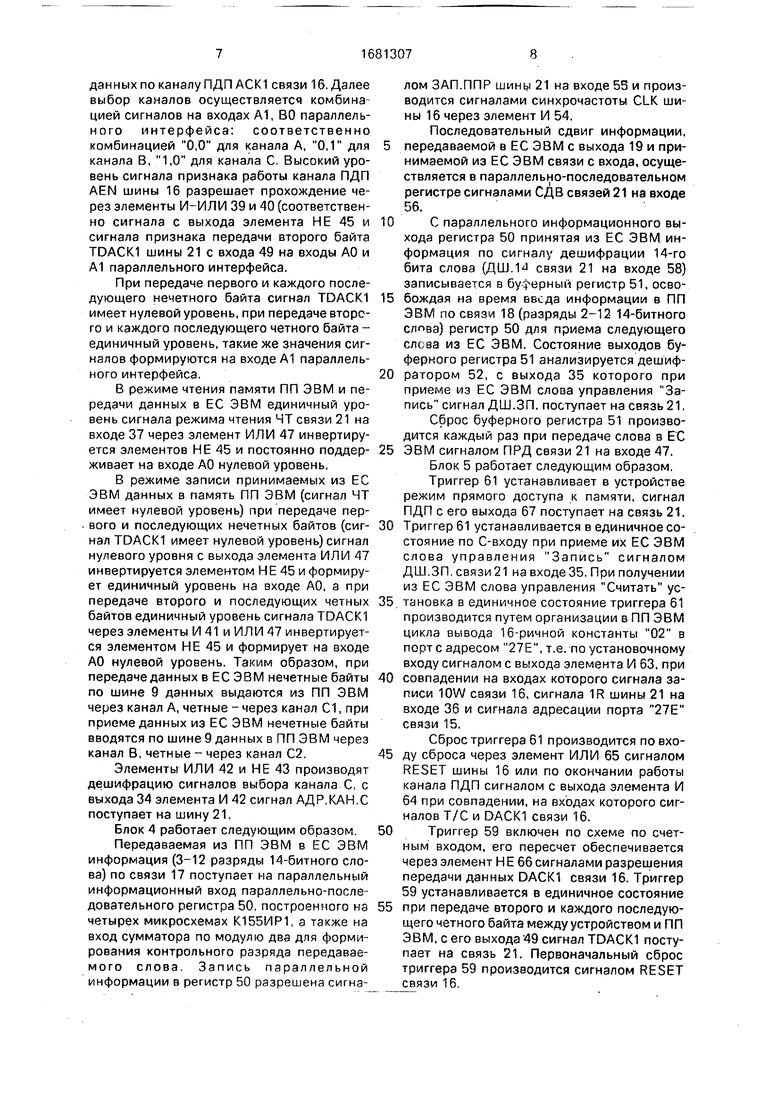

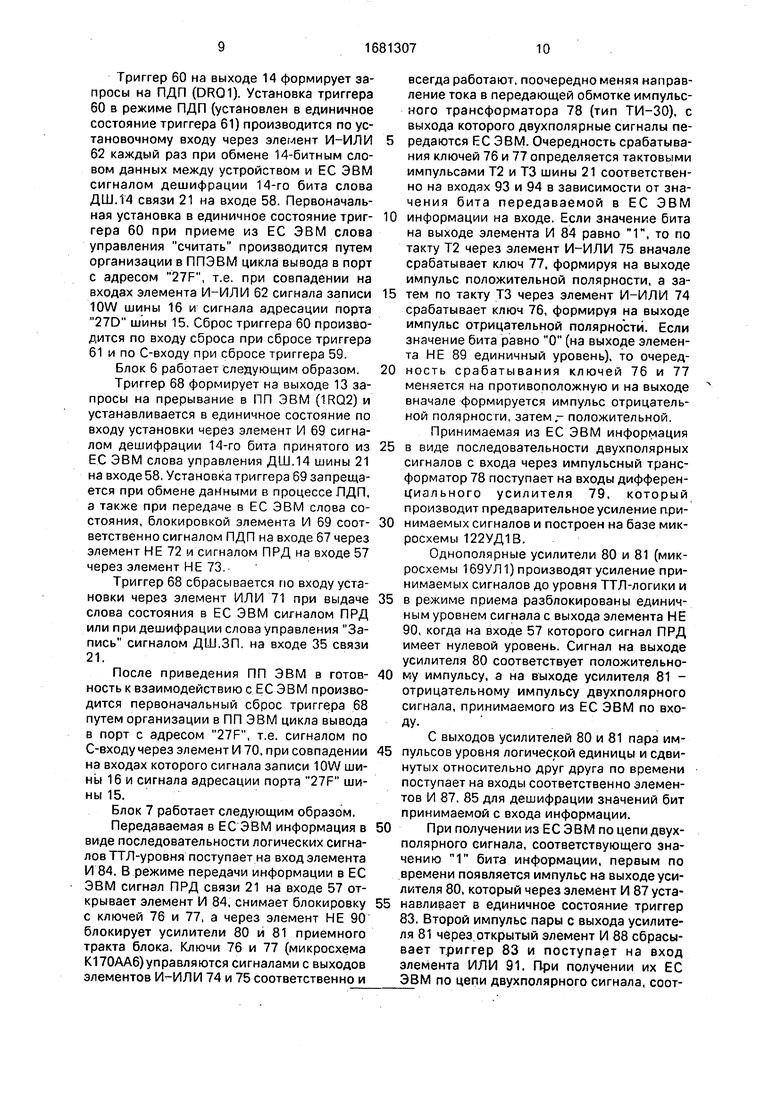

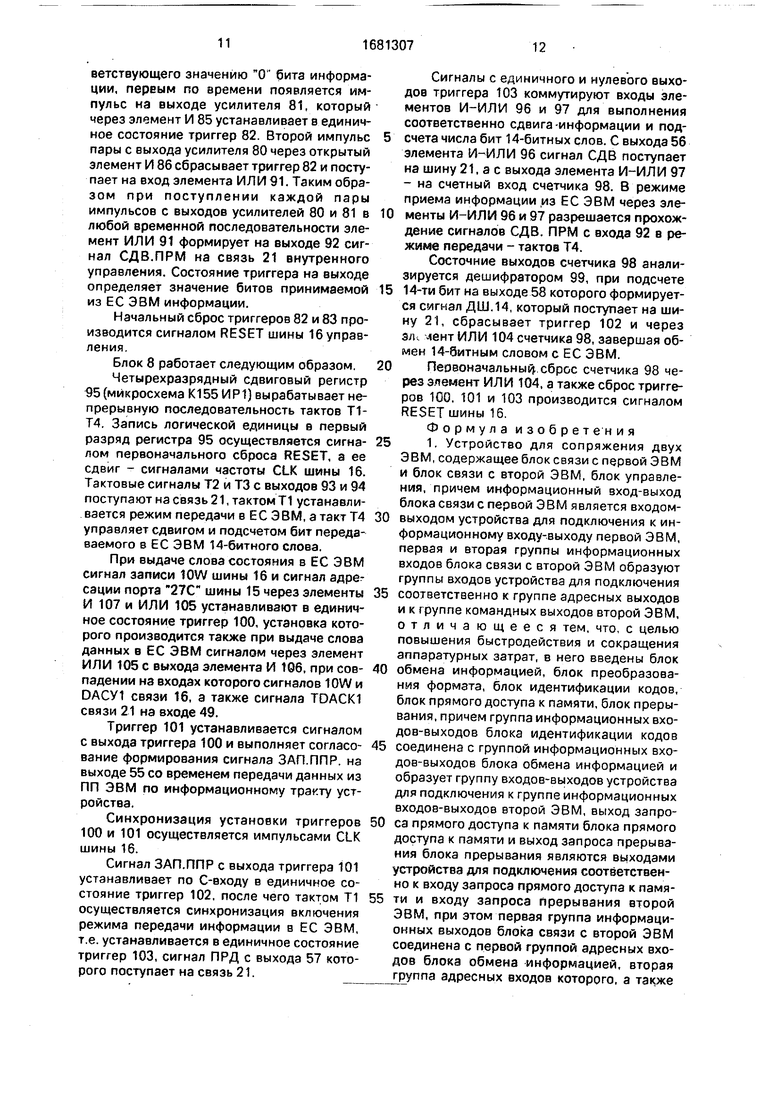

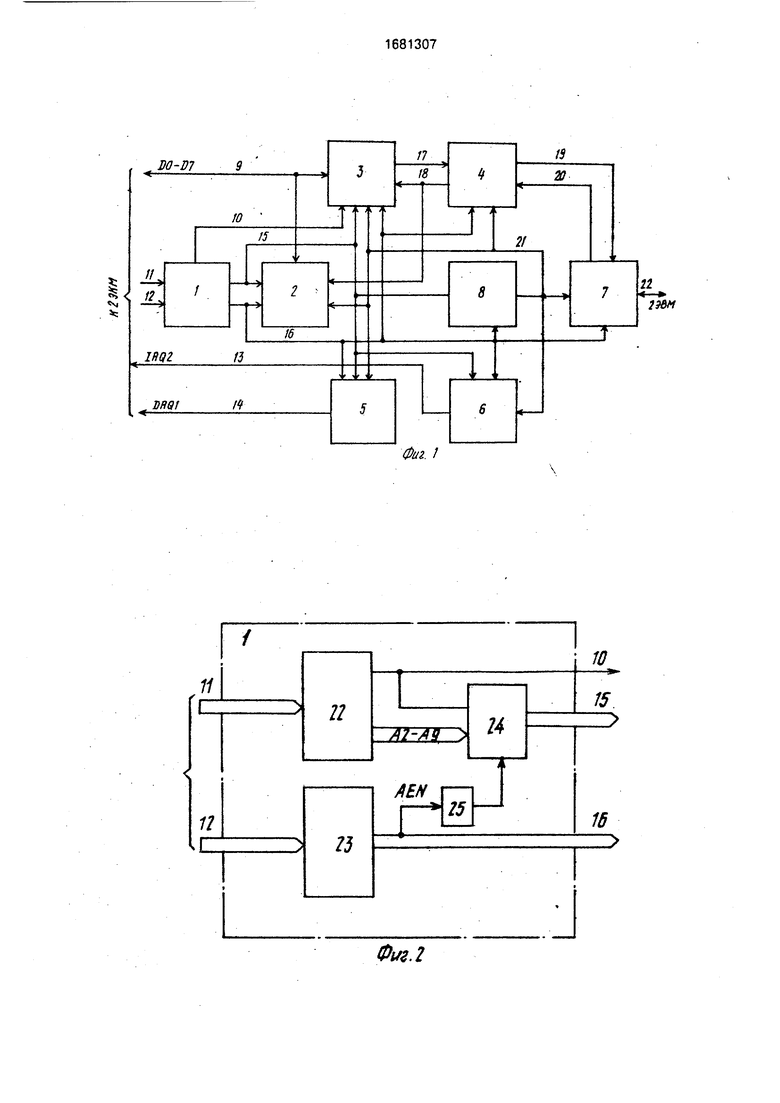

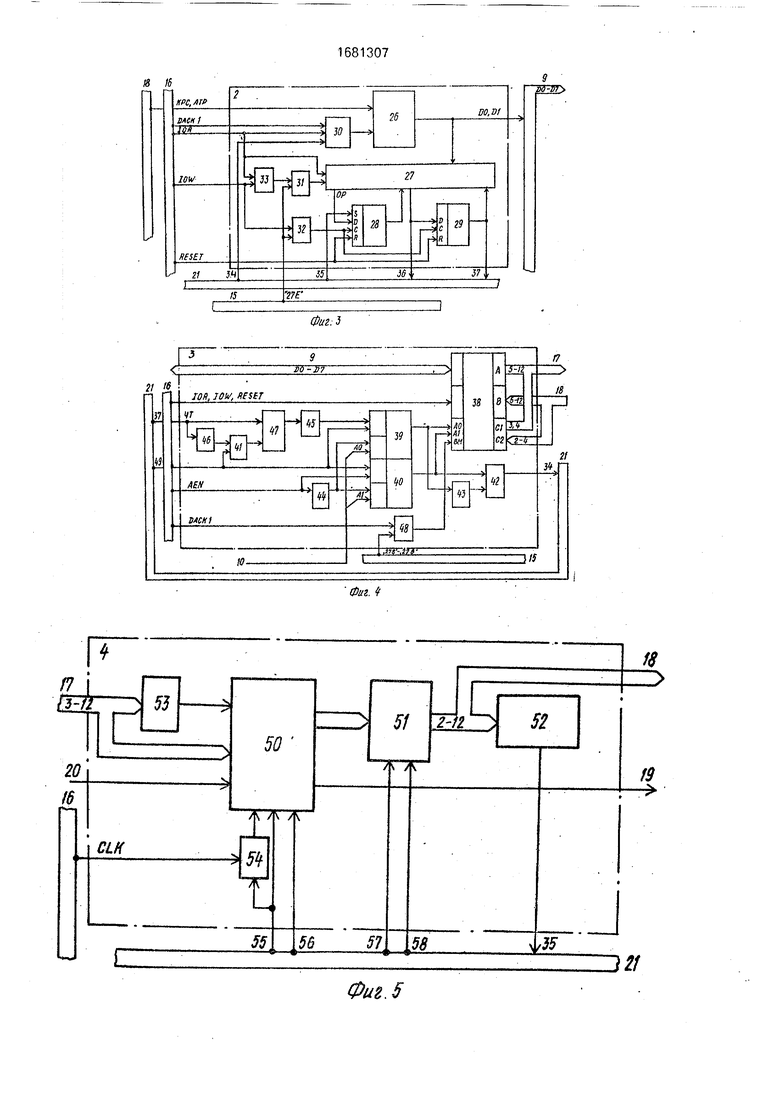

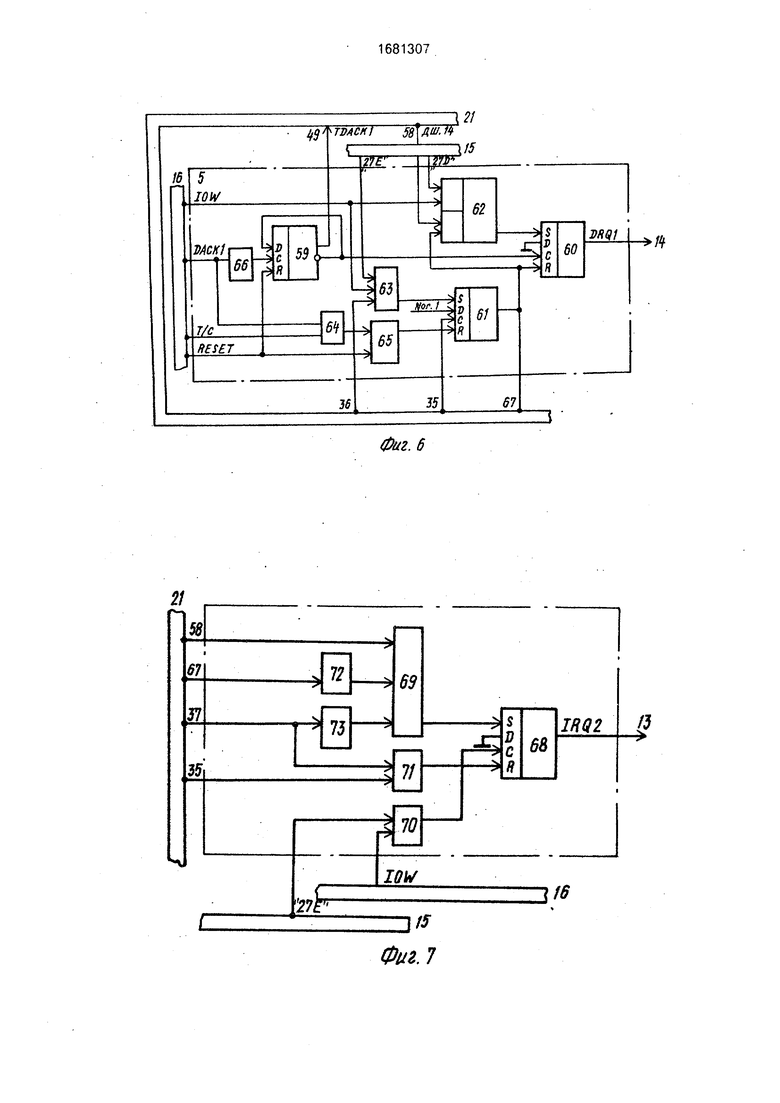

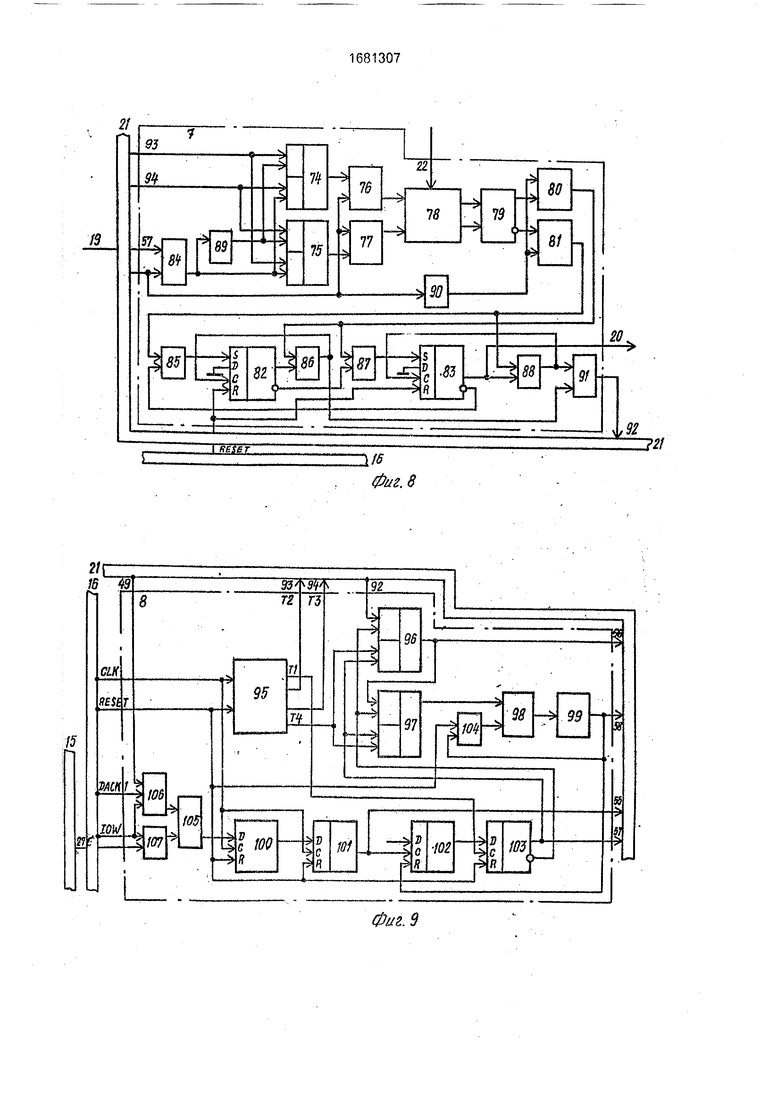

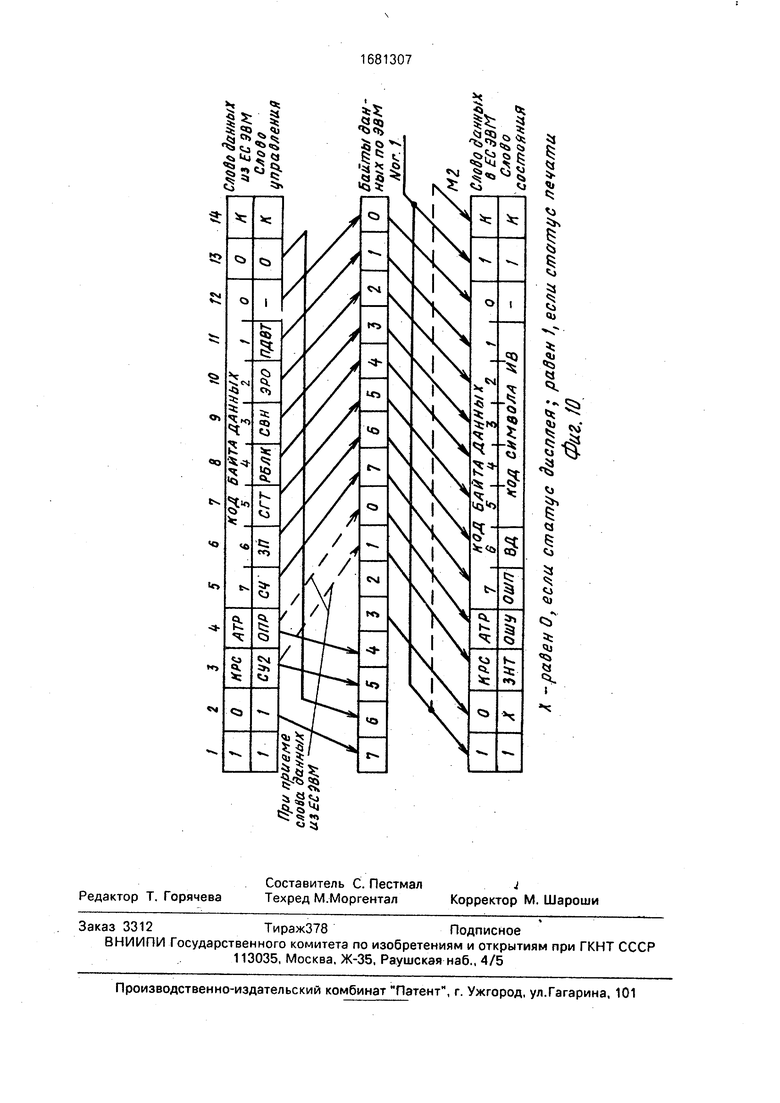

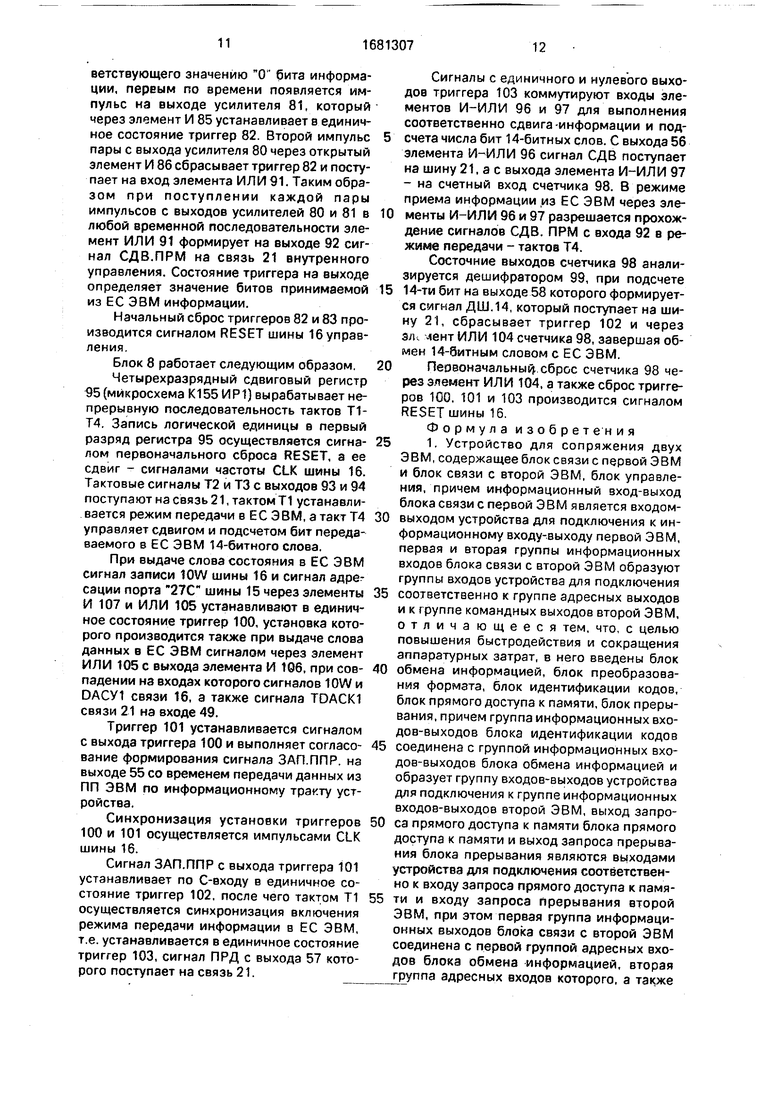

На фиг 1 представлена структурная схема предлагаемого устройства, на фиг.2 - функциональная схема блока связи с второй ЭВМ; на фиг 3 - функциональная схема tno- ка индентификации кодов, на фиг 4 - функ- циональная схема блока обмена информацией; на фиг.5 - функциональная схема блока преобразования кодов, на фиг.6 - функциональная схема блока прямого доступа к памяти, на фиг 7 - функциональная схема блока прерываний, на фиг ,8 - функциональная схема блока связи с первой ЭВМ; на фиг.9 - функциональная схема блока управления; на фиг. 10 - преобразование форматов информации первой и второй ЭВМ

Устройство содержит блок 1 связи с второй ЭВМ, блок 2 идентификации кодов, блок 3 обмена информацией, блок 4 преобразования формата, блок 5 прямого доступа к памяти (ПДП), блок 6 прерываний, блок 7 связи с первой ЭВМ, блок 8 управления, шину 9 данных, выход 10 младших разрядов адреса АО и А1 блока 1, шину 11 адреса (АО-А9), шину 12 управления, выход 13 запросов на прерывание, выход 14 запросов на прямой доступ к памяти, внутренние связи 15-21.

Блок 1 содержит приемник 22 адресных сигналов, приемник 23 сигналов управления, дешифратор 24 адреса портов ввода- вывода и элемент НЕ 25.

Блок 2 содержит шинные формирователи 26 и 27, триггеры 28 и 29, элементы И 30-32, элементы ИЛИ 33, вход 34 сигнала адресации канала С(адр.кан.С), вход 35 сигсл

С

с

00

со о

нала дешифрации указания Запись (ДШ.ЗП), выход 36 первого разряда байта данных (1R), выход 37 идентификации режима Чтение (ЧТ).

Блок 3 содержит приемопередатчик 38, элементы И-ИЛИ 39 и 40, элементы И 41 и 42, элементы НЕ 43-46, элементы ИЛИ 47 и 48, вход 49 признака передачи второго байта (ТДАСК-1).

Блок 4 содержит регистр 50, буферный регистр 51, дешифратор 52, сумматор 53 по модулю 2, элемент И 54, вход 55 параллельного занесения в регистр 50 (ЗАП.ППР), вход 56 сдвига информации в регистре 50 (СДВ), вход 57 сигнала режима передачи информации в первую ЭВМ (ПРД), вход 58 сигнала дешифрации 14-го бита слова (ДШ.14).

Блок 5 содержит триггеры 59-61, элемент И-ИЛИ 62, элементы И 63 и 64. элемент ИЛИ 65, элемент НЕ 66, выход 67 сигнала режима прямого доступа к памяти (ПДП).

Блок 6 содержит триггер 68, элементы И 69 и 70, элемент ИЛИ 71, элементы НЕ 72 и 73.

Блок 7 содержит элементы И-ИЛИ 74 и 75 Ключи 76 и 77, импульсный трансформатор 78, дифференциальный усилитель 79, усилители 80 и 81, триггеры 82 и 83. элементы И 84-88, элементы НЕ 89 и 90, элемент ИЛИ 91, выход 92 сдвига принимаемой из первой ЭВМ информации (СДВ.ПРМ), вход 93 такта Т2, вход 94 такта ТЗ.

Блок 8 содержит регистр 95, элементы И-ИЛИ 96 и 97, счетчик 98, дешифратор 99, триггеры 100-103, элементы ИЛИ 104 и 105, элементы И 106 и 107.

Устройство работает следующим образом.

Информация, последовательно принимаемая из первой ЭВМ, в качестве которой выступает ЕС ЭВМ, в виде двухполярных 14-битных слов по линии связи, преобразуется блоком 7 в последовательность логических сигналов ТТЛ-уровня и по связи 20 передается в блок 4, с выхода 18 которого информация в параллельном коде через блок 3 вводится по шине9 данных во вторую ЭВМ, в качестве которой выступает персональная профессиональная ЭВМ {ПП ЭВМ).

Информация, передаваемая в ЕС ЭВМ, поступает из ПП ЭВМ по шине 9 данных через блок 3 и его выход в блок 4, с выхода которого последовательный код выдается в блок 7 для формирования двухполярного сигнала и выдачи его по линии связи в ЕС ЭВМ.

Обмен 14-битными словами между ЕС ЭВМ и ПП ЭВМ по 8-разрядной шине 9

данных производится за два машинных цикла ввода-вывода, причем в первом цикле по шине 9 данных передается байт, соответствующий разрядам 5-12 14-битного слова, во

втором цикле - байт, соответствующий разрядам 2-4. Соответствие форматов представления информации ЕС ЭВМ и ПП ЭВМ приведено на фиг. 10.

Параллельно-последовательное преоб0 разование информации, формирвоание двухполярных сигналов и передача их в ЕС ЭВМ, а также формирование запросов в ПП ЭВМ осуществляется под управлением блока 8 сигналами на связи 21.

5 По окончании приема слова управления из ЕС ЭВМ блоком 8 выбрасывается сигнал дешифрации 14-го бита слова, который по связи 21 поступает в блок 6, на выходе 13 которого формируется запрос на прерыва0 ние в ППЭВМ(ЛР02). В процессе обработки прерывания ПП ЭВМ считывает слово управления из блока 3 или выдает слово состояния в.блок 3 по шине 9 данных.

При обмене между ПП ЭВМ и ЕС ЭВМ

5 словами данных по сигналу дешифрации 14- го бита слова блоком 5 на выходе 14 формируются запросы, Обмен данными производится в режиме прямого доступа к памяти, причем при вводе слова данных в

0 ПП ЭВМ третий и четвертый разряды 14- битного слова одновременно передаются как по разрядам 4 и 5 шины 9 данных из блока 3, так и по разрядам 0 и 1 из блока 2.

5 Признаки чтения данных из ПП ЭВМ и записи данных в ПП ЭВМ формируются в блоке 2.

В процессе выполнения циклов ввода- вывода ПП ЭВМ выдает в блок 1 коды адре0 сов портов ввода-вывода по шине 11 адреса и сигналы управления по шине 12. Блок 1 обеспечивает доступ к различным блокам устройства сигналов управления ПП ЭВМ по связи 16 и сигналов адресации портов по

5 связи 15, а также с выхода 10 выдает два младших разряда кода адреса (АО и А9) в блок 3.

Блок 1 работает следующим образом. Приемники 22 и 23 осуществляют раз0 вязку системой шины ПП ЭВМ по нагрузке. Приемник 23 транслирует сигналы управления ПП ЭВМ с шины 12 на связь 16. Через приемник 22 разряды кода адреса АО-А9 с шины 11 поступают на дешифратор 24, ко5 торый на выходе производит дешифрацию адресов портов ввода-вывода. Во время работы канала ПДП дешифратор 24 блокируется через элемент НЕ 25 сигналом АЕН с выхода приемника 23. Два младших разряда АО и А1 кода адреса выдаются в устройства с выхода 10 приемника 22.

Блок 2 работает следующим образом.

В процессе ввода в ПП ЭВМ в режиме прямого доступа к памяти принимаемых из ЕС ЭВМ данных шинный формирователь 26 осуществляет передачу на шину 9 данных (разряды 0 и 1) признаков курсора (КРС) и атрибута (АТР-) с шины 18. Включение шинного формирователя 26 осуществляется сиг- налом с выхода элемента И 30, при совпадении на входах которого сигналов чтения ЮР и разрешения передачи данных по каналу ПДП АКСК1 связи 16 управления ПП ЭВМ, а также сигнала адресации канала С (сигнал АДР.КАН.С) на входе 34 связи 21. Дублирование ввода признаков КПС и АТР (см. фиг.10) по разрядам 4, 5 и 0, 1 шины 9 данных производится в целях своевременной подготовки буфера данных в памяти ПП ЭВМ для случаев его немедленной передачи в ЕС ЭВМ сразу же вслед за его приемом из ЕС ЭВМ.

Триггеры 28 и 29 идентифицируют направление передачи данных через устройство: единичное состояние триггера 28 определяет режим записи данных из ЕС ЭВМ в память ПП ЭВМ, единичное состояние триггера 29 - режим чтения данных из памяти ПП ЭВМ в ЕС ЭВМ. Начальный сброс триггеров 28 и 29 производится сигналом сброса RESET шины 16 управления ПП ЭВМ.

Установка в единичное состояние триггера 28 производится сигналом ДШ.ЗП. (вход 35 шины 21) при аппаратной дешифрации в устройстве слова управления записать, принятого из ЕС ЭВМ.(все другие слова управления ЕС ЭВМ анализируются в ПП ЭВМ программой обработки прерываний).

Установка в единичное состояние триггера 29 осуществляется при получении из ЕС ЭВМ слова управления считать путем организации в ПП ЭВМ цикла вывода 16- ричной константы 02 в порт с адресом 27Е. т.е. сигналом на С-входе триггера 29 с выхода элемента И 32, при совпадении на входах которого сигнала записи 10N шины 16 и сигнала адресации порта 27Е шины 15, а также при наличии единичного уровня сигнала 1R на входе триггера 29 с выхода шинного формирователя 27. Сигнал 1R с выхода 36 также поступает на шину 21.

По окончании передачи данных производится сброс триггеров 28 и 29 путем организации цикла вывода константы О в порт с адрером 27Е, так как это показано для случая установки в единичное состояние триггера 29, за исключением того, что здесь на входы триггера с выхода шинного формирователя 27 поступают нулевые уровни сигналов OR и 1R.

Состояние триггеров 28 и 29 программно-доступно для считывания в ПП ЭВМ, их выходы соединены с входами шинного формирователя 27. Выход 37 (ЧТ) триггера 29, кроме того, связан со связью 21.

Направление передачи разрядов DO и D1 (OR и 1R) через шинный формирователь

0 27 (микросхема К589АП16) задается сигналом чтения ЮР, а также сигналом с выхода элемента И 31, на один вход которого поступает сигнал адресации порта 27Е связи 15, а на другой - через элемент ИЛИ 33

5 сигнал чтения 10R или записи 10W шины 16.

Блок 3 работает следующим образом.

Основу блока составляет микросхема

программируемогоинтерфейса

(КР580ВВ55А), начальный сброс которой

0 производится сигналом RESET связи 16. Перед началом работы устройства производится задание режимов параллельного интерфейса таким образом, что канал А настраивается на передачу разрядов 5-12 145 битного слова с шины 9 на связь 17 передаваемых в ЕС ЭВМ данных, канал В - передачу разрядов 5-12 14-битного слова со связи 18 принимаемых из ЕС ЭВМ данных на шину 9, младшая тетрада канала С (С1) 0 на передачу разрядов 3 и 4 14-битного слова с шины 9 на связь 17, старшая тетрада канала С (С2) - на передачу разрядов 2-4 14- битного слова с шины 18 на шину 9. Направление передачи информации через

5 параллельный интерфейс определяется сигналами чтения 10R и записи 10W связи 16, при этом выбор каналов осуществляется сигналами на входах АО, А1 и ВМ параллельного интерфейса. Задание указанного ре0 жима работы параллельного интерфейса производится записью в его внутренней регистр управления по адресу 27В 16-рич- ной константы ВА, а в процессе программного ввода-вывода выбор каналов

5 осуществляется сигналами адресации А - 278, В - 279й, С - 27В. В этих случаях на вход ВМ параллельного интерфейса через элемент ИЛИ 48 поступает сигнал адресации диапазона портов 278 - 27В, а на

0 входы АО и А1 через элементы И-ИЛИ 39 и 40 соответственно поступают разряды АО и В1 кода адреса с входа 10, их прохождение через элементы И-ИЛИ 39 и 40 разрешено низким уровнем сигнала AEN шины 16, ко5 торый инвертируется элементом НЕ 44.

При обмене данными в режиме прямого доступа к памяти выбор каналов параллельного интерфейса производится следующим образом. На вход ВМ через элемент ИЛИ 48 поступает сигнал разрешения передачи

данных по каналу ПДПАСК1 связи 16. Далее выбор каналов осуществляется комбина цией сигналов на входах А1, ВО параллельного интерфейса: соответственно комбинацией 0,0 для канала А, 0,1 для канала В, 1,0 для канала С. Высокий уровень сигнала признака работы канала ПДП AEN шины 16 разрешает прохождение через элементы И-ИЛИ 39 и 40 (соответственно сигнала с выхода элемента НЕ 45 и сигнала признака передачи второго байта TDACK1 шины 21 с входа 49 на входы АО и А1 параллельного интерфейса.

При передаче первого и каждого последующего нечетного байта сигнал TDACK1 имеет нулевой уровень, при передаче вторе- го и каждого последующего четного байта - единичный уровень, такие же значения сигналов формируются на входе А1 параллельного интерфейса.

В режиме чтения памяти ПП ЭВМ и передачи данных в ЕС ЭВМ единичный уровень сигнала режима чтения ЧТ связи 21 на входе 37 через элемент ИЛИ 47 инвертируется элементов НЕ 45 и постоянно поддерживает на входе АО нулевой уровень.

В режиме записи принимаемых из ЕС ЭВМ данных в память ПП ЭВМ (сигнал ЧТ имеет нулевой уровень) при передаче первого и последующих нечетных байтов (сигнал TDACK1 имеет нулевой уровень) сигнал нулевого уровня с выхода элемента ИЛИ 47 инвертируется элементом НЕ 45 и формирует единичный уровень на входе АО, а при передаче второго и последующих четных байтов единичный уровень сигнала TDACK1 через элементы И 41 и ИЛИ 47 инвертируется элементом НЕ 45 и формирует на входе АО нулевой уровень. Таким образом, при передаче данных в ЕС ЭВМ нечетные байты по шине 9 данных выдаются из ПП ЭВМ через канал А, четные - через канал С1, при приеме данных из ЕС ЭВМ нечетные байты вводятся по шине 9 данных в ПП ЭВМ через канал В, четные - через канал С2.

Элементы ИЛИ 42 и НЕ 43 производят дешифрацию сигналов выбора канала С, с выхода 34 элемента И 42 сигнал АДР.КАН.С поступает на шину 21.

Блок 4 работает следующим образом.

Передаваемая из ПП ЭВМ в ЕС ЭВМ информация (3-12 разряды 14-битного слова) по связи 17 поступает на параллельный информационный вход параллельно-последовательного регистра 50, построенного на четырех микросхемах К155ИР1, а также на вход сумматора по модулю два для формирования контрольного разряда передаваемого слова. Запись параллельной информации в регистр 50 разрешена сигналом ЗАП.ППР шину 21 на входе 55 и производится сигналами синхрочастоты CLK шины 16 через элемент И 54,

Последовательный сдвиг информации,

передаваемой в ЕС ЭВМ с выхода 19 и принимаемой из ЕС ЭВМ связи с входа, осуществляется в параллельно-последовательном регистре сигналами СДВ связей 21 на входе 56.

0 С параллельного информационного выхода регистра 50 принятая из ЕС ЭВМ информация по сигналу дешифрации 14-го бита слова (ДШ.1 связи 21 на входе 58) записывается в буферный регистр 51, осво5 бождая на время ввсда информации в ПП ЭВМ по связи 18 (разряды 2-12 14-битного слова) регистр 50 для приема следующего слева из ЕС ЭВМ. Состояние выходов буферного регистра 51 анализируется дешиф0 ратором 52, с выхода 35 которого при приеме из ЕС ЭВМ слова управления Запись сигнал ДШ.ЗП. поступает на связь 21. Сброс буферного регистра 51 производится каждый раз при передаче слова в ЕС

5 ЭВМ сигналом ПРД связи 21 на входе 47. Блок 5 работает следующим образом. Триггер 61 устанавливает в устройстве режим прямого доступа к памяти, сигнал ПДП с его выхода 67 поступает на связь 21.

0 Триггер 61 устанавливается в единичное состояние по С-входу при приеме их ЕС ЭВМ слова управления Запись сигналом ДШ.ЗП. связи 21 на входе 35. При получении из ЕС ЭВМ слова управления Считать ус5 тановка в единичное состояние триггера 61 производится путем организации в ПП ЭВМ цикла вывода 16-ричной константы 02 в порт с адресом 27Е, т.е. по установочному входу сигналом с выхода элемента И 63, при

0 совпадении на входах которого сигнала записи 10W связи 16, сигнала 1R шины 21 на входе 36 и сигнала адресации порта 27Е связи 15.

Сброс триггера 61 производится по вхо5 ду сброса через элемент ИЛИ 65 сигналом RESET шины 16 или по окончании работы канала ПДП сигналом с выхода элемента И 64 при совпадении, на входах которого сигналов Т/С и DACK1 связи 16.

0 Триггер 59 включен по схеме по счетным входом, его пересчет обеспечивается через элемент НЕ 66 сигналами разрешения передачи данных DACK1 связи 16. Триггер 59 устанавливается в единичное состояние

5 при передаче второго и каждого последующего четного байта между устройством и ПП ЭВМ, с его выхода 49 сигнал TDACK1 поступает на связь 21. Первоначальный сброс триггера 59 производится сигналом RESET связи 16.

Триггер 60 на выходе 14 формирует запросы на ПДП (DR01). Установка триггера

60в режиме ПДП (установлен в единичное состояние триггера 61) производится по установочному входу через элемент И-ИЛИ 62 каждый раз при обмене 14-битным словом данных между устройством и ЕС ЭВМ сигналом дешифрации 14-го бита слова ДШ.14 связи 21 на входе 58. Первоначальная установка в единичное состояние триг- гера 60 при приеме из ЕС ЭВМ слова управления считать производится путем организации в ППЭВМ цикла вывода в порт

с адресом 27F, т.е. при совпадении на входах элемента И-ИЛИ 62 сигнала записи 10W шины 16 и сигнала адресации порта 27D шины 15. Сброс триггера 60 производится по входу сброса при сбросе триггера

61и по С-входу при сбросе триггера 59.

Блок 6 работает следующим образом.

Триггер 68 формирует на выходе 13 запросы на прерывание в ПП ЭВМ (1RQ2) и устанавливается в единичное состояние по входу установки через элемент И 69 сигналом дешифрации 14-го бита принятого из ЕС ЭВМ слова управления ДШ.14 шины 21 на входе 58, Установка триггера 69 запрещается при обмене данными в процессе ПДП, а также при передаче в ЕС ЭВМ слова состояния, блокировкой элемента И 69 соот- ветственно сигналом ПДП на входе 67 через элемент НЕ 72 и сигналом ПРД на входе 57 через элемент НЕ 73.

Триггер 68 сбрасывается по входу установки через элемент ИЛИ 71 при выдаче слова состояния в ЕС ЭВМ сигналом ПРД или при дешифрации слова управления Запись сигналом ДШ.ЗП. на входе 35 связи 21.

После приведения ПП ЭВМ в готов- ность к взаимодействию с ЕС ЭВМ производится первоначальный сброс триггера 68 путем организации в ПП ЭВМ цикла вывода в порт с адресом 27F, т.е. сигналом по С-входу через элемент И 70, при совпадении на входах которого сигнала записи 10W шины 16 и сигнала адресации порта 27F шины 15.

Блок 7 работает следующим образом.

Передаваемая в ЕС ЭВМ информация в виде последовательности логических сигналов ТТЛ-уровня поступает на вход элемента И 84. В режиме передачи информации в ЕС ЭВМ сигнал ПРД связи 21 на входе 57 открывает элемент И 84, снимает блокировку с ключей 76 и 77, а через элемент НЕ 90 блокирует усилители 80 и 81 приемного тракта блока. Ключи 76 и 77 (микросхема К170АА6)управляются сигналами с выходов элементов И-ИЛИ 74 и 75 соответственно и

всегда работают, поочередно меняя направление тока в передающей обмотке импульсного трансформатора 78 (тип ТИ-30), с выхода которого двухполярные сигналы передаются ЕС ЭВМ. Очередность срабатывания ключей 76 и 77 определяется тактовыми импульсами Т2 и ТЗ шины 21 соответственно на входах 93 и 94 в зависимости от значения бита передаваемой в ЕС ЭВМ информации на входе. Если значение бита на выходе элемента И 84 равно 1й, то по такту Т2 через элемент И-ИЛИ 75 вначале срабатывает ключ 77, формируя на выходе импульс положительной полярности, а затем по такту ТЗ через элемент И-ИЛИ 74 срабатывает ключ 76, формируя на выходе импульс отрицательной полярности. Если значение бита равно О (на выходе элемента НЕ 89 единичный уровень), то очередность срабатывания ключей 76 и 77 меняется на противоположную и на выходе вначале формируется импульс отрицательной полярности, затем,- положительной.

Принимаемая из ЕС ЭВМ информация в виде последовательности двухполярных сигналов с входа через импульсный трансформатор 78 поступает на входы дифферен- циального усилителя 79. который производит предварительное усиление принимаемых сигналов и построен на базе микросхемы 122УД1В.

Однополярные усилители 80 и 81 (микросхемы 169УЛ1)производят усиление принимаемых сигналов до уровня ТТЛ-логики и в режиме приема разблокированы единичным уровнем сигнала с выхода элемента НЕ 90, когда на входе 57 которого сигнал ПРД имеет нулевой уровень. Сигнал на выходе усилителя 80 соответствует положительному импульсу, а на выходе усилителя 81 - отрицательному импульсу двухполярного сигнала, принимаемого из ЕС ЭВМ по вхоДУС выходов усилителей 80 и 81 пара импульсов уровня логической единицы и сдвинутых относительно друг друга по времени поступает на входы соответственно элементов И 87, 85 для дешифрации значений бит принимаемой с входа информации.

При получении из ЕС ЭВМ по цепи двухполярного сигнала, соответствующего значению 1 бита информации, первым по времени появляется импульс на выходе усилителя 80, который через элемент И 87 устанавливает в единичное состояние триггер 83. Второй импульс пары с выхода усилителя 81 через открытый элемент И 88 сбрасывает триггер 83 и поступает на вход элемента ИЛИ 91. При получении их ЕС ЭВМ по цепи двухполярного сигнала, соответствующего значению О бита информации, первым по времени появляется импульс на выходе усилителя 81, который через элемент И 85 устанавливает в единичное состояние триггер 82. Второй импульс пары с выхода усилителя 80 через открытый элемент И 86 сбрасывает триггер 82 и поступает на вход элемента ИЛИ 91. Таким образом при поступлении каждой пары импульсов с выходов усилителей 80 и 81 в любой временной последовательности элемент ИЛИ 91 формирует на выходе 92 сигнал СДВ.ПРМ на связь 21 внутреннего управления. Состояние триггера на выходе определяет значение битов принимаемой из ЕС ЭВМ информации.

Начальный сброс триггеров 82 и 83 производится сигналом RESET шины управления.

Блок 8 работает следующим образом.

Четырехразрядный сдвиговый регистр 95 (микросхема К155ИР1) вырабатывает непрерывную последовательность тактов Т1- Т4. Запись логической единицы в первый разряд регистра 95 осуществляется сигналом первоначального сброса RESET, а ее сдвиг - сигналами частоты CLK шины 16. Тактовые сигналы Т2 и ТЗ с выходов 93 и 94 поступают на связь 21, тактом Т1 устанавливается режим передачи в ЕС ЭВМ, а такт Т4 управляет сдвигом и подсчетом бит передаваемого в ЕС ЭВМ 14-битного слова.

При выдаче слова состояния в ЕС ЭВМ сигнал записи 10W шины 16 и сигнал адресации порта 27С шины 15 через элементы И 107 и ИЛИ 105 устанавливают в единичное состояние триггер 100, установка которого производится также при выдаче слова данных в ЕС ЭВМ сигналом через элемент ИЛИ 105 с выхода элемента И 106, при совпадении на входах которого сигналов 10W и DACV1 связи 16, а также сигнала TDACK1 связи 21 на входе 49.

Триггер 101 устанавливается сигналом с выхода триггера 100 и выполняет согласование формирования сигнала ЗАП.ППР. на выходе 55 со временем передачи данных из ПП ЭВМ по информационному тракту устройства.

Синхронизация установки триггеров 100 и 101 осуществляется импульсами CLK шины 16.

Сигнал ЗАП.ППР с выхода триггера 101 устанавливает по С-входу в единичное состояние триггер 102, после чего тактом Т1 осуществляется синхронизация включения режима передачи информации в ЕС ЭВМ, т.е. устанавливается в единичное состояние триггер 103, сигнал ПРД с выхода 57 которого поступает на связь 21.

Сигналы с единичного и нулевого выходов триггера 103 коммутируют входы элементов И-ИЛИ 96 и 97 для выполнения соответственно сдвига-информации и подсчета числа бит 14-битных слов. С выхода 56 элемента И-ИЛИ 96 сигнал СДВ поступает на шину 21, а с выхода элемента И-ИЛИ 97 - на счетный вход счетчика 98. В режиме приема информации из ЕС ЭВМ через эле0 менты И-ИЛИ 96 и 97 разрешается прохождение сигналов СДВ. ПРМ с входа 92 в режиме передачи - тактов Т4.

Состочние выходов счетчика 98 анализируется дешифратором 99, при подсчете

5 14-ти бит на выходе 58 которого формируется сигнал ДШ.14, который поступает на шину 21, сбрасывает триггер 102 и через зл, лент ИЛИ 104 счетчика 98, завершая обмен 14-битным словом с ЕС ЭВМ.

0 Первоначальны сброс счетчика 98 через элемент ИЛИ 104, а также сброс триггеров 100, 101 и 103 производится сигналом RESET шины 16.

Формула изобретения

51. Устройство для сопряжения двух

ЭВМ, содержащее блок связи с первой ЭВМ и блок связи с второй ЭВМ, блок управления, причем информационный вход-выход блока связи с первой ЭВМ является входом0 выходом устройства для подключения к информационному входу-выходу первой ЭВМ, первая и вторая группы информационных входов блока связи с второй ЭВМ образуют группы входов устройства для подключения

5 соответственно к группе адресных выходов и к группе командных выходов второй ЭВМ, отличающееся тем, что, с целью повышения быстродействия и сокращения аппаратурных затрат, в него введены блок

0 обмена информацией, блок преобразования формата, блок идентификации кодов, блок прямого доступа к памяти, блок прерывания, причем группа информационных входов-выходов блока идентификации кодов

5 соединена с группой информационных входов-выходов блока обмена информацией и образует группу входов-выходов устройства для подключения к группе информационных входов-выходов второй ЭВМ, выход запро0 са прямого доступа к памяти блока прямого доступа к памяти и выход запроса прерывания блока прерывания являются выходами устройства для подключения соответственно к входу запроса прямого доступа к ламя5 ти и входу запроса прерывания второй ЭВМ, при этом первая группа информационных выходов блока связи с второй ЭВМ соединена с первой группой адресных входов блока обмена информацией, вторая группа адресных входов которого, а также

группа адресных входов блока управления, группа адресных входов блока прямого доступа к памяти, адресный вход блока прерывания, адресный вход блока идентификации кодов соединены с второй группой информационных выходов блока связи с второй ЭВМ, группы кодовых входов блока идентификации кодов, блока прямого доступа к памяти, блока обмена информацией, группа входов логического условия блока управления, синхровходы блока преобразования формата и блока прерывания и установочный вход блока связи с первой ЭВМ соединены с третьей группой информационных выходов блока связи с второй ЭВМ, группа входов-выходов логического условия блока управления соединена с группами кодовых входов-выходов блока связи с первой ЭВМ, блока преобразования формата, блока прямого доступа к памяти, блока идентификации кодов, блока обмена информацией, с группой кодовых входов блока прерывания, информационные вход и выход блока связи с первой ЭВМ соединены соответственно с информационными выходом и входом блока преобразования формата, группа информационных входов которого соединена с группой информационных выходов блока обмена информацией, группа информационных входов которого и группа входов при- знаков блока идентификации кодов соединены с группой информационных выходов блока преобразования формата.

2. Устройство поп.1,отличающее- с я тем, что блок идентификации кодов содержит два шинных формирователя, два триггера, три элемента И, элемент ИЛИ, причем первый вход первого элемента И соединен с первым входом второго элемента И и является адресным входом блока, группа информационных входов первого шинного формирователя образует группу входов признаков блока, группа информ а- ционных выходов первого шинного формирователя соединен с группой информационных входов-выходов второго шинного формирователя и образует группу информационных входов-выходов блока, первый вход третьего элемента И, второй вход третьего элемента И, соединенный с первым входом элемента ИЛИ и с первым входом режима работы второго шинного формирователя, второй вход элемента ИЛИ, соединенный с вторым входом первого элемента И, вход сброса первого триггера, соединенный с входом сброса второго триггера, образуют группу кодовых входов блока, третий вход третьего элемента И, установочный вход первого триггера, первый информационный выход второго шинного

формирователя, соединенный с информационным входом второго триггера, выход второго триггера, соединенный с первым информационным входом второго шинного 5 формирователя, образуют группу кодовых входов-выходов блока, при этом выход элемента ИЛИ соединен с вторым входом второго элемента И, выход которого соединен с вторым входом режима работы второго

0 шинного формирователя, вторые информационные выход и вход которого соединены соответственно с информационным входом и выходом первого триггера, синхровход которого соединен с смнхровходом второго

5 триггера и с выходом первого элемента И, выход третьего элемента И соединен с разрешающим входом первого шинного фор- мирователя.

3. Устройство по п. 1,отличающее

0 с я тем, что блок обмена информацией содержит приемопередатчик, два элемента И, два элемента ИЛИ, два элемента И-ИЛИ, четыре элемента НЕ, причем группа информационных входов-выходов приемопере5 датчика образует группу информационных входов-выходов блока, первая и вторая группы информационных выходов и входов приемопередатчика образуют соответственно группы информационных выходов и

0 входов блока, первый вход первого элемента ИЛИ, соединенный с входом первого элемента НЕ, первый вход первого элемента И, соединенный с первыми входами первого и второго элементов И-ИЛИ, выход второго

5 элемента И образуют группу кодовых входов-выходов блока, группа управляющих входов приемопередатчика, вход второго элемента НЕ, соединенный с вторым входом вторго элемента И-ИЛИ, вход второго

0 элемента ИЛИ образуют группу кодовых входов блока, группа входов второго элемента ИЛИ образует вторую группу адресных входов блока, второй вход первого элемента И-ИЛИ и третий вход второго эле5 мента И-ИЛИ образуют первую группу адресных входов блока, при этом выход первого элемента НЕ соединен с вторым входом первого элемента И, выход которого соединен с вторым входом первого элемен0 та ИЛИ, выход которого соединен с входом третьего элемента НЕ, выход которого соединен с третьим входом первого элемента И-ИЛИ, четвертый вход которого соединен с выходом второго элемента НЕ и с четвер5 тым входом второго элемента И-ИЛИ, выход которого соединен с первым адресным входом приемопередатчика и с первым входом второго элемента И, второй вход которого соединен с выходом четвертого элемента НЕ, вход которого соединен с выходом первого элемента И-ИЛИ и с вторым адресным входом приемопередатчика, разрешающий вход которого соединен с выходом второго элемента ИЛИ.

4.Устройство по п.1,отличающее с я тем, что блок преобразования формата содержит регистр, буферный регистр, дешифратор, сумматор по модулю два, элемент И, причем группа информационных входов сумматора по модулю два соединена с группой информационных входов регистра и образует группу информационных входов блока, первый информационный вход регистра является информационным входом блока, группа выходов буферного регистра соединена с группой информационных входов дешифратора и образует группу информационных выходов блока, информационный выход регистра является информационным выходом блока, первый вход элемента И является синхровходом блока, второй вход элемента И, соединенный с разрешающим входом регистра, вход сдвига регистра, установочный вход и вход записи буферного регистра, выход дешифратора образуют группу кодовых входов-выходов блока, при этом выход сумматора по модулю два соединен с вторым информационным входом регистра, группа информаци- онных выходов которого соединена с группой информационных входов буферного регистра.

5.Устройство по п.-1, о т л и ч а ю щ е е- с я тем, что блок управления содержит регистр, счетчик, дешифратор, четыре триггера, два элемента И, два элемента ИЛИ, два элемента И-ИЛИ, причем первый вход первого элемента И является адресным входом блока, вход сдвига регистра, соединенный с синхровходами первого, второго-триггеров, вход записи регистра, соединенный с первым входом первого элемента ИЛИ, с входами сброса первого, второго, третьего триггеров, первый вход второго элемента И, второй вход первого элемента И, соединенный с вторым входом второго элемента И, образуют группу входов логического условия блока, третий вход второго элемента И, первый, второй выходы регистра, первый вход элемента И-ИЛИ, выход первого элемента И-ИЛИ, соединенный с первым входом второго элемента И-ИЛИ, выход дешифратора, соединенный с вторым входом первого элемента ИЛИ, с входом сброса четвертого триггера, выход второго триггера, соединенный с синхровходом четвертого триггера, единичный выход третьего триггера, соединенный с вторыми входами первого и второго элементов И-ИЛИ образуют группу входов-выходов логического условия блока, при этом выходы первого и второго элементов И соединены соответственно с первым и вторым входами второго элемента ИЛИ, выход которого соединен с информационным входом первого триггера,

выход которого соединен с информационным входом второго триггера, выход четвертого триггера соединен с информационным входом третьего триггера, синхровход которого соединен с третьим выходом регистра,

четвертый выход которого соединен с третьими входами первого и второго элементов И-ИЛИ, четвертые входы которых соединены с нулевым выходом третьего триггера, информационный вход дешифратора соединен с выходом счетчика, счетный вход и установочный вход которого соединены соответственно с выходом второго элемента И-ИЛИ и с выходом первого элемента ИЛИ, информационный вход четвертого

триггера подключен к шине единичного потенциала устройства.

, Jto-irt

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для сопряжения магистрали ЭВМ с периферийными устройствами | 1990 |

|

SU1751775A1 |

| Устройство для сопряжения ЭВМ с абонентом | 1990 |

|

SU1702380A1 |

| УСТРОЙСТВО ДЛЯ СОПРЯЖЕНИЯ ЭВМ С ВНЕШНИМ АБОНЕНТОМ | 1992 |

|

RU2084952C1 |

| Устройство для сопряжения ЭВМ с внешним устройством | 1986 |

|

SU1377864A1 |

| Устройство для сопряжения ЭВМ с общей магистралью | 1990 |

|

SU1728867A1 |

| Устройство для сопряжения вычислительной машины с линиями связи | 1985 |

|

SU1262512A1 |

| Устройство для объема информацией между ЭВМ и периферийными устройствами | 1989 |

|

SU1679497A1 |

| Устройство для сопряжения каналов ЭВМ с периферийными устройствами | 1990 |

|

SU1732348A1 |

| Устройство для сопряжения двух электронных вычислительных машин | 1984 |

|

SU1251093A1 |

| Устройство для сопряжения источника информации с ЭВМ | 1986 |

|

SU1381528A1 |

Изобретение относится к вычислительной технике, в частности к системам обработки информации на базе ЭВМ единой системы, к которым подключение персональных ЭВМ типа ЕС-1840 может быть осуществлено через локальные (дистанционные) устройства дисплейных комплексов. Цель изобретения - повышение быстродействия и сокращение аппаратурных затрат Устройство содержит блок связи с первой ЭВМ, блок связи с второй ЭВМ, блок управления, блок обмена информацией, блок преобразования формата, блок идентификации кодов, блок прямого доступа к памяти, блок прерывания. 4 з.п. ф-лы, 10 ил.

Фиг. 2

$

CS

l

735

01 со

CO

о -j

Фиг. 6

ФигЛ

ReSE Т

W

US

Фиг. 8

Фиг. в

I

lall

1зг|

сЗ5

t

Јi

О)

«о

к

«М

& |

I

a Ч

8

|tj

r

a

a i

«j i

u 4i

13

X

;

| Релейно-контакторное устройство для автоматического управления насосами водопонизительных скважин | 1960 |

|

SU135127A1 |

| Винтовой компрессор | 1979 |

|

SU792001A1 |

| Насос | 1917 |

|

SU13A1 |

Авторы

Даты

1991-09-30—Публикация

1989-08-14—Подача