Изобретение относится к области радиотехники и связи и может быть использовано в качестве устройства усиления аналоговых сигналов, в структуре аналоговых микросхем различного функционального назначения (например, в прецизионных инструментальных и решающих усилителях, компараторах и т.п.).

Известны схемы операционных усилителей (ОУ) на основе входных комплементарных дифференциальных каскадов (двух параллельно включенных классических дифференциальных усилителей с токостабилизирующими двухполюсниками в эмиттерных цепях входных транзисторов - так называемых «dual input stage») и промежуточных каскадов, выполненных на токовых зеркалах. ОУ с такой архитектурой стали основой построения многих современных аналоговых микросхем [1-14], в т.ч. ОУ с опцией rail-to-rail, имеющих максимальную амплитуду выходного напряжения, близкую к напряжению питания.

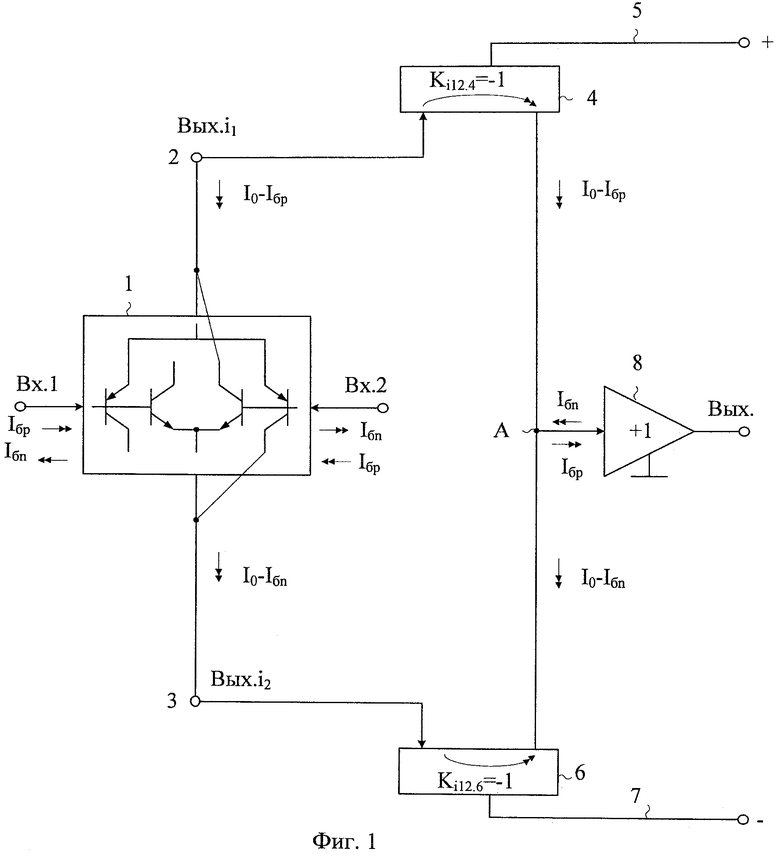

Ближайшим прототипом (фиг.1) заявляемого устройства является прецизионный операционный усилитель, описанный в патенте US №5374897, fig.3. Архитектура ОУ-прототипа также используется во многих других патентах ведущих микроэлектронных фирм [1-14]. ОУ фиг.1 содержит входной комплементарный дифференциальный каскад 1 на n-р-n и р-n-р транзисторах с первым 2 и вторым 3 токовыми выходами, первое 4 токовое зеркало, согласованное с первой 5 шиной источника питания, вход которого соединен с первым 2 токовым выходом входного дифференциального каскада 1, второе 6 токовое зеркало, согласованное со второй 7 шиной источника питания, вход которого соединен со вторым токовым выходом входного дифференциального каскада 1, и комплементарный буферный усилитель 8.

Существенный недостаток известного ДУ фиг.1 состоит в том, что он имеет повышенное значение систематической составляющей напряжения смещения нуля (Uсм), зависящей от свойств его архитектуры.

Основная задача предлагаемого изобретения состоит в уменьшении абсолютного значения Uсм и его температурного и/или радиационного дрейфа.

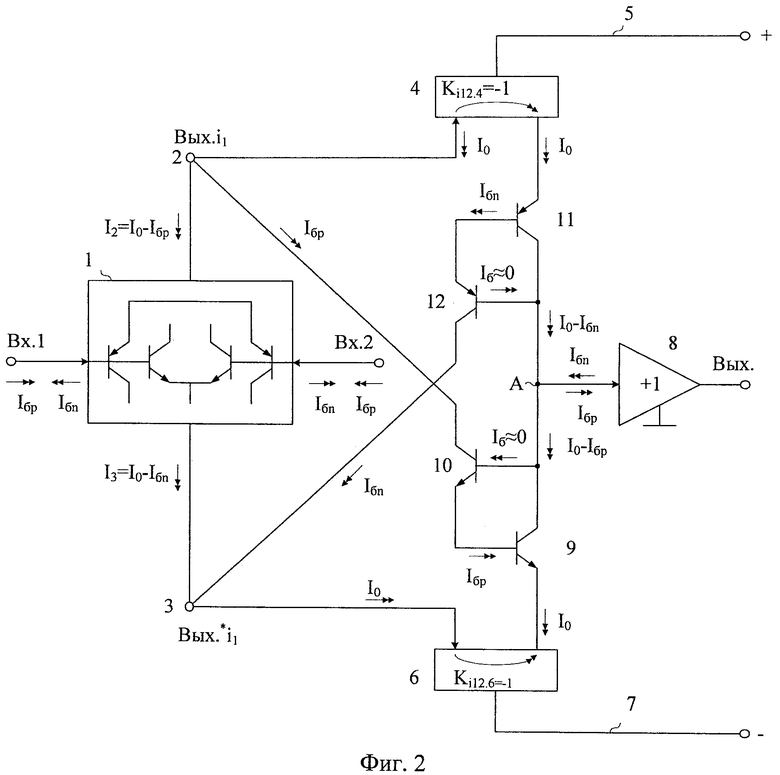

Поставленная задача достигается тем, что в прецизионном операционном усилителе (фиг.1), содержащем входной комплементарный дифференциальный каскад 1 на n-р-n и р-n-р транзисторах с первым 2 и вторым 3 токовыми выходами, первое 4 токовое зеркало, согласованное с первой 5 шиной источника питания, вход которого соединен с первым 2 токовым выходом входного дифференциального каскада 1, второе 6 токовое зеркало, согласованное со второй 7 шиной источника питания, вход которого соединен со вторым 3 токовым выходом входного дифференциального каскада 1, комплементарный буферный усилитель 8, предусмотрены новые элементы и связи - первый 9 и второй 10 выходные транзисторы n-р-n типа, а также первый 11 и второй 12 выходные транзисторы р-n-р типа, коллектор первого 9 выходного транзистора n-р-n типа и коллектор первого 11 выходного транзистора р-n-р типа объединены и подключены ко входу комплементарного буферного усилителя 8, коллектор первого 9 выходного транзистора n-р-n типа соединен с базой второго 10 выходного транзистора n-р-n типа, эмиттер второго 10 выходного транзистора n-р-n типа соединен с базой первого 9 выходного транзистора n-р-n типа, коллектор второго 10 выходного транзистора n-р-n типа соединен со входом первого 4 токового зеркала, а эмиттер первого 9 выходного транзистора n-р-n типа соединен с выходом второго 6 токового зеркала, коллектор первого 11 выходного транзистора р-n-р типа соединен с базой второго 12 выходного транзистора р-n-р типа, эмиттер второго 12 выходного транзистора р-n-р типа соединен с базой первого 11 выходного транзистора р-n-р типа, коллектор второго 12 выходного транзистора р-n-р типа соединен со входом второго 6 токового зеркала, а эмиттер первого 11 выходного транзистора р-n-р типа соединен с выходом первого 4 токового зеркала.

Схема операционного усилителя-прототипа представлена на фиг.1.

На фиг.2 показана схема заявляемого ОУ в соответствии с п.1 формулы изобретения.

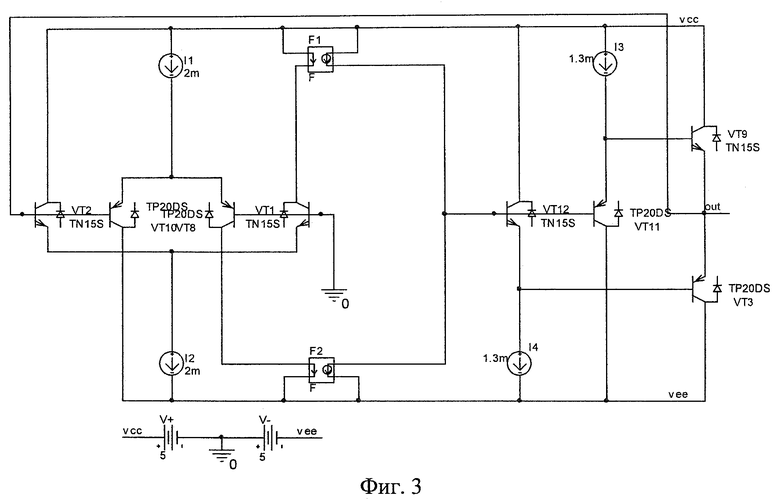

На фиг.3 показана схема дифференциального усилителя-прототипа (фиг.1) в среде компьютерного моделирования РSpice на моделях интегральных транзисторов ФГУП НПП «Пульсар» с буферным усилителем 8 на базе «бриллиантовых» составных транзисторов. Для данного ОУ напряжение смещения нуля Uсм=814,9 мкВ при коэффициентах усиления по току базы βn=25, βр=43 и статических токах входных транзисторов буферного усилителя I3=I4=1,3 мА.

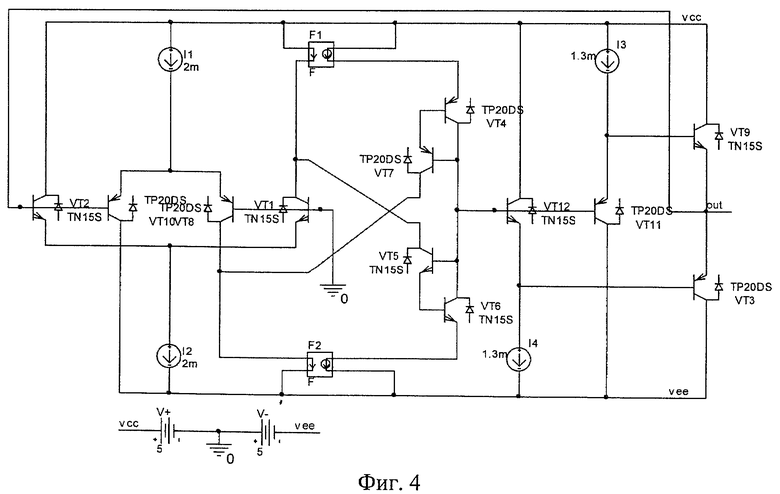

На фиг.4 показана схема заявляемого ОУ в среде компьютерного моделирования PSpice на моделях интегральных транзисторов ФГУП НПП «Пульсар». Для данного ОУ при токах I3=I4=1,3 мА и βn=25, βр=43 напряжение смещения нуля Uсм=-1,6 мкВ.

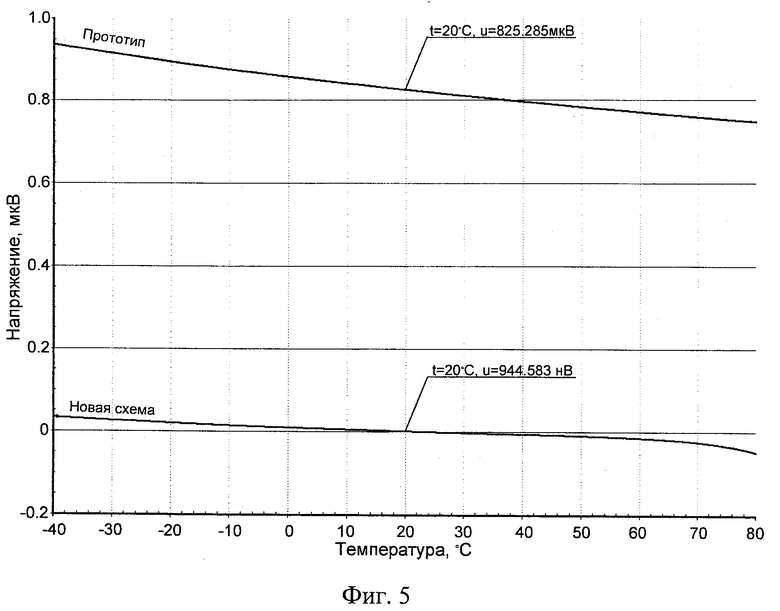

На фиг.5 приведены температурные зависимости напряжения смещения нуля сравниваемых схем ОУ фиг.3 и фиг.4 при βn=25, βр=43.

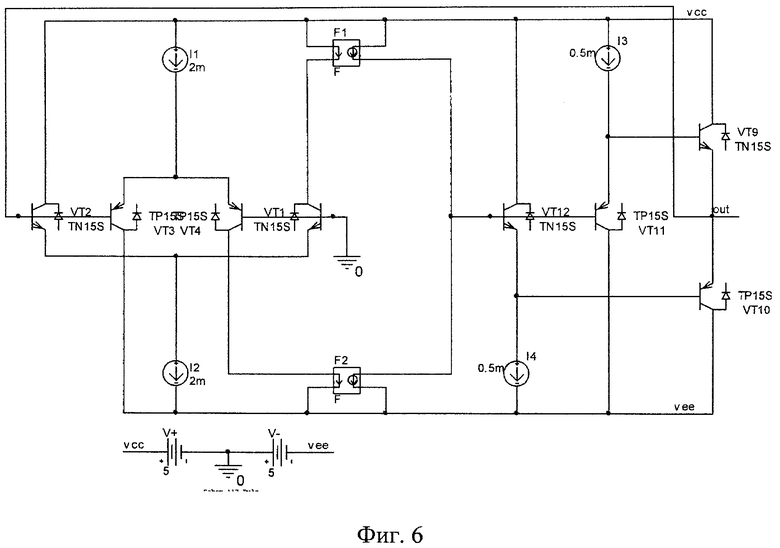

На фиг.6 представлена схема классического ОУ в среде компьютерного моделирования PSpice на моделях интегральных транзисторов ФГУП НПП «Пульсар». Для данного ОУ Ucм=-192,2 мкВ при статических токах входных транзисторов буферного усилителя I3=I4=0,5 мА.

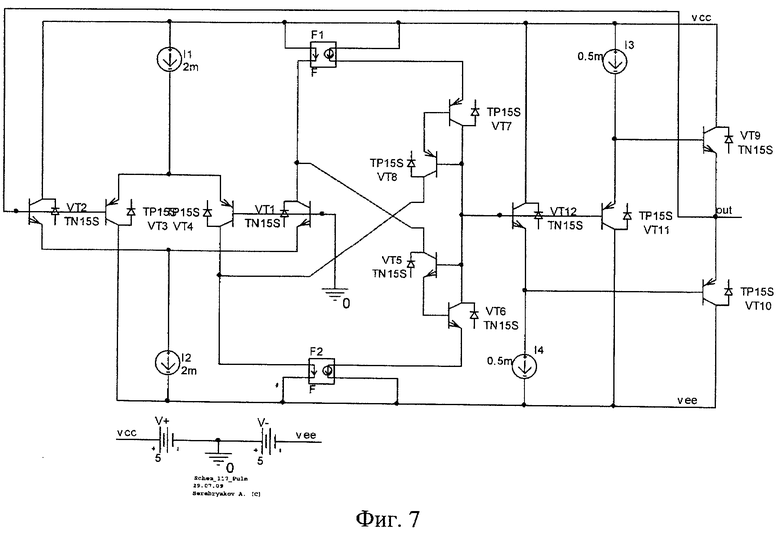

На фиг.7 показана схема предлагаемого ОУ в среде Pspice на моделях интегральных транзисторов ФГУП НПП «Пульсар». В этой схеме Ucм=4,5 мкВ при статических токах входных транзисторов БУ I3=I4=0,5 мА.

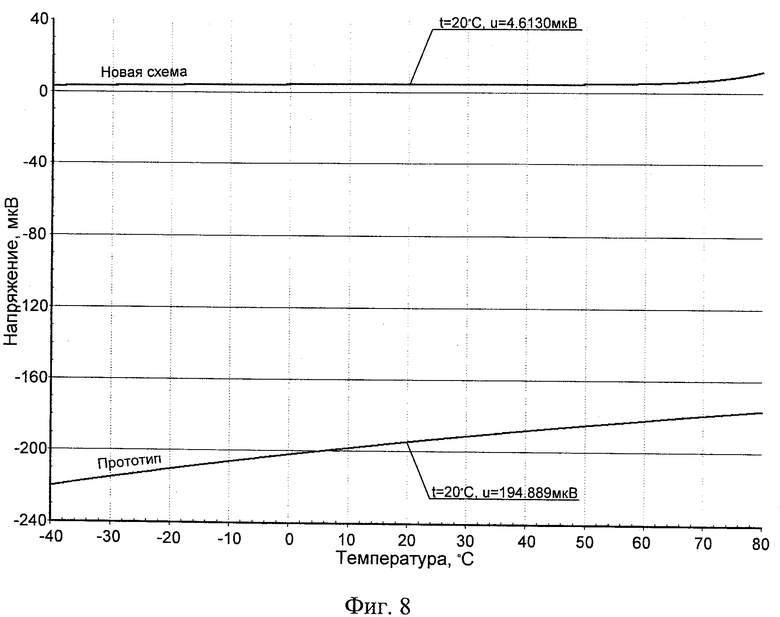

На фиг.8 показаны температурные зависимости напряжения смещения нуля сравниваемых схем ОУ при I3=I4=0,5 мА.

Прецизионный операционный усилитель фиг.2 содержит входной комплементарный дифференциальный каскад 1 на n-р-n и р-n-р транзисторах с первым 2 и вторым 3 токовыми выходами, первое 4 токовое зеркало, согласованное с первой 5 шиной источника питания, вход которого соединен с первым 2 токовым выходом входного дифференциального каскада 1, второе 6 токовое зеркало, согласованное со второй 7 шиной источника питания, вход которого соединен со вторым 3 токовым выходом входного дифференциального каскада 1, комплементарный буферный усилитель 8. Первый 9 и второй 10 выходные транзисторы n-р-n типа, а также первый 11 и второй 12 выходные транзисторы р-n-р типа, коллектор первого 9 выходного транзистора n-р-n типа и коллектор первого 11 выходного транзистора р-n-р типа объединены и подключены ко входу комплементарного буферного усилителя 8, коллектор первого 9 выходного транзистора n-р-n типа соединен с базой второго 10 выходного транзистора n-р-n типа, эмиттер второго 10 выходного транзистора n-р-n типа соединен с базой первого 9 выходного транзистора n-р-n типа, коллектор второго 10 выходного транзистора n-р-n типа соединен со входом первого 4 токового зеркала, а эмиттер первого 9 выходного транзистора n-р-n типа соединен с выходом второго 6 токового зеркала, коллектор первого 11 выходного транзистора р-n-р типа соединен с базой второго 12 выходного транзистора р-n-р типа, эмиттер второго 12 выходного транзистора р-n-р типа соединен с базой первого 11 выходного транзистора р-n-р типа, коллектор второго 12 выходного транзистора р-n-р типа соединен со входом второго 6 токового зеркала, а эмиттер первого 11 выходного транзистора р-n-р типа соединен с выходом первого 4 токового зеркала.

На фиг.2 в соответствии с п.2 формулы изобретения комплементарный буферный усилитель 8 имеет две противоположно направленные составляющие статического входного тока, приблизительно равные соответствующим токам базы первого 9 n-р-n и первого 11 р-n-р выходных транзисторов. Этот тип выходных каскадов широко применяется в ОУ рассматриваемого класса (см., например, патенты US 5515005, fig.2, 6268769, fig.3, JP 7050528), а их входной ток имеет две противоположно направленные составляющие, каждая из которых обусловлена токами базы n-р-n (Iбр) и р-n-р (Iбn) транзисторов. Примеры построения таких БУ приведены на фиг.3, фиг.4.

Рассмотрим факторы, определяющие систематическую составляющую напряжения смещения нуля Uсм в схеме фиг.2 (т.е. зависящие от схемотехники ОУ) с комплементарным буферным усилителем 8 (фиг.3, фиг.4).

Если учесть, что выходные токи входного комплементарного дифференциального каскада 1 удовлетворяют условиям:

то можно найти выходные токи токовых зеркал 4 (I4) и 6 (I6), в качестве которых рекомендуется использовать классические токовые зеркала Вильсона с коэффициентом передачи по току Кi12=-1:

где Iбi=Iэ.i/βi - ток базы n-p-n (Iбр) или р-n-р (Iбn) транзисторов схемы ОУ при их эмиттерном токе Iэ.i=I0;

βi - коэффициент усиления по току базы i-го транзистора.

Учитывая, что токи базы транзисторов 10 и 12 малы в сравнении с токами базы транзисторов 9 и 11, можно найти коллекторные токи транзисторов 9 и 11 при входном токе комплементарного буферного усилителя IБУ=Iбр-Iбn:

Таким образом, в схеме фиг.2 в высокоимпедансном узле «А» обеспечивается взаимная компенсация токов, обусловленных ошибкой установления статического режима входного комплементарного каскада 1 и выходного комплементарного буферного усилителя, связанной с неидентичностью β применяемых р-n-р и n-р-n транзисторов. Поэтому систематическая составляющая напряжения смещения нуля в схеме ОУ фиг.2 близка к нулю (Uсм≈0).

Результаты компьютерного моделирования известной (фиг.3) и предлагаемой (фиг.4) схем ОУ, представленные на фиг.5, показывают, что схема фиг.4 имеет меньшее значение Uсм=-1,6 мкВ и его температурный дрейф при статических токах входных транзисторов буферного усилителя, равных I3=I4=1,3 мА.

Исследования в среде PSpice схем ОУ фиг.6 и фиг.7, которые в отличии от фиг.3, фиг.4 используют другой статический режим входных транзисторов комплементарного буферного усилителя 8, также показывают (фиг.8) преимущества заявляемой схемы ОУ по величине Uсм и его дрейфа.

Таким образом, заявляемое устройство обладает существенными преимуществами в сравнении с прототипом по величине статической ошибки усиления сигналов постоянного тока.

БИБЛИОГРАФИЧЕСКИЙ СПИСОК

1. Патент США №5512859, fig.1.

2. Патент США №5515005, fig.1.

3. Патентная заявка Японии JP 2008/235963.

4. Патент США №4783637, fig.1.

5. Патент Японии JP 7050528.

6. Патент США №5374897, fig.3.

7. Патент США №6268769.

8. Патент США №3968471.

9. Патент РФ №611288.

10. Патентная заявка США №2006/0125522, fig.1B.

11. Патент США №5291149, fig.3.

12. Патент США №5225791, fig.2.

13. Патент США №6504419, fig.2.

14. Патент США №5714906, fig.15.

| название | год | авторы | номер документа |

|---|---|---|---|

| ПРЕЦИЗИОННЫЙ ОПЕРАЦИОННЫЙ УСИЛИТЕЛЬ | 2011 |

|

RU2455757C1 |

| ПРЕЦИЗИОННЫЙ ОПЕРАЦИОННЫЙ УСИЛИТЕЛЬ | 2011 |

|

RU2449466C1 |

| ПРЕЦИЗИОННЫЙ ОПЕРАЦИОННЫЙ УСИЛИТЕЛЬ | 2011 |

|

RU2444119C1 |

| ПРЕЦИЗИОННЫЙ ОПЕРАЦИОННЫЙ УСИЛИТЕЛЬ | 2011 |

|

RU2450425C1 |

| КОМПЛЕМЕНТАРНЫЙ ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ | 2009 |

|

RU2412530C1 |

| ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ С МАЛЫМ НАПРЯЖЕНИЕМ СМЕЩЕНИЯ НУЛЯ | 2010 |

|

RU2421889C1 |

| КОМПЛЕМЕНТАРНЫЙ ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ | 2009 |

|

RU2411644C1 |

| ПРЕЦИЗИОННЫЙ ОПЕРАЦИОННЫЙ УСИЛИТЕЛЬ | 2011 |

|

RU2449465C1 |

| ОПЕРАЦИОННЫЙ УСИЛИТЕЛЬ С МАЛЫМ НАПРЯЖЕНИЕМ СМЕЩЕНИЯ НУЛЯ | 2011 |

|

RU2462812C1 |

| КАСКОДНЫЙ ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ С МАЛЫМ НАПРЯЖЕНИЕМ СМЕЩЕНИЯ НУЛЯ | 2009 |

|

RU2402152C1 |

Изобретение относится к области радиотехники и связи и может быть использовано в качестве устройства усиления аналоговых сигналов, в структуре аналоговых микросхем различного функционального назначения (например, в прецизионных интегральных и решающих усилителях, компараторах и т.п.). Технический результат заключается в уменьшении абсолютного значения напряжения смещения нуля и его температурного и/или радиационного дрейфа. Прецизионный операционный усилитель содержит входной комплементарный дифференциальный каскад на n-p-n и р-n-р транзисторах, первое и второе токовые зеркала, комплементарный буферный усилитель, первый и второй выходные тразнисторы n-p-n типа, первый и второй выходные транзисторы p-n-р типа. 1 з.п. ф-лы, 8 ил.

1. Прецизионный операционный усилитель, содержащий входной комплементарный дифференциальный каскад (1) на n-p-n и р-n-р транзисторах с первым (2) и вторым (3) токовыми выходами, первое (4) токовое зеркало, согласованное с первой (5) шиной источника питания, вход которого соединен с первым (2) токовым выходом входного дифференциального каскада (1), второе (6) токовое зеркало, согласованное со второй (7) шиной источника питания, вход которого соединен со вторым (3) токовым выходом входного дифференциального каскада (1), комплементарный буферный усилитель (8), отличающийся тем, что в схему введены первый (9) и второй (10) выходные транзисторы n-p-n типа, а также первый (11) и второй (12) выходные транзисторы p-n-р типа, коллектор первого (9) выходного транзистора n-p-n типа и коллектор первого (11) выходного транзистора p-n-р типа объединены и подключены ко входу комплементарного буферного усилителя (8), коллектор первого (9) выходного транзистора n-p-n типа соединен с базой второго (10) выходного транзистора n-p-n типа, эмиттер второго (10) выходного транзистора n-p-n типа соединен с базой первого (9) выходного транзистора n-p-n типа, коллектор второго (10) выходного транзистора n-р-n типа соединен со входом первого (4) токового зеркала, а эмиттер первого (9) выходного транзистора n-p-n типа соединен с выходом второго (6) токового зеркала, коллектор первого (11) выходного транзистора р-n-р типа соединен с базой второго (12) выходного транзистора p-n-р типа, эмиттер второго (12) выходного транзистора p-n-р типа соединен с базой первого (11) выходного транзистора p-n-р типа, коллектор второго (12) выходного транзистора p-n-р типа соединен со входом второго (6) токового зеркала, а эмиттер первого (11) выходного транзистора p-n-р типа соединен с выходом первого (4) токового зеркала.

2. Прецизионный операционный усилитель по п.1, отличающийся тем, что комплементарный буферный усилитель (8) имеет две противоположно направленные составляющие статического входного тока, приблизительно равные соответствующим токам базы первого (9) n-p-n и первого (11) р-n-р выходных транзисторов.

| US 5374897 А, 20.12.1994 | |||

| US 5399991 А, 21.03.1995 | |||

| ПРЕЦИЗИОННЫЙ ОПЕРАЦИОННЫЙ УСИЛИТЕЛЬ С МАЛЫМ НАПРЯЖЕНИЕМ СМЕЩЕНИЯ НУЛЯ | 2009 |

|

RU2411637C1 |

| ПРЕЦИЗИОННЫЙ ОПЕРАЦИОННЫЙ УСИЛИТЕЛЬ | 2008 |

|

RU2368064C1 |

Авторы

Даты

2012-05-10—Публикация

2011-03-17—Подача