Изобретение относится к области радиотехники и связи и может быть использовано в качестве устройства усиления аналоговых и высокочастотных сигналов, в структуре аналоговых интерфейсов различного функционального назначения (например, драйверах линий связи).

Известны схемы классических дифференциальных операционных усилителей (ДОУ) [1-14] с отрицательной обратной связью по синфазному сигналу, которые стали основой многих серийных аналоговых микросхем первого и второго поколения.

В последние годы ДОУ данного класса стали снова активно применяться в структуре СВЧ-устройств с низкоомным дифференциальным выходом [1, 2, 3], реализованных на базе новейших SiGe-технологий. Это связано с возможностью построения на их основе активных RC-фильтров гигагерцового диапазона для современных и перспективных систем связи. В значительной степени этому способствует простота установления статического режима ДОУ при низковольтном питании (1,2÷2,1)В, которое характерно для SiGe транзисторов с предельными частотами 120÷160 ГГц.

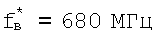

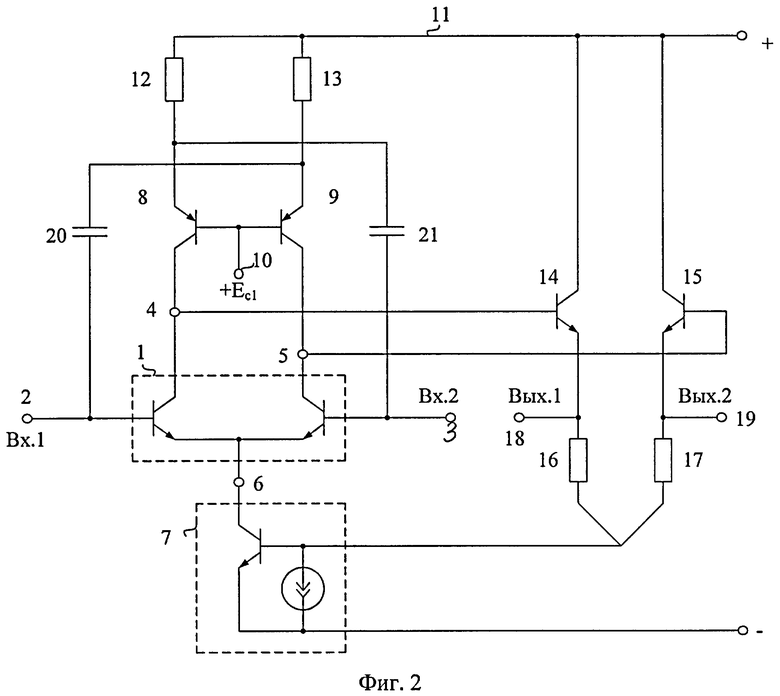

Ближайшим прототипом (фиг.1) заявляемого устройства является широкополосный операционный усилитель с дифференциальным выходом (ШОУ), описанный в статье «Схемотехника СВЧ операционных усилителей для аналоговых интерфейсов с глубокой обратной связью» (А.С.Будяков, Н.Н.Прокопенко, К.Schmalz, С.Scheytt, P.Ostrovskyy // Проблемы разработки перспективных микро- и наноэлектронных систем - 2008. Сборник научных трудов III Всероссийской научно-технической конференции / под общ. ред. Академика РАН А.Л.Стемпковского. - М.: Институт проблем проектирования в микроэлектронике РАН, 2008. - С.301-306, рис.4), содержащий входной дифференциальный каскад 1, имеющий первый 2 и второй 3 входы, первый 4 и второй 5 токовые выходы, и токовый вход 6 в общей эмиттерной цепи, управляемый источник опорного тока 7, выход которого связан с токовым входом 6 в общей эмиттерной цепи, первый 8 и второй 9 вспомогательные транзисторы, базы которых подключены к источнику напряжения смещения 10, коллектор первого 8 вспомогательного транзистора соединен с первым 4 токовым выходом входного дифференциального каскада, а эмиттер подключен к шине источника питания 11 через первый токостабилизирующий двухполюсник 12, коллектор второго 9 вспомогательного транзистора подключен ко второму 5 токовому выходу входного дифференциального каскада 1, а эмиттер подключен к шине источника питания 11 через второй 13 токостабилизирующий двухполюсник, первый 14 и второй 15 выходные транзисторы, первый 16 и второй 17 резисторы нагрузки, соединенные с эмиттерами соответствующих первого 14 и второго 15 выходных транзисторов и первым 18 и вторым 19 выходами устройства, причем общая точка первого 16 и второго 17 резисторов нагрузки связана со входом управляемого источника опорного тока 7, база первого 14 выходного транзистора соединена с первым 4 токовым выходом входного дифференциального каскада 1, а база второго 15 выходного транзистора соединена со вторым 5 токовым входом дифференциального каскада.

Существенный недостаток известного ШОУ состоит в том, что он имеет недостаточно высокие значения верхней граничной частоты fв, что ограничивает предельный диапазон частот ШОУ при работе в схемах с глубокой отрицательной обратной связью.

Основная цель предлагаемого изобретения состоит в расширении диапазона рабочих частот ШОУ и электронных устройств на его основе.

Поставленная цель достигается тем, что в операционном усилителе фиг.1, содержащем входной дифференциальный каскад 1, имеющий первый 2 и второй 3 входы, первый 4 и второй 5 токовые выходы, и токовый вход 6 в общей эмиттерной цепи, управляемый источник опорного тока 7, выход которого связан с токовым входом 6 в общей эмиттерной цепи, первый 8 и второй 9 вспомогательные транзисторы, базы которых подключены к источнику напряжения смещения 10, коллектор первого 8 вспомогательного транзистора соединен с первым 4 токовым выходом входного дифференциального каскада, а эмиттер подключен к шине источника питания 11 через первый токостабилизирующий двухполюсник 12, коллектор второго 9 вспомогательного транзистора подключен ко второму 5 токовому выходу входного дифференциального каскада 1, а эмиттер подключен к шине источника питания 11 через второй 13 токостабилизирующий двухполюсник, первый 14 и второй 15 выходные транзисторы, первый 16 и второй 17 резисторы нагрузки, соединенные с эмиттерами соответствующих первого 14 и второго 15 выходных транзисторов и первым 18 и вторым 19 выходами устройства, причем общая точка первого 16 и второго 17 резисторов нагрузки связана со входом управляемого источника опорного тока 7, база первого 14 выходного транзистора соединена с первым 4 токовым выходом входного дифференциального каскада 1, а база второго 15 выходного транзистора соединена со вторым 5 токовым входом дифференциального каскада, предусмотрены новые элементы и связи - первый 2 вход входного дифференциального каскада 1 связан с эмиттером второго 9 вспомогательного транзистора через первый 20 дополнительный конденсатор, а второй 3 вход входного дифференциального каскада 1 связан с эмиттером первого 8 вспомогательного транзистора через второй 21 дополнительный конденсатор.

Схема заявляемого устройства, соответствующего п.1 формулы изобретения, показана на чертеже фиг.2.

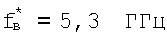

На чертеже фиг.3 показана схема заявляемого устройства в соответствии с п.2 формулы изобретения.

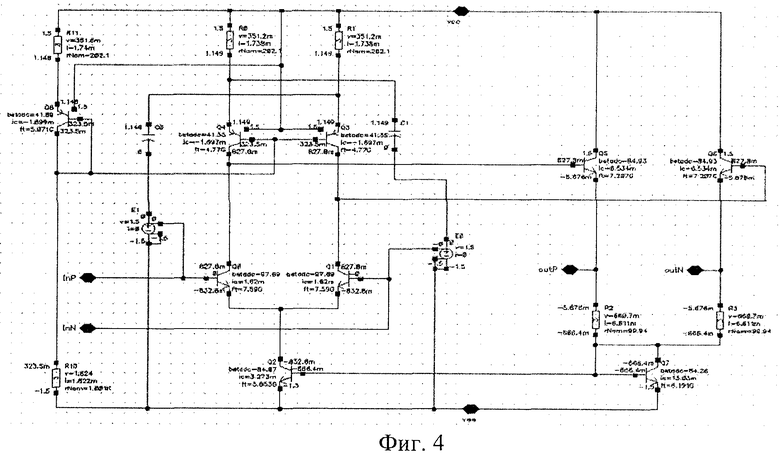

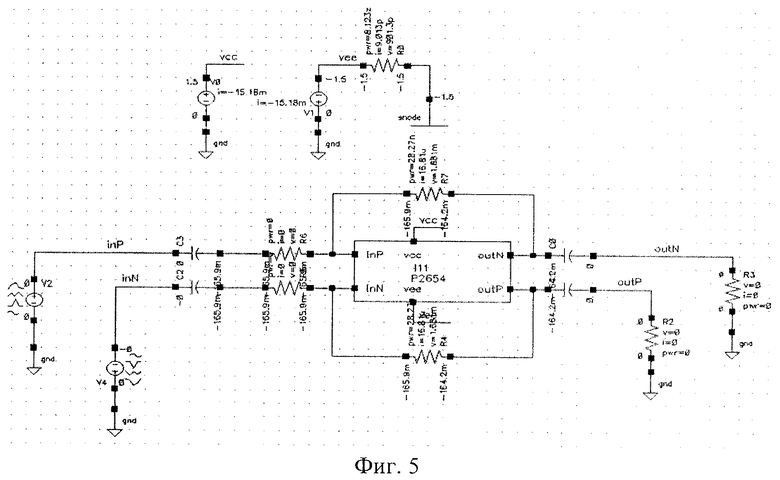

На чертеже фиг.4 показана схема заявляемого ШОУ в среде компьютерного моделирования Cadance на моделях интегральных транзисторов ФГУП НПП «Пульсар», а на чертеже фиг.5 - схема включения ШОУ фиг.2 с коэффициентом усиления Кп=-1 (резистор R0 имитирует сопротивление контакта на подложку, резисторы обратной связи - все по 100 Ом).

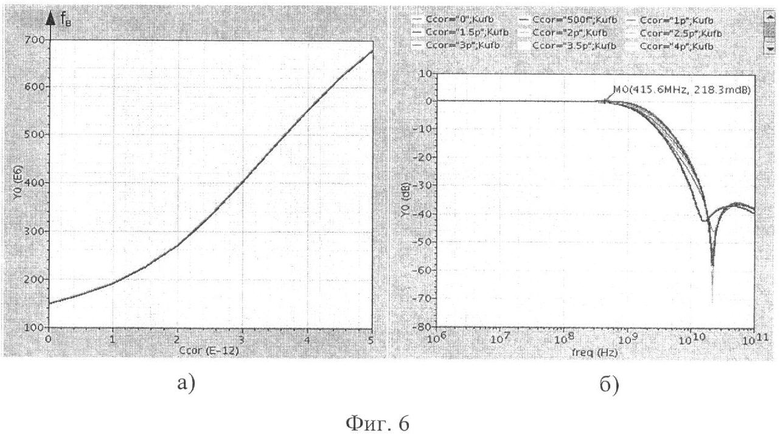

На чертеже фиг.6а показан график изменения верхней граничной частоты fв по уровню (-3 дБ), а на чертеже фиг.6б - ЛАЧХ дифференциального коэффициента усиления для ОУ фиг.4 (включение Кп=-1, фиг.5) при вариации емкостей коррекции 20 и 21 C20=C21=Ccor=0…5 пФ с шагом 0,5 пФ.

Широкополосный операционный усилитель фиг.2 содержит входной дифференциальный каскад 1, имеющий первый 2 и второй 3 входы, первый 4 и второй 5 токовые выходы, и токовый вход 6 в общей эмиттерной цепи, управляемый источник опорного тока 7, выход которого связан с токовым входом 6 в общей эмиттерной цепи, первый 8 и второй 9 вспомогательные транзисторы, базы которых подключены к источнику напряжения смещения 10, коллектор первого 8 вспомогательного транзистора соединен с первым 4 токовым выходом входного дифференциального каскада, а эмиттер подключен к шине источника питания 11 через первый токостабилизирующий двухполюсник 12, коллектор второго 9 вспомогательного транзистора подключен ко второму 5 токовому выходу входного дифференциального каскада 1, а эмиттер подключен к шине источника питания 11 через второй 13 токостабилизирующий двухполюсник, первый 14 и второй 15 выходные транзисторы, первый 16 и второй 17 резисторы нагрузки, соединенные с эмиттерами соответствующих первого 14 и второго 15 выходных транзисторов и первым 18 и вторым 19 выходами устройства, причем общая точка первого 16 и второго 17 резисторов нагрузки связана со входом управляемого источника опорного тока 7, база первого 14 выходного транзистора соединена с первым 4 токовым выходом входного дифференциального каскада 1, а база второго 15 выходного транзистора соединена со вторым 5 токовым входом дифференциального каскада. Первый 2 вход входного дифференциального каскада 1 связан с эмиттером второго 9 вспомогательного транзистора через первый 20 дополнительный конденсатор, а второй 3 вход входного дифференциального каскада 1 связан с эмиттером первого 8 вспомогательного транзистора через второй 21 дополнительный конденсатор.

В широкополосном операционном усилителе, соответствующем п.2 формулы изобретения (фиг.3), первый вход 2 входного дифференциального каскада 1 связан с эмиттером второго 9 вспомогательного транзистора через последовательно соединенные первый 20 дополнительный конденсатор и первый 22 дополнительный буферный усилитель, а второй вход 3 входного дифференциального каскада 1 связан с эмиттером первого 8 вспомогательного транзистора через последовательно соединенные второй 21 дополнительный конденсатор и второй 23 дополнительный буферный усилитель.

На чертеже фиг.4 приведена модель ШОУ фиг.3 с дополнительными буферными усилителями, в которой емкости конденсаторов C20=C21 определяются параметром Ccor.

Рассмотрим работу ШОУ фиг.3.

Статический режим по току входных транзисторов предлагаемого ШОУ, например, в схеме включения фиг.5 устанавливается цепью отрицательной обратной связи по синфазному сигналу и двухполюсниками 12 и 13, а также источником напряжения смещения 10. При этом эмиттерные токи транзисторов 14 и 15 определяются входной цепью управляемого источника опорного тока 7.

В типовой схеме включения ОУ фиг.2, например в структуре драйвера линии связи (фиг.5), частотные свойства петли отрицательной обратной связи определяются амплитудно-частотной характеристикой входного каскада 1 и паразитными емкостями в цепи первого 4 и второго 5 выходов, зависящими от емкостей на подложку и емкостей коллектор-база транзисторов схемы. В ШОУ-прототипе это приводит к формированию достаточно небольших значений верхней граничной частоты fв<<fт, где fт - граничная частота усиления транзисторов [2-3].

В заявляемом устройстве с помощью конденсаторов 20 и 21 создается более высокочастотный (чем через транзисторы входного каскада 1) канал передачи сигнала со входов 2 и 3 к выходным узлам 4 и 5. Действительно, входной сигнал передается через элементы 22, 20 и 23, 21 на выходы 4 и 5 по более высокочастотным каналам - транзисторы 8 и 9, включенные по схеме с общей базой, характеризующейся большей широкополосностью, чем схема с общим эмиттером (каскад 1). В результате операционный усилитель становится более широкополосным.

Представленные на чертеже фиг.6 результаты компьютерного моделирования схемы фиг.4 на базе транзисторов ФГУП НПП «Пульсар» с граничными частотами 8-8,5 ГГц показывают, что полоса пропускания (fв) предлагаемого устройства повышается более чем в 4 раза (от fв=150 МГц до  ). При использовании SiGe полевых (8, 9) и биполярных (14, 15) транзисторов (модели IHP) выигрыш по

). При использовании SiGe полевых (8, 9) и биполярных (14, 15) транзисторов (модели IHP) выигрыш по  достигает 1,3-1,8 раза при

достигает 1,3-1,8 раза при  .

.

Следует отметить, что введение предлагаемых элементов частотной коррекции не ухудшает запас устойчивости ШОУ при одновременном повышении fв - выброс ЛАЧХ не превышает 0,2 дБ (фиг.6б).

Таким образом заявляемый усилитель обеспечивает в 4-5 раз большую полосу пропускания. Это весьма существенно для интерфейсных микросхем систем связи и телекоммуникаций.

БИБЛИОГРАФИЧЕСКИЙ СПИСОК

1. S.P.Voinigescu, Design Methodology and Applications of SiGe BiCMOS Cascode Opamps with up to 37-GHz Unity Gain Bandwidth [Text] / S.P.Voinigescu et al. // IEEE CSICS, Techn. Digest, Nov. 2005, pp.283-286.

2. Design of Bipolar Differential OpAmps with Unity Gain Bandwidth up to 23 GHz [Text] / A.Budyakov, K.Schmalz, N.N.Prokopenko, C.Scheytt, P.Ostrovskyy // Proceeding of the 4-th European Conference on Circuits and Systems for Communications - ECCSC′08 / Politehnica University, Bucharest, Romania: July 10-11, 2008. - pp.50-53.

3. Будяков A.C. Схемотехника СВЧ операционных усилителей для аналоговых интерфейсов с глубокой обратной связью [Текст] / А.С.Будяков, Н.Н.Прокопенко, К.Schmalz, С.Scheytt, P.Ostrovskyy // Проблемы разработки перспективных микро- и наноэлектронных систем - 2008. Сборник научных трудов III Всероссийской научно-технической конференции / под общ. ред. Академика РАН А.Л.Стемпковского. - М.: Институт проблем проектирования в микроэлектронике РАН, 2008. - С.301-306, рис.4.

4. Патент США №4.274.394, фиг.2.

5. Патент США №3.619.797.

6. Патент США №3.622.902.

7. Патент США №3.440.554.

8. Авт.св. СССР №299013.

9. Патент Англии №1.175.329, НЗТ.

10. Патент США №3.304.512.

11. Патент США №4.371.93.

12. Авт.св. СССР №421105.

13. Авт.св. СССР №764100.

14. Авт.св. СССР №669471.

| название | год | авторы | номер документа |

|---|---|---|---|

| ШИРОКОПОЛОСНЫЙ ДИФФЕРЕНЦИАЛЬНЫЙ ОПЕРАЦИОННЫЙ УСИЛИТЕЛЬ | 2016 |

|

RU2641445C1 |

| ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ С РАСШИРЕННЫМ ДИАПАЗОНОМ АКТИВНОЙ РАБОТЫ | 2007 |

|

RU2333593C1 |

| ДИФФЕРЕНЦИАЛЬНЫЙ ОПЕРАЦИОННЫЙ УСИЛИТЕЛЬ С ПАРАФАЗНЫМ ВЫХОДОМ | 2011 |

|

RU2441315C1 |

| ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ С РАСШИРЕННЫМ ДИАПАЗОНОМ АКТИВНОЙ РАБОТЫ | 2007 |

|

RU2331971C1 |

| ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ С РАСШИРЕННЫМ ЧАСТОТНЫМ ДИАПАЗОНОМ | 2014 |

|

RU2568316C1 |

| ИЗБИРАТЕЛЬНЫЙ УСИЛИТЕЛЬ | 2012 |

|

RU2475947C1 |

| ДИФФЕРЕНЦИАЛЬНЫЙ ОПЕРАЦИОННЫЙ УСИЛИТЕЛЬ | 2009 |

|

RU2412537C1 |

| ИЗБИРАТЕЛЬНЫЙ УСИЛИТЕЛЬ | 2011 |

|

RU2467469C1 |

| ШИРОКОПОЛОСНЫЙ ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ С ПАРАФАЗНЫМ ВЫХОДОМ | 2012 |

|

RU2479113C1 |

| ДВУХТАКТНЫЙ ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ | 2006 |

|

RU2319289C1 |

Изобретение относится к области радиотехники и связи и может быть использовано в качестве устройства усиления аналоговых сигналов, в структуре аналоговых микросхем различного функционального назначения (например, операционных усилителях (ОУ), компараторах). Технический результат: расширение диапазона рабочих частот. Широкополосный операционный усилитель (ШОУ) с дифференциальным выходом содержит входной дифференциальный каскад (ДК) (1), имеющий первый (2) и второй (3) входы, первый (4) и второй (5) токовые выходы, и токовый вход (6) в общей эмиттерной цепи, управляемый источник опорного тока (УИОТ) (7), выход которого связан с токовым входом (6), первый (8) и второй (9) вспомогательные транзисторы (Т), базы которых подключены к источнику напряжения смещения (ИНС) (10), коллектор Т (8) соединен с первым (4) токовым выходом ДК (1), а эмиттер подключен к шине источника питания (11) через первый токостабилизирующий двухполюсник (ТД) (12), коллектор Т (9) подключен ко второму (5) токовому выходу ДК (1), а эмиттер подключен к шине источника питания (11) через второй ТД (13), первый (14) и второй (15) выходные Т, первый (16) и второй (17) резисторы нагрузки, соединенные с эмиттерами соответствующих Т (14) и Т (15)и первым (18) и вторым (19) выходами ШОУ, причем общая точка первого (16) и второго (17) резисторов нагрузки связана со входом УИОТ (7), база Т (14) соединена с первым (4) токовым выходом ДК (1), а база Т (15) соединена со вторым (5)

токовым выходом ДК (1). Первый вход (2) ДК (1) связан с эмиттером Т (9) через первый (20) дополнительный конденсатор, а второй вход (3) ДК (1) связан с эмиттером Т (8) через второй (21) дополнительный конденсатор. 1 з.п. ф-лы, 6 ил.

1. Широкополосный операционный усилитель с дифференциальным выходом, содержащий входной дифференциальный каскад (1), имеющий первый (2) и второй (3) входы, первый (4) и второй (5) токовые выходы, и токовый вход (6) в общей эмиттерной цепи, управляемый источник опорного тока (7), выход которого связан с токовым входом (6) в общей эмиттерной цепи, первый (8) и второй (9) вспомогательные транзисторы, базы которых подключены к источнику напряжения смещения (10), коллектор первого (8) вспомогательного транзистора соединен с первым (4) токовым выходом входного дифференциального каскада, а эмиттер подключен к шине источника питания (11) через первый токостабилизирующий двухполюсник (12), коллектор второго (9) вспомогательного транзистора подключен ко второму (5) токовому выходу входного дифференциального каскада (1), а эмиттер подключен к шине источника питания (11) через второй (13) токостабилизирующий двухполюсник, первый (14) и второй (15) выходные транзисторы, первый (16) и второй (17) резисторы нагрузки, соединенные с эмиттерами соответствующих первого (14) и второго (15) выходных транзисторов и первым (18) и вторым (19) выходами устройства, причем общая точка первого (16) и второго (17) резисторов нагрузки связана со входом управляемого источника опорного тока (7), база первого (14) выходного транзистора соединена с первым (4) токовым выходом входного дифференциального каскада (1), а база второго (15) выходного транзистора соединена со вторым (5) токовым выходом дифференциального каскада, отличающийся тем, что первый вход (2) входного дифференциального каскада (1) связан с эмиттером второго (9) вспомогательного транзистора через первый (20) дополнительный конденсатор, а второй вход (3) входного дифференциального каскада (1) связан с эмиттером первого (8) вспомогательного транзистора через второй (21) дополнительный конденсатор.

2. Устройство по п.1, отличающееся тем, что первый вход (2) входного дифференциального каскада (1) связан с эмиттером второго (9) вспомогательного транзистора через последовательно соединенные первый (20) дополнительный конденсатор и первый (22) дополнительный буферный усилитель, а второй вход (3) входного дифференциального каскада (1) связан с эмиттером первого (8) вспомогательного транзистора через последовательно соединенные второй (21) дополнительный конденсатор и второй (23) дополнительный буферный усилитель.

| US 4272728 А, 09.06.1981 | |||

| Дифференциальный усилитель | 1973 |

|

SU527003A1 |

| Дифференциальный усилитель | 1981 |

|

SU1104648A1 |

| US 3395358 А, 30.07.1968. | |||

Авторы

Даты

2010-06-27—Публикация

2009-02-18—Подача