65

4:iib

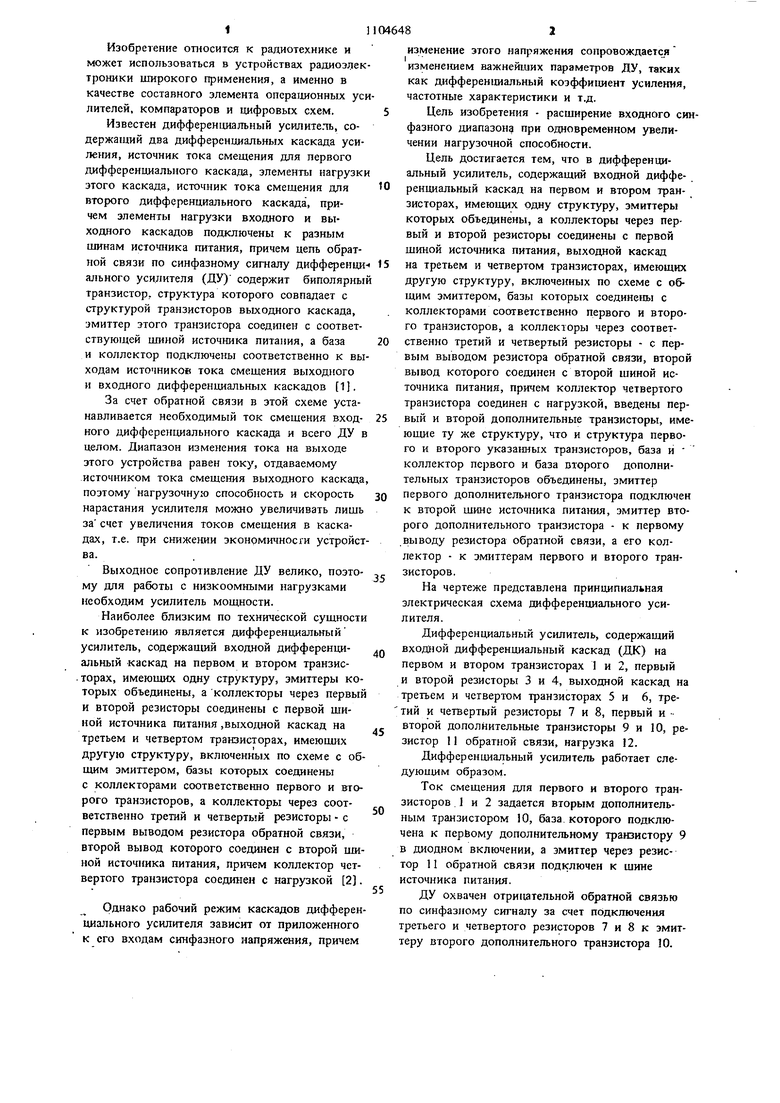

00 1 Изобретение относится к радиотехнике и может использоваться в устройствах радиоэлек троники широкого применения, а именно в качестве составного элемента операционных уси лителей, компараторов и цифровых схем. Известен дифферен1шальный усилитель, содержащий два дифференциальных каскада усиления, источник тока смещения для первого дифференциального каскада, элементы нагрузки этого каскада, источник тока смещения для второго дифференциального каскада, причем элементы нагрузки входного и выходного каскадов подключены к разным шинам источника питания, причем цепь обратной связи по синфазному сигналу дифференци ального усилителя (ДУ) содержит биполярны транзистор, структура которого совпадает с структурой транзисторов выходного каскада, эмиттер этого транзистора соединен с соответствующей щиной источника питания, а база и коллектор подключены соответственно к вы ходам источников тока смещения выходного и входного дифференциальных каскадов 1. За счет обратной связи в этой схеме устанавливается необходимый ток смещения входного дифференциального каскада и всего ДУ в целом. Диапазон изменения тока на выходе этого устройства равен току, отдаваемому источником тока смещения выходного каскада поэтому нагрузочную способность и скорость нарастания усилителя можно увеличивать лишь за счет увеличения токов смещения в каскадах, т.е. при снижении экономичное ги устройст ва. Выходное сопротивление ДУ велико, поэтому для работы с низкоомными нагрузками необходим усилитель мощности. Наиболее близким но технической сущности к изобретению является дифференциальный усилитель, содержащий входной дифференциальный каскад на первом и втором траизис. торах, имеющих одну структуру, эмиттеры которых объединены, а коллекторы через первый и второй резисторы соединены с первой шиной источника питания ,выходаой каскад на третьем и четвертом трашисторах, имеющих другую структуру, включенных по схеме с об щим эмиттером, базы которых соединены с коллекторами соответственно первого и второго транзисторов, а коллекторы через соответственно третий и четвертый резисторы - с первым выводом резистора обратной связи, второй вывод которого соединен с второй ши ной источника питания, причем коллектор четвертого транзистора соединен с нагрузкой 2 Однако рабочий режим каскадов дифферен циального усилителя зависит от приложенного к его входам синфазного напряжения, причем 8 изменение этого напряжения сопровождается измене1шем важнейших параметров ДУ, таких как дифферен1шальный коэффициент усиления, частотные характеристики и т.д. Цель изобретения - расширение входного синфазного диапазона при одновременном увеличении нагрузочной способности. Цель достигается тем, что в дифференциальный усилитель, содержащий входной дифференциальный каскад на первом и втором транзисторах, имеющих одну структуру, эмиттеры которых объединены, а коллекторы через первый и второй резисторы соединены с первой шиной источника питания, выходной каскад на третьем и четвертом транзисторах, имеющих другую структуру, включенных по схеме с общим эмиттером, базы которых соединены с коллекторами соответственно первого и второго транзисторов, а коллекторы через соответственно третий и четвертый резисторы - с первым выводом резистора обратной связи, второй вывод которого соединен с второй шиной источника питания, причем коллектор четвертого транзистора соединен с нагрузкой, введены первый и второй дополнительные транзисторы, имеющие ту же структуру, что и структура первого и второго указа1шых транзисторов, база и коллектор первого и база второго дополнительных транзисторов объединены, эмиттер первого дополнительного транзистора подключен к второй щине источника питания, эмиттер второго дополнительного транзистора - к первому выводу резистора обратной связи, а его коллектор - к эмиттерам первого и второго транзисторов. На чертеже представлена принципиальная электрическая схема дифференциального усилителя. Дифференциальный усилитель, содержащий входной дифференциальный каскад (ДК) на первом и втором транзисторах 1 и 2, первый и второй резисторы 3 и 4, выходной каскад на третьем и четвертом транзисторах 5 и 6, третий и четвертый резисторы 7 и 8, первый и второй дополнительные транзисторы 9 и 10, резистор 11 обратной связи, нагрузка 12. Дифференциальный усилитель работает следуюцщм образомТок смещения для первого и второго транзисторов . 1 и 2 задается вторым дополнительным транзистором 10, база, которого подключена к перЗому дополнительному транзистору 9 в диодном включении, а эмиттер через резистор 11 обратной связи подключен к шине источника питания. ДУ охвачен отрицательной обратной связью по синфазному сигналу за счет подключения третьего и четвертого резисторов 7 и 8 к эмиттеру второго дополнительного транзистора 10. Для нагрузки 1Л обратная связь по синфазному сигналу является пара/тельной обратной связью по току, которая, совместно с отсутствием токоограннчиваюишх элементов в эмиттерах третьего и четвертого транзисторов 5 и 6 позволяет получить высокие показатели по нагрузочной способности и быстродействию ДУ, при этом дифферен1шальный коэффициент уси.ления слабо зависит от сопротивления несим- . метричной нагрузки. Однако за счет того, что эмиттеры первого и второго транзисторов 1 и 2 соединены с резистором 11 обратной связи через высокое внутреннее сопротивление геифатора тока, выполненного на втором дополнительном транзисторе 10, козффишент усиления по синфазному сигналу ДУ много меньше единицы, а параметры ДУ стабильны в широком диапазоне синфазных входных напряжений. При этом допустимый входной синфазный диапазон ДУ ограничен лишь насыщением первого и второго транзисторов 1 и 2 второго дополнительного транзистора 10. ДУ обладает также широком динамическим диапазоном по выходу, что совместно с высокой нагрузочной способностью ДУ позволяет использовать его без специализированного усилителя мощности. Свойства выходного каскада позволяют работать на нагрузку с значительной щунтируюи ей емкостью, обеспечивая малую задержку распространения. Это расишряет область применения предлагаемых 1Ц1фференщ1альных усилителей, используемых не только как составную часть операционных усилителей и компараторов, но и при защите транзисторов выходного каскада от режима насыщения, в качестве логического элемента (усилителя-инвертора) с высокими показателями по быстродействию, помехозащищенности и нагрузочной способности. 7Ш I сгзн

| название | год | авторы | номер документа |

|---|---|---|---|

| Дифференциальный усилитель | 1983 |

|

SU1124427A1 |

| Дифференциальный усилитель | 1983 |

|

SU1146792A1 |

| ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ С ПАРАФАЗНЫМ ВЫХОДОМ | 2009 |

|

RU2419193C1 |

| ДИФФЕРЕНЦИАЛЬНЫЙ ОПЕРАЦИОННЫЙ УСИЛИТЕЛЬ С ПАРАФАЗНЫМ ВЫХОДОМ | 2010 |

|

RU2436226C1 |

| ДИФФЕРЕНЦИАЛЬНЫЙ ОПЕРАЦИОННЫЙ УСИЛИТЕЛЬ С ПАРАФАЗНЫМ ВЫХОДОМ | 2010 |

|

RU2439778C1 |

| УСИЛИТЕЛЬ ТОКА | 1991 |

|

RU2020729C1 |

| ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ С РАСШИРЕННЫМ ДИАПАЗОНОМ ИЗМЕНЕНИЯ ВХОДНОГО СИНФАЗНОГО СИГНАЛА | 2012 |

|

RU2474953C1 |

| Дифференциальный усилитель | 1983 |

|

SU1140227A1 |

| КАСКОДНЫЙ ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ | 2006 |

|

RU2321158C1 |

| ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ | 2005 |

|

RU2292633C1 |

ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ, содержащий входной дифференциаль( каскад на первом и втором транзисторах, имеющих одну структуру, эмиттеры которых объединены, а коллекторы через первый и второй резисторы соеданены с первой шиной источника питания, выходной каскад на третьем и четвертом транзисторах, имеющих другую структуру, включенных по схеме с общим эмиттером, базы которых соединены с коллекторами соответственно первого и второго транзисторов,, а коллекторы через соответственно гретий и четвертый резисторы - с первым выводом резистора обратной связи, второй вывод которого соединен с второй шиной источника питания, причем коллектор четвертого транзистора соединен с нагрузкой, отличающийся тем, что, с целью расщирения входного синфазного диапазона при одновременном увеличении нагрузочной способности, введены первый и второй дополнительные транзисторы, имеющие ту же структуру, что и структура первого и второго указанга 1х транзисторов, база и коллектор перi вого и база второго дополнительных транзисторов объединены, эмиттер первого дополнитель(Л ного транзистора подключен к второй шине истошика питашя, эмиттер второго дополнительного транзистора - к первому выводу резистора обратной связи, а его коллектор - к эмиттерам первого и второго транзисторов.

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Патент США № 3959733, кл | |||

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Патент США № 3168709, кл | |||

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1984-07-23—Публикация

1981-06-26—Подача