Изобретение относится к области электросвязи и информационных технологий, а именно к технике защиты подлинности электронных изображений, сжимаемых алгоритмами сжатия электронных изображений, такими как JPEG, MPEG-2 и т.п., и передаваемых отправителем получателю по общедоступным каналам передачи, в которых нарушитель может осуществлять действия по навязыванию получателю ложных электронных изображений. Заявленное устройство может быть использовано для установления подлинности электронных изображений, передаваемых в современных информационно-телекоммуникационных системах.

Известны устройства контроля подлинности электронных изображений на основе вычисления и проверки аутентификатора из существенных характеристик заверяемого изображения, например устройство контроля подлинности электронных изображений по патенту США 6532541, МПК7 H04L 9/00, от 11.03.2003. Данное устройство содержит передающую сторону и приемную сторону. Передающая сторона устройства предназначена для формирования аутентификатора электронного изображения (ЭИ) и передачи ЭИ и его аутентификатора по каналу передачи. Передающая сторона устройства содержит разделитель на блоки ЭИ, первый блок извлечения существенных характеристик, блок формирования аутентификатора и блок памяти ключа аутентификации.

Вход разделителя на блоки ЭИ является информационным входом передающей стороны устройства. Выход разделителя на блоки ЭИ подключен к входу первого блока извлечения существенных характеристик, выход которого подключен к первому входу блока формирования аутентификатора, второй вход которого подключен к выходу блока памяти ключа аутентификации. Выход блока формирования аутентификатора является выходом передающей стороны устройства, причем разделитель на блоки ЭИ, первый блок извлечения существенных характеристик, блок формирования аутентификатора и блок памяти ключа аутентификации снабжены управляющими входами, на которые поступают соответствующие сигналы управления.

Приемная сторона устройства предназначена для приема и проверки подлинности принятого ЭИ. Приемная сторона устройства содержит второй блок извлечения существенных характеристик, блок проверки аутентификатора, блок памяти ключа проверки аутентификации и блок сравнения. Первый информационный вход блока проверки аутентификатора является информационным входом “принятый аутентификатор” приемной стороны устройства, второй вход блока проверки аутентификатора подключен к выходу блока памяти ключа аутентификации. Выход блока проверки аутентификатора подключен к первому входу блока сравнения, второй вход которого подключен к выходу второго блока извлечения существенных характеристик, информационный вход которого является информационным входом “принятое электронное изображение” приемной стороны устройства. Выход “подтверждение подлинности” блока сравнения является одноименным выходом приемной стороны устройства, а выход “неподтверждение подлинности” блока сравнения является одноименным выходом приемной стороны устройства, причем блок проверки аутентификатора, блок памяти ключа проверки аутентификации, блок сравнения и второй блок извлечения существенных характеристик снабжены управляющими входами, на которые поступают соответствующие сигналы управления.

Недостатками указанного аналога являются необходимость дополнительной передачи аутентификатора ЭИ, а также низкая формализуемость допустимой величины различия существенных характеристик ЭИ при вынесении решения в блоке сравнения о подлинности принятого ЭИ.

Также известно устройство формирования и проверки заверенного цифровым водяным знаком ЭИ, описанное, например, в книге: Marvel L., Boncelet C., Retter J. Reliable Blind Information Hiding for Images // Proceedings of 2nd Workshop on Information Hiding. Lecture Notes in Computer Science. 1998, p.89-94. Устройство формирования и проверки заверенного цифровым водяным знаком (ЦВЗ) электронного изображения содержит передающую сторону и приемную сторону. Передающая сторона устройства предназначена для формирования заверенного цифровым водяным знаком электронного изображения путем вычисления цифрового водяного знака из ЭИ и его встраивания в это же ЭИ, а также передачи заверенного цифровым водяным знаком ЭИ по каналу передачи. Передающая сторона устройства содержит первый блок памяти цифрового водяного знака, блок преобразования передачи, первый блок памяти ключа аутентификации, первый блок кодирования, модулятор, блок памяти ключа встраивания, формирователь модулирующей последовательности, перемежитель, блок памяти ключа перемежения, сумматор, квантователь и блок передачи, причем блок преобразования передачи, первый блок кодирования, модулятор, формирователь модулирующей последовательности, перемежитель и квантователь снабжены управляющими входами, на которые поступают соответствующие сигналы управления.

Приемная сторона устройства предназначена для приема ЭИ и проверки его подлинности. Приемная сторона устройства содержит блок приема, корреляционный декодер, второй блок памяти цифрового водяного знака, блок преобразования приема, второй блок кодирования, второй блок памяти ключа аутентификации, демодулятор, блок памяти ключа извлечения, формирователь демодулирующей последовательности, деперемежитель, блок памяти ключа деперемежения и блок формирования решения, причем корреляционный декодер, блок преобразования приема, второй блок кодирования, демодулятор, формирователь демодулирующей последовательности, деперемежитель и блок формирования решения снабжены управляющими входами, на которые поступают соответствующие сигналы управления.

Указанный аналог обеспечивает повышение устойчивости к воздействию ошибок канала передачи на заверенное цифровым водяным знаком электронное изображение, но не обеспечивает контроль подлинности электронных изображений, сжимаемых с использованием алгоритмов сжатия, таких как JPEG, MPEG-2 и т.п. Данный недостаток известного устройства формирования и проверки заверенного цифровым водяным знаком электронного изображения обусловлен тем, что встраивание цифрового водяного знака осуществляется в значения яркости пикселов электронного изображения, и при выполнении преобразования Фурье и квантования коэффициентов Фурье в процессе сжатия электронного изображения цифровой водяной знак искажается, что приводит к непризнанию подлинным принятого получателем заверенного цифровым водяным знаком электронного изображения.

Наиболее близким по своей технической сущности к заявляемому устройству формирования и проверки заверенного цифровым водяным знаком электронного изображения является устройство формирования и проверки заверенного цифровым водяным знаком электронного изображения по патенту США 7280669, МПК8 G06K 9/00, от 09.10.07. Устройство-прототип формирования и проверки заверенного цифровым водяным знаком электронного изображения состоит из передающей стороны и приемной стороны. Передающая сторона устройства содержит блок разделения электронного изображения, первый блок преобразования Фурье, первый блок разделения коэффициентов Фурье, первый блок памяти ключа аутентификации, формирователь аутентификатора блока, формирователь цифрового водяного знака блока, сумматор, блок встраивания цифрового водяного знака, блок объединения коэффициентов Фурье, блок обратного преобразования Фурье, блок объединения электронного изображения и блок передачи.

Приемная сторона устройства содержит блок приема, блок разделения принятого электронного изображения, второй блок преобразования Фурье, второй блок разделения коэффициентов Фурье, второй блок памяти ключа аутентификации, формирователь аутентификатора принятого блока, блок извлечения цифрового водяного знака, коррелятор и блок формирования решения.

Информационный вход блока разделения электронного изображения является информационным входом передающей стороны устройства. M-разрядный выход блока разделения электронного изображения подключен к M-разрядному входу первого блока преобразования Фурье, где М≥2, выход которого подключен ко входу блока разделения коэффициентов Фурье. Выход “первые коэффициенты Фурье” блока разделения коэффициентов Фурье подключен к входу “первые коэффициенты Фурье” сумматора и к входу “первые коэффициенты Фурье” блока объединения коэффициентов Фурье, а выход “вторые коэффициенты Фурье” блока разделения коэффициентов Фурье подключен к первому информационному входу блока встраивания цифрового водяного знака. Выход первого блока памяти ключа аутентификации подключен к информационному входу “ключ аутентификации” формирователя аутентификатора блока, выход которого подключен к информационному входу “аутентификатор блока” формирователя цифрового водяного знака блока, выход которого подключен к входу “ЦВЗ блока” сумматора. Выход сумматора подключен к информационному входу “суммированный ЦВЗ” блока встраивания цифрового водяного знака, выход которого подключен к входу “встроенный ЦВЗ” блока объединения коэффициентов Фурье. Выход блока объединения коэффициентов Фурье подключен к входу блока обратного преобразования Фурье, выход которого подключен к входу блока объединения электронного изображения. Выход блока объединения электронного изображения подключен к входу блока передачи, выход которого является выходом передающей стороны устройства, причем блок разделения электронного изображения, формирователь аутентификатора блока и блок встраивания цифрового водяного знака снабжены управляющими входами считывания, формирователь цифрового водяного знака блока снабжен управляющим входом записи, а блок разделения электронного изображения и блок встраивания цифрового водяного знака снабжены также управляющими входами записи, на которые поступают соответствующие сигналы управления.

Вход блока приема, подключенный через канал передачи к выходу передающей стороны устройства, является входом приемной стороны устройства. Выход блока приема подключен к информационному входу блока разделения принятого электронного изображения, выход которого подключен к входу второго блока преобразования Фурье. Выход второго блока преобразования Фурье подключен к входу второго блока разделения коэффициентов Фурье, выход “первые коэффициенты Фурье” и выход “вторые коэффициенты Фурье” которого подключены соответственно к одноименным информационным входам блока извлечения цифрового водяного знака. Выход блока извлечения цифрового водяного знака подключен к первому входу коррелятора. Выход второго блока памяти ключа аутентификации подключен к информационному входу “ключ аутентификации” формирователя аутентификатора принятого блока, выход которого подключен ко второму входу коррелятора. Выход коррелятора подключен к информационному входу блока формирования решения, выход “подлинное электронное изображение” и выход “неподлинное электронное изображение” которого являются соответствующими выходами приемной стороны устройства, причем блок разделения принятого электронного изображения, формирователь аутентификатора принятого блока и блок формирования решения снабжены управляющими входами считывания, а блок извлечения цифрового водяного знака снабжен управляющим входом записи, на которые поступают соответствующие сигналы управления.

Недостатком ближайшего аналога (прототипа) заявляемого устройства формирования и проверки заверенного цифровым водяным знаком электронного изображения является относительно низкая защищенность изображения, заверенного цифровым водяным знаком отправителя, от навязывания ложного электронного изображения нарушителем, которому известно хотя бы одно заверенное отправителем цифровым водяным знаком электронное изображение. Это обусловлено тем, что нарушитель, для которого значение секретного ключа аутентификации неизвестно, способен из блока заверенного цифровым водяным знаком отправителя электронного изображения извлечь встроенный в него цифровой водяной знак, затем встроить извлеченный цифровой водяной знак в блок ложного электронного изображения, который при проверке получателем будет ошибочно признан подлинным. Для извлечения встроенного в блок заверенного цифровым водяным знаком отправителя электронного изображения его цифрового водяного знака нарушитель выполняет преобразование Фурье над значениями яркости пикселов этого блока и, так же как и получатель, вычисляет цифровой водяной знак блока электронного изображения из коэффициентов Фурье, принадлежащих к первой и второй частотным областям этого блока. Следовательно, нарушитель способен без знания секретного ключа аутентификации извлечь цифровой водяной знак из заверенного отправителем электронного изображения и встроить извлеченный цифровой водяной знак в ложное электронное изображение, которое получателем будет ошибочно признано подлинным.

Техническим результатом заявляемого решения является повышение защищенности заверенного цифровым водяным знаком электронного изображения от преднамеренных действий нарушителя по изменению содержания электронного изображения за счет использования неизвестной для нарушителя зависимости цифрового водяного знака от электронного изображения.

Указанный технический результат достигается тем, что в известном устройстве формирования и проверки заверенного цифровым водяным знаком электронного изображения, содержащем на передающей стороне блок преобразования Фурье, M-разрядный вход которого подключен к M-разрядному выходу блока разделения электронного изображения, где M≥2, информационный вход которого является информационным входом устройства, формирователь аутентификатора блока, информационный вход “ключ аутентификации” и выход которого подключены соответственно к выходу первого блока памяти ключа аутентификации и к информационному входу “аутентификатор блока” формирователя цифрового водяного знака блока, выход которого подключен к входу “ЦВЗ блока” сумматора, выход которого подключен к информационному входу “суммированный ЦВЗ” блока встраивания цифрового водяного знака, выход которого подключен к входу блока передачи, выход которого является выходом передающей стороны устройства, причем блок разделения электронного изображения, формирователь аутентификатора блока и блок встраивания цифрового водяного знака снабжены управляющими входами считывания, формирователь цифрового водяного знака блока снабжен управляющим входом записи, а блок разделения электронного изображения и блок встраивания цифрового водяного знака снабжены также управляющими входами записи, на которые поступают соответствующие сигналы управления, на приемной стороне устройства блок приема, вход которого через канал передачи подключен к выходу передающей стороны устройства, формирователь аутентификатора принятого блока, информационный вход “ключ аутентификации” которого подключен к выходу второго блока памяти ключа аутентификации, блок извлечения цифрового водяного знака и блок формирования решения, выходы которого “подлинное электронное изображение” и “неподлинное электронное изображение” являются соответствующими выходами устройства, причем формирователь аутентификатора принятого блока и блок формирования решения снабжены управляющими входами считывания, а блок извлечения цифрового водяного знака снабжен управляющим входом записи, на которые поступают соответствующие сигналы управления, дополнительно введены на передающей стороне первый квантователь, кодер Хаффмана, первый выделитель совпадающих последовательностей, первый блок памяти пар последовательностей, первый счетчик совпадающих последовательностей, второй квантователь, формирователь последовательности блока и первый блок памяти ключа встраивания, выход которого подключен к входу “ключ встраивания” сумматора. M-разрядный выход блока разделения электронного изображения подключен к M-разрядному информационному входу второго квантователя, G-разрядный выход которого подключен к G-разрядному информационному входу формирователя последовательности блока, где 2≤G≤М, выход которого подключен к информационному входу “последовательность блока” формирователя аутентификатора блока, M-разрядный выход блока преобразования Фурье подключен к M-разрядному информационному входу первого квантователя, G-разрядный выход которого подключен к G-разрядному информационному входу кодера Хаффмана, Q-разрядный выход которого подключен к Q-разрядному информационному входу “последовательность Хаффмана” первого выделителя совпадающих последовательностей и к одноименному информационному входу блока встраивания цифрового водяного знака, где Q≥2. S-разрядный выход “номер совпадения” первого выделителя совпадающих последовательностей подключен к одноименному S-разрядному информационному входу блока встраивания цифрового водяного знака, где S≥2, выход “наличие совпадения” первого выделителя совпадающих последовательностей подключен к одноименному информационному входу блока встраивания цифрового водяного знака и к входу первого счетчика совпадающих последовательностей, R-разрядный выход которого подключен к R-разрядному информационному входу "число совпадений" формирователя цифрового водяного знака блока, где R≥log2(N×N). С первого по S-й Q-разрядные выходы первого блока памяти пар последовательностей подключены к соответствующим Q-разрядным информационным входам “последовательности пар” первого выделителя совпадающих последовательностей и блока встраивания цифрового водяного знака, причем первый квантователь, кодер Хаффмана, первый выделитель совпадающих последовательностей, первый блок памяти пар последовательностей, второй квантователь и формирователь последовательности блока снабжены управляющими входами считывания, а формирователь последовательности блока снабжен дополнительно управляющим входом записи, на которые поступают соответствующие сигналы управления.

На приемной стороне дополнительно введены выделитель последовательностей Хаффмана принятого блока, декодер Хаффмана, деквантователь, блок обратного преобразования Фурье, третий квантователь, формирователь последовательности принятого блока, второй блок памяти пар последовательностей, второй выделитель совпадающих последовательностей, второй счетчик совпадающих последовательностей, сумматор, второй блок памяти ключа встраивания и блок сравнения, информационные входы “аутентификатор принятого блока” и “извлеченный ЦВЗ” которого подключены к выходам соответственно формирователя аутентификатора принятого блока и блока извлечения цифрового водяного знака. R-разрядный информационный вход “число совпадений” блока извлечения цифрового водяного знака подключен к R-разрядному выходу второго счетчика совпадающих последовательностей, вход которого подключен к выходу “наличие совпадения” второго выделителя совпадающих последовательностей, Q-разрядный информационный вход “последовательность Хаффмана” и с первого по S-й Q-разрядные информационные входы “последовательности пар” которого подключены соответственно к Q-разрядному выходу выделителя последовательностей Хаффмана принятого блока и к соответствующим Q-разрядным выходам второго блока памяти пар последовательностей. Выход “идентификация” второго выделителя совпадающих последовательностей подключен к одноименному входу сумматора, вход “ключ встраивания” которого подключен к выходу второго блока памяти ключа встраивания. Выход блока приема подключен к информационному входу выделителя последовательностей Хаффмана принятого блока, Q-разрядный выход которого подключен к Q-разрядному информационному входу декодера Хаффмана, G-разрядный выход которого подключен к G-разрядному информационному входу деквантователя, M-разрядный выход которого подключен к M-разрядному входу блока обратного преобразования Фурье, M-разрядный выход которого подключен к M-разрядному информационному входу третьего квантователя, G-разрядный выход которого подключен к G-разрядному информационному входу формирователя последовательности принятого блока, выход которого подключен к информационному входу “последовательность принятого блока” формирователя аутентификатора принятого блока. Выход сумматора подключен к информационному входу “суммированный сигнал” блока извлечения цифрового водяного знака, выход блока сравнения подключен к информационному входу блока формирования решения. Причем выделитель последовательностей Хаффмана принятого блока, декодер Хаффмана, деквантователь, третий квантователь, формирователь последовательности принятого блока, второй блок памяти пар последовательностей, второй выделитель совпадающих последовательностей и блок сравнения снабжены управляющими входами считывания, а выделитель последовательностей Хаффмана принятого блока и формирователь последовательности принятого блока снабжены дополнительно управляющими входами записи, на которые поступают соответствующие сигналы управления.

Указанная новая совокупность существенных признаков за счет непредсказуемой для нарушителя зависимости цифрового водяного знака блока заверенного цифровым водяным знаком электронного изображения от значений яркости пикселов этого блока и секретного ключа аутентификации обеспечивает невозможность для нарушителя, которому неизвестно ни одно заверенное цифровым водяным знаком электронное изображение, сформировать цифровой водяной знак для встраивания в ложное электронное изображение, которое будет признано получателем при его проверке подлинным. При перехвате нарушителем одного или нескольких заверенных цифровым водяным знаком электронных изображений за счет непредсказуемости для него зависимости цифрового водяного знака блока заверенного электронного изображения от значения секретного ключа встраивания нарушитель не способен извлечь встроенный цифровой водяной знак с целью его встраивания в ложное электронное изображение, что обеспечивает повышение защищенности заверенного цифровым водяным знаком электронного изображения от преднамеренных действий нарушителя по изменению его содержания.

Заявленное устройство поясняется чертежами, на которых показаны:

- на фиг.1 - общая схема устройства формирования и проверки заверенного цифровым водяным знаком электронного изображения;

- на фиг.2 - структурная схема передающей стороны 1 устройства формирования и проверки заверенного цифровым водяным знаком электронного изображения;

- на фиг.3 - структурная схема приемной стороны 2 устройства формирования и проверки заверенного цифровым водяным знаком электронного изображения;

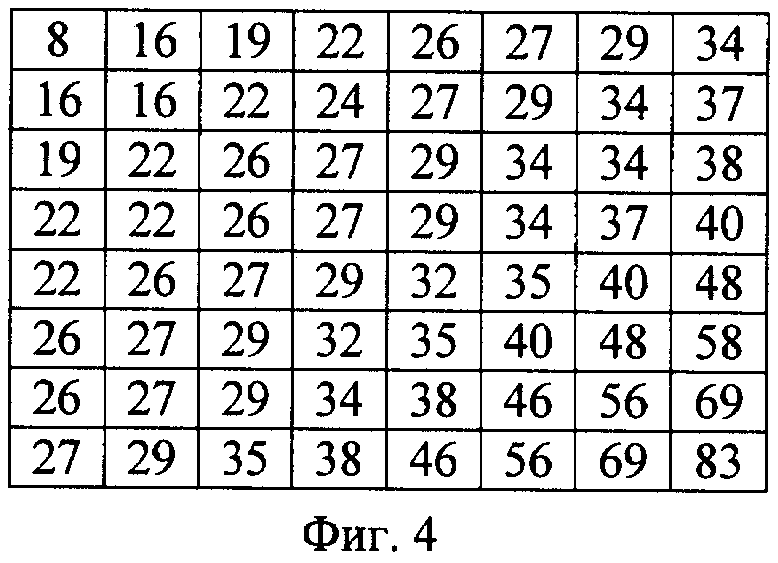

- на фиг.4 - пример построения первой функции квантования в табличном виде;

- на фиг.5 - пример нумерации коэффициентов Фурье блока электронного изображения;

- на фиг.6 - структурная схема первого квантователя 1.3;

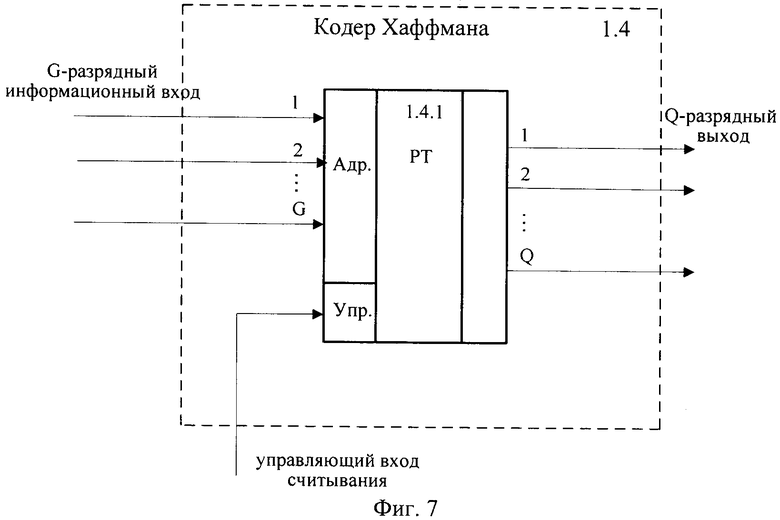

- на фиг.7 - структурная схема кодера Хаффмана 1.4;

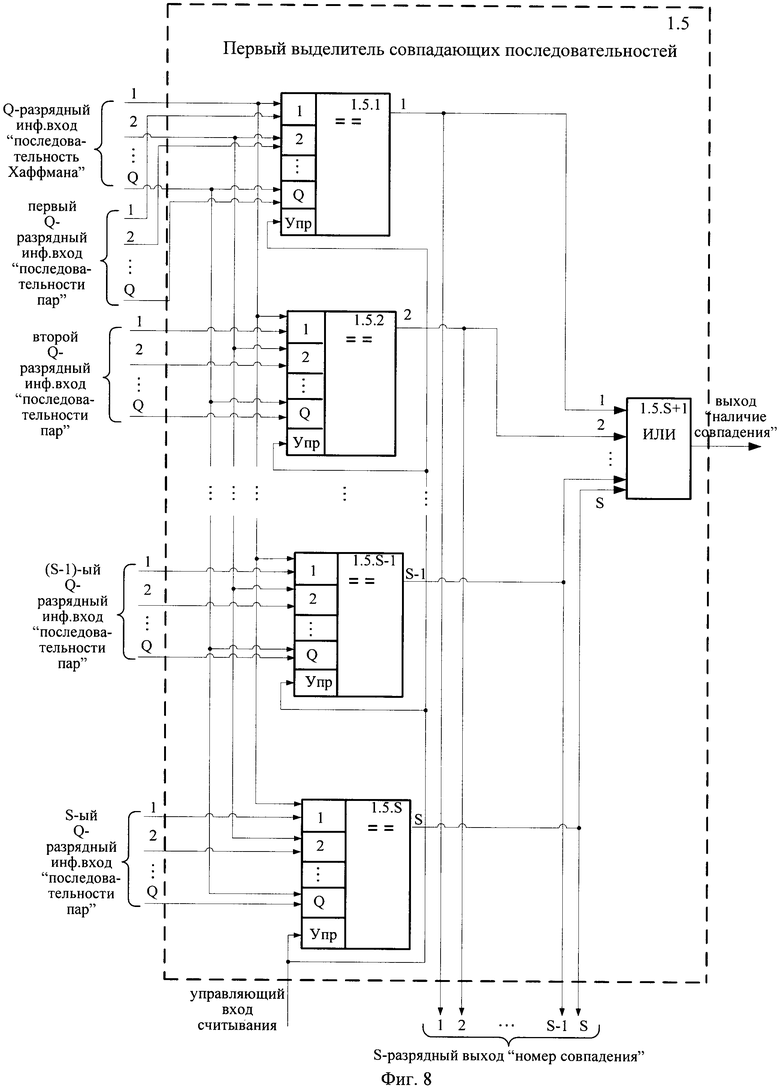

- на фиг.8 - структурная схема первого выделителя совпадающих последовательностей 1.5;

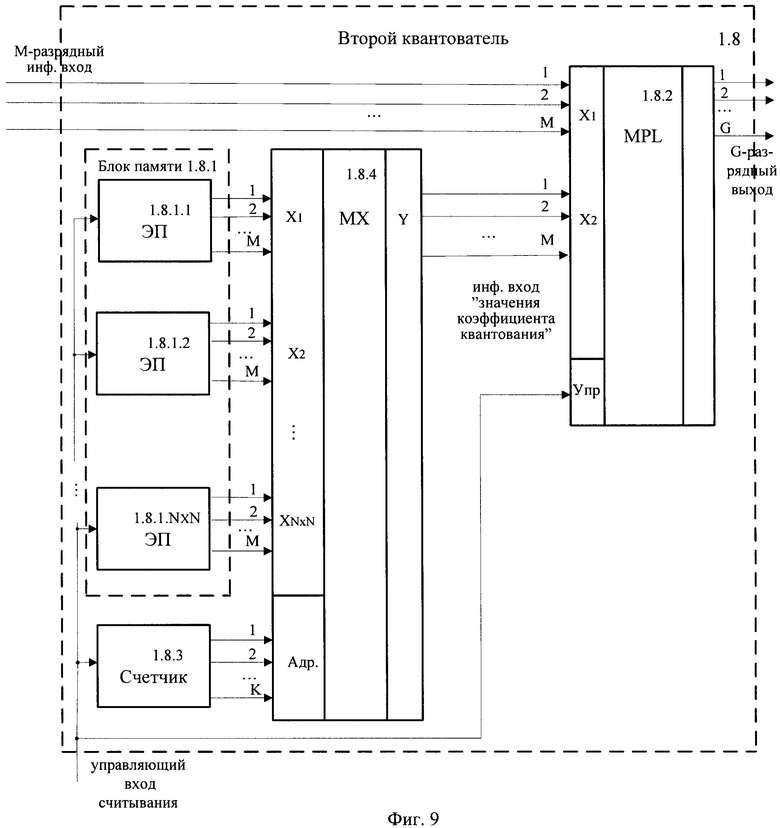

- на фиг.9 - структурная схема второго квантователя 1.8;

- на фиг.10 - структурная схема формирователя аутентификатора блока 1.10;

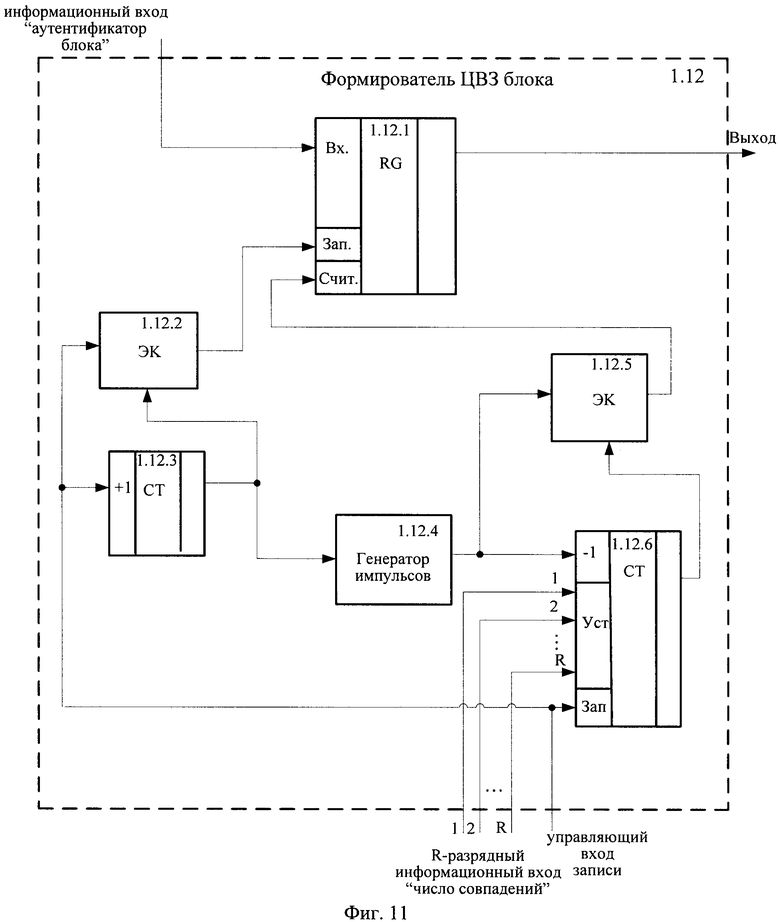

- на фиг.11 - структурная схема формирователя цифрового водяного знака блока 1.12;

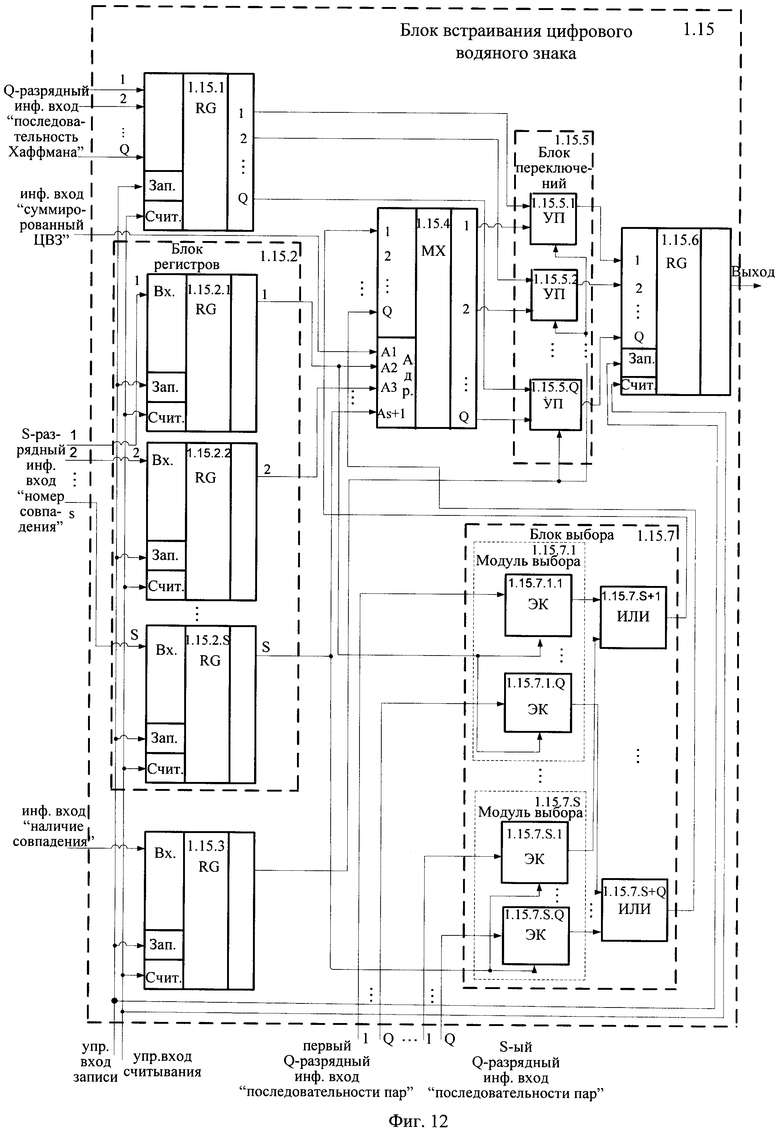

- на фиг.12 - структурная схема блока встраивания цифрового водяного знака 1.15;

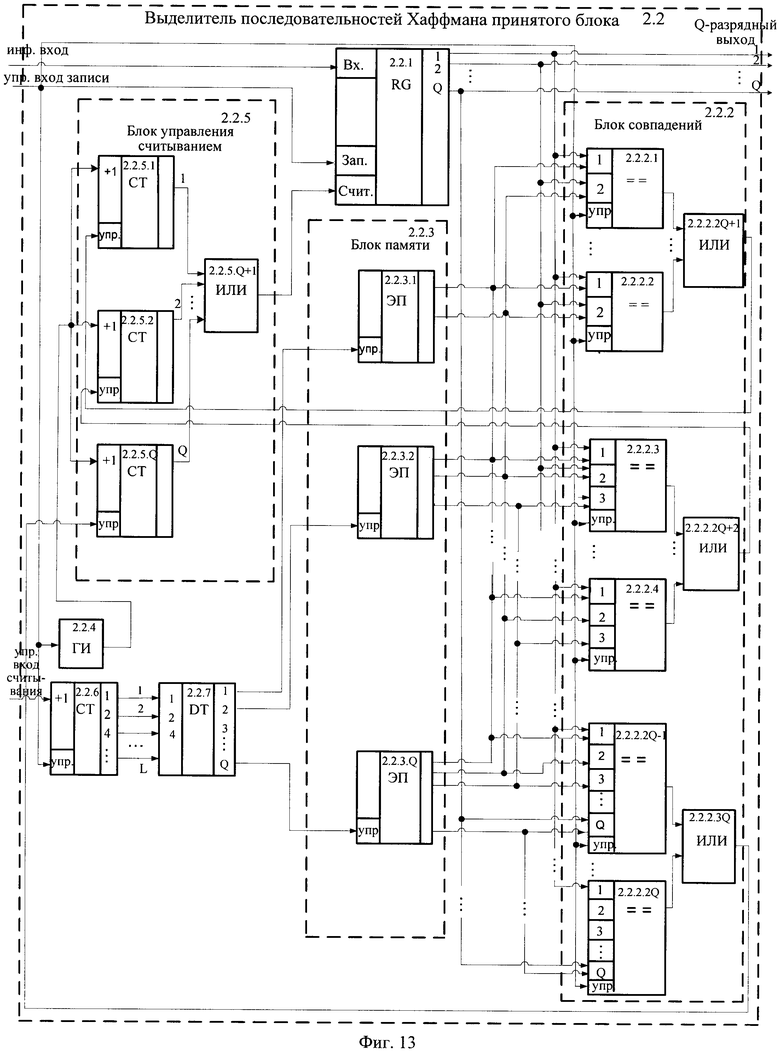

- на фиг.13 - структурная схема выделителя последовательностей Хаффмана принятого блока 2.2;

- на фиг.14 - структурная схема деквантователя 2.4;

- на фиг.15 - структурная схема второго выделителя совпадающих последовательностей 2.11;

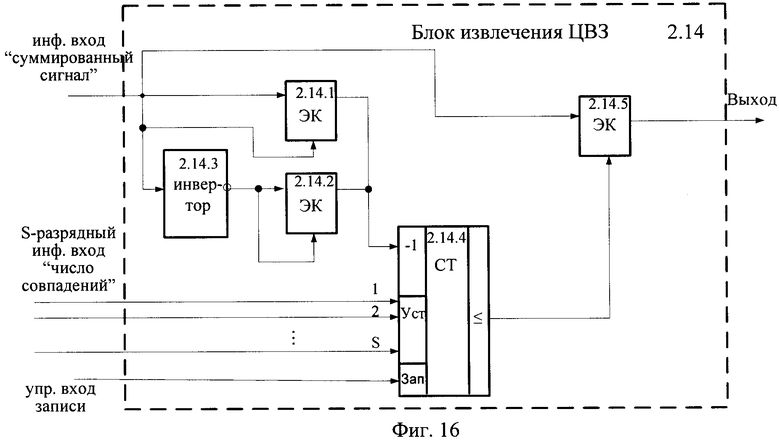

- на фиг.16 - структурная схема блока извлечения цифрового водяного знака 2.14;

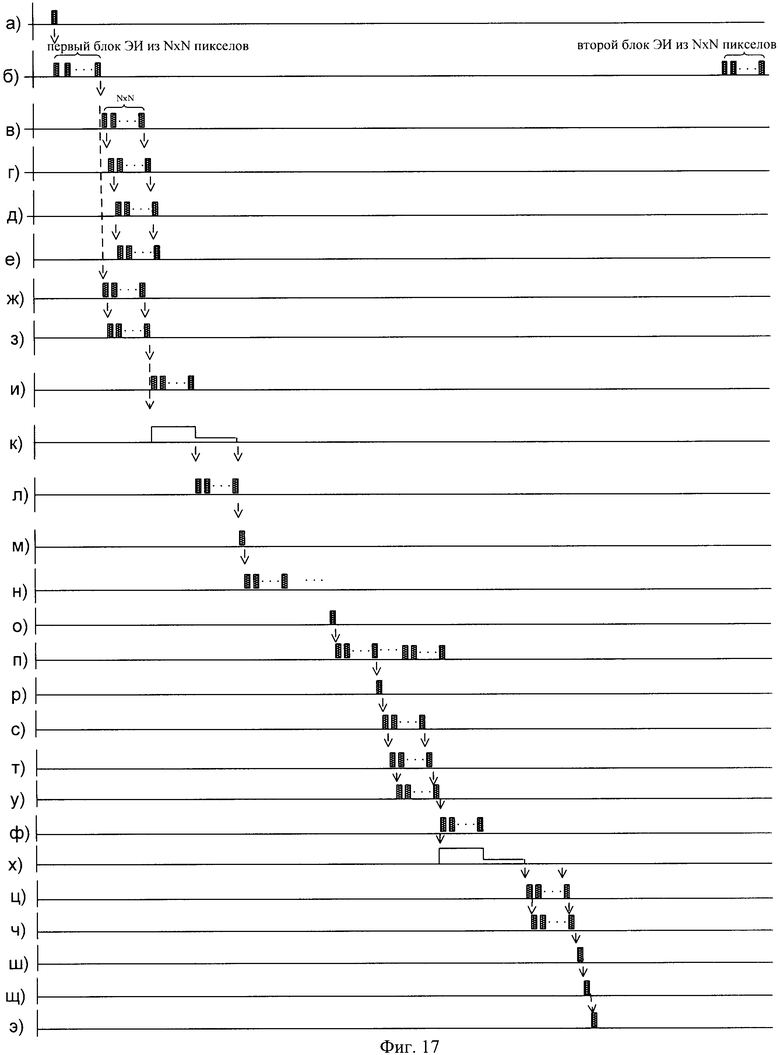

- на фиг.17 - временные диаграммы формирования и проверки заверенного цифровым водяным знаком электронного изображения;

- на фиг.18 - график, показывающий эффект заявляемого устройства.

Заявляемое устройство, показанное на фигуре 1, состоит из передающей стороны 1 устройства и приемной стороны 2 устройства, которые взаимодействуют через канал передачи. Передающая сторона 1 устройства предназначена для вычисления из заверяемого электронного изображения цифрового водяного знака с использованием секретного ключа аутентификации и встраивания его в это же изображение с использованием секретного ключа встраивания, а также передачи сформированного таким образом заверенного цифровым водяным знаком электронного изображения по каналу передачи. На передающую сторону 1 устройства поступают заверяемое электронное изображение, секретный ключ аутентификации и секретный ключ встраивания. Выход передающей стороны 1 устройства через канал передачи соединен с входом приемной стороны 2 устройства. В канале передачи нарушителем может осуществляться перехват переданного отправителем заверенного цифровым водяным знаком электронного изображения. Нарушитель пытается извлечь цифровой водяной знак из заверенного электронного изображения и извлеченный цифровой водяной знак встроить в ложное электронное изображение, после чего нарушитель ложное электронное изображение передает получателю по каналу передачи. Приемная сторона 2 устройства предназначена для приема из канала передачи электронного изображения, извлечения из принятого электронного изображения цифрового водяного знака с использованием секретного ключа встраивания и проверки его подлинности с использованием секретного ключа аутентификации. На приемную сторону 2 устройства поступают секретный ключ аутентификации и секретный ключ встраивания. Результат проверки подлинности принятого электронного изображения считывают с выходов приемной стороны 2 устройства “подлинное электронное изображение” и “неподлинное электронное изображение”.

Передающая сторона 1 устройства (фиг.2) состоит из блока разделения электронного изображения 1.1, блока преобразования Фурье 1.2, первого квантователя 1.3, кодера Хаффмана 1.4, первого выделителя совпадающих последовательностей 1.5, первого блока памяти пар последовательностей 1.6, первого счетчика совпадающих последовательностей 1.7, второго квантователя 1.8, формирователя последовательности блока 1.9, формирователя аутентификатора блока 1.10, первого блока памяти ключа аутентификации 1.11, формирователя цифрового водяного знака блока 1.12, сумматора 1.13, первого блока памяти ключа встраивания 1.14, блока встраивания цифрового водяного знака 1.15 и блока передачи 1.16.

M-разрядный вход блока преобразования Фурье 1.2 подключен к M-разрядному выходу блока разделения электронного изображения 1.1, где M≥2, информационный вход которого является информационным входом устройства. Информационный вход “ключ аутентификации” и выход формирователя аутентификатора блока 1.10 подключены соответственно к выходу первого блока памяти ключа аутентификации 1.11 и к информационному входу “аутентификатор блока” формирователя цифрового водяного знака блока 1.12, выход которого подключен к входу “ЦВЗ блока” сумматора 1.13, выход которого подключен к информационному входу “суммированный ЦВЗ” блока встраивания цифрового водяного знака 1.15, выход которого подключен к входу блока передачи 1.16, выход которого является выходом передающей стороны устройства. Выход первого блока памяти ключа встраивания 1.14 подключен к входу “ключ встраивания” сумматора 1.13. M-разрядный выход блока разделения электронного изображения 1.1 подключен к M-разрядному информационному входу второго квантователя 1.8, G-разрядный выход которого подключен к G-разрядному информационному входу формирователя последовательности блока 1.9, где 2≤G≤M, выход которого подключен к информационному входу “последовательность блока” формирователя аутентификатора блока 1.10. M-разрядный выход блока преобразования Фурье 1.2 подключен к M-разрядному информационному входу первого квантователя 1.3, G-разрядный выход которого подключен к G-разрядному информационному входу кодера Хаффмана 1.4, Q-разрядный выход которого подключен к Q-разрядному информационному входу “последовательность Хаффмана” первого выделителя совпадающих последовательностей 1.5 и к одноименному информационному входу блока встраивания цифрового водяного знака 1.15, где Q≥2. S-разрядный выход “номер совпадения” первого выделителя совпадающих последовательностей 1.5 подключен к одноименному S-разрядному информационному входу блока встраивания цифрового водяного знака 1.15, где S≥2. Выход “наличие совпадения” первого выделителя совпадающих последовательностей 1.5 подключен к одноименному информационному входу блока встраивания цифрового водяного знака 1.15 и к входу первого счетчика совпадающих последовательностей 1.7, R-разрядный выход которого подключен к R-разрядному информационному входу “число совпадений” формирователя цифрового водяного знака блока 1.12, где R≥log2(N×N). С первого по S-й Q-разрядные выходы первого блока памяти пар последовательностей 1.6 подключены к соответствующим Q-разрядным информационным входам “последовательности пар” первого выделителя совпадающих последовательностей 1.5 и блока встраивания цифрового водяного знака 1.15. Причем блок разделения электронного изображения 1.1, первый квантователь 1.3, кодер Хаффмана 1.4, первый выделитель совпадающих последовательностей 1.5, первый блок памяти пар последовательностей 1.6, второй квантователь 1.8, формирователь последовательности блока 1.9, формирователь аутентификатора блока 1.10 и блок встраивания цифрового водяного знака 1.15 снабжены управляющими входами считывания, формирователь цифрового водяного знака блока 1.12 снабжен управляющим входом записи, а блок разделения электронного изображения 1.1, формирователь последовательности блока 1.9 и блок встраивания цифрового водяного знака 1.15 снабжены также управляющими входами записи, на которые поступают соответствующие сигналы управления от блока управления (на схеме не показан).

Приемная сторона 2 устройства (фиг.3) состоит из блока приема 2.1, выделителя последовательностей Хаффмана принятого блока 2.2, декодера Хаффмана 2.3, деквантователя 2.4, блока обратного преобразования Фурье 2.5, третьего квантователя 2.6, формирователя последовательности принятого блока 2.7, формирователя аутентификатора принятого блока 2.8, второго блока памяти ключа аутентификации 2.9, второго блока памяти пар последовательностей 2.10, второго выделителя совпадающих последовательностей 2.11, второго счетчика совпадающих последовательностей 2.12, сумматора 2.13, блока извлечения цифрового водяного знака 2.14, второго блока памяти ключа встраивания 2.15, блока сравнения 2.16 и блока формирования решения 2.17.

На приемной стороне устройства вход блока приема 2.1 через канал передачи подключен к выходу передающей стороны устройства. Информационный вход “ключ аутентификации” формирователя аутентификатора принятого блока 2.8 подключен к выходу второго блока памяти ключа аутентификации 2.9. Выходы “подлинное электронное изображение” и “неподлинное электронное изображение” блока формирования решения 2.17 являются соответствующими выходами устройства. Информационные входы “аутентификатор принятого блока” и “извлеченный ЦВЗ” блока сравнения 2.16 подключены к выходам соответственно формирователя аутентификатора принятого блока 2.8 и блока извлечения цифрового водяного знака 2.14, R-разрядный информационный вход “число совпадений” которого подключен к R-разрядному выходу второго счетчика совпадающих последовательностей 2.12, вход которого подключен к выходу “наличие совпадения” второго выделителя совпадающих последовательностей 2.11, Q-разрядный информационный вход “последовательность Хаффмана” и с первого по S-й Q-разрядные информационные входы “последовательности пар” которого подключены соответственно к Q-разрядному выходу выделителя последовательностей Хаффмана принятого блока 2.2 и к соответствующим Q-разрядным выходам второго блока памяти пар последовательностей 2.10. Выход “идентификация” второго выделителя совпадающих последовательностей 2.11 подключен к одноименному входу сумматора 2.13, вход “ключ встраивания” которого подключен к выходу второго блока памяти ключа встраивания 2.15. Выход блока приема 2.1 подключен к информационному входу выделителя последовательностей Хаффмана принятого блока 2.2, Q-разрядный выход которого подключен к Q-разрядному информационному входу декодера Хаффмана 2.3, G-разрядный выход которого подключен к G-разрядному информационному входу деквантователя 2.4, M-разрядный выход которого подключен к M-разрядному входу блока обратного преобразования Фурье 2.5, M-разрядный выход которого подключен к M-разрядному информационному входу третьего квантователя 2.6, G-разрядный выход которого подключен к G-разрядному информационному входу формирователя последовательности принятого блока 2.7, выход которого подключен к информационному входу “последовательность принятого блока” формирователя аутентификатора принятого блока 2.8. Выход сумматора 2.13 подключен к информационному входу “суммированный сигнал” блока извлечения цифрового водяного знака 2.14, выход блока сравнения 2.16 подключен к информационному входу блока формирования решения 2.17. Причем выделитель последовательностей Хаффмана принятого блока 2.2, декодер Хаффмана 2.3, деквантователь 2.4, третий квантователь 2.6, формирователь последовательности принятого блока 2.7, формирователь аутентификатора принятого блока 2.8, второй блок памяти пар последовательностей 2.10, второй выделитель совпадающих последовательностей 2.11, блок сравнения 2.16 и блок формирования решения 2.17 снабжены управляющими входами считывания, блок извлечения цифрового водяного знака 2.14 снабжен управляющим входом записи, а выделитель последовательностей Хаффмана принятого блока 2.2 и формирователь последовательности принятого блока 2.7 снабжены дополнительно управляющими входами записи, на которые поступают соответствующие сигналы управления от блока управления (на схеме не показан).

Блок разделения электронного изображения 1.1 предназначен для разделения заверяемого электронного изображения на непересекающиеся блоки каждый размером N×N пикселов, где размер N×N блока составляет, например, 8×8, 16×16 и более пикселов. Он может быть реализован в виде динамического оперативного запоминающего блока с мультиплексором кода адреса, в который последовательно по строкам и столбцам записываются значения яркости пикселов электронного изображения в момент времени, определяемый управляющим сигналом записи, поступающим на управляющий вход записи. По управляющему сигналу считывания, поступающему на его управляющий вход считывания, на выход блока поочередно, с первого до последнего блока, считываются блоки электронного изображения, каждый из которых состоит из матрицы значений яркости пикселов, состоящей из N строк и N столбцов. Значения пикселов блока электронного изображения считываются по M-разрядной шине с параллельной передачей. Схема блока разделения электронного изображения 1.1 известна и приведена, например, в книге: О.Н.Лебедев, А.К.Марцинкявичус, Э.К.Багданскис, Р.Л.Пошюнас, Б.В.Драган и др. Микросхемы памяти. ЦАП и АЦП. - М.: КубК-а, 1996, стр.91-94, рис.3.9.

Блок преобразования Фурье 1.2 предназначен для выполнения преобразования Фурье блока электронного изображения. Над N×N значениями яркости пикселов блока электронного изображения в блоке преобразования Фурье 1.2 выполняют преобразование Фурье, в результате которого формируется N×N значений коэффициентов Фурье этого блока. Схема блока преобразования Фурье 1.2 известна и приведена, например, в патенте РФ 2125290, Арифметическое устройство для выполнения быстрого преобразования Хартли-Фурье. Он может быть реализован, например, на программируемых логических схемах Xilinx XCV100-4 серии Virtex, содержащей 100 тыс. вентилей (см. Каталог электронных изделий фирмы Xilinx, 2003, стр.129-133).

Первый квантователь 1.3 предназначен для квантования значений коэффициентов Фурье блока электронного изображения. В первый квантователь 1.3 предварительно записывают N×N значений, обратных соответствующим значениям коэффициентов квантования коэффициентов Фурье блока электронного изображения. Величину каждого значения, обратного соответствующему значению коэффициента квантования, определяют как положительное число в диапазоне значений от нулевого до единичного значения, на которое умножают значение соответствующего коэффициента Фурье блока электронного изображения при его квантовании. Значения коэффициентов квантования блока электронного изображения размером 8×8 пикселов в соответствии с алгоритмом сжатия электронных изображений MPEG-2 описаны, например, в книге Д.Ватолин, А.Ратушняк, М.Смирнов, В.Юкин, Методы сжатия данных. Устройство архиваторов, сжатие изображений и видео. - М.: ДИАЛОГ-МИФИ, 2002, стр.308, и представлены на фигуре 4. Коэффициенты Фурье блока электронного изображения нумеруют с первого по (N×N)-й. Порядок нумерации коэффициентов Фурье блока электронного изображения описан, например, в книге Д.Ватолин, А.Ратушняк, М.Смирнов, В.Юкин, Методы сжатия данных. Устройство архиваторов, сжатие изображений и видео. - М.: ДИАЛОГ-МИФИ, 2002, стр.309, и для блока размером 8×8 показан на фигуре 5.

Первый квантователь 1.3, представленный на фигуре 6, состоит из блока памяти 1.3.1, умножителя (MPL) 1.3.2, счетчика 1.3.3 и коммутатора (MX) 1.3.4. M-разрядный информационный вход первого квантователя 1.3, реализованный в виде шины с параллельной передачей, является информационным входом “коэффициенты Фурье” (Х1) умножителя 1.3.2. Группа N×N выходов блока памяти 1.3.1, реализованных в виде M-разрядных шин с параллельной передачей, подключена к группе N×N соответствующих информационных входов (Х1, X2, …, XN×N) коммутатора 1.3.4. Выход (Y) коммутатора 1.3.4, реализованный в виде M-разрядной шины с параллельной передачей, подключен к M-разрядному информационному входу “обратные значения коэффициентов квантования” (X2) умножителя 1.3.2. Выход счетчика 1.3.3, реализованный в виде K-разрядной шины с параллельной передачей, подключен к управляющему входу (Адр.) коммутатора 1.3.4. Управляющие входы считывания блока памяти 1.3.1 и умножителя 1.3.2, а также информационный вход счетчика 1.3.3 объединены и являются управляющим входом считывания первого квантователя 1.3. Выход умножителя 1.3.2, реализованный в виде G-разрядной шины с параллельной передачей, где 2≤G≤M, является G-разрядным выходом первого квантователя 1.3.

Блок памяти 1.3.1 предназначен для хранения N×N значений, обратных соответствующим значениям коэффициентов квантования коэффициентов Фурье блока электронного изображения. Блок памяти 1.3.1 состоит из N×N одинаковых элементов памяти (ЭП) 1.3.1.1, 1.3.1.2, …, 1.3.1. N×N. В эти ЭП в соответствии с их номером предварительно записывают значения, обратные к соответствующим значениям коэффициентов квантования коэффициентов Фурье блока электронного изображения. Управляющие входы считывания ЭП 1.3.1.1, 1.3.1.2, …, 1.3.1. N×N являются управляющим входом считывания блока памяти 1.3.1. Схема ЭП 1.3.1.1, 1.3.1.2, …, 1.3.1. N×N известна и приведена, например, в книге А.А.Сикарев, О.Н.Лебедев, Микроэлектронные устройства формирования и обработки сложных сигналов. - М.: Радио и связь, 1983, стр.138, рис.5.28. Они могут быть реализованы, например, на микросхеме ПЗУ КМ1608РТ1 (см. Цифровые и аналоговые интегральные микросхемы: справочник / С.В.Якубовский, Л.И.Ниссельсон, В.И.Кулешова и др. Под ред. С.В.Якубовского. - М.: Радио и связь, 1989, стр.317).

Умножитель 1.3.2 предназначен для умножения значений коэффициентов Фурье блока электронного изображения на соответствующие им значения, обратные значению коэффициентов квантования коэффициентов Фурье блока электронного изображения. Умножитель 1.3.2 имеет информационный вход “коэффициенты Фурье” (вход записи Х1 первого сомножителя) и информационный вход “обратные значения коэффициентов квантования” (вход записи Х2 второго сомножителя). Перемножение значений, поступающих по этим информационным входам, и считывание результата перемножения на выход умножителя осуществляются по управляющему сигналу считывания, поступающему на вход управления считывания умножителя 1.3.2. Схема умножителя 1.3.2 известна и приведена, например, в книге: Г.И.Пухальский, Т.Я.Новосельцев, Проектирование дискретных устройств на интегральных микросхемах. - М.: Радио и связь, 1990, стр.152-157, рис.3.70. Умножитель 1.3.2 может быть реализован на микросхеме 1802ВР4.

Счетчик 1.3.3 предназначен для формирования управляющих сигналов, подключающих через коммутатор 1.3.4 выход выбранного из элементов памяти 1.3.1.1, 1.3.1.2, …, 1.3.1. N×N элемента памяти к информационному входу “обратные значения коэффициентов квантования” умножителя 1.3.2. Схема счетчика 1.3.3 известна и приведена, например, в книге А.А.Сикарев, О.Н.Лебедев, Микроэлектронные устройства формирования и обработки сложных сигналов. - М.: Радио и связь, 1983, стр.127, рис.5.18. Счетчик 1.3.3 может быть реализован, например, на микросхеме К155ИЕ2 (см. А.А.Сикарев, О.Н.Лебедев, Микроэлектронные устройства формирования и обработки сложных сигналов. - М.: Радио и связь, 1983, стр.126).

Коммутатор 1.3.4 предназначен для подключения в соответствии с формируемыми счетчиком 1.3.3 управляющими сигналами выхода выбранного из элементов памяти 1.3.1.1, 1.3.1.2, …, 1.3.1. N×N элемента памяти к информационному входу “обратные значения коэффициентов квантования” умножителя 1.3.2. Через коммутатор 1.3.4 на информационный вход “обратные значения коэффициентов квантования” умножителя 1.3.2 поочередно, с первого по (N×N)-й, считывают значения, обратные соответствующим значениям коэффициентов квантования коэффициентов Фурье блока электронного изображения. Схема коммутатора 1.3.4 известна и приведена, например, в книге А.А.Сикарев, О.Н.Лебедев, Микроэлектронные устройства формирования и обработки сложных сигналов. - М.: Радио и связь, 1983, стр.112, рис.5.11. Он может быть реализован, например, на микросхеме мультиплексора 555КП7 (см. Г.И.Пухальский, Т.Я.Новосельцев, Проектирование дискретных устройств на интегральных микросхемах. - М.: Радио и связь, 1990, стр.103-106, рис.3.10).

Кодер Хаффмана 1.4, представленный на фигуре 7, предназначен для кодирования N×N значений квантованных коэффициентов Фурье блока электронного изображения путем их замены на N×N предварительно установленные двоичные последовательности кода Хаффмана. Кодер Хаффмана 1.4 состоит из матрицы памяти (РТ) 1.4.1. Информационный вход (Адр.) матрицы памяти 1.4.1, реализованный в виде G-разрядной шины с параллельной передачей, является G-разрядным информационным входом кодера Хаффмана 1.4, а выход матрицы памяти 1.4.1, реализованный в виде Q-разрядной шины с параллельной передачей, является Q-разрядным выходом кодера Хаффмана 1.4. Управляющий вход считывания (Упр.) матрицы памяти 1.4.1 является управляющим входом считывания кодера Хаффмана 1.4.

В ячейки матрицы памяти 1.4.1 предварительно записывают двоичные последовательности кода Хаффмана. Адресами ячеек матрицы памяти 1.4.1 являются соответствующие предварительно записанным двоичным последовательностям кода Хаффмана значения квантованных коэффициентов Фурье блока электронного изображения. С выхода первого квантователя 1.3 на информационный вход (Адр.) матрицы памяти 1.4.1 поступает значение квантованного коэффициента Фурье блока электронного изображения, и с выхода матрицы памяти считывается соответствующая ему двоичная последовательность кода Хаффмана. Момент считывания определяется управляющим сигналом считывания, поступающим на управляющий вход считывания (Упр.) матрицы памяти 1.4.1. Схема матрицы памяти 1.4.1 известна и приведена, например, в книге А.А.Сикарев, О.Н.Лебедев, Микроэлектронные устройства формирования и обработки сложных сигналов. - М.: Радио и связь, 1983, стр.138, рис.5.28. Матрица памяти 1.4.1 может быть реализована, например, на микросхеме ПЗУ КМ1608РТ1 (см. Цифровые и аналоговые интегральные микросхемы: справочник / С.В.Якубовский, Л.И.Ниссельсон, В.И.Кулешова и др. Под ред. С.В.Якубовского. - М.: Радио и связь, 1989, стр.317).

Первый выделитель совпадающих последовательностей (ПВСП) 1.5, представленный на фигуре 8, предназначен для выделения совпадающих последовательностей из двоичных последовательностей кода Хаффмана блока электронного изображения, считываемых с выхода кодера Хаффмана 1.4, и двоичных последовательностей, входящих в одну из предварительно сформированных пар двоичных последовательностей, записанных в первый блок памяти пар последовательностей 1.6.

ПВСП 1.5 состоит из Q-разрядных компараторов 1.5.1, 1.5.2, …,1.5.S и блока объединения 1.5.S+1. Число S равно удвоенному числу предварительно сформированных пар двоичных последовательностей, записанных в первый блок памяти пар последовательностей 1.6. Первые входы разрядов компараторов 1.5.1, 1.5.2, …, 1.5.S реализованы в виде Q-разрядной шины с параллельной передачей. Одноименные первые входы разрядов компараторов 1.5.1, 1.5.2, …, 1.5.S объединены и являются Q-разрядным информационным входом “последовательность Хаффмана” ПВСП 1.5. Вторые входы Q разрядов компаратора 1.5.1 являются первым Q-разрядным информационным входом “последовательности пар” ПВСП 1.5, вторые входы Q разрядов компаратора 1.5.2 являются вторым Q-разрядным информационным входом “последовательности пар” ПВСП 1.5 и т.д. Выходы компараторов 1.5.1, 1.5.2, …, 1.5.S являются S-разрядным выходом “номер совпадения” ПВСП 1.5. Выходы компараторов 1.5.1, 1.5.2, …, 1.5.S также подключены к одноименным входам блока объединения 1.5.S+1, выход которого является выходом “наличие совпадения” ПВСП 1.5. Управляющие входы считывания компараторов 1.5.1, 1.5.2, …, 1.5.S объединены и являются управляющим входом считывания ПВСП 1.5.

Одинаковые компараторы 1.5.1, 1.5.2, …, 1.5.S предназначены для выявления совпадающих двоичных последовательностей кода Хаффмана блока электронного изображения и S двоичных последовательностей, входящих в одну из предварительно сформированных пар двоичных последовательностей. При выявлении такого совпадения на выходе соответствующего компаратора в момент времени, определяемый управляющим сигналом считывания на его управляющем входе считывания, появляется единичный двоичный сигнал. Схема компараторов 1.5.1, 1.5.2, …, 1.5.S известна и приведена, например, в книге А.А.Сикарев, О.Н.Лебедев, Микроэлектронные устройства формирования и обработки сложных сигналов. - М.: Радио и связь, 1983, стр.108, рис.5.6. Они могут быть реализованы, например, на микросхеме К564ИП2 (см. А.А.Сикарев, О.Н.Лебедев, Микроэлектронные устройства формирования и обработки сложных сигналов. - М.: Радио и связь, 1983, стр.109).

Схема объединения 1.5.S+1 предназначена для объединения сигналов с выходов компараторов 1.5.1, 1.5.2, …, 1.5.S. При срабатывании любого из компараторов на выходе схемы объединения 1.5.S+1 появляется единичный двоичный сигнал. Схема объединения 1.5.S+1 известна как логический элемент “ИЛИ” и приведена, например, в книге: Г.И.Пухальский, Т.Я.Новосельцев, Проектирование дискретных устройств на интегральных микросхемах. - М.: Радио и связь, 1990, стр.33-36, рис.2.1. Она может быть реализована, например, на микросхеме 155ЛЕ7 (см. Г.И.Пухальский, Т.Я. Новосельцев, Проектирование дискретных устройств на интегральных микросхемах. - М.: Радио и связь, 1990, стр.39, рис.2.3).

Первый блок памяти пар последовательностей (ПБППП) 1.6 предназначен для хранения двоичных последовательностей предварительно сформированных пар. ПБППП 1.6 имеет S Q-разрядных выходов, нумеруемых с первого по S-й. Считывание двоичных последовательностей предварительно сформированных пар с выхода ПБППП 1.6 определяется управляющим сигналом считывания, поступающим на его управляющий вход считывания. Схема ПБППП 1.6 известна и приведена, например, в книге А.А.Сикарев, О.Н.Лебедев, Микроэлектронные устройства формирования и обработки сложных сигналов. - М.: Радио и связь, 1983, стр.138, рис.5.28. Он может быть реализован на микросхеме ПЗУ КМ1608РТ1 (см. Цифровые и аналоговые интегральные микросхемы: справочник / С.В.Якубовский, Л.И.Ниссельсон, В.И.Кулешова и др. Под ред С.В.Якубовского. - М.: Радио и связь, 1989, стр.317).

Первый счетчик совпадающих последовательностей (ПССП) 1.7 предназначен для подсчета числа N1 совпадающих последовательностей из двоичных последовательностей кода Хаффмана блока электронного изображения и двоичных последовательностей, входящих в одну из предварительно сформированных пар двоичных последовательностей. Подсчитанное число N1 считывается с выхода ПССП 1.7, реализованного в виде R-разрядной шины с параллельной передачей, где R≥log2(N×N). Схема ПССП 1.7 известна и приведена, например, в книге А.А.Сикарев, О.Н.Лебедев, Микроэлектронные устройства формирования и обработки сложных сигналов. - М.: Радио и связь, 1983, стр.127, рис.5.18. Он может быть реализован, например, на микросхеме К155ИЕ2 (см. А.А.Сикарев, О.Н.Лебедев, Микроэлектронные устройства формирования и обработки сложных сигналов. - М.: Радио и связь, 1983, стр.126).

Второй квантователь 1.8, представленный на фигуре 9, предназначен для квантования значений яркости пикселов блока электронного изображения. Во второй квантователь 1.8 предварительно записывают N×N значений коэффициентов квантования яркости пикселов блока электронного изображения. Порядок установления значений коэффициентов квантования яркости пикселов блока электронного изображения описан, например, в книге A.Dilgin, P.Sementilli, М.Marcellin, Progressive image coding using trellis coded quantization / IEEE Trans. on Image Processing. №11, 1997, p.1240-1253.

Второй квантователь 1.8 состоит из блока памяти 1.8.1, умножителя (MPL) 1.8.2, счетчика 1.8.3 и коммутатора (MX) 1.8.4. M-разрядный информационный вход второго квантователя 1.8 является M-разрядным информационным входом “значения яркости пикселов” (вход Х1) умножителя 1.8.2. Группа N×N выходов блока памяти 1.8.1, реализованных в виде M-разрядных шин с параллельной передачей, подключена к группе N×N соответствующих информационных входов (Х1, X2, …,XN×N) коммутатора 1.8.4. M-разрядный выход (Y) коммутатора 1.8.4 подключен к M-разрядному информационному входу “значения коэффициентов квантования” (Х2) умножителя 1.8.2. Выход счетчика 1.8.3, реализованный в виде K-разрядной шины с параллельной передачей, подключен к управляющему входу (Адр.) коммутатора 1.8.4. Управляющие входы считывания блока памяти 1.8.1 и умножителя 1.8.2, а также информационный вход счетчика 1.8.3 объединены и являются управляющим входом считывания второго квантователя 1.8. Выход умножителя 1.8.2, реализованный в виде G-разрядной шины с параллельной передачей, где G≤М, является G-разрядным выходом второго квантователя 1.8.

Блок памяти 1.8.1 предназначен для хранения N×N значений коэффициентов квантования яркости пикселов блока электронного изображения. Схема блока памяти 1.8.1 аналогична схеме блока памяти 1.3.1, описанной ранее.

Умножитель 1.8.2 предназначен для умножения значений яркости пикселов блока электронного изображения на соответствующие им значения коэффициентов квантования яркости пикселов. Схема умножителя 1.8.2 аналогична схеме умножителя 1.3.2, описанной ранее.

Счетчик 1.8.3 предназначен для формирования управляющих сигналов, подключающих через коммутатор 1.8.4 выход выбранного из элементов памяти 1.8.1.1, 1.8.1.2, …, 1.8.1. N×N элемента памяти к информационному входу “значение коэффициентов квантования” умножителя 1.8.2. Схема счетчика 1.8.3 аналогична схеме счетчика 1.3.3, описанной ранее.

Коммутатор 1.8.4 предназначен для подключения в соответствии с формируемыми счетчиком 1.8.3 управляющими сигналами выхода выбранного из элементов памяти 1.8.1.1, 1.8.1.2, …, 1.8.1. N×N элемента памяти к информационному входу “значение коэффициентов квантования” умножителя 1.8.2. Схема коммутатора 1.8.4 аналогична схеме коммутатора 1.3.4, описанной ранее.

Формирователь последовательности блока (ФПБ) 1.9 предназначен для формирования двоичной последовательности блока электронного изображения путем конкатенации двоичных последовательностей квантованных значений яркости пикселов этого блока. В ФПБ 1.9 последовательно записывают, с первой до (N×N)-й, двоичные последовательности квантованных значений яркости пикселов блока электронного изображения таким образом, чтобы начало очередной двоичной последовательности записывалось вплотную к концу предыдущей двоичной последовательности. Последовательной записью двоичных последовательностей квантованных значений яркости пикселов блока электронного изображения управляют с помощью сигналов управления записью, поступающих на управляющий вход записи ФПБ 1.9. Последовательным считыванием двоичной последовательности блока электронного изображения управляют с помощью сигналов управления считыванием, поступающих на управляющий вход считывания ФПБ 1.9.

ФПБ 1.9 физически является регистром сдвига с последовательной записью и последовательным считыванием двоичной последовательности. Схема ФПБ 1.9 известна и описана, например, в книге А.В.Асосков, М.А.Иванов, А.А.Мирский и др. Поточные шифры. - М.: КУДИЦ-ОБРАЗ, 2003, стр.174-180, рис.5.5. Он может быть реализован, например, на микросхеме К155ИР8 (см. Цифровые и аналоговые интегральные микросхемы: справочник / С.В.Якубовский, Л.И.Ниссельсон, В.И.Кулешова и др. Под ред. СВ. Якубовского. - М: Радио и связь, 1989, стр.50).

Формирователь аутентификатора блока (ФАБ) 1.10, представленный на фигуре 10, предназначен для формирования аутентификатора блока электронного изображения. ФАБ 1.10 состоит из переключателей 1.10.1 и 1.10.4, регистров 1.10.2 и 1.10.5, сумматоров 1.10.3, 1.10.6 и 1.10.7, электронного ключа 1.10.8, ждущего мультивибратора 1.10.9 и генератора импульсов 1.10.10. Информационный вход “последовательность блока” ФАБ 1.10 является информационным входом “последовательность блока” переключателя 1.10.1, информационный вход “сигнал обратной связи” которого подключен к выходу сумматора 1.10.3. Информационный вход “ключ аутентификации” ФАБ 1.10 является информационным входом “ключ аутентификации” переключателя 1.10.4, информационный вход “сигнал обратной связи” которого подключен к выходу сумматора 1.10.6. Выход ждущего мультивибратора 1.10.9 подключен к входу генератора импульсов 1.10.10, выход которого подключен к управляющим входам “тактовые импульсы” регистров 1.10.2 и 1.10.5, информационные входы которых подключены соответственно к выходам переключателей 1.10.1 и 1.10.4. Первые входы сумматоров 1.10.7 и 1.10.3 объединены и подключены к выходу “рекуррентная последовательность” регистра 1.10.2. Второй вход сумматора 1.10.7 и первый вход сумматора 1.10.6 объединены и подключены к выходу “рекуррентная последовательность” регистра 1.10.5. Второй вход сумматора 1.10.3 подключен к выходу “сдвинутая последовательность” регистра 1.10.2, второй вход сумматора 1.10.6 подключен к выходу “сдвинутая последовательность” регистра 1.10.5. Выход сумматора 1.10.7 подключен к информационному входу электронного ключа 1.10.8, выход которого является выходом ФАБ 1.10. Управляющий вход считывания ФАБ 1.10 является управляющим входом считывания соответственно переключателей 1.10.1, 1.10.4, ждущего мультивибратора 1.10.9 и электронного ключа 1.10.8.

Переключатель 1.10.1 предназначен для первоначального подключения информационного входа “последовательность блока” ФАБ 1.10 к информационному входу регистра 1.10.2 для записи в него последовательности блока электронного изображения и последующего подключения информационного входа регистра 1.10.2 к выходу сумматора 1.10.3. Схема такого переключателя известна и приведена, например, в книге В.Л.Шило, Популярные микросхемы КМОП. Справочник. - М.: Ягуар, 1993, стр.22. Переключатель 1.10.4 предназначен для первоначального подключения информационного входа “ключ аутентификации” ФАБ 1.10 к информационному входу регистра 1.10.5 для записи в него последовательности секретного ключа аутентификации и последующего подключения информационного входа регистра 1.10.5 к выходу сумматора 1.10.6. Схема переключателя 1.10.4 аналогична, например, схеме переключателя 1.10.1, описанной ранее.

Регистры 1.10.2 и 1.10.5 аналогичны и предназначены для сдвига под управлением тактовых импульсов, поступающих на их управляющие входы “тактовые импульсы”, записанных в них последовательности блока электронного изображения и последовательности секретного ключа аутентификации соответственно. Схемы регистров известны и описаны, например, в книге А.В.Асосков, М.А.Иванов, А.А.Мирский и др. Поточные шифры. - М.: КУДИЦ-ОБРАЗ, 2003, стр.174-180, рис.5.5. Они могут быть реализованы, например, на микросхеме К155ИР2 (см. Цифровые и аналоговые интегральные микросхемы: справочник /С.В.Якубовский, Л.И.Ниссельсон, В.И.Кулешова и др. Под ред. С.В.Якубовского. - М.: Радио и связь, 1989, стр.50).

Одинаковые сумматоры 1.10.3 и 1.10.6 предназначены для суммирования по модулю 2 двоичных последовательностей, поступающих с выходов “рекуррентная последовательность” и “сдвинутая последовательность” регистров 1.10.2 и 1.10.5 соответственно. Схема сумматоров известна и приведена, например, в книге А.А.Сикарев, О.Н.Лебедев, Микроэлектронные устройства формирования и обработки сложных сигналов. - М.: Радио и связь, 1983, стр.108, рис.5.5. Они могут быть реализованы, например, на микросхеме КМ155ИМ3 (см. Цифровые и аналоговые интегральные микросхемы: справочник / С.В.Якубовский, Л.И.Ниссельсон, В.И.Кулешова и др. Под ред. С.В.Якубовского. - М.: Радио и связь, 1989, стр.50).

Сумматор 1.10.7 предназначен для суммирования по модулю 2 двоичных последовательностей, поступающих с выходов “рекуррентная последовательность” регистров 1.10.2 и 1.10.5. Выходной сигнал сумматора 1.10.7 является аутентификатором блока электронного изображения. Схема сумматора 1.10.7 аналогична, например, схеме сумматора 1.10.3, описанной ранее.

Электронный ключ 1.10.8 предназначен для считывания аутентификатора блока электронного изображения с выхода сумматора 1.10.7 на выход ФАБ 1.10 при поступлении на управляющий вход считывания данного электронного ключа управляющего сигнала считывания. По физической сущности электронный ключ 1.10.8 представляет собой элементарный управляемый переключатель. Схема электронного ключа 1.10.8 известна и приведена, например, в книге В.Л.Шило, Популярные микросхемы КМОП, справочник. - М.: Ягуар, 1993, стр.22.

Ждущий мультивибратор 1.10.9 предназначен для формирования сигнала запуска, который запускает генератор импульсов 1.10.10 при появлении на управляющем входе считывания ждущего мультивибратора 1.10.9 соответствующего сигнала управления. Схема ждущего мультивибратора 1.10.9 известна и приведена, например, в книге А.С Партин, В.Г. Борисов, Введение в цифровую технику. - М.: Радио и связь, 1987, стр.13, рис.13. Он может быть реализован, например, на микросхеме К155ЛА3 (см. А.С.Партин, В.Г.Борисов, Введение в цифровую технику. - М.: Радио и связь, 1987, стр.15).

Генератор импульсов 1.10.10 предназначен для формирования последовательности тактовых импульсов, предназначенных для сдвига последовательности блока электронного изображения и последовательности секретного ключа аутентификации в регистрах 1.10.2 и 1.10.5 соответственно. Схема генератора импульсов 1.10.10 известна и приведена, например, в книге А.С.Партин, В.Г.Борисов, Введение в цифровую технику. - М.: Радио и связь, 1987, стр.13, рис.12. Он может быть реализован, например, на микросхеме К155ЛА3 (см. А.С.Партин, В.Г.Борисов, Введение в цифровую технику. - М.: Радио и связь, 1987, стр.13).

Первый блок памяти ключа аутентификации 1.11 предназначен для хранения значения секретного ключа аутентификации. Схема первого блока памяти ключа аутентификации 1.11 известна и приведена, например, в книге А.А.Сикарев, О.Н.Лебедев, Микроэлектронные устройства формирования и обработки сложных сигналов. - М.: Радио и связь, 1983, стр.138, рис.5.28. Он может быть реализован на микросхеме ПЗУ КМ1608РТ1 (см. Цифровые и аналоговые интегральные микросхемы: справочник / С.В.Якубовский, Л.И.Ниссельсон, В.И.Кулешова и др. Под ред. С.В.Якубовского. - М.: Радио и связь, 1989, стр.317).

Формирователь цифрового водяного знака блока (ФЦВЗБ) 1.12, представленный на фигуре 11, предназначен для формирования цифрового водяного знака блока электронного изображения. Для этого в него через информационный вход “аутентификатор блока” ФЦВЗБ 1.12 с выхода формирователя аутентификатора блока 1.10 считывают аутентификатор блока электронного изображения и через R-разрядный информационный вход “число совпадений” считывают число совпадающих последовательностей с выхода ПССП 1.7, равное N1. В двоичную последовательность цифрового водяного знака блока электронного изображения записывают первые N1 бит его аутентификатора, а оставшиеся биты аутентификатора блока электронного изображения отбрасывают. ФЦВЗБ 1.12 состоит из регистра сдвига (RG) 1.12.1, электронных ключей (ЭК) 1.12.2 и 1.12.5, счетчиков (СТ) 1.12.3 и 1.12.6 и генератора импульсов 1.12.4.

Информационный вход “аутентификатор блока” ФЦВЗБ 1.12 является информационным входом регистра сдвига 1.12.1, выход которого является выходом ФЦВЗБ 1.12. R-разрядный информационный вход "число совпадений" ФЦВЗБ 1.12 является управляющим входом установки коэффициента счета (Уст.) счетчика 1.12.6. Управляющий вход записи ФЦВЗБ 1.12 является управляющим входом записи счетчика 1.12.6, а также информационными входами электронного ключа 1.12.2 и счетчика 1.12.3. Выход электронного ключа 1.12.2 подключен к управляющему входу записи регистра сдвига 1.12.1. Выход счетчика 1.12.3 подключен к управляющему входу электронного ключа 1.12.2 и управляющему входу генератора импульсов 1.12.4, выход которого подключен к информационному входу счетчика 1.12.6 и информационному входу электронного ключа 1.12.5. Выход счетчика 1.12.6 подключен к управляющему входу электронного ключа 1.12.5, выход которого подключен к управляющему входу считывания регистра сдвига 1.12.1.

Регистр сдвига 1.12.1 предназначен для записи аутентификатора блока электронного изображения, поступающего на его информационный вход, и последующего считывания его первых N1 бит на выход. Запись осуществляется при поступлении на его управляющий вход записи управляющего сигнала записи, считывание осуществляется при поступлении на его управляющий вход считывания управляющего сигнала считывания. Схема регистра сдвига 1.12.1 известна и приведена, например, в книге А.А.Сикарев, О.Н.Лебедев, Микроэлектронные устройства формирования и обработки сложных сигналов. - М.: Радио и связь, 1983, стр.121, рис.5.16б. Он может быть реализован, например, на микросхеме К144ИР2 (см. А.А.Сикарев, О.Н.Лебедев, Микроэлектронные устройства формирования и обработки сложных сигналов. - М.: Радио и связь, 1983, стр.122).

Электронный ключ 1.12.2 предназначен для подключения управляющего сигнала, поступающего на управляющий вход записи ФЦВЗБ 1.12 к управляющему входу записи регистра сдвига 1.12.1. В течение передачи по управляющему входу записи ФЦВЗБ 1.12 N×N импульсов на управляющий вход электронного ключа 1.12.2 с выхода счетчика 1.12.3 поступает управляющий сигнал, разрешающий запись в регистр сдвига 1.12.1. Схема электронного ключа 1.12.2 известна и приведена, например, в книге В.Л.Шило, Популярные цифровые микросхемы. Справочник. - М.: Радио и связь, 1987, стр.226, рис.2.27.

Счетчик 1.12.3 предназначен для подсчета N×N импульсов, поступающих на его информационный вход. После подсчета N×N тактовых импульсов сигнал на выходе счетчика 1.12.3 меняется с разрешающего на запрещающий прохождение импульсов через электронный ключ 1.12.2, одновременно этот выходной сигнал поступает на вход генератора импульсов 1.12.4, разрешая генерацию импульсов. Схема счетчика 1.12.3 известна и приведена, например, в книге В.Л.Шило, Популярные цифровые микросхемы. Справочник. - М.: Радио и связь, 1987, стр.90, рис.1.67.

Генератор импульсов 1.12.4 предназначен для формирования на его выходе последовательности тактовых импульсов, которые подсчитываются счетчиком 1.12.6 и одновременно поступают на информационный вход электронного ключа 1.12.5. Генерация импульсов начинается с момента поступления сигнала с выхода счетчика 1.12.3 на вход генератора импульсов 1.12.4. Схема генератора импульсов известна и приведена, например, в книге А.С.Партин, В.Г.Борисов, Введение в цифровую технику. - М.: Радио и связь, 1987, стр.13, рис.12. Он может быть реализован, например, на микросхеме К155ЛА3 (см. А.С.Партин, В.Г.Борисов, Введение в цифровую технику. - М.: Радио и связь, 1987, стр.13).

Электронный ключ 1.12.5 предназначен для подключения тактовых импульсов с выхода генератора импульсов 1.12.4 на управляющий вход считывания регистра 1.12.1 в течение времени, когда на управляющий вход электронного ключа 1.12.5 с выхода счетчика 1.12.6 поступает сигнал разрешения их прохождения. Схема электронного ключа 1.12.5 аналогична, например, схеме электронного ключа 1.12.2, описанной ранее.

Счетчик 1.12.6 предназначен для подсчета N1 тактовых импульсов, поступающих на его информационный вход. В течение подсчета N1 тактовых импульсов с выхода счетчика 1.12.6 на управляющий вход электронного ключа 1.12.5 поступает разрешающий сигнал. Число подлежащих подсчету N1 тактовых импульсов записывается в счетчик 1.12.6 через его вход установки коэффициента счета, реализованный в виде R-разрядной шины с параллельной передачей, и записывается в него при поступлении управляющего сигнала записи на его управляющий вход записи. Информационный вход счетчика 1.12.6 работает в режиме “вычитающего входа”, и при поступлении на информационный вход счетчика очередного тактового импульса из записанного в счетчик числа N1 вычитается единица. При достижении счета тактовых импульсов сигнал разрешения на выходе счетчика 1.12.6 меняется на сигнал запрета прохождения тактовых импульсов через электронный ключ 1.12.5. Схема счетчика 1.12.6 известна и приведена, например, в книге В.Л.Шило, Популярные цифровые микросхемы. Справочник. - М.: Радио и связь, 1987, стр.90, рис.1.67.

Сумматор 1.13 предназначен для суммирования по модулю 2 последовательности секретного ключа встраивания, поступающей с выхода первого блока памяти ключа встраивания 1.14 на вход “ключ встраивания”, и последовательности цифрового водяного знака блока электронного изображения, поступающей с выхода ФЦВЗБ 1.12 на вход “ЦВЗ блока” с образованием на выходе сумматора 1.13 суммированного цифрового водяного знака блока электронного изображения. Схема сумматора 1.13 известна и приведена, например, в книге А.А.Сикарев, О.Н.Лебедев, Микроэлектронные устройства формирования и обработки сложных сигналов. - М.: Радио и связь, 1983, стр.108, рис.5.5. Он может быть реализован, например, на микросхеме КМ155ИМ3 (см. Цифровые и аналоговые интегральные микросхемы: справочник / С.В.Якубовский, Л.И.Ниссельсон, В.И.Кулешова и др. Под ред. С.В.Якубовского. - М.: Радио и связь, 1989, стр.50).

Первый блок памяти ключа встраивания (ПБПКВ) 1.14 предназначен для хранения и считывания значения секретного ключа встраивания в виде двоичной последовательности. Схема ПБПКВ 1.14 известна и приведена, например, в книге А.А.Сикарев, О.Н.Лебедев, Микроэлектронные устройства формирования и обработки сложных сигналов. - М.: Радио и связь, 1983, стр.138, рис.5.28. Он может быть реализован на микросхеме ПЗУ КМ1608РТ1 (см. Цифровые и аналоговые интегральные микросхемы: справочник / С.В.Якубовский, Л.И.Ниссельсон, В.И.Кулешова и др. Под ред. С.В.Якубовского. - М.: Радио и связь, 1989, стр.317).

Блок встраивания цифрового водяного знака (БВЦВЗ) 1.15, представленный на фигуре 12, предназначен для встраивания суммированного цифрового водяного знака блока электронного изображения в этот же блок. БВЦВЗ 1.15 состоит из регистров сдвига (RG) 1.15.1 и 1.15.3, блока регистров 1.15.2, мультиплексора (MX) 1.15.4, блока переключений 1.15.5, параллельно/последовательного регистра (RG) 1.15.6 и блока выбора 1.15.7. Вход регистра сдвига 1.15.1, реализованный в виде Q-разрядной шины с параллельной передачей, является Q-разрядным информационным входом “последовательность Хаффмана” БВЦВЗ 1.15, информационный вход блока регистров 1.15.2, реализованный в виде S-разрядной шины с параллельной передачей, является S-разрядным информационным входом “номер совпадения” БВЦВЗ 1.15, информационный вход регистра сдвига 1.15.3 является информационным входом “наличие совпадения” БВЦВЗ 1.15. S Q-разрядных информационных входов блока выбора 1.15.7 являются соответствующими Q-разрядными информационными входами “последовательности пар” БВЦВЗ 1.15. Управляющий вход “выбор младшего разряда адреса” (A1) мультиплексора 1.15.4 является информационным входом “суммированный ЦВЗ” БВЦВЗ 1.15. Управляющий вход “выбор старших разрядов адреса” мультиплексора 1.15.4 (A2, A3, …, AS+1), реализованный в виде S-разрядной шины с параллельной передачей, подключен к S-разрядному выходу блока регистров 1.15.2. Первый информационный вход блока переключений 1.15.5, реализованный в виде Q-разрядной шины с параллельной передачей, подключен к выходу регистра сдвига 1.15.1. Выход мультиплексора 1.15.4, реализованный в виде Q-разрядной шины с параллельной передачей, подключен к второму информационному входу блока переключений 1.15.5. Выход блока выбора 1.15.7, реализованный в виде Q-разрядной шины с параллельной передачей, подключен к Q-разрядному информационному входу мультиплексора 1.15.4. Управляющий вход блока переключений 1.15.5 подключен к выходу регистра сдвига 1.15.3. Выход блока переключений 1.15.5, реализованный в виде Q-разрядной шины с параллельной передачей, подключен к информационному входу параллельно/последовательного регистра 1.15.6, выход которого является выходом БВЦВЗ 1.15. Управляющий вход записи БВЦВЗ 1.15 является управляющим входом записи регистров сдвига 1.15.1, 1.15.3, блока регистров 1.15.2 и параллельно/последовательного регистра 1.15.6. Управляющий вход считывания БВЦВЗ 1.15 является управляющим входом считывания регистров сдвига 1.15.1, 1.15.3, блока регистров 1.15.2 и параллельно/последовательного регистра 1.15.6.

Регистр сдвига 1.15.1 предназначен для записи двоичных последовательностей кода Хаффмана блока электронного изображения, поступающих на его информационный вход, и последующего их считывания на выход. Запись осуществляется при поступлении на его управляющий вход записи управляющего сигнала записи, считывание осуществляется при поступлении на его управляющий вход считывания управляющего сигнала считывания. Схема регистра сдвига 1.15.1 известна и приведена, например, в книге А.А.Сикарев, О.Н.Лебедев, Микроэлектронные устройства формирования и обработки сложных сигналов. - М.: Радио и связь, 1983, стр.121, рис.5.16б. Он может быть реализован, например, на микросхеме К144ИР2 (см. А.А.Сикарев, О.Н.Лебедев, Микроэлектронные устройства формирования и обработки сложных сигналов. - М.: Радио и связь, 1983, стр.122).

Блок регистров 1.15.2 предназначен для записи номеров совпавших последовательностей кода Хаффмана блока электронного изображения, поступающих на его информационный вход, и последующего их считывания на выход. Запись осуществляется при поступлении на его управляющий вход записи сигнала записи, считывание осуществляется при поступлении на его управляющий вход считывания сигнала считывания. Блок регистров 1.15.2 состоит из S одинаковых регистров сдвига (RG) 1.15.2.1, 1.15.2.2, …, 1.15.2.S. Управляющие входы записи и управляющие входы считывания регистров сдвига 1.15.2.1, 1.15.2.2, …, 1.15.2.S подключены к соответствующим управляющим входам блока регистров 1.15.2. Схема регистров сдвига 1.15.2.1, 1.15.2.2, …, 1.15.2.S аналогична, например, схеме регистра сдвига 1.15.1, описанной ранее.

Регистр сдвига 1.15.3 предназначен для записи поступающей на его информационный вход “наличие совпадения” последовательности двоичных значений с одноименного выхода ПВСП 1.5 и последующего ее считывания на выход. Запись осуществляется при поступлении на его управляющий вход записи управляющего сигнала записи, считывание осуществляется при поступлении на его управляющий вход считывания управляющего сигнала считывания. Схема регистра сдвига 1.15.3 известна и приведена, например, в книге А.А.Сикарев, О.Н.Лебедев, Микроэлектронные устройства формирования и обработки сложных сигналов. - М.: Радио и связь, 1983, стр.121, рис.5.16б. Он может быть реализован, например, на микросхеме К144ИР2 (см. А.А.Сикарев, О.Н.Лебедев, Микроэлектронные устройства формирования и обработки сложных сигналов. - М.: Радио и связь, 1983, стр.122).

Мультиплексор 1.15.4 предназначен для выбора двоичной последовательности из пар двоичных последовательностей, поступающих на его Q-разрядный информационный вход. Выбор осуществляется в соответствии с адресными сигналами, состоящими из сигнала выбора младшего разряда адреса (A1), поступающего на управляющий вход "выбор младшего разряда адреса" мультиплексора 1.15.4, и сигналов выбора старших разрядов адреса (A2, A3, …, AS+1), поступающих на управляющий вход “выбор старших разрядов адреса” этого мультиплексора. Выбранная двоичная последовательность с выхода мультиплексора 1.15.4, реализованного в виде Q-разрядной шины с параллельной передачей, поступает на второй информационный вход блока переключений 1.15.5. Схема мультиплексора 1.15.4 известна и приведена, например, в книге: Г.И.Пухальский, Т.Я.Новосельцев, Проектирование дискретных устройств на интегральных микросхемах. - М: Радио и связь, 1990, стр.99-110, рис.3.8. Она может быть реализована, например, на микросхеме 555КП2 (см. Г.И.Пухальский, Т.Я.Новосельцев, Проектирование дискретных устройств на интегральных микросхемах. - М: Радио и связь, 1990, стр.105, рис.3.10).

Блок переключений 1.15.5 предназначен для подключения одного из своих двух информационных входов на выход в соответствии со значением управляющего сигнала, поступающего на его управляющий вход. Если управляющий сигнал имеет нулевое двоичное значение, то на выход подключается первый информационный вход блока переключений 1.15.5. Если управляющий сигнал имеет единичное двоичное значение, то на выход подключается второй информационный вход. Блок переключений 1.15.5 состоит из Q одинаковых управляемых переключателей (УП) 1.15.5.1, 1.15.5.2, …, 1.15.5.Q. Схема таких управляемых переключателей известна и приведена, например, в книге В.Л.Шило, Популярные микросхемы КМОП. Справочник. - М.: Ягуар, 1993, стр.22.

Параллельно/последовательный регистр 1.15.6 предназначен для преобразования параллельно считываемых двоичных сигналов на его Q-разрядном информационном входе в последовательный двоичный сигнал на его выходе. Запись в параллельно/последовательный регистр 1.15.6 выполняется при поступлении на его управляющий вход записи управляющего сигнала записи, а считывание - при поступлении на его управляющий вход считывания управляющего сигнала считывания. Схема параллельно/последовательного регистра известна и приведена, например, в книге А.А.Сикарев, О.Н.Лебедев, Микроэлектронные устройства формирования и обработки сложных сигналов. - М.: Радио и связь, 1983, стр.121, рис.5.16а. Он может быть реализован, например, на микросхеме К155ИР13 (см. А.А.Сикарев, О.Н.Лебедев, Микроэлектронные устройства формирования и обработки сложных сигналов. - М.: Радио и связь, 1983, стр.122).

Блок выбора 1.15.7 предназначен для выбора из S Q-разрядных информационных входов “последовательности пар” БВЦВЗ 1.15 в соответствии с сигналом на S-разрядном выходе блока регистров 1.15.2 и подключения выбранного Q-разрядного информационного входа “последовательности пар” БВЦВЗ 1.15 к Q-разрядному информационному входу мультиплексора 1.15.4. Блок выбора 1.15.7 состоит из S одинаковых модулей выбора 1.15.7.1, …, 1-15.7.S и Q одинаковых схем объединения 1.15.7.S+1, …, 1.15.7.S+Q. Q-разрядный информационный вход модуля выбора 1.15.7.1 подключен к первому Q-разрядному информационному входу “последовательности пар” БВЦВЗ 1.15 и так далее, Q-разрядный информационный вход модуля выбора 1.15.7.S подключен к S-му Q-разрядному информационному входу “последовательности пар” БВЦВЗ 1.15 и т.д. Управляющий вход модуля выбора 1.15.7.1 подключен к выходу регистра сдвига 1.15.2.1 блока регистров 1.15.2 и так далее, управляющий вход модуля выбора 1.15.7.S подключен к выходу регистра сдвига 1.15.2.S блока регистров 1.15.2. Первые выходы модулей выбора 1.15.7.1, …, 1.15.7.S подключены к одноименным входам схемы объединения 1.15.7.S+1 и так далее, Q-е выходы модулей выбора 1.15.7.1, …, 1.15.7.S подключены к одноименным входам схемы объединения 1.15.7.S+Q.

Каждый модуль выбора 1.15.7.1, …, 1.15.7.S состоит из Q электронных ключей (ЭК) 1.15.7.1.1, …, 1.15.7.1.Q, …, 1.15.7.S.1, …, 1.15.7.S.Q, предназначенных для подключения соответствующего разряда соответствующего Q-разрядного информационного входа “последовательности пар” БВЦВЗ 1.15. Информационные входы электронных ключей 1.15.7.1.1, …, 1.15.7.1.Q являются Q-разрядным информационным входом модуля выбора 1.15.7.1 и т.д. Соединенные между собой управляющие входы электронных ключей 1.15.7.1.1, …, 1.15.7.1.Q являются управляющим входом модуля выбора 1.15.7.1 и т.д. Схемы указанных электронных ключей аналогичны, например, схеме электронного ключа 1.12.2, описанной ранее.

Схема объединения 1.15.7.S+1 предназначена для объединения сигналов с выходов электронных ключей 1.15.7.1.1, …, 1.15.7.S.1 и подключения выходного сигнала на первый разряд Q-разрядного информационного входа мультиплексора 1.15.4 и так далее, схема объединения 1.15.7.S+Q предназначена для объединения сигналов с выходов Q-х в своем модуле выбора электронных ключей 1.15.7.1.Q, …, 1.15.7.S.Q и подключения выходного сигнала на Q-й разряд Q-разрядного информационного входа этого же мультиплексора. Схемы объединения 1.15.7.S+1, …, 1.15.7.S+Q аналогичны, например, схеме объединения 1.5.S+1, описанной ранее.

Блок передачи 1.16 предназначен для передачи заверенного цифровым водяным знаком электронного изображения по каналу передачи. Схема блока передачи 1.16 известна и описана, например, в книге: Защита информации в системах мобильной связи: учебное пособие для вузов / А.А.Чекалин, А.В.Заряев, С.В.Скрыль, В.А.Вохминцев и др. - 2-е изд., испр. и доп. - М.: Горячая линия - Телеком, 2005, стр.15, рис.1.2.2.

Блок приема 2.1 предназначен для приема из канала передачи электронного изображения. Схема блока приема 2.1 известна и описана, например, в книге Защита информации в системах мобильной связи: учебное пособие для вузов / А.А.Чекалин, А.В.Заряев, С.В.Скрыль, В.А.Вохминцев и др. - 2-е изд., испр. и доп. - М.: Горячая линия - Телеком, 2005, стр.15, рис.1.2.2.

Выделитель последовательностей Хаффмана принятого блока (ВПХПБ) 2.2, представленный на фигуре 13, предназначен для выделения из принятого электронного изображения двоичных последовательностей кода Хаффмана принятого блока электронного изображения.

ВПХПБ 2.2 состоит из регистра сдвига (RG) 2.2.1, блока совпадений 2.2.2, блока памяти 2.2.3, генератора импульсов (ГИ) 2.2.4, блока управления считыванием 2.2.5, счетчика (СТ) 2.2.6 и дешифратора (DT) 2.2.7. Вход регистра сдвига 2.2.1 является информационным входом ВПХПБ 2.2, выход этого регистра, реализованный в виде Q-разрядной шины с параллельной передачей, является Q-разрядным выходом ВПХПБ 2.2 и одновременно подключен к первой группе информационных входов блока совпадений 2.2.2. Выход блока памяти 2.2.3, реализованный в виде Q-разрядной шины с параллельной передачей, подключен к второй группе информационных входов блока совпадений 2.2.2. Выход генератора импульсов 2.2.4 подключен к информационному входу блока управления считыванием 2.2.5, выход которого соединен с управляющим входом считывания регистра сдвига 2.2.1. Выход блока совпадений 2.2.2, реализованный в виде Q-разрядной шины с параллельной передачей, подключен к группе управляющих входов блока управления считыванием 2.2.5. Информационный вход счетчика 2.2.6 является управляющим входом считывания ВПХПБ 2.2. Выход счетчика 2.2.6, реализованный в виде L-разрядной шины с параллельной передачей, где L=log2Q, подключен к одноименным входам дешифратора 2.2.7, выход которого, реализованный в виде Q-разрядной шины с параллельной передачей, подключен к группе управляющих входов блока памяти 2.2.3. Управляющий вход записи регистра сдвига 2.2.1, управляющие входы блока совпадений 2.2.2, генератора импульсов 2.2.4 и счетчика 2.2.6 являются управляющим входом записи ВПХПБ 2.2.