Область техники, к которой относится изобретение

Настоящее изобретение относится к процессорам и, в частности, выполняет итерационные арифметические операции повышенной точности в процессоре.

Предшествующий уровень техники

Обычные процессоры содержат одно и более арифметико-логических устройств, выполняющих итерационные операции, например деление, вычисление квадратного корня и трансцендентных операций (такие, как SIN, COS). Итерационные арифметические операции обычно выполняют до получения определенного результата, который имеет фиксированную, определенную точность. Поэтому операнды итерационно обрабатывают, чтобы обеспечить результат, имеющий полную точность, например, такой как целевая точность, точность соответствующего регистра или точность соответствующих исходных операнд. Например, Институт Инженеров по Электронике и радиотехнике (IEEE) определил стандарт IEEE 754, разъясняющий бинарные арифметические вычисления с плавающей точкой. Стандарт IEEE 754 описывает форматы чисел, основные операции, переносы и условия исключений, имеющие отношение к операциям с плавающей точкой одинарной и двойной точности.

Соответствующие стандарту IEEE 754 числа с плавающей точкой содержат три компоненты: знаковый бит, экспоненту и мантиссу. Мантисса дополнительно делится на целочисленную и дробную части. Биты соответствующие дробной части хранят закодированными. Для нормальных чисел целочисленная часть в неявном виде принимается равной 1. Соответствующие IEEE 754 числа одинарной точности представлены в виде знакового бита, 8 бит экспоненты и 23 бита дробной части, в то время как числа двойной точности представляются в виде знакового бита, 11 бит экспоненты и 52 битов дробной части. Таким образом, итерационные вычисления с числами, которые соответствуют IEEE 754, обеспечивают результирующую точность в 24 бита для операндов одинарной точности и точность в 53 бита для операндов двойной точности. Например, процессор, оснащенный арифметико-логическим устройством, соответствующим одинарной точности по IEEE 754, обеспечивает точность в 24 бита. Тем не менее, обычные приложения, такие как графические приложения OpenGL, не всегда требуют полной точности в 24 бита одинарной точности. По этой причине излишнее потребление энергии и циклов вычислений процессора имеют место при вычислении результатов с одинарной точностью в 24 бита, при этом самому приложению достаточно меньшей точности вычислений, чем полные вычисления стандартной точности, например вполне достаточно точности в 16 бит.

Некоторые из обычных процессоров обеспечивают результаты меньшей точности, чем точность целевого формата. Тем не менее, такие процессоры завершают итерационные арифметические операции раньше, чем целевой формат, только в тех случаях, когда исполняются операнды меньшей точности, чем целевой формат. Например, процессор двойной точности способен исполнять операции одинарной точности с операндами одинарной точности, обеспечивая результат одинарной точности, даже тогда, когда целевой формат регистра соответствует значению двойной точности. Таким образом, точность некоторых обычных арифметических вычислений зависит от точности исполняемого операнда, и, следовательно, полученные результаты имеют эквивалент полной точности, соответствующую операндам. В результате мощность и процессорные циклы излишне используются, производя вычисления повышенной точности тогда, когда некоторым из приложений она на самом деле не нужна.

Сущность изобретения

Согласно способам и устройствам, раскрытым в данном описании, процессор будет оснащен итерационным арифметико-логическим устройством (IALU) с контролируемой точностью, которое производит субточные результаты, т.е. результаты, имеющие точность меньше, чем полная точность. В одном или более вариантах осуществления IALU с контролируемой точностью содержит арифметико-логическую схему и схему контроля точности. Арифметико-логическая схема выполнена с возможностью итерационной обработки операндов первой точности для получения результата. Схема контроля точности выполнена с возможностью завершения обработки итерационного операнда, когда результат достигает запрограммированной второй точности, меньшей, чем первая точность. Именно поэтому операции полной точности, в сравнении с операциями уменьшенной точности, могут высчитать больше битов, чем на самом деле необходимо в конечном результате для получения округленного результата. Эти «округленные биты» обычно именуют защитными, округлыми и связанными битами. В одном варианте осуществления схема контроля точности заставляет арифметико-логическую схему завершить выполнение итерационного операнда в ответ на индикатор, полученный контрольной схемой. IALU с контролируемой точностью дополнительно содержит логику округления, выполненную с возможностью условного сокращения результата в наименее значащем бите (LSB) субточного результата, основанном на режиме округления, LSB и битов округления. В одном варианте осуществления логика округления выполнена с возможностью округления результата, выравниванием значения округления с LSB результата, и условного добавления выровненного значения округления к результату.

Таким образом, по меньшей мере, в одном варианте осуществления, субточные результаты получены в процессоре посредством итерационной обработки операндов первой точности для получения результата и завершения итерационной обработки, когда результат достигает запрограммированной второй точности, меньшей, чем первая точность. Таким образом, битовую ширину результатов подточности можно подогнать заполнением результата таким образом, что заполненный результат имеет битовую ширину, соответствующую первой точности.

В другом варианте осуществления, процессор содержит IALU с контролируемой точностью. Процессор дополнительно содержит элемент запоминающего устройства, выполненный с возможностью хранения запрограммированную вторую точность в виде фиксированного значения или как динамически изменяемое значение. Если запрограммированная вторая точность сохранена как динамически изменяемое значение, она может быть изменена соответствующими одной, либо более инструкциями, полученными процессором. IALU с контролируемой точностью выполнено с возможностью завершения итерационной обработки операндов в соответствие с индикатором, полученным процессором. В одном варианте осуществления, индикатор является флаговым битом, хранимым в регистре, содержащемся в процессоре.

Конечно, настоящее описание не ограничивается раскрытыми ранее признаками. Для специалиста в области техники будут очевидными дополнительные признаки при прочтении подробного описания и просмотра приложенных чертежей.

Перечень фигур чертежей

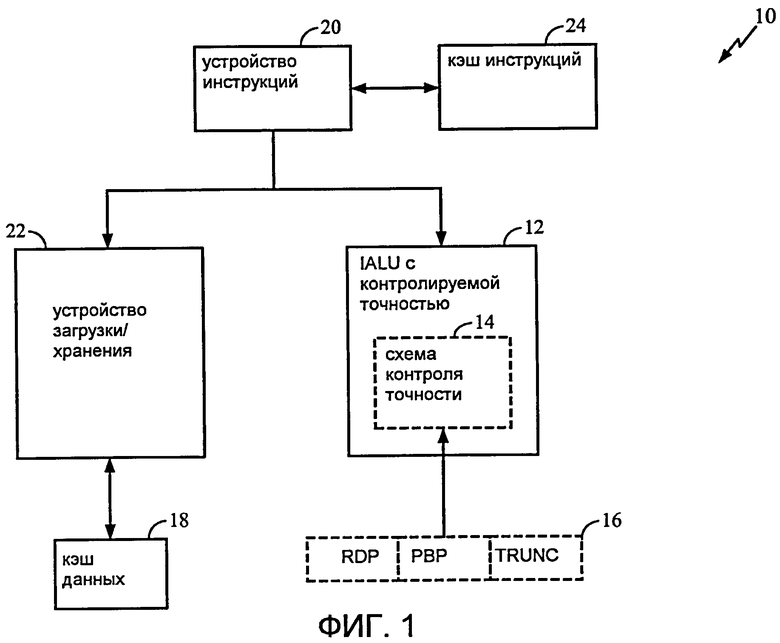

Фиг.1 изображает блок-схему одного варианта осуществления процессора, содержащего итерационное арифметико-логическое устройство (IALU) с контролируемой точностью.

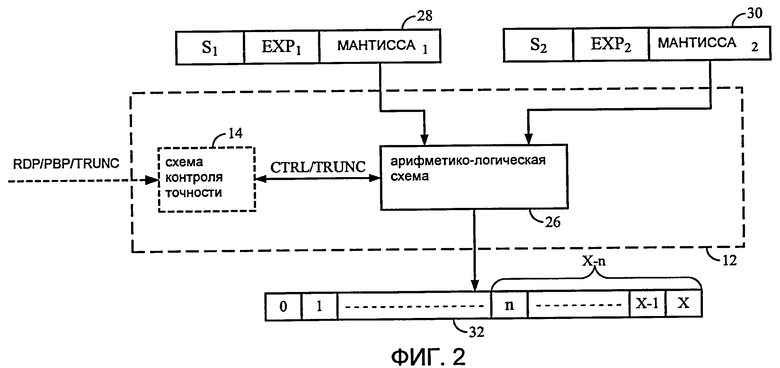

Фиг.2 изображает блок-схему одного варианта осуществления IALU с контролируемой точностью по фиг.1.

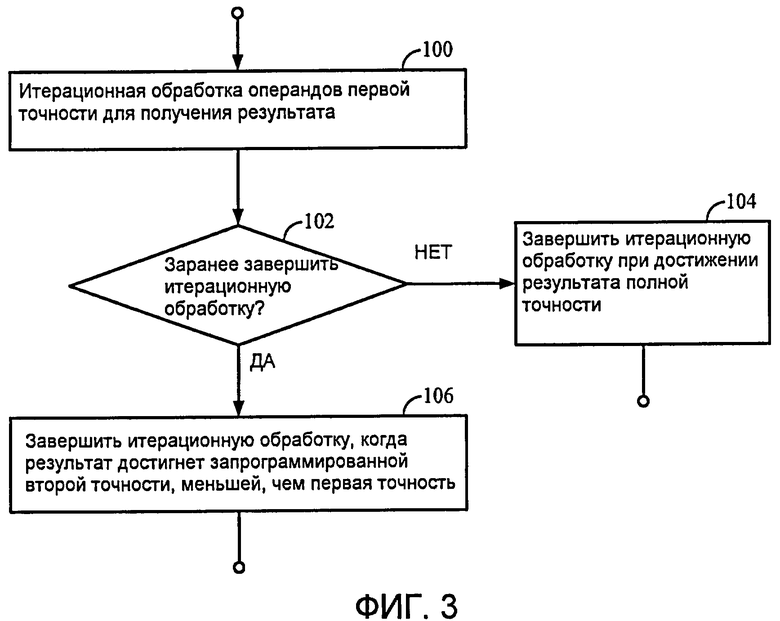

Фиг.3 иллюстрирует логическую схему последовательности операций одного варианта осуществления программной логики для выполнения итерационной арифметической операции.

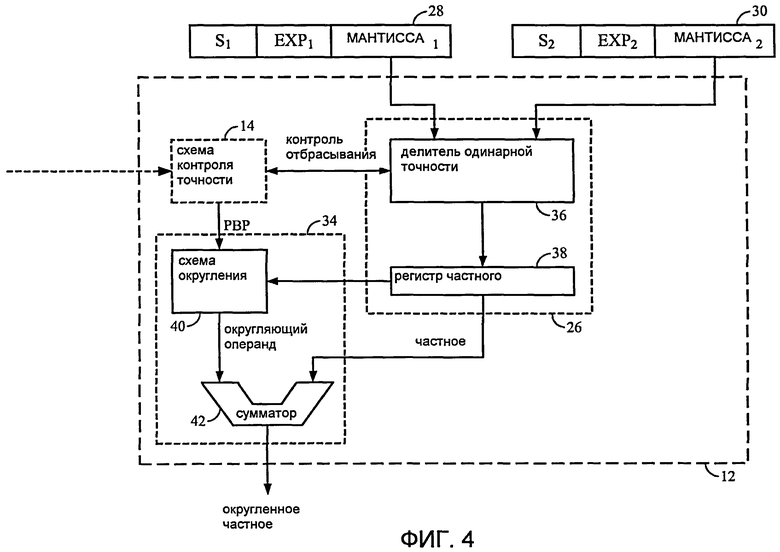

Фиг.4 иллюстрирует блок-схему одного варианта осуществления IALU с контролируемой точностью по фиг.1, дополнительно включающий схему округления.

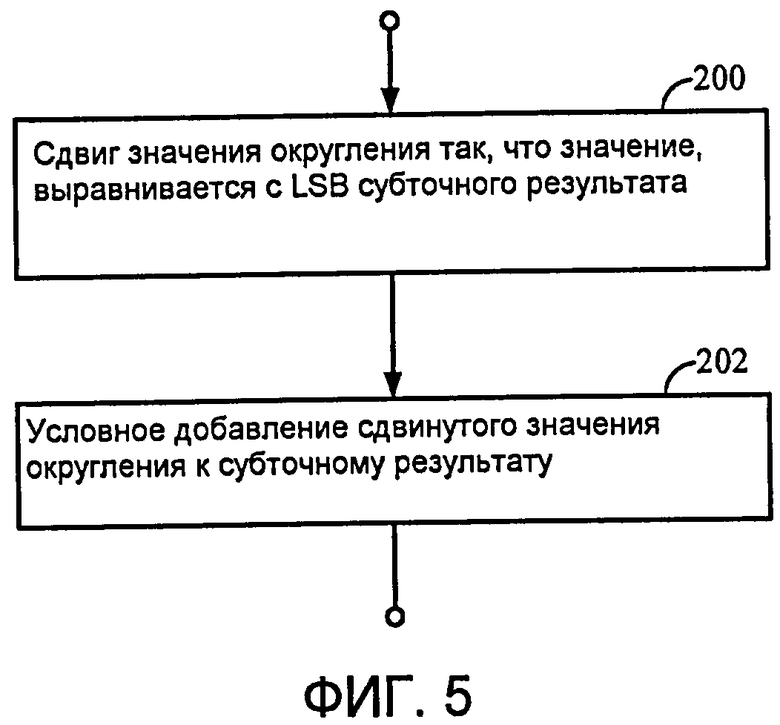

Фиг.5 иллюстрирует логическую схему последовательности операций одного варианта осуществления программной логики для округления субточного результата, полученного IALU с контролируемой точностью по фиг.4.

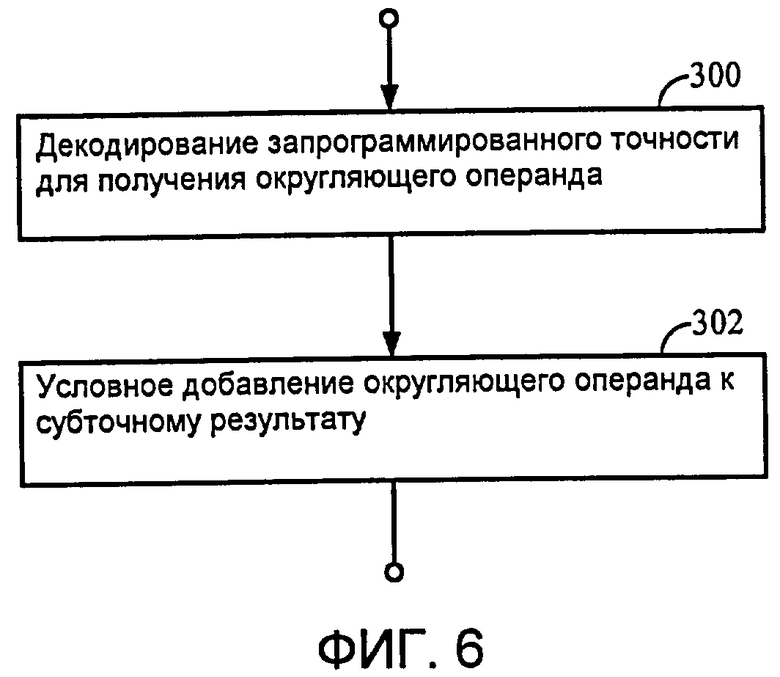

Фиг.6 иллюстрирует логическую схему последовательности операций другого варианта осуществления программной логики для округления субточного результата, обеспечиваемого IALU с контролируемой точностью по фиг.4.

Подробное описание изобретения

Фиг.1 иллюстрирует один вариант осуществления процессора 10, содержащего одно или более итерационных арифметико-логических устройств 12 (IALU). IALU 12 с контролируемой точностью, под управлением схемы 14 контроля точности, являющегося частью IALU 12 или соединенная с ним, выполнено возможностью завершения итерационных арифметических вычислений перед получением результата полной точности в IALU 12. Так, в ответ на значение программируемого бита точности (PBP), полученного схемой 14 контролируемой точности, контрольная схема 14 заставляет IALU 12 генерировать субточные результаты, т.е. результаты, имеющие меньшую точность, чем целевая точность, такая как точность, соответствующая регистру результатов, или точность, соответствующая начальному операнду. Значение PBP показывает ожидаемую точность, соответствующую высчитываемым в IALU 12 результатам. Таким образом, схема 14 контроля точности, в ответ на значение PBP, заставляет IALU 12 завершить обработку операнда до достижения конечного результата с полной точностью. Субточный результат, обеспечиваемый IALU 12, который имеет точность, соответствующую значению PBP, а не полную точность. Значение PBP может быть сохранено в элементе запоминающего устройства, содержащемся в процессоре 10, например регистр 16 специального или общего назначения или память 18 кэша данных. В одном варианте осуществления значение PBP жестко связано и поэтому не может быть перепрограммировано. В другом варианте осуществления значение PBP динамически изменяемое значение, хранимое в регистре 16 PBP, или в кэше 18 данных, и является таким образом изменяемым. Значение PBP может быть предоставлено процессору 10 как часть инструкции или набора инструкций, например, как часть очень длинного слова инструкции.

Независимо от способа получения значение PBP, способа его хранения и изменения, схема 14 контроля точности использует значение PBP для управления IALU 12 с контролируемой точностью для завершения итерационных арифметических операций до того момента, как результат достигнет полной точности. В отличие от обычных техник, схема 14 контроля точности может заставлять IALU 12 завершать обработку операнда до того, как результат получит полную точность вне зависимости от точности операнда. Вместо этого схема 14 контроля точности основывается в логике своего раннего завершения на значении PBP, которое напрямую не связано с точностью операнда. Следовательно, IALU 12 с контролируемой точностью способно выдавать субточные результаты в независимости от точности операнда, тем самым снижая потребление электроэнергии и улучшая эффективность процессора 10, когда процессор 10 выполняет приложения, которые могут использовать субточные результаты, например, такие как графические приложения.

Процессор 10 дополнительно содержит устройство 20 инструкций, одно или более устройств 22 загрузки/хранения и кэш 24 инструкций. Устройство 20 инструкций обеспечивает централизованное управление потоком инструкций разных устройств выполнения, таких как устройство 22 загрузки/хранения и IALU 12 с контролируемой точностью. Устройства выполнения могут выполнять параллельно несколько инструкций. Таким образом, процессор 10 является суперскалярным и/или суперконвейерным. Кэши 18, 24 инструкций и данных дают возможность системным регистрам (не изображены) и устройствам выполнения получать быстрый доступ к инструкциям и данным. Далее данные могут быть перемещены из кэша 18 данных и системных регистров через одно из устройств выполнения, например, устройство 22 загрузки/хранения.

Фиг.2 иллюстрирует один вариант осуществления IALU 12 с управляемой точностью. В этом варианте осуществления IALU 12 включает в себя арифметико-логическую схему 26. Арифметико-логическая схема 26 выполнена с возможностью выполнения итерационных арифметических операций, таких как деление, вычисление квадратного корня и трансцендентных функций. Арифметико-логическая схема 26 получает операнды из регистров 28, 30, содержащихся в процессоре 10. В одном примере операнды соответствуют одинарной точности стандарта IEEE 754, и, следовательно, каждый регистр 28, 30 хранит знаковый бит, 8 бит экспоненты и 23 бита дробной части. В другом примере операнды соответствуют двойной точности стандарта IEEE 754, и, следовательно, каждый регистр 28, 30 хранит знаковый бит, 11 бит экспоненты и 52 бита дробной части. В других примерах точность операндов отличается от полной точности, о которых идет речь в стандарте IEEE 754, такие как операнды достаточные для OpenGL стандарта либо специфических приложений.

Для простоты изложения подробное описание IALU 12 с контролируемой точностью далее дается со ссылками на операнды, которые имеют полную точность, соответствующие одинарной точности по стандарту IEEE 754 (в основном речь пойдет об одинарной точности). Тем не менее, специалисты в данной области техники поймут, что один или более вариантов осуществления данного IALU 12 с контролируемой точностью полностью совместима с обработкой операнд, имеющих любую точность, и поэтому может завершать итерационные арифметические операции раньше полных итерационных вычислений, вне зависимости от того, какая точность определяет полную точность.

Возвращаясь к фиг.2, упомянем, что арифметико-логическая схема 26 итерационно обрабатывает операнды одинарной точности, полученные из регистров 28, 30 операнда, как показано на этапе 100 фиг.3. Схема 14 контроля точности, в зависимости от содержимого регистра 16 значения PBP либо одной или нескольких инструкций, также обеспечит арифметико-логическую схему 26 полной итерационной безостановочной обработкой либо вызовет арифметико-логическую схему 26 для осуществления «преждевременного останова», завершая итерационную обработку перед получением результата полной точности, как показано на этапе 102 фиг.3. Как часть информации, полученной из регистра 16 значения PBP или как обеспечено одной или более инструкций, схема 14 контроля точности получает индикатор (RDP), определяющий, должна ли арифметико-логическая схема 26 завершить обработку раньше, т.е. выдавая субточный результат. В одном варианте осуществления индикатор является флаговым битом, который устанавливается в регистре 16 значения PBP. Если индикатор не установлен, тогда схема 14 контроля точности позволяет арифметико-логической схеме 26 выполнять итерации до полной одинарной точности, тем самым предоставляя результат полной точности, как показано на этапе 104 фиг.3. Тем не менее, если индикатор установлен, тогда схема 14 контроля точности активирует контролирующий сигнал (CTRL), заставляющий арифметико-логическую схему 26 остановить итерацию, когда достаточное количество бит сгенерировано для предполагаемого субточного результата, включая в себя некоторое количество необходимых бит округления, таким образом, получая субточный результат, как показано на этапе 106 фиг.3.

Значение PBP указывает, точность результата, при которой схема 14 контроля точности заставляет арифметико-логическую схему 26 завершить вычисления. Например, если значение PBP указывает точность 16 бит, то схема 14 контроля точности заставит арифметико-логическую схему 26 завершить итерационные вычисления, когда промежуточный результат имеет достаточное количество бит, чтобы обеспечить должным образом округленный результат с точностью 16 бит.

В одном варианте осуществления бит RDB без значения PBP используется для получения субточного результата предопределенного размера. В альтернативном варианте осуществления значение PBP без бита RDP используется также для того, чтобы разрешить уменьшенную точность операции.

В одном варианте осуществления схема 14 контроля точности содержит машину состояний, или счетчик, чтобы отслеживать количество выполненных арифметических итераций. Таким образом, схема 14 контроля точности следит за выполнением в арифметико-логической схеме. Когда арифметико-логическая схема 26 обеспечивает промежуточный результат, имеющий достаточное количество бит для получения должным образом округленного результата с точностью, соответствующей значению PBP, схема 14 контроля точности активирует контролирующий сигнал, заставляющий арифметико-логическую схему 26 завершить обработку. Например, схема 14 контроля точности считает количество циклов обработки, которые выполнила арифметико-логическая схема 26, заставляя арифметико-логическую схему 26 завершить обработку, когда счетчик показывает, что точность конечного результата соответствует значению PBP.

IALU 12 с контролируемой точностью хранит полученный результат в регистре 32 результатов, включенном в процессор 10. Регистр 32 результатов имеет достаточную битовую ширину для хранения результатов полной точности. Для результатов одинарной точности, регистр 32 содержит 23 бита позиций для хранения дробных результатов полной точности (где x=23). Арифметико-логическая схема 26 может заполнять субточные результаты, когда сохраняет результаты в регистре 32, чтобы удостовериться, что содержимое регистра 32 имеет заполненную битовую ширину, соответствующую полной точности. В одном варианте осуществления арифметико-логическая схема 26 заполняет субточный результат, присоединяя достаточное количество нулевых бит к результату так, что заполненный субточный результат имеет битовую ширину, эквивалентную полной точности. IALU 12 может хранить субточные результаты в регистре 32 результатов, однако x-n биты регистра не будут действительны, где n = позиции бита одного значительно большего, чем значение PBP. Иначе IALU 12 хранит субточные результатов в ином регистре результатов (не показан), в котором количество битовая ширина остальных регистров соответствует значению PBP.

Арифметико-логическая схема 26 может отбрасывать один или более операнда наименее значимых битов (LSB) так, что отброшенные операнды имеют меньшую точность, чем полная точность операнда, и большую, либо эквивалентную той точности, которая связана со значением PBP. Арифметико-логическая схема 26 отбрасывает один или более операнд LSB в ответ на отброшенное значение (TRONC), полученное из схемы 14 контроля точности. Схема контроля точности получает отброшенное значение либо из PBP регистра 16 либо из одной или более инструкций. В одном примере арифметико-логическая схема 26 отбрасывает один или более LSB операнда путем маскирования LSB операнда.

Фиг.4 иллюстрирует другой вариант осуществления IALU 12 с контролируемой точностью, где IALU 12 дополнительно содержит логику 24 для округления результатов, полученных арифметико-логической схемой 26. В этом варианте осуществления арифметико-логическая схема 26 содержит делитель 36 одинарной точности и регистр 38 частного для временного хранения результатов частного. Обычная логика округления реализует одну или несколько алгоритмов округления для удаления LSB результата и корректировки оставшихся битов. Например, обычная логика округления реализует один или более из следующих алгоритмов округления: округление в сторону четного, округление до нуля, округление вверх и/или округление вниз. Защитные, округленные и связанные биты могут быть использованы для содействия в процессе округления. Тем не менее, традиционные схемы округления имеют сложность в округлении субточных результатов. Это особенно заметно, когда меняется точность, соответствующая таким субточным результатам, например, в ответ на динамическое изменение значения РВР, таким образом вынуждая LSB, защитные, округлые и связанные биты результата менять позиции.

Логика 34 округления, включенная в IALU 12 с контролируемой точностью, вычисляет для точности, связанной с субточными результатами, включающими в себя динамически изменяемые точностные характеристики, посредством определения LSB частного субточного результата. Логика 34 вычисляет LSB субточного результата путем выравнивания округляющего значения с LSB, что обеспечивает лучшее округление результата. Логика 34 округления содержит схему 40 округления и сумматор 42. Схема 40 округления обрабатывает значение PBP, чтобы определить, какая позиция бита, соответствующая частному результату, должна быть условно увеличена. Например, схема 40 округления в ответ на значение PBP определяет LSB результата хранимого в регистре 38 частного, который следует условно увеличить. В одном варианте осуществления схема 40 округления содержит сдвиговое устройство. Сдвиговое устройство передвигает или сдвигает значение округления таким образом, что значение округления выравнивается LSB частного субточного результата, как проиллюстрировано на этапе 200 фиг.5. Значение округления может быть выровнено сдвигом значения логической единицы в бит позиции, соответствующий LSB значения PBP. Так, значение округления содержит конфигурацию битов, имеющую все логические нули, кроме тех позиций бит, которые соответствуют LSB соответствующего результата. Далее сдвинутое значение округления поступает на сумматор 42 как операнд. Арифметико-логическая схема 26 выдает субточный результат, выполняющий функцию другого операнда, например результат, хранимый в регистре 38 частного. Сумматор 42 условно добавляет сдвинутые округляющие значения к результату генерируемому арифметико-логической схемой 26 для получения точного округленного результата, как показано на этапе 202 фиг.5. Специалисты в уровне техники оценят, что результат может быть округлен исходя из LSB, защитных, округлых и связанных битов совместно с режимом округления, используя один из известных обычных способов увеличения, каждый из которых находится в объеме вариантов осуществления, раскрытых в данном изобретении.

В другом варианте осуществления схема 40 округления содержит декодер для выравнивания округляющего значения с LSB субточного результата, что позволяет надлежащим образом округлять результат. Декодер получает значение PBP и генерирует значение округления, соответствующее значению PBP, как показано на этапе 300 фиг.6. В одном варианте осуществления значение округления содержит конфигурацию битов, имеющую все логические нули, кроме позиции бита, соответствующей LSB значения PBP. Позиция бита значения округления, соответствующего LSB значению PBP, содержит логическую единицу. Округляющее значение затем поступает на сумматор 42 как операнд, и результат, полученный арифметико-логической схемой 26, выполняет функцию другого операнда. Сумматор 42 условно добавляет округляющее значение к результату, генерируемому арифметико-логической схемой 26, для получения точного округленного результата, как показано на этапе 302 фиг.6. Таким образом, либо сдвигом округляющего значения или декодированием значения РВР для получения округляющего операнда, и условного добавления округляющего операнда, и условного добавления округляющего операнда к соответствующему результату, IALU 12 с контролируемой точностью способно предоставлять точные субточные результаты.

С представленным широким кругом вариантов и приложений, следует понимать, что настоящее описание не ограничено предшествующим описанием, так же как оно не ограничено приложенными чертежами. Вместе с тем, настоящее изобретение ограничено только предложенной формулой изобретения и ее законодательным отражением.

Изобретения относятся к процессорам, содержащим итерационные арифметико-логические устройства с контролируемой точностью для выполнения итерационных арифметических операций. Техническим результатом является снижение потребляемой мощности процессора при выполнении вычислений. Устройство содержит арифметико-логическую схему, выполненную с возможностью итерационно обрабатывать операнды первой точности, для получения результата; и схему контроля точности, выполненную с возможностью принимать программируемый бит точности (РВР) указывающий ожидаемую вторую точность, которая меньше, чем первая точность, и обеспечивать возможность процессору завершать итерационную обработку, когда результат достигает запрограммированной второй точности, меньшей, чем первая точность. 3 н. и 12 з.п. ф-лы, 6 ил.

1. Способ выполнения итерационной арифметической операции в процессоре, содержащий этапы, на которых:

итерационно обрабатывают операнды первой точности для получения результата,

принимают программируемый бит точности (РВР), указывающий ожидаемую вторую точность, которая меньше, чем первая точность, и обеспечивают возможность процессору завершать итерационную обработку, когда результат достигает ожидаемой второй точности.

2. Способ по п.1, дополнительно содержащий этап, на котором заполняют результат так, что заполненный результат имеет битовую ширину соответствующую первой точности.

3. Способ по п.2, в котором этап, на котором заполняют результат так, что заполненный результат имеет битовую ширину, соответствующую первой точности, содержит этап, на котором добавляют один или более битов логических нулей к результату.

4. Способ по п.1, дополнительно содержащий этап, на котором хранят результат в регистре, имеющем битовую ширину, меньшую, чем первая точность.

5. Способ по п.1, дополнительно содержащий этап, на котором отбрасывают один или более наименее значащих бит (LSB) операндов перед началом итерационной обработки, таким образом, что отброшенные операнды имеют точность, меньшую, чем первая точность и больше или равную запрограммированной второй точности.

6. Способ по п.5, в котором этап, на котором отбрасывают один или более LSB операнда, содержит этап маскирования одного или более LSB операнда.

7. Способ по п.1, дополнительно содержащий этап, на котором округляют результат.

8. Способ по п.7, в котором этап, на котором округляют результат, содержит:

этап выравнивания округленного значения, с наименее значащим битом (LSB) результата; и

этап условного добавления выровненного округленного значения к результату.

9. Способ по п.8, в котором этап выравнивания значения округления с LSB результата содержит этап сдвига значения округления таким образом, что значение округления имеет одну логическую единицу, расположенную в позиции бита, соответствующей LSB результата.

10. Способ по п.8, в котором этап выравнивания значения округления LSB результата содержит этап декодирования запрограммированной второй точности, чтобы получить округленный операнд.

11. Способ по п.1, дополнительно содержащий этап изменения запрограммированной второй точности, в ответ на изменение содержимого регистра, содержащегося в процессоре.

12. Способ по п.1, дополнительно содержащий этап изменения запрограммированной второй точности, в ответ на одну или более инструкций, полученных процессором.

13. Итерационное арифметико-логическое устройство для использования в процессоре, содержащее:

арифметико-логическую схему, выполненную с возможностью итерационно обрабатывать операнды первой точности, для получения результата; и

схему контроля точности, выполненную с возможностью

принимать программируемый бит точности (РВР) указывающий ожидаемую вторую точность, которая меньше, чем первая точность, и

обеспечивать возможность процессору завершать итерационную обработку, когда результат достигает запрограммированной второй точности, меньшей, чем первая точность.

14. Итерационное арифметико-логическое устройство по п.13, в котором арифметико-логическая схема дополнительно выполнена с возможностью заполнения результата таким образом, что заполненный результат имеет битовую ширину, соответствующую первой точности.

15. Процессор, содержащий итерационное арифметико-логическое устройство, выполненное с возможностью выполнения этапов способа по пп.1-12.

| Прибор для очистки паром от сажи дымогарных трубок в паровозных котлах | 1913 |

|

SU95A1 |

| US 4839846 A, 13.06.1989 | |||

| US 5128889 A, 07.07.1992 | |||

| RU 2004104325 A, 27.06.2005. | |||

Авторы

Даты

2011-03-10—Публикация

2007-04-20—Подача