Область техники, к которой относится изобретение

Данное изобретение, в общем, относится к области микропроцессоров. В частности, изобретение относится к эффективным методикам обработки исключения с плавающей запятой в процессоре, который выполняет инструкции типа один поток команд - много потоков данных (SIMD, ОКМД).

Уровень техники

В стандарте IEEE (Институт инженеров по электротехнике и радиоэлектронике) для арифметики с плавающей запятой (IEEE 754) определяют, как числа с плавающей запятой одиночной точности (32 бита), двойной точности (64 бита)), одиночной расширенной точности (≥43 битов, не имеет общего применения) и двойной расширенной точности (≥79 битов, обычно воплощены с 80 битами) должны быть представлены (включая в себя отрицательное значение нуля, денормализованные числа, бесконечности и NaN (не числа)), а также как следует выполнять арифметические правила с ними. Только 32-битные значения требуются в соответствии со стандартом; другие являются не обязательными. Здесь также описаны четыре режима округления и пять исключений (включающие в себя, когда возникают исключения, и что происходит, когда они действительно возникают).

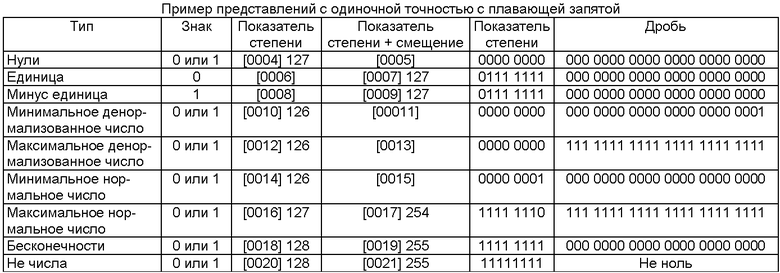

Показатели степени смещены на (2е-1)-1, где e представляет собой количество битов, используемое для поля показателей степени. Например, числа с одиночной точностью имеют 8-битный показатель степени, и поэтому его показатель степени сохраняют с 27-1=127 битами, добавленными к нему, также называется "смещенным на 127". Нормальные показатели степени с одиночной точностью находятся в пределах от -126 до 127. Показатель степени 128 зарезервирован для идентификации плюса или минуса. Показатель степени -127 (все нули) зарезервирован для нуля с плюсом или минусом (или для денормализованных чисел, но в случае денормализованных чисел используемое смещение составляет (2е-1)-2, то есть 126, а не 127, поскольку предполагается, что старший значащий бит мантиссы равен нулю, а не единице). Некоторые примеры представлений с одиночной точностью с плавающей запятой представлены в таблице.

Нормальное число с плавающей запятой имеет значение ν=s×2е×m, где s, e и m определены как

s=+1 (положительные числа и +0), когда бит знака равен 0

s=-1 (отрицательные числа и -0), когда бит знака равен 1

е = показатель степени - смещение (то есть показатель степени сохраняется со смещением, добавленным к нему)

m=1, дробная часть двоичного числа (то есть мантисса или значащая часть числа представляет собой неявно заданное значение 1 ведущего бита, после чего следует запятая, после которой следуют двоичные биты дробной части). Таким образом, 1≤m<2.

Денормализованное число (также называемое денормализованным числом, или поднормальным числом) представляет собой число, меньшее (в абсолютном значении), чем наименьшее нормальное число, но все еще не равное нулю. Получение денормализованного числа иногда называют постепенной потерей значимости, поскольку оно позволяет плавно рассчитывать медленную потерю точности при малом результате. Денормализованные числа воплощены в сопроцессорах с плавающей запятой Intel 8087 в то время, когда писали стандарт IEEE 754. Такое воплощение продемонстрировало, что денормализованные числа могут поддерживаться в практическом воплощении.

В нормальном представлении с плавающей запятой предполагается, что ведущая двоичная цифра мантиссы равна 1. Поскольку известно, что она равна 1, ведущая двоичная цифра мантиссы в некоторых представлениях с плавающей запятой может быть исключена и значение показателя степени может быть соответствующим образом отрегулировано. Денормализованные значения представляют собой такие значения, которые нельзя представить в нормализованной форме (то есть, имеющими наименьший возможный показатель степени с мантиссой, не равной нулю). Некоторые варианты воплощения блок арифметики для операций с плавающей запятой (FPU, БПЗ) не поддерживают непосредственно денормализованные числа в аппаратных средствах, а скорее используются определенного рода программное средство или поддержка на уровне микрокода. Хотя это может быть понятно для пользователя, такой подход может привести к расчетам, которые производят или используют денормализованные числа, обработка которых выполняется намного медленнее, чем аналогичные расчеты с нормальными числами.

Современные процессоры также могут иметь инструкции, которые выполняют операции с одним потоком команд и множеством потоков данных (ОКМД) для чисел с плавающей запятой. Когда такие операции ОКМД производят или используют денормализованные числа, может быть инициировано исключение для обработки операции в программных средствах или в аппаратных средствах с помощью микрокода. Один из способов поддержки денормализованных чисел в аппаратных средствах представляет собой более широкое внутреннее представление, которое обладает достаточной точностью для того, чтобы просто обрабатывать денормализованные числа как малые нормальные числа. Например, если будет инициировано исключение, подразумевающее денормализованные числа с одиночной точностью, микрокод может преобразовать операнды обработки с одиночной точностью в нормальные операнды с двойной точностью и после этого повторно выполнить операции более широких представлений, после чего выполняется денормализация результатов и преобразование их обратно в нормальные числа с одиночной точностью. Аналогично, денормализованные числа двойной точности могут быть обработаны как нормали расширенной двойной точности. Один из недостатков состоит в том, что расчеты, которые позволяют постоянно получать или использовать денормализованные числа, выполняются значительно медленнее, чем аналогичные расчеты для нормальных чисел.

До настоящего времени еще не были полностью исследованы эффективные технологии обработки исключения с плавающей запятой в процессоре, который выполняет инструкции ОКМД.

Краткое описание чертежей

Настоящее изобретение представлено в качестве примера, а не для ограничений на приложенных чертежах.

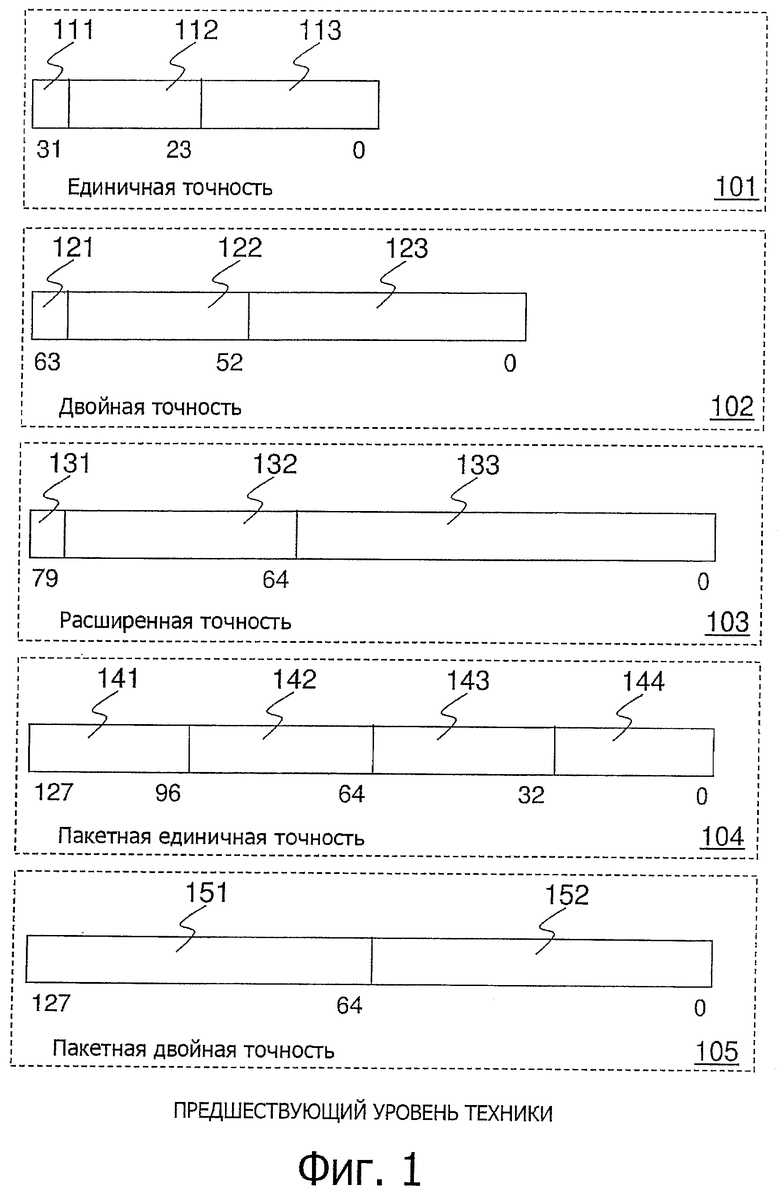

На фиг.1 иллюстрируются примерные форматы сохранения, предназначенные для сохранения скалярных и пакетных чисел с плавающей запятой в соответствии с IEEE.

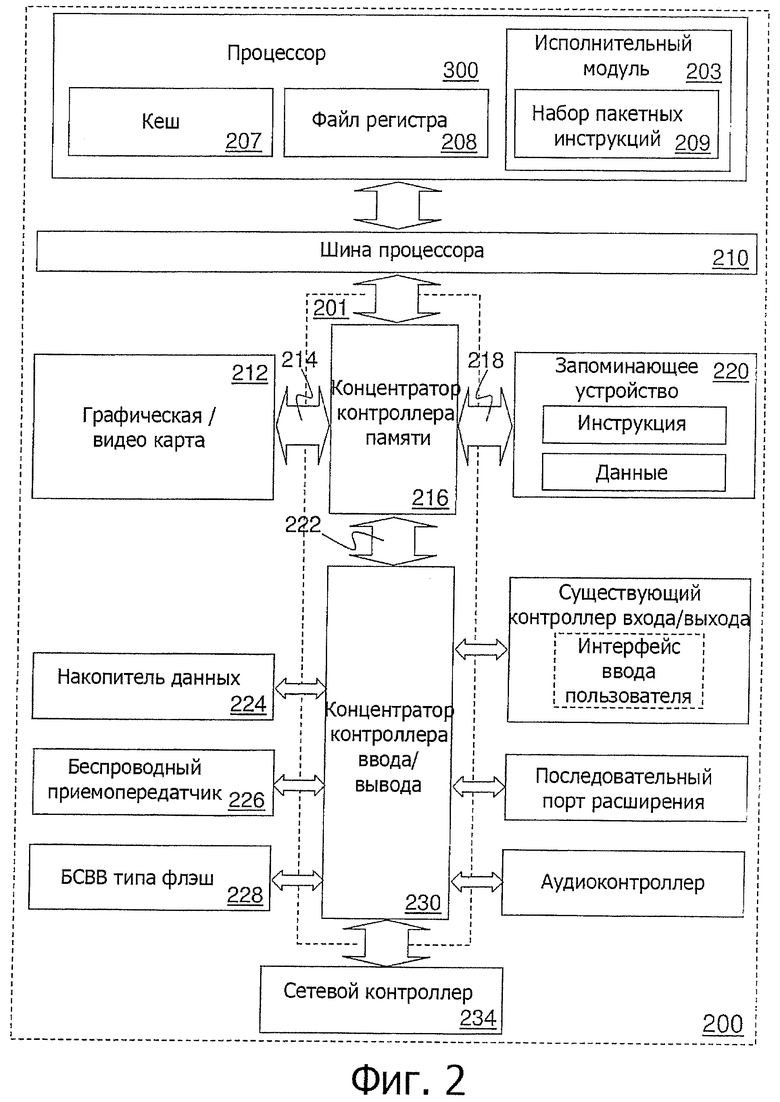

На фиг.2 иллюстрируется один вариант воплощения системы, включающей в себя процессор, который выполняет инструкции с плавающей запятой ОКМД и использует эффективные методики для обработки исключения с плавающей запятой ОКМД.

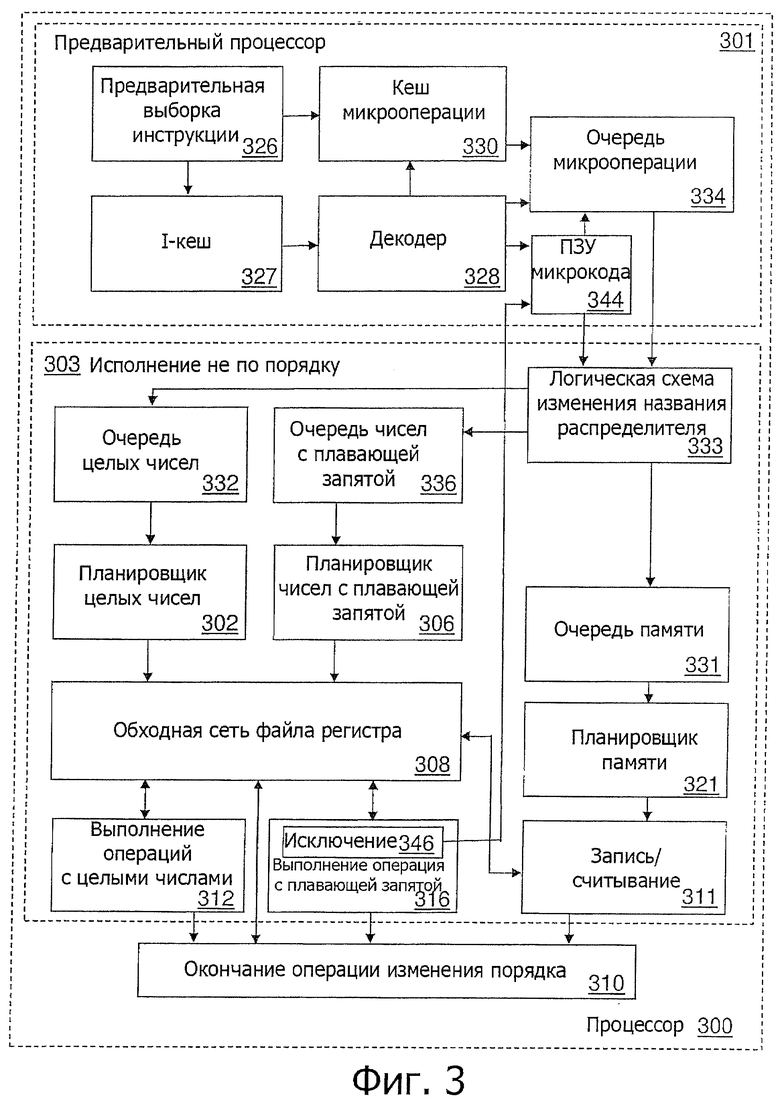

На фиг.3 иллюстрируется один вариант воплощения процессора, который выполняет инструкции с плавающей запятой ОКМД и использует эффективные технологии, для обработки исключения с плавающей запятой ОКМД.

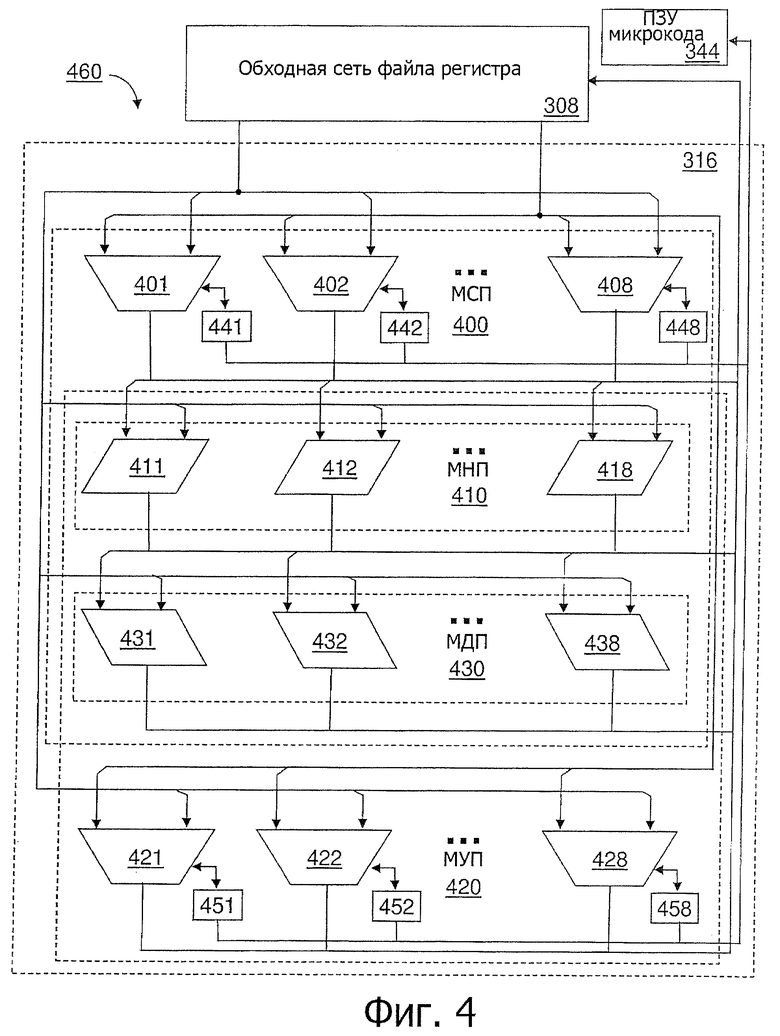

На фиг.4 иллюстрируется один альтернативный вариант воплощения устройства для эффективной обработки исключений с плавающей запятой в процессоре, который выполняет инструкции с одним потоком команд и множеством потоков данных (ОКМД).

На фиг.5а-b иллюстрируются примерные форматы сохранения для сохранения внутренних представлений пакетов чисел с плавающей запятой.

На фиг.6 иллюстрируется блок-схема последовательности операций для одного варианта воплощения обработки, в которой обрабатывают определенные числовые исключения в сумматоре с плавающей запятой ОКМД.

На фиг.7 иллюстрируется блок-схема последовательности операций для одного варианта воплощения процесса по обработке определенных общих исключений в умножителе с плавающей запятой ОКМД.

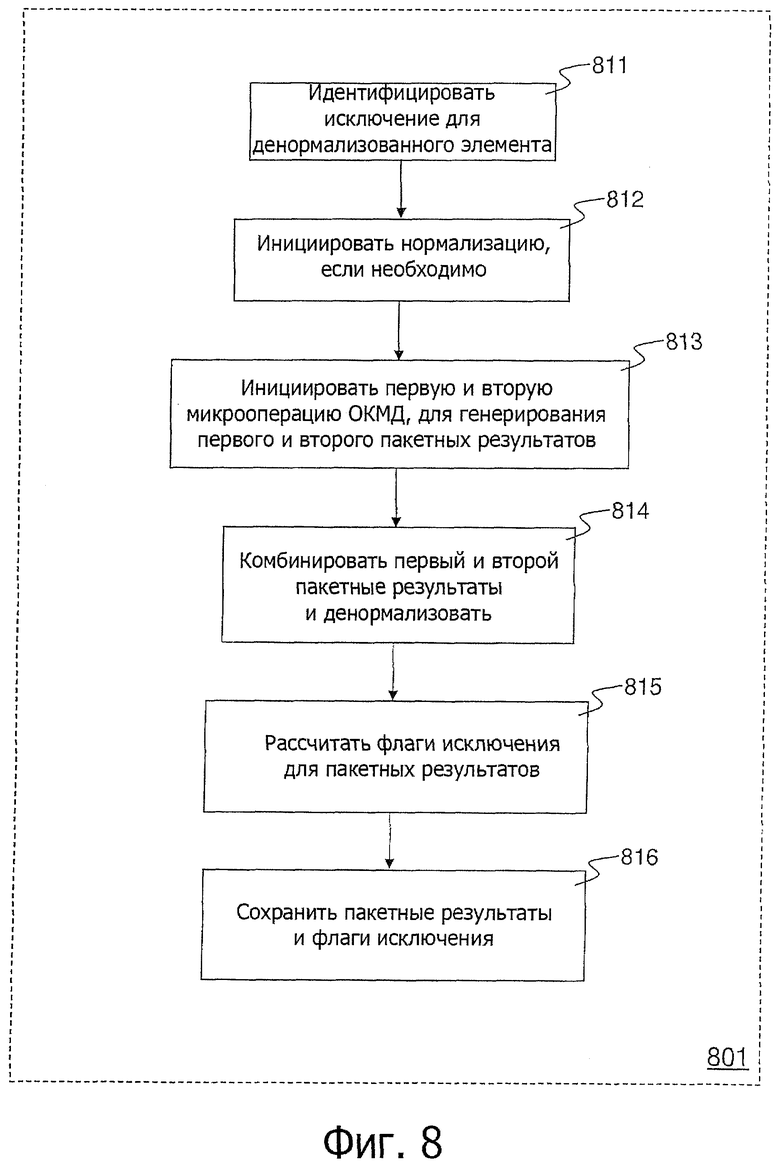

На фиг.8 иллюстрируется блок-схема последовательности операций для альтернативного варианта воплощения процесса для обработки числовых исключений в процессоре, который выполняет инструкции с плавающей запятой ОКМД.

Подробное описание изобретения

Раскрыты способы и устройство для обработки исключения с плавающей запятой в процессоре, который выполняет инструкции с одним потоком команд и множеством потоков данных (ОКМД). В одном варианте воплощения численное исключение идентифицируют для операции с плавающей запятой ОКМД и пару микроопераций ОКМД инициируют для генерирования двух пакетных частичных результатов пакетного результата для операции с плавающей запятой ОКМД. Численное исключение в контексте следующего раскрытия можно понимать, как включающее в себя, по меньшей мере, одно исключение, инициированное путем идентификации денормализованного входного значения или путем идентификации состояния потери значимости, которое потенциально может привести к получению в качестве результата денормализованного выходного значения и, следовательно, может потребовать содействия с помощью микрокода. Микрооперацию денормализации ОКМД инициируют для комбинирования двух пакетных частичных результатов и для денормализации одного или больше элементов, комбинированных частичных пакетных результатов для генерирования пакетного результата для операции с плавающей запятой ОКМД, имеющей один или больше денормализованных элементов. Флаги могут быть установлены и сохранены в частичных пакетных результатах и/или в пакетных результатах для идентификации денормализованных элементов.

В одном варианте воплощения микрооперацию нормализации ОКМД инициируют для генерирования нормализованного псевдовнутреннего представления с плавающей запятой перед операцией с плавающей запятой ОКМД, когда она представляет собой умножение (или деление, квадратный корень или преобразование). Такие псевдовнутренние представления с плавающей запятой можно сохранять в тех же регистрах, что и нормальные пакетные операнды с плавающей запятой, с флагами, установленными для обозначения, какие из них соответствуют псевдовнутренним представлениям с плавающей запятой денормализованных элементов, которые должны быть преобразованы в фактическое представление с плавающей запятой денормализованных элементов. В таких псевдовнутренних представлениях с плавающей запятой денормализованных элементов мантиссы могут быть нормализованы, и показатели степени могут быть сохранены таким образом, чтобы их можно было легко восстановить в виде более широкого показателя степени фактического внутреннего представления с плавающей запятой. Например, если количество начальных нулей мантиссы вычесть из показателя степени денормализованного числа (со смещением в более широком формате показателя степени фактического внутреннего представления с плавающей запятой), верхние биты могут быть постоянными (например, 10) и поэтому их можно отбросить из псевдовнутреннего представления с плавающей запятой и легко восстановить.

Таким образом, такие технологии можно использовать для одновременной прозрачной обработки исключения с плавающей запятой ОКМД, без преобразования в скалярные операции, и при этом требуется выполнение только небольшого количества дополнительных микроопераций.

Эти и другие варианты воплощения настоящего изобретения могут быть реализованы в соответствии со следующим описанием, и следует понимать, что различные модификации и изменения могут быть выполнены в следующих описаниях без выхода за пределы широкой сущности и объема изобретения. Описание и чертежи в соответствии с этим требуется рассматривать как иллюстрацию, а не в ограничительном смысле, и изобретение можно оценивать только на основании формулы изобретения и ее эквивалентов. В следующем описании с целью пояснения представлены различные конкретные детали для обеспечения полного понимания настоящего изобретения. Для специалистов в данной области техники, однако, будет понятно, что эти конкретные детали не обязательно являются необходимыми для выполнения на практике некоторых вариантов воплощения настоящего изобретения. В других случаях хорошо известные электрические структуры и схемы не были представлены достаточно подробно для того, чтобы не сделать непонятными варианты воплощения настоящего изобретения.

Поскольку все большее количество компьютерных систем используется в Интернет и в мультимедийных приложениях, с течением времени была введена дополнительная поддержка процессора. Например, инструкции для целых чисел/чисел с плавающей запятой одного потока команд и множества потоков данных (ОКМД) и исключения при потоковой передаче данных ОКМД (SSE, ИПО) представляют собой инструкции, которые уменьшают общее количество инструкций, требуемых для выполнения определенной программной задачи. Эти инструкции могут ускорить работу программных средств благодаря параллельной обработке множества элементов данных. В результате может быть достигнут прирост рабочих характеристик в широком диапазоне приложений, включающих в себя обработку видеоданных, речевых данных и изображений/фотоизображений. Варианты воплощения инструкций ОКМД в микропроцессорах и аналогичных типах логических схем обычно имеют ряд проблем. Кроме того, сложность операций ОКМД часто приводит к необходимости использования дополнительных схем для того, чтобы правильно обрабатывать и манипулировать с данными.

На фиг.1 иллюстрируются некоторые примерные форматы 101-105 сохранения, предназначенные для сохранения скалярных и пакетных чисел с плавающей запятой IEEE. Формат 101 с одиночной точностью содержит 32 бита: знаковый бит 111, 8 битов 112 показателя степени и 23 бита 113 значимой части числа или мантиссы. Формат 102 с двойной точностью содержит 64 бита: бит 121 знака, 11 битов 122 показателя степени и 52 бита 123 значимой части числа или мантиссы. Формат 103 с двойной расширенной точностью содержит 80 битов: бит 131 знака, 15 битов 132 показателя степени и 64 бита 133 значимой части числа или мантиссы. В каждом из форматов сохранения для чисел с плавающей запятой в соответствии со стандартом IEEE значимые части чисел или мантиссы 112, 122 и 132 также могут включать в себя скрытый старший значимый бит J, который, как предполагается, равен единице. Таким образом, если используется 52-битная мантисса для формата 102 с двойной точностью, например, в котором сохранено шестнадцатеричное значение 23456789ABCDE, это шестнадцатеричное значение будет представлено как 1,23456789ABCDE с запятой, следующей после неявно заданного бита J. Показатели степени смещены на (2е-1)-1, где e представляет собой количество битов, используемых для поля показателя степени. Таким образом, 8-битный показатель степени формата 101 с одиночной точностью будет смещен на 127, и 11-битный показатель степени формата 102 с двойной точностью будет смещен на 1023.

Пакетный формат 104 с одиночной точностью содержит 128 битов, и каждый из участков 141-144 размером 32 бита содержит число с плавающей запятой с одиночной точностью, которое имеет формат 101 с одиночной точностью. Пакетный формат 105 с двойной точностью также содержит 128 битов, каждый из участков 151-152 размером 64 бита содержит число с плавающей запятой с двойной точностью, имеющее формат 102 с двойной точностью. Пакетный формат 104 с одиночной точностью и пакетный формат 105 с двойной точностью известны в данной области техники как используемые для выполнения операций с плавающей запятой ОКМД. Следует понимать, что, хотя пакетный формат 104 с одиночной точностью и пакетный формат 105 с двойной точностью были представлены как содержащие 128 битов, настоящее изобретение не ограничивается этим. В частности, варианты воплощения настоящего изобретения могут включать в себя форматы для пакетных чисел с одиночной точностью и пакетных чисел с плавающей запятой с двойной точностью, которые содержат 256 битов или 512 битов данных, или больше, для выполнения операций с плавающей запятой ОКМД.

Когда такие операции с плавающей запятой ОКМД формируют или используют денормализованные числа, исключение (возможно, замаскированное) может быть инициировано для обработки операции в программном средстве или в аппаратных средствах и/или с использованием микрокода. В некоторых процессорах предшествующего уровня техники обработка таких исключений может включать в себя преобразование пакетных чисел с плавающей запятой в скалярные числа с плавающей запятой или более широкое представление и повторное выполнение операций в качестве скалярных операций в более широких представлениях, после которых следует денормализация результатов, в соответствии с необходимостью, и преобразование их обратно в пакетные числа с плавающей запятой. Как отмечено выше, обработка при таких расчетах, в результате которых формируются или используются денормализованные числа, может выполняться значительно медленнее, чем аналогичная обработка нормальных чисел, в частности, если форматы для пакетных чисел с плавающей запятой могут содержать 256 битов или 512 битов или больше данных. Таким образом, существует потребность в более эффективных технологиях, раскрытых здесь для обработки исключений с плавающей запятой в процессоре, который выполняет инструкции ОКМД.

На фиг.2 иллюстрируется один вариант воплощения системы 200, включающей в себя процессор 300, который выполняет инструкции с плавающей запятой ОКМД и использует более эффективные технологии для обработки исключения с плавающей запятой ОКМД. Система 200 включает в себя такой компонент, как процессор 300 для использования модулей исключения, включающих в себя логические схемы, для выполнения алгоритмов, для выполнения операций с плавающей запятой ОКМД, в соответствии с настоящим изобретением, таким как в варианте воплощения, описанном здесь. Система 200 представляет собой системы обработки, основанные на использовании микропроцессоров PENTIUM® III, PENTIUM® 4, CELERON®, XEON ™, ITANIUM®, CENTRINO®, CORE™ Duo, CORE™ 2 Duo и/или CORE™ 2 Quad, поставляемых компанией Intel Corporation, Санта Клара, Калифорния, хотя другие системы (включающие в себя PC (ПК), имеющие другие микропроцессоры, автоматизированные рабочие станции, телевизионные приставки и т.п.) также можно использовать. В одном варианте воплощения примерная система 200 может выполнять версию операционной системы WINDOWS™, которая поставляется компанией Microsoft Corporation, г.Редмонд, Вашингтон, хотя другие операционные системы (например, операционные системы MAC OS® X Leopard®, UNIX и/или Linux), встроенное программное обеспечение и/или графические интерфейсы пользователя также можно использовать. Таким образом, настоящее изобретение не ограничивается какой-либо конкретной комбинацией аппаратных схем и программных средств.

Процессор 300 включает в себя один или больше исполнительных модулей 203 для выполнения инструкции ОКМД для пакетных данных с плавающей запятой в соответствии с настоящим изобретением. Настоящий вариант воплощения описан в контексте настольного компьютера с одним процессором или системы сервера, но альтернативные варианты воплощения могут быть включены в микропроцессорную систему. Один вариант воплощения системы 200 представляет собой пример архитектуры концентратора. Компьютерная система 200 включает в себя процессор 300 для обработки данных сигналов. Процессор 300 может представлять собой микропроцессор, такой как процессор со сложным набором команд (CISC, ПСНК), микропроцессор для вычислений с сокращенным набором команд (RISC, BCHK), микропроцессор с архитектурой с командными словами очень большой длины (VLIW, КСБД), процессор, воплощающий комбинацию наборов инструкций, или любое другое устройство процессора, такое как, например, процессор цифровых сигналов. Процессор 300 соединен с шиной 210 процессора, которая может передавать сигналы данных между процессором 300 и другими компонентами в системе 200. Элементы системы 200 выполняют свои обычные функции, которые хорошо известны специалистам в данной области техники.

В одном варианте воплощения процессор 300 включает в себя запоминающее устройство 207 внутреннего кеш-уровня 1 (L1). В зависимости от архитектуры процессор 300 может иметь одиночный внутренний кеш или множество уровней внутреннего кеш. В качестве альтернативы, в другом варианте воплощения, запоминающее устройство-кеш может быть расположено как внешнее устройство для процессора 300. Другие варианты воплощения также могут включать в себя комбинацию как внутреннего, так и внешнего кеш, в зависимости от конкретных воплощений и потребностей. Файл 208 регистра может сохранять различные типы данных в различных регистрах, включающих в себя регистры ОКМД и/или скалярные регистры, регистры целых чисел, регистры с плавающей запятой, регистры состояния и регистры указателя инструкции.

Исполнительный модуль 203, включающий в себя логику для выполнения операций с целыми числами и с плавающей запятой, также находится в процессоре 300. Процессор 300 также включает в себя ПЗУ микрокода (u-кода), в котором сохраняется микрокод для некоторых макроинструкций и/или для обработки операции исключения в аппаратных средствах с помощью микрокода. Для данного варианта воплощения исполнительный модуль 203 включает в себя логику, предназначенную для обработки набора 209 пакетных инструкций, который включает в себя инструкции с плавающей запятой ОКМД. Благодаря включению набора 209 пакетных инструкций в набор инструкций процессора 300 общего назначения вместе с соответствующими схемами для выполнения инструкций операции, используемые множеством мультимедийных приложений, могут быть выполнены с использованием пакетных данных в процессоре 300 общего назначения. Таким образом, множество мультимедийных приложений могут быть ускорены и могут быть выполнены более эффективно, используя шину данных процессора полной ширины для выполнения операций с пакетными данными. Это может устранить необходимость передачи меньших модулей данных через шину данных процессора для выполнения одной или больше операций по одному элементу данных одновременно.

Альтернативные варианты воплощения исполнительного модуля 203 также можно использовать в микроконтроллерах, встроенных процессорах, графических устройствах, DSP (ЦСП, цифровой сигнальный процессор) и других типах логических схем. Система 200 включает в себя запоминающее устройство 220. Запоминающее устройство 220 может представлять собой динамическое оперативное запоминающее устройство (DRAM, ДОЗУ), статическое оперативное запоминающее устройство (SRAM, СОЗУ), запоминающее устройство типа флэш или другие запоминающие устройства. Запоминающее устройство 220 может сохранять инструкции и/или данные, представленные сигналами данных, которые могут быть выполнены процессором 300.

Системная логическая микросхема 216 соединена с шиной 210 процессора и запоминающим устройством 220. Системная логическая микросхема 216 в представленном варианте воплощения представляет собой концентратор контроллера памяти (МСН, ККП). Процессор 300 может связываться с ККП 216 через шину 210 процессора. ККП 216 обеспечивает канал 218 для запоминающего устройства с широкой полосой пропускания к запоминающему устройству 220 для передачи инструкций и сохранения данных, и для сохранения графических команд, данных и текстур. ККП 216 предназначен для направления сигналов данных между процессором 300, запоминающим устройством 220 и другими компонентами в системе 200 и для установления мостика для сигналов данных между шиной 210 процессора, запоминающим устройством 220 и входом/выходом 222 системы. В некоторых вариантах воплощения системная логическая микросхема 216 может обеспечивать графический порт для подключения к графическому контроллеру 212. ККП 216 соединена с запоминающим устройством 220 через интерфейс 218 памяти. Графическую карту 212 подключают к ККП 216 через взаимное соединение 214 ускоренного графического порта (AGP, УГП).

В некоторых вариантах воплощения системы 200 используется специализированная шина 222 интерфейса концентратора для подключения ККП 216 к концентратору 230 контроллера ввода/вывода (ICH, ККВ). ККВ 230 обеспечивает прямое соединение с некоторыми устройствами ввода/вывода через локальную шину ввода/вывода. Локальная шина ввода/вывода представляет собой высокоскоростную шину ввода/вывода, предназначенную для соединения периферийных устройств с запоминающим устройством 220, набором микросхем и процессором 300. Некоторые примеры представляют собой аудиоконтроллер, концентратор 228 встроенного программного обеспечения (BIOS (БСВВ, базовая система ввода/вывода) в памяти типа флэш), приемопередатчик 226 беспроводного канала передачи данных, хранилище 224 данных, традиционный контроллер ввода/вывода, содержащий интерфейсы ввода пользователя и клавиатуры, последовательный порт расширения, такой как универсальная последовательная шина (USB, УПШ), и сетевой контроллер 234. Устройство 224 сохранения данных может содержать привод жесткого диска, привод гибкого диска, привод CD-ROM, запоминающее устройство типа флэш или другие устройства сохранения большой емкости. В некоторых вариантах воплощения системы 200 ККП 216 и ККВ 230 могут быть интегрированы в единую системную логическую микросхему 201. В некоторых альтернативных вариантах воплощения ККП 216 может быть интегрирован непосредственно в процессор 300 для направления доступа к процессору 300 к запоминающему устройству 220. Для других вариантов воплощения системы 200 процессор 300 может быть непосредственно интегрирован в систему на микросхеме. В одном варианте воплощения системы на микросхеме содержат процессор 300 и запоминающее устройство 220. Запоминающее устройство 220 для одной такой системы представляет собой запоминающее устройство типа флэш. Запоминающее устройство 220 типа флэш может быть расположено на том же кристалле, что и процессор 300 и другие системные компоненты. В случае необходимости другие логические блоки, такие как контроллер памяти или графический контроллер, также могут быть расположены в системе на микросхеме.

На фиг.3 иллюстрируется один вариант воплощения процессора 300, который выполняет инструкции с плавающей запятой ОКМД и в котором используются эффективные технологии обработки исключения с плавающей запятой ОКМД. Работающий по порядку блок 301 предварительной обработки данных представляет собой часть 300 процессора, которая выбирает макроинструкции для выполнения, и подготавливает их для последующего использования в конвейере процессора. Работающий по порядку блок 301 предварительной обработки данных в соответствии с данным вариантом воплощения включает в себя несколько модулей. Блок 326 предварительной выборки инструкции выполняет выборку макроинструкции в запоминающем устройстве 220 и/или из I-кеш 327 и передает их в декодер 328 инструкций, который, в свою очередь, декодирует их в примитивы, называемые микроинструкциями или микрооперациями (также называемые микро-ops или uops), которые может выполнять вычислительное устройство. Кеш 330 микроопераций отбирает декодированные микрооперации и сохраняет их для будущего повторного выполнения без декодирования. Некоторые варианты воплощения кеш 330 микроопераций могут включать в себя кеш отслеживания, который собирает микроинструкции в программу упорядоченной последовательности или следы в очереди 334 микроопераций для выполнения. Для некоторых вариантов воплощения, когда декодер 328 или когда кеш отслеживания в кеш 330 микроопераций сталкивается со сложной макроинструкцией, ПЗУ 344 микрокода может предоставлять микрооперации, необходимые для завершения этой операции.

Многие макроинструкции преобразуют в одиночные микрооперации, но для других требуется несколько микроопераций для завершения всей операции. В одном варианте воплощения, если более чем четыре микрооперации требуется для завершения макроинструкции, декодер 328 обращается к ПЗУ 344 микрокода для обеспечения требуемых микроопераций, для выполнения макроинструкции.

Для одного варианта воплощения исключение для операции с плавающей запятой может быть кодировано в и может быть обработано малым количеством микроопераций в ПЗУ 344 микрокода, для повторного выполнения операций с плавающей запятой таким образом, чтобы получить поддержку для исключительного случая, такого как обработка денормализованных чисел в процессоре 300, который выполняет инструкции с плавающей запятой ОКМД.

Некоторые ОКМД и другие мультимедийные типы инструкций рассматриваются как сложные инструкции. Большая часть инструкций, относящихся к плавающей запятой, также представляют собой сложные инструкции. При этом, когда декодер 328 инструкций сталкивается со сложными макроинструкциями, обращаются к соответствующему местоположению в ПЗУ микрокода 344 для выборки последовательности микрокода для этой макроинструкции. Различные микрооперации, необходимые для выполнения этой макроинструкции, передают в механизм 303 выполнения не по порядку для выполнения соответствующих исполнительных модулей для целых чисел и плавающей запятой.

Механизм 303 выполнения не по порядку предусмотрен там, где микроинструкции подготавливают для выполнения. Логика выполнения не по порядку имеет множество буферов для сглаживания и изменения порядка потока микроинструкций для оптимизации рабочих характеристик по мере работы конвейера и планирует их выполнение. Логическая схема 333 изменения названия распределителя выделяет буферы вычислительного устройства и ресурсы, которые требуются для выполнения микроопераций, и изменяет названия логических регистров по входам в файл регистра. В одном варианте воплощения логическая схема 333 изменения названия распределителя также выделяет вход для каждой микрооперации в различных очередях, которые могут включать в себя очередь 331 запоминающего устройства для операций, в запоминающее устройство, очередь 332 целого числа для операций с целыми числами или с плавающей запятой и очередь 336 плавающей запятой для операций с плавающей запятой. Из этих очередей (например, 331, 332 и 336 соответственно) микрооперации планируют с помощью планировщика 321 памяти, планировщика 302 целых чисел и планировщика 306 чисел с плавающей запятой для выполнения соответственно модулем 311 считывания/записи, исполнительным модулем 312 операций с целыми числами и исполнительным модулем 316 операций с плавающей запятой. Планировщики 321, 302 и 306 микроопераций определяют, когда микрооперация готова к выполнению, на основе готовности зависящих от них источников операнда входного регистра и доступности ресурсов выполнения, микроопераций, необходимых для завершения их работы. Следует понимать, что каждый или любой из исполнительных модулей 311, 312 и 316 может иметь дублированные модули расширения для выполнения скалярных операций или операций ОКМД.

Обходная сеть 308 файла регистра расположена между планировщиками 321, 302 и 306 и исполнительными модулями 311, 312 и 316. В некоторых вариантах воплощения обходной сети 308 файла регистра может находиться отдельный файл регистра для операций с целыми числами и плавающей запятой. Каждый файл регистра в таких вариантах воплощения также может включать обходную сеть, которая может обводить или передавать только что полученные результаты, которые еще не были записаны в файл регистра в новые зависимые микрооперации, и также могут быть выполнены с возможностью обмена данными друг с другом. В альтернативных вариантах воплощения обходной сети 308 файла регистра они могут быть унифицированы. Один альтернативный вариант воплощения обходной сети 308 файла регистра имеет записи в регистре, по меньшей мере, шириной 256 битов для сохранения пакетных операндов источника и назначения, включающих в себя пакетные операнды источника с плавающей запятой и пакетные результаты с плавающей запятой для операций с плавающей запятой ОКМД.

Некоторые варианты воплощения планировщиков 321, 302 и 306 микроопераций могут отправлять зависимые операции до того, как будет закончено выполнение родительской нагрузки. Поскольку микрооперации были запланированы и выполнялись в процессоре 300 спекулятивно, процессор 300 также включает в себя логику для обработки потерь в памяти. Если происходит потеря загрузки данных в кеше для данных, могут существовать зависимые операции, выполняемые в данный момент времени в конвейере, которые оставили в планировщике временно некорректные данные. Механизм повторного воспроизведения может отслеживать и повторно выполнять инструкции, которые используют некорректные данные. Повторное воспроизведение может потребоваться только для зависимых операций, и может быть разрешено окончание независимых операций. После завершения выполнения микроопераций выполняют их окончание в последовательном порядке программы с использованием изменяющей порядок логики 310 окончания операций.

В одном варианте воплощения исполнительный модуль 316 с плавающей запятой включает в себя схему 346 исключения для идентификации исключений для операций с плавающей запятой ОКМД, включающий в себя, например, численные исключения. Обработчик исключения микрокода, который может резидентно находиться в ПЗУ 344 микрокода или в некотором специализированном конечном автомате (например, в схеме 346 исключения), использует ПЗУ 344 микрокода, которое реагирует на численные исключения для инициирования последовательности микроопераций ОКМД для операции с плавающей запятой ОКМД, в которой произошло исключение. В одном варианте воплощения микрооперации ОКМД генерируют два пакетных частичных результата из пакетного результата для операции с плавающей запятой ОКМД. Микрооперация денормализации ОКМД комбинирует два пакетных частичных результата и денормализует один или больше элементов комбинированных пакетных частичных результатов для генерирования пакетного результата для операции с плавающей запятой ОКМД, имеющей один или больше денормализованных элементов. Флаги могут быть установлены и сохранены с пакетными частичными результатами для идентификации денормализованного результата в одном или больше элементов, и в этом случае нормализация одного из пакетных частичных результатов может потребоваться для некоторых вариантов воплощения перед микрооперацией денормализации.

В одном варианте воплощения обработчик исключения микрокода ПЗУ 344 микрокода также можно использовать для инициирования микрооперации нормализации ОКМД для генерирования нормализованного псевдовнутреннего представления с плавающей запятой как части последовательности микроопераций ОКМД для операции с плавающей запятой ОКМД, когда выполняется произведение. Флаги могут быть установлены и сохранены с пакетными результатами для идентификации денормализованного результата, представленного в нормализованном псевдовнутреннем представлении с плавающей запятой. Для данного варианта воплощения микрооперация нормализации ОКМД может не быть необходимой, когда операция с плавающей запятой ОКМД представляет собой сложение, поскольку сумматор с плавающей запятой ОКМД может быть выполнен с возможностью приема пакетных операндов, включающих в себя денормализованные значения как входные данные для суммирования с плавающей запятой ОКМД. В некоторых вариантах воплощения флаги могут быть установлены и сохранены с нормализованным псевдовнутренним представлением с плавающей запятой для идентификации денормализованных элементов и обеспечения возможности реконструкции фактического представления с внутренней плавающей запятой из нормализованного псевдовнутреннего представления с плавающей запятой.

Таким образом, механизм помощи микрокоду, как описано выше, может использовать ПЗУ 344 микрокода для прозрачной обработки исключений с плавающей запятой ОКМД.

На фиг.4 иллюстрируется один альтернативный вариант воплощения устройства 460 для эффективной обработки исключений с плавающей запятой в процессоре, который выполняет инструкции с одним потоком команд и множеством потоков данных (ОКМД). Устройство 460 включает в себя обходную сеть 308 файла регистра, которая функционально соединена с исполнительным модулем 316 с плавающей запятой. В одном варианте воплощения исполнительный модуль 316 с плавающей запятой ОКМД включает в себя модуль 400 сумматора с плавающей запятой ОКМД (FAU, МСП) и модуль 420 умножения с плавающей запятой ОКМД (FMU, МУП). Варианты воплощения, которые включают в себя МСП 400 ОКМД и/или МУП 420 ОКМД, также могут включать себя модуль 410 нормализации с плавающей запятой ОКМД (FNU, МНП) и модуль 430 денормализации с плавающей запятой ОКМД (FDU, МДП).

МСП 400 ОКМД включает в себя сумматоры 401, 402,… 408 с плавающей запятой, которые могут содержать множество сумматоров с плавающей запятой, выполненных с возможностью выполнения суммирования с одиночной точностью, с использованием внутреннего представления плавающей запятой для значения с плавающей запятой и одиночной точностью и множество сумматоров с плавающей запятой, выполненных с возможностью выполнения суммирования с двойной точностью, с использованием внутреннего представления с плавающей запятой для значений с плавающей запятой с двойной точностью. В одном варианте воплощения МСП 400 ОКМД каждый сумматор 401, 402,… 408 с плавающей запятой выполнен с возможностью выполнения суммирования как с одиночной, так и с двойной точностью. В альтернативном варианте воплощения МСП 400 ОКМД сумматоры 401, 402,… 408 с плавающей запятой могут быть разделены и/или скомбинированы для выполнения суммирования с одиночной и/или двойной точностью соответственно. Варианты воплощения сумматоров 401, 402,… 408 с плавающей запятой включают в себя схемы совмещения, предназначенные для совмещения мантисс элементов операнда с плавающей запятой, и схемы суммирования, предназначенные для суммирования мантисс элементов операнда с плавающей запятой.

МСП 400 ОКМД также включает в себя схемы 441, 442, … 448 исключения, соединенные с сумматорами 401, 402, … 408 с плавающей запятой соответственно. Некоторые варианты воплощения схем 441, 442, … 448 исключения содержат схемы детектирования денормализованных элементов, которые предназначены для детектирования денормализованных элементов пакетных операндов для операций суммирования с плавающей запятой ОКМД, и схемы генерирования исключения, предназначенные для идентификации исключительных результатов операций суммирования с плавающей запятой ОКМД, включающих в себя денормализованные результаты. Варианты воплощения схем 441, 442, … 448 исключения также могут быть функционально соединены с ПЗУ 344 микрокода для инициирования последовательности микроопераций, для повторного выполнения операции суммирования с плавающей запятой ОКМД в ответ на идентифицированные результаты исключения. В некоторых вариантах воплощения МСП 400 ОКМД схемы совмещения сумматоров 401, 402,… 408 с плавающей запятой могут совмещать мантиссу денормализованного первого элемента с мантиссой соответствующего второго элемента в соответствии с несмещенной разностью показателя степени (то есть вместо смещенной разности показателя степени), если соответствующий второй элемент не является денормализованным, но оставляют совмещение без изменений, когда как первый, так и второй элементы являются денормализованными. В этих вариантах воплощения сумматоры 401, 402,… 408 с плавающей запятой также могут округлять и повторно нормализовать полученную в результате сумму (например, используя МНП 410), если получаемая в результате сумма может быть представлена как нормальный, получаемый в результате элемент пакетного результата для операции суммирования с плавающей запятой ОКМД. Варианты воплощения сумматоров 401, 402, … 408 с плавающей запятой (или нормализаторов 411, 412, … 418) также могут устанавливать флаг для идентификации результата суммирования как денормализованного элемента пакетного результата, если определяется, что результат не может быть представлен как нормальный, получаемый в результате элемент пакетного результата для операции суммирования с плавающей запятой ОКМД.

Варианты воплощения обходной сети 308 файла регистра также содержат схемы сохранения результата для сохранения пакетных результатов операций с плавающей запятой ОКМД и для сохранения любых флагов, идентифицирующих элементы результата как денормализованные элементы пакетного результата.

МНП 410 ОКМД включает в себя нормализаторы 411, 412, … 418 с плавающей запятой, которые могут содержать множество нормализаторов с плавающей запятой, выполненных с возможностью выполнения нормализации с одиночной точностью, используя внутреннее представление с плавающей запятой для значений с плавающей запятой с одиночной точностью, и множество нормализаторов с плавающей запятой, выполненных с возможностью выполнения нормализации с двойной точностью, используя внутреннее представление с плавающей запятой для значений с плавающей запятой с двойной точностью. В одном варианте воплощения ОКМД МНП 410 каждый нормализатор 411, 412, … 418 с плавающей запятой выполнен с возможностью выполнения как нормализации с одиночной точностью, так и с двойной точностью. В альтернативном варианте воплощения МНП 410 ОКМД нормализаторы 411, 412, … 418 с плавающей запятой могут быть разделены и/или скомбинированы для выполнения нормализации с одиночной и/или двойной точностью соответственно. Варианты воплощения нормализаторов 411, 412, … 418 с плавающей запятой также могут включать в себя схемы округления мантиссы для выполнения одновременного округления с одиночной и/или двойной точностью и нормализации. Некоторые варианты воплощения нормализаторов 411, 412, … 418 с плавающей запятой также могут использовать постоянное значение (например, 10) при нормализации пакетных операндов в псевдовнутреннее представление с плавающей запятой.

МУП 420 ОКМД включает в себя умножители 421, 422, … 428 с плавающей запятой, которые могут содержать множество умножителей с плавающей запятой, выполненных с возможностью выполнения умножения с одиночной точностью, с использованием внутреннего представления с плавающей запятой для значений с одиночной точностью с плавающей запятой, и множество умножителей с плавающей запятой, выполненных с возможностью выполнения умножения с двойной точностью, используя внутреннее представление с плавающей запятой для значений с плавающей запятой с двойной точностью. В одном варианте воплощения МУП 420 ОКМД каждый умножитель 421, 422, … 428 с плавающей запятой выполнен с возможностью выполнения как умножения с одиночной точностью, так и с двойной точностью. В альтернативном варианте воплощения МУП 420 ОКМД умножители 421, 422, … 428 с плавающей запятой могут быть разделены и/или скомбинированы для выполнения умножений с одиночной точностью и/или двойной точностью соответственно.

МУП 420 ОКМД также включает в себя схемы 451, 452, … 458 исключения, соединенные с умножителями 421, 422, … 428 с плавающей запятой соответственно. Некоторые варианты воплощения схем 451, 452,… 458 исключения содержат схемы детектирования денормализованных элементов для детектирования денормализованных элементов пакетных операндов, для операций умножения с плавающей запятой ОКМД и схемы генерирования исключения для идентификации результатов исключения операций умножения с плавающей запятой ОКМД, включающих в себя денормализованные результаты. Варианты воплощения схем 451, 452, … 458 исключения также могут быть функционально соединены с ПЗУ 344 микрокода для инициирования последовательности микроопераций для повторного выполнения операции умножения с плавающей запятой ОКМД в ответ на детектируемые денормализованные элементы пакетных операндов или в ответ на идентифицированные результаты исключения.

Варианты выполнения умножителей 421, 422, … 428 с плавающей запятой могут включать в себя схемы компаратора показателя степени и предсказатели, которые делают прогнозы в отношении некоторых общих результатов (например, нуля, наименьшего репрезентативного денормализованного элемента, или, в случае необходимости, бесконечности), выполняют умножение на элемент исключения операнда на основе сравнений и обеспечивают сохранение результатов таких прогнозов, как результат умножения, для предотвращения исключения. В противном случае, когда такие общие результаты умножения на элемент исключения операнда не прогнозируют, умножение может осуществляться по принятым операндам, и любые исключения, которые возникают, могут быть обработаны в соответствии с альтернативными методиками, описанными здесь (например, как в процессе 801).

МДП 430 ОКМД включает в себя денормализаторы 431, 432, … 438 с плавающей запятой, которые могут содержать множество денормализаторов с плавающей запятой, которые выполнены с возможностью выполнения денормализации с одиночной точностью, используя внутреннее представление с плавающей запятой для значений с плавающей запятой с одиночной точностью, и множество денормализаторов с плавающей запятой, выполненных с возможностью выполнения денормализации с двойной точностью, используя внутреннее представление с плавающей запятой для значений с плавающей запятой с двойной точностью. В одном варианте воплощения МДП 430 ОКМД каждый денормализатор 431, 432, … 438 с плавающей запятой выполнен с возможностью выполнения как денормализации с одиночной, так и с двойной точностью. В альтернативном варианте воплощения МДП 430 ОКМД денормализаторы 431, 432, … 438 с плавающей запятой могут быть разделены и/или скомбинированы для выполнения денормализации с одиночной и/или с двойной точностью соответственно. Варианты воплощения денормализаторов 431, 432, … 438 с плавающей запятой также могут включать в себя схемы округления мантиссы, предназначенные для выполнения одновременного округления с одиночной и/или двойной точностью и денормализации. Некоторые варианты воплощения денормализаторов 431, 432, … 438 с плавающей запятой могут быть выполнены с возможностью использования постоянных денормализованных степенных значений (например, -126 или -1022) при денормализации пар пакетных частичных результатов.

Варианты воплощения МНП 410 ОКМД могут во время работы формировать псевдовнутренние представления с плавающей запятой пакетных операндов, имеющих элементы с плавающей запятой нормального и/или денормализованного компонента. Варианты воплощения МСП 400 ОКМД и МУП 420 ОКМД могут работать в нормальном режиме для получения одиночного пакетного результата, имеющего элементы с плавающей запятой - нормальные компоненты, и в режиме обработки численного исключения из пакетного результата формируют два пакетных частичных результата, имеющих элементы с плавающей запятой, представляющие собой нормальные и/или денормализованные компоненты. В одном варианте выполнения режима обработки с численным исключением пакетный частичный результат фазы один и пакетный частичный результат фазы два могут быть сохранены в отдельных местах сохранения в файле регистра (одновременно или по отдельности в любом временном порядке), при этом они составляют два пакетных частичных результата. Варианты воплощения ПЗУ 344 микрокода также могут включать в себя микрооперации, которые обозначают для МСП 400 ОКМД и МУП 420 ОКМД, выполняют ли они режим обработки из численного исключения фазы один или режим обработки из численного исключения фазы два. Варианты воплощения МДП 430 ОКМД могут во время работы принимать два пакетных частичных результата, состоящих из пакетного результата, имеющего элементы с плавающей запятой с нормальным и/или денормализованным компонентом, и для получения одиночного пакетного результата, имеющего элементы с плавающей запятой с нормальными и/или денормализованнымии компонентам.

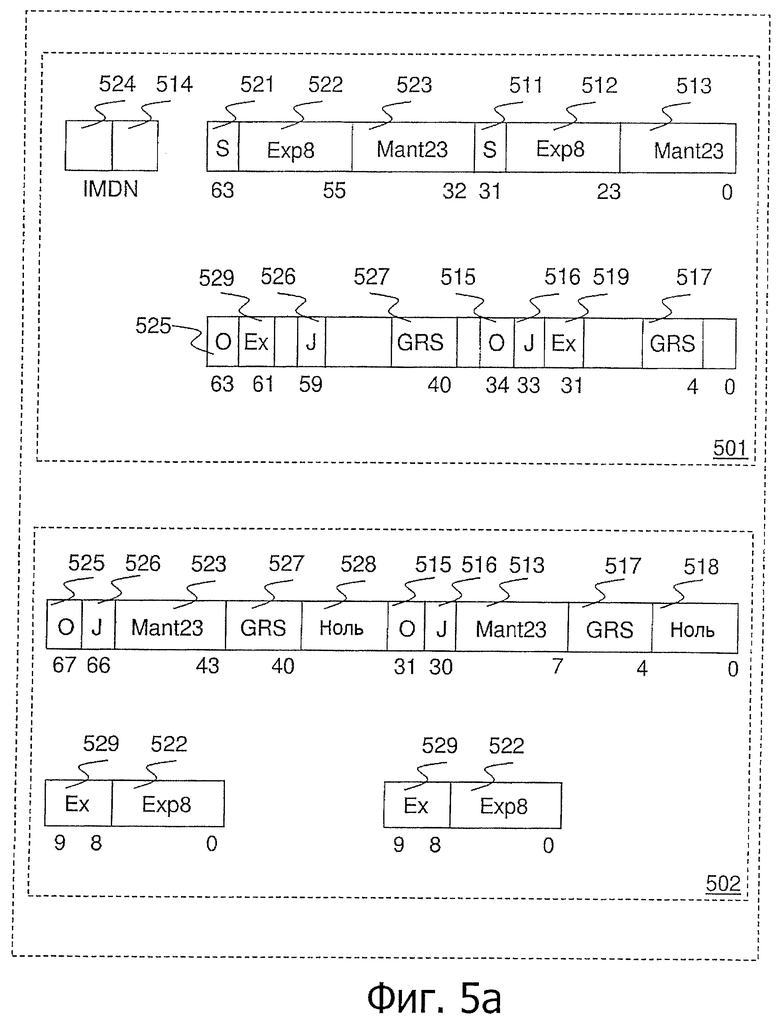

На фиг.5а иллюстрируются примерные форматы 501 и 502 сохранения, предназначенные для сохранения внутренних представлений пакетных чисел с плавающей запятой. Формат 501 и формат 502 представлены с использованием пары чисел с плавающей запятой с одиночной точностью, но следует понимать, что формат 501 и формат 502 представляют собой всего лишь представление типично более широких пакетных операндов с плавающей запятой (например, пакетных операндов, имеющих 4 элемента с одиночной точностью или 2 элемента с двойной точностью, или пакетные операнды, имеющие 8 элементов с одиночной точностью или 4 элемента с двойной точностью).

Формат 501 представляет собой пример пары пакетных частичных результатов (в файле регистра ОКМД, например, в таком как обходная сеть 308 файла регистра) пакетного операнда назначения с одиночной точностью для операций с плавающей запятой ОКМД. Формат 501 включает в себя пару элементов одиночной точности, каждый из которых содержит 39 битов: первый элемент, включающий в себя бит знака (S 511), 10 битов показателя степени (Ех 519 и Ехр 8512) и 28 битов мантиссы (О 515, явно заданный бит J 516, Mant23 513 и GRS 517); и второй элемент, включающий в себя бит знака (S 521), 10 битов показателя степени (Ех 529 и Ехр8 522) и 28 битов мантиссы (О 525, явно заданный бит J 526, Mant23 523 и GRS 527). Формат 501 включает в себя пару битов флага IMDN 514 и 524, который идентифицируют, представляет ли собой первый элемент и/или второй элемент соответственно денормализованные элементы.

В одном варианте воплощения формата 501 компоненты пары элементов одиночной точности сохраняют в двух регистрах пакетных данных: первый регистр пакетных данных содержит пару битов флага IMDN 514 и 524, бит знака S 521 (например, бит 63), биты показателя степени Ехр8 522 (например, биты 62-55), биты мантиссы Mant23 523 (например, биты 54-32), бит знака S 511 (например, бит 31), биты показателя степени Ехр8 512 (например, биты 30-23), биты мантиссы Mant23 513 (например, биты 22-0); и второй регистр пакетных данных содержит два старших значимых бита мантиссы О 525 и J 526 (например, биты 63 и 59), биты показателя степени Ех 529 (например, биты 62-61), три младших значимых бита мантиссы GRS 527 (например, биты 42-40), два старших значимых бита мантиссы O 515 и J 516 (например, биты 34-33), биты показателя степени Ех 519 (например, биты 32-31) и три младших значимых бита мантиссы GRS 517 (например, биты 6-4).

Следует понимать, что конструктор может выбрать определенные места расположения, где компоненты пакетных элементов сохраняются в двух регистрах пакетных данных как пара пакетных частичных результатов, с тем, чтобы удобно способствовать перемножению компонентов пакетных элементов из пары пакетных частичных результатов во внутреннее представление с плавающей запятой арифметического модуля с плавающей запятой (например, МСП 400 ОКМД и/или МДП 430 ОКМД для денормализации).

Формат 502 представляет пример внутреннего представления с плавающей запятой (в арифметическом модуле с плавающей запятой, например, таком как МСП 400) пакетного операнда источника для операций с плавающей запятой ОКМД. Как и в формате 501, формат 502 включает в себя внутренние представления пары элементов с одиночной точностью, каждый из которых содержит 39 битов: первый элемент включает в себя бит знака (S 511), 10 битов показателя степени (Ех 519 и Ехр8 512) и 28 битов мантиссы (О 515, J 516, Mant23 513 и GRS 517); и второй элемент включает в себя бит знака (S 521), 10 битов показателя степени (Ех 529 и Ехр8 522) и 28 битов мантиссы (О 525, J 526, Mant23 523 и GRS 527). В одном варианте воплощения формата 502 внутреннее представление с плавающей запятой арифметического модуля с плавающей запятой содержит отдельные показатели степени: Ех 519 и Ехр8 512 для первого элемента (например, биты 9-0) и Ех 529 и Ехр8 522 для второго элемента (например, биты 9-0). В данном варианте воплощения формата 502 мантиссы двух элементов могут быть сохранены как пакетные мантиссы: первая мантисса имеет O 515 (например, бит 67), J 516 (например, бит 66), Mant23 513 (например, биты 65-43) и GRS 517 (например, биты 42-40); и вторая мантисса имеет О 525 (например, бит 31), J 526 (например, бит 30), Mant23 523 (например, биты 29-7) и GRS 527 (например, биты 6-4); с заполнением нулями в младших значащих битах каждого из них (например, биты 39-32 и биты 3-0).

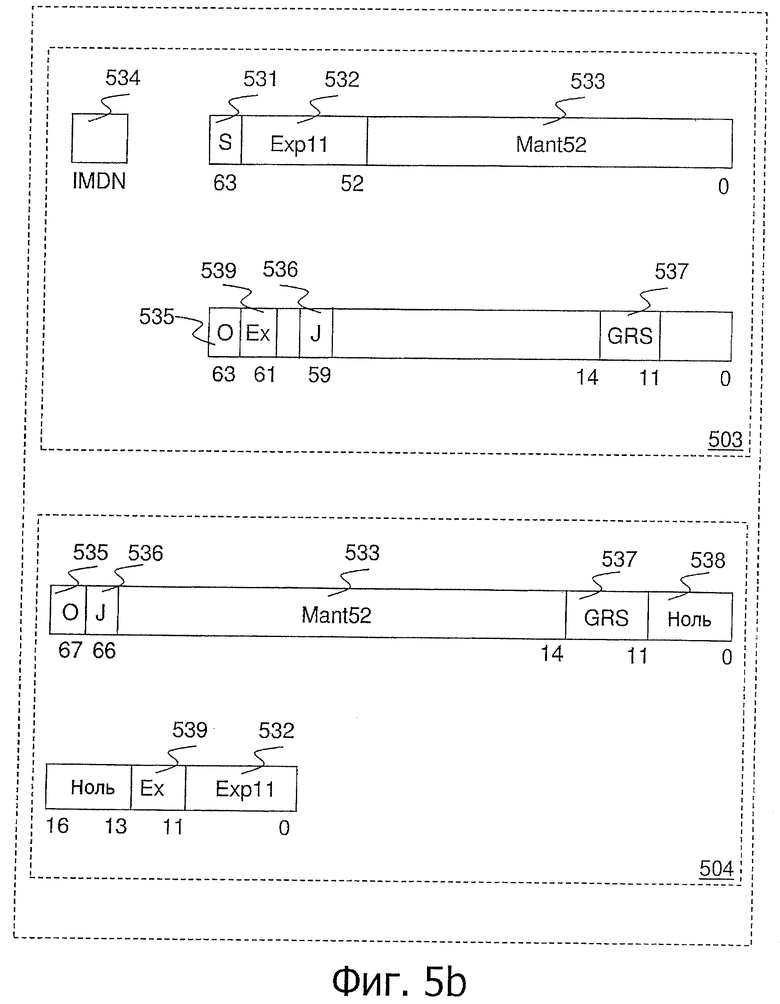

На фиг.5b иллюстрируются примерные форматы 503 и 504 сохранения, предназначенные для сохранения внутренних представлений пакетных чисел с плавающей запятой. Формат 503 и формат 504 иллюстрируются с использованием числа с плавающей запятой с двойной точностью, но следует понимать, что формат 503 и формат 504 просто представляют типично более широкие пакетные операнды с плавающей запятой (например, пакетные операнды, имеющие 4 элемента с одиночной точностью или 2 элемента с двойной точностью, или пакетные операнды, имеющие 8 элементов с одиночной точностью или 4 элемента с двойной точностью).

Формат 503 представляет пример пары пакетных частичных результатов (в файле регистра ОКМД, например, таком как обходная сеть 308 в файле регистра) элемента операнда назначения с двойной точностью пакетного операнда для операций с плавающей запятой ОКМД. Формат 503 включает в себя пару пакетных частичных результатов элемента с двойной точностью, содержащего 71 или больше битов, включающего в себя: бит знака (S 531), 13 или больше битов показателя степени (Ех 539 и Ехр11 532) и 57 битов мантиссы (О 535, явно заданный бит J 536, Mant52 533 и GRS 537). Формат 503 включает в себя бит флага IMDN 534, связанный с каждым элементом с двойной точностью, для идентификации, является ли этот элемент денормализованным элементом.

Следует понимать, что конструктор может выбрать специфичные места расположения, где компоненты пакетных элементов содержатся в двух регистрах пакетных данных, как пара пакетных частичных результатов, для того, чтобы удобно способствовать умножению компонентов пакетных элементов из пары пакетных частичных результатов во внутреннее представление с плавающей запятой арифметического модуля с плавающей запятой.

Формат 504 представляет пример внутреннего представления с плавающей запятой (в арифметическом модуле с плавающей запятой, например, таком как МСП 400) элемента пакетного операнда источника для пакетного операнда операций с плавающей запятой ОКМД. Как и формат 503, формат 504 включает в себя внутреннее представление элементов с двойной точностью, содержащих 71 или больше битов, включающих в себя: бит знака (S 531), 13 или больше битов показателя степени (Ех 539 и Ехр11 532) и 57 битов мантиссы (О 535, J 536, Mant52 533 и GRS 537). В одном варианте воплощения формата 504 внутреннее представление с плавающей запятой арифметического модуля с плавающей запятой содержит отдельные показатели степени Ех 539 и Ехр11 532 для каждого элемента (например, битов 16-0). В этом варианте воплощения формата 504 мантиссы пакетных элементов могут быть сохранены как пакетные мантиссы, при этом первая мантисса имеет: О 535 (например, бит 67), J 536 (например, бит 66), Mant52 533 (например, биты 65-14) и GRS 537 (например, биты 14-11), с нулевым заполнением в младших значащих битах каждого (например, биты 10-0).

Следует понимать, что, используя форматы 501-504 внутреннего сохранения, пакетные данные с плавающей запятой можно сохранять в регистрах с фиксированным размером, в то время как исключения с плавающей запятой ОКМД можно обрабатывать прозрачно, без преобразования в скалярные операции и с необходимостью выполнения только малого количества дополнительных микроопераций. Также следует понимать, что в вариантах воплощения формата 501, 502, 503 и/или 504 некоторые биты (например, О 525, J 526, О 535 и/или J 536) могут быть представлены неявно заданными.

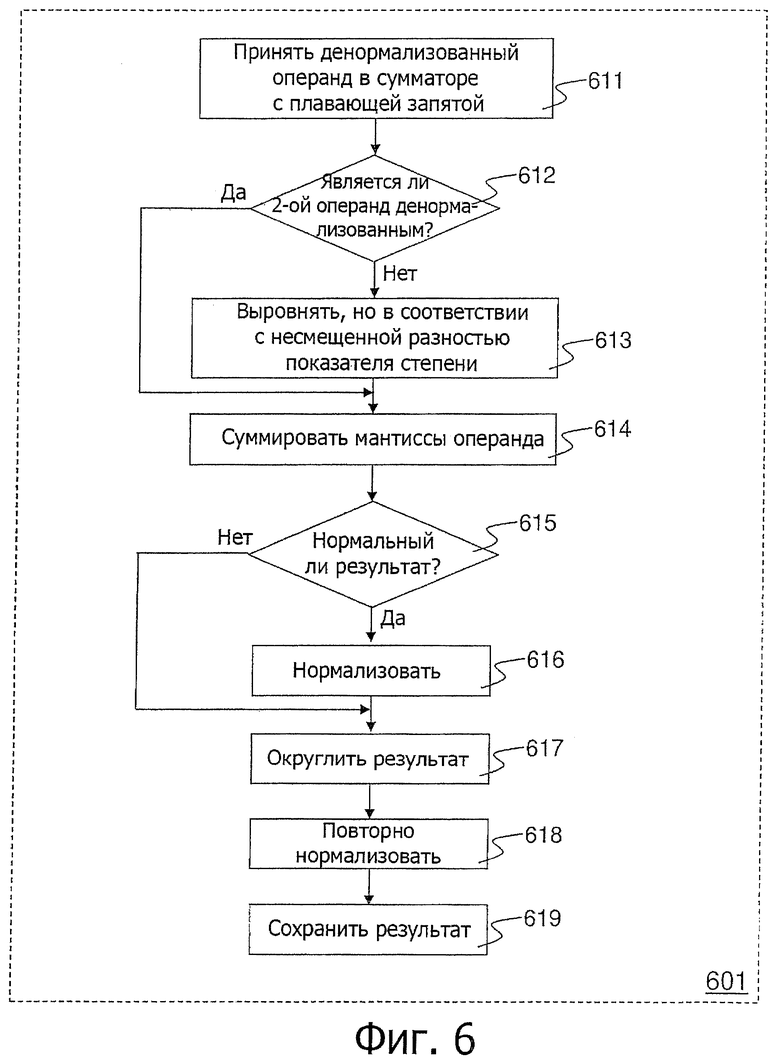

На фиг.6 иллюстрируется блок-схема последовательности операций одного варианта воплощения процесса 601 для обработки определенных численных исключений в сумматоре с плавающей запятой ОКМД. Процесс 601 и другие процессы, раскрытые здесь, выполняют с помощью блоков обработки, которые могут содержать специализированные аппаратное или программное средство, или коды операций встроенного программного обеспечения, выполняемые устройствами общего назначения, или устройствами специального назначения, или с использованием комбинаций обоих этих подходов. Некоторые варианты воплощения процесса 601 и других процессов, раскрытых здесь, воплощены в виде исполняемых устройством инструкций или переходов состояния. Инструкции или переходы состояния можно использовать для обеспечения выполнения этапов настоящего изобретения процессором общего назначения или специализированным процессором, который запрограммирован с использованием инструкций или переходов состояний.

Настоящее изобретение может быть представлено как компьютерный программный продукт, или программное средство, или фрагмент микрокода, который может включать в себя считываемый устройством или считываемый компьютером носитель информации, на котором записаны инструкции, или переходы состояния, которые можно использовать для программирования компьютера (или других электронных устройств), для выполнения обработки в соответствии с настоящим изобретением. Такое программное средство может быть сохранено в запоминающем устройстве системе или в сетевом сервере. Аналогично, код может распределяться через сеть или с помощью других считываемых компьютером носителей информации. Таким образом, считываемый устройством носитель может включать в себя любой механизм для сохранения или передачи информации в форме, считываемой устройством (например, компьютером), но не ограничивается этим, такой как гибкие дискеты, оптические диски, компакт-диск, постоянное запоминающее устройство (CD-ROM, КД-ПЗУ), и магнитооптические диски, постоянное запоминающее устройство (ROM, ПЗУ), оперативное запоминающее устройство (RAM, ОЗУ), стираемое программируемое постоянное запоминающее устройство (EPROM, СППЗУ), электрически стираемое программируемое постоянное запоминающее устройство (EEPROM, ЭСППЗУ), магнитные или оптические карты, запоминающее устройство типа флэш, передача через Интернет, электрические, оптические, акустические или другие формы распространяющихся сигналов.

Начиная в блоке 611 обработки, денормализованный элемент операнда пакетного операнда для операции суммирования с плавающей запятой ОКМД принимают в одной из схем сумматора с плавающей запятой МСП ОКМД. В блоке 612 обработки определяют, является ли соответствующий второй элемент операнда второго пакетного операнда для операции суммирования с плавающей запятой ОКМД также денормализованным элементом. В одном варианте воплощения денормализованный элемент операнда и потенциально соответствующий второй элемент операнда могут быть детектированы с помощью схемы детектирования денормализованных элементов (например, одной из схем 441-448).

Если соответствующий второй элемент операнда не является денормализованным, денормализованный элемент операнда и соответствующий второй элемент операнда вводят в схему совмещения в блоке 613 обработки, где мантиссу денормализованного элемента операнда совмещают с мантиссой соответствующего второго элемента операнда в соответствии с несмещенной разностью показателя степени. В остальном мантиссы денормализованного элемента операнда и соответствующего второго элемента операнда уже выровнены, если соответствующий второй элемент операнда также является денормализованным, поэтому обработка переходит непосредственно в блок 614 обработки, где мантиссы суммируют с помощью схемы суммирования с плавающей запятой.

В блоке 615 обработки определяют, может ли результат суммирования быть представлен как нормальный элемент результата с плавающей запятой пакетного результата для операции суммирования с плавающей запятой ОКМД. Если это так, полученную в результате сумму нормализуют в блоке 616 обработки. В противном случае полученную в результате сумму просто округляют в блоке 617 обработки и ее повторно нормализуют (например, сдвигают вправо на один бит, если О равно 1) в блоке 618 обработки, и денормализованный результат может быть сохранен как элемент пакетного результата, когда пакетный результат для операции суммирования с плавающей запятой ОКМД сохраняют в блоке 619 обработки. Следует понимать, что схема сохранения результата, в которой сохраняют пакетный результат для операции суммирования с плавающей запятой ОКМД, также может сохранять флаг, идентифицирующий полученную в результате сумму, как денормализованный элемент результата пакетного результата, если в блоке 615 обработки определяют, что полученная в результате сумма не может быть представлена как нормальный элемент результата с плавающей запятой.

Следует понимать, что варианты воплощения обработки 601 могут обрабатывать общие входы исключения, например денормализованные элементы в операциях с плавающей запятой ОКМД в исполнительном модуле ОКМД (например, исполнительном модуле 316 с плавающей запятой ОКМД), без необходимости дополнительной помощи (например, от микрокода).

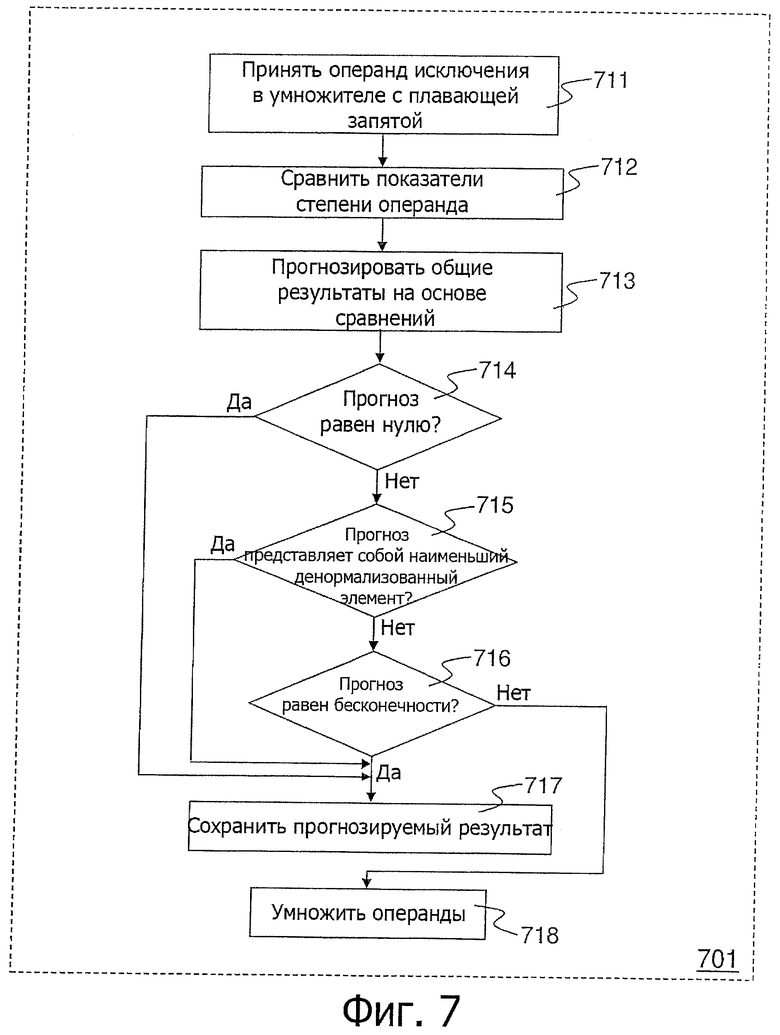

На фиг.7 иллюстрируется блок-схема последовательности операций для одного варианта воплощения обработки 701, которая обрабатывает определенные общие (маскированные) исключения в умножителе с плавающей запятой ОКМД. В блоке 711 обработки принимают исключительный элемент операнда для пакетного операнда операции умножения с плавающей запятой ОКМД в одной из схем умножителя с плавающей запятой МУП ОКМД. В блоке 712 обработки сравнивают показатели степени для соответствующих элементов операнда. На основе сравнения делают прогноз по некоторым общим результатам умножения с помощью элемента исключения операнда в блоке 713 обработки. В блоке 714 обработки, если прогнозируемый результат равен нулю, обработка переходит в блок 717 обработки, где прогнозируемое значение, равное нулю, сохраняют как результат. В противном случае обработка продолжается в блоке 715 обработки, где, если прогнозируемый результат должен представлять собой наименьшее представительное денормализованное число, обработка переходит в блок 717 обработки, где прогнозируемое наименьшее представительное денормализованное значение сохраняют как результат. В противном случае обработка, в случае необходимости, продолжается в блоке 716 обработки, где, если прогнозируемый результат будет равен бесконечности, обработка переходит в блок 717 обработки, где прогнозируемое значение бесконечности сохраняют как результат. В противном случае, в блоке 718 обработки для принятых операндов выполняют умножение и любые исключения, которые возникают, обрабатывают в соответствии с альтернативными методиками, описанными здесь (например, как при обработке 801).

Следует понимать, что варианты воплощения обработки 701 могут прогнозировать и обрабатывать общие результаты исключения операций с плавающей запятой ОКМД в исполнительном модуле ОКМД (например, в исполнительном модуле 316 с плавающей запятой ОКМД), без необходимости дополнительной помощи (например, от микрокода). В таких постоянно возникающих случаях потери, связанные с обработкой случаев исключения, могут быть в существенной степени устранены или уменьшены. В качестве альтернативы, в остальных случаях можно использовать методики обработки исключения с плавающей запятой ОКМД без преобразования в скалярные операции, которые требуют только малого количества дополнительных микроопераций.

На фиг.8 иллюстрируется блок-схема последовательности операций альтернативного варианта воплощения обработки 801 для обработки денормализованных исключений с плавающей запятой в процессоре, который выполняет инструкции с плавающей запятой ОКМД. В блоке 811 обработки числовое исключение идентифицируют для операции с плавающей запятой ОКМД. В зависимости от числового исключения одну или больше необязательных микроопераций нормализации инициируют в блоке 812 обработки, в случае необходимости. В одном варианте воплощения обработки 801 микрооперации нормализации инициируют, если операция с плавающей запятой ОКМД должна быть выполнена, по меньшей мере, частично умножителем с плавающей запятой ОКМД (например, умножение, деление, квадратный корень или преобразование из одиночной в двойную точность). В результате выполнения микрооперации нормализации может быть сохранен пакетный операнд, как нормализованное псевдовнутреннее представление с плавающей запятой исходного пакетного операнда для операции с плавающей запятой ОКМД, содержащейся в денормализованном элементе. Для одного варианта воплощения обработки 801 микрооперация (микрооперации) нормализации не требуется, если операция с плавающей запятой ОКМД должна быть выполнена сумматором с плавающей запятой ОКМД (например, суммирование/вычитание или преобразование из двойной в одиночную точность), поскольку сумматор с плавающей запятой ОКМД может быть выполнен с возможностью приема операндов, содержащих денормализованные элементы как входные данные.

В блоке 813 обработки первую микрооперацию ОКМД инициируют для генерирования первого пакетного частичного результата для операции с плавающей запятой ОКМД и вторую микрооперацию ОКМД инициируют для генерирования второго пакетного частичного результата для операции с плавающей запятой ОКМД. Следует понимать, что в некоторых вариантах воплощения обработки 801 первая и вторая микрооперация ОКМД могут быть выполнены в любом порядке, если только они формируют пару пакетных частичных результатов, сохраняемых для пакетного результата для операции с плавающей запятой ОКМД.

В блоке 814 обработки микрооперацию денормализации ОКМД инициируют для комбинирования пары пакетных частичных результатов и для денормализации, в соответствии с необходимостью, любых элементов комбинированных пакетных частичных результатов, для генерирования пакетного результата, имеющего соответствующие денормализованные элементы. Для некоторых вариантов воплощения МСП 400 ОКМД комбинированная пара пакетных частичных результатов также может включать в себя нормализацию пакетных частичных результатов в режиме обработки численного исключения фазы один. В блоке 815 обработки флаги исключения (например, IMDN 514 и 524 или 534) рассчитывают для идентификации денормализованных элементов пакетного результата. Такие флаги исключения сохраняют как результаты вместе с пакетным результатом для операции с плавающей запятой ОКМД в блоке 816 обработки.

Следует понимать, что варианты воплощения обработки 801 обеспечивают эффективные методики, которые можно использовать для обработки исключения с плавающей запятой ОКМД, которые позволяют получать денормализованные элементы и требуют повторного выполнения. Такие исключения можно прозрачно обрабатывать, параллельно с преобразованием в скалярные операции, и при этом требуется выполнение только небольшого количества дополнительных микроопераций.

Приведенное выше описание предназначено для иллюстрации предпочтительных вариантов воплощения настоящего изобретения. Из приведенного выше описания должно быть также понятно, что, в частности, в такой области технологии, где происходит быстрый рост и трудно предусмотреть дальнейшее усовершенствование, изобретение может быть модифицировано по компоновкам и в деталях специалистами в данной области техники, без выхода за пределы принципов настоящего изобретения, в соответствии с объемом приложенной формулы изобретения и ее эквивалентов.

| название | год | авторы | номер документа |

|---|---|---|---|

| ИНСТРУКЦИЯ И ЛОГИЧЕСКАЯ СХЕМА ДЛЯ ВЫПОЛНЕНИЯ ОПЕРАЦИИ СКАЛЯРНОГО ПРОИЗВЕДЕНИЯ | 2007 |

|

RU2421796C2 |

| ВЫПОЛНЕНИЕ ОПЕРАЦИЙ ОКРУГЛЕНИЯ В СООТВЕТСТВИИ С ИНСТРУКЦИЕЙ | 2011 |

|

RU2447484C1 |

| ВЫПОЛНЕНИЕ ОПЕРАЦИЙ ОКРУГЛЕНИЯ В СООТВЕТСТВИИ С ИНСТРУКЦИЕЙ | 2007 |

|

RU2420790C2 |

| СПОСОБ И УСТРОЙСТВО ТАСОВАНИЯ ДАННЫХ | 2004 |

|

RU2316808C2 |

| ЦЕЛОЧИСЛЕННОЕ УМНОЖЕНИЕ ВЫСОКОГО ПОРЯДКА С ОКРУГЛЕНИЕМ И СДВИГОМ В АРХИТЕКТУРЕ С ОДНИМ ПОТОКОМ КОМАНД И МНОЖЕСТВОМ ПОТОКОВ ДАННЫХ | 2003 |

|

RU2263947C2 |

| СПОСОБ И УСТРОЙСТВО ДЛЯ ВЫПОЛНЕНИЯ КОМАНД С ПЛАВАЮЩЕЙ ЗАПЯТОЙ И УПАКОВАННЫХ ДАННЫХ, ИСПОЛЬЗУЯ ОДИНОЧНЫЙ ФАЙЛ РЕГИСТРА | 1996 |

|

RU2179331C2 |

| СИСТЕМЫ И СПОСОБЫ ОТСЛЕЖИВАНИЯ ФЛАГА В ОПЕРАЦИЯХ УСТРАНЕНИЯ ПЕРЕМЕЩЕНИЯ | 2014 |

|

RU2628156C2 |

| Устройство для округления суммы и разности двоично-кодированных чисел с плавающей запятой | 1986 |

|

SU1361542A1 |

| Устройство для округления суммы и разности двоичнокодированных чисел с плавающей запятой | 1986 |

|

SU1339549A1 |

| СПОСОБ, УСТРОЙСТВО И КОМАНДА ДЛЯ ВЫПОЛНЕНИЯ ЗНАКОВОЙ ОПЕРАЦИИ УМНОЖЕНИЯ | 2003 |

|

RU2275677C2 |

Изобретение относится к способу и устройствам для обработки исключения с плавающей запятой в процессоре, который выполняет инструкции с одним потоком команд и множеством потоков данных (ОКМД). Техническим результатом является повышение быстродействия при использовании денормализованных чисел. В способе: числовые исключения идентифицированы для операции с плавающей запятой ОКМД, и микрооперации ОКМД инициируют для генерирования двух пакетных частичных результатов пакетного результата для операции с плавающей запятой ОКМД. Микрооперацию денормализации ОКМД инициируют для комбинирования двух пакетных частичных результатов и для денормализации одного или больше элементов комбинированных пакетных частичных результатов, для генерирования пакетного результата для операции с плавающей запятой ОКМД, имеющей один или больше денормализованных элементов. Флаги устанавливают и сохраняют с пакетными частичными результатами для идентификации денормализованных элементов. 4 н. и 18 з.п. ф-лы, 9 ил., 1 табл.

1. Способ обработки исключения с плавающей запятой в процессоре, который выполняет инструкции с одним потоком команд и множеством потоков данных (ОКМД), способ, содержащий:

идентифицируют числовое исключение для операции с плавающей запятой ОКМД;

инициируют первую микрооперацию ОКМД для генерирования первого пакетного частичного результата для операции с плавающей запятой ОКМД;

инициируют вторую микрооперацию ОКМД для генерирования второго пакетного частичного результата для операции с плавающей запятой ОКМД;

инициируют микрооперацию денормализации ОКМД для комбинирования первого и второго пакетных частичных результатов и для денормализации первого элемента комбинированных первого и второго пакетных частичных результатов, для генерирования третьего пакетного результата, имеющего денормализованный элемент;

сохраняют третий пакетный результат для операции с плавающей запятой ОКМД и

устанавливают флаг, идентифицирующий денормализованный элемент третьего пакетного результата в упомянутом первом пакетном частичном результате.

2. Способ по п.1, дополнительно содержащий:

инициируют микрооперацию нормализации ОКМД по первому пакетному частичному результату для операции с плавающей запятой ОКМД.

3. Способ по п.1, в котором набор из одного или больше пакетных операндов источника, используемых для формирования первого и второго пакетных частичных результатов для операции с плавающей запятой ОКМД, сохраняют с их исходной шириной представления.

4. Способ по п.1 дополнительно содержащий:

инициируют микрооперацию нормализации ОКМД, если операция с плавающей запятой ОКМД должна быть выполнена, по меньшей мере, частично умножителем с плавающей запятой ОКМД.

5. Способ по п.3, в котором микрооперация нормализации ОКМД нормализует второй элемент в псевдовнутреннем представлении с плавающей запятой пакетного операнда для операции с плавающей запятой ОКМД, причем второй элемент соответствует денормализованному элементу пакетного операнда для операции с плавающей запятой ОКМД.

6. Способ по п.5, в котором флаг сохраняют с псевдовнутренним представлением с плавающей запятой пакетного операнда для операции с плавающей запятой ОКМД, идентифицирующим второй элемент как соответствующий упомянутому денормализованному элементу.

7. Носитель информации, считываемый устройством, включающий в себя данные и инструкции для обработки числового исключения для операции с плавающей запятой ОКМД, которые при доступе к ним устройства обеспечивают, что устройство:

инициирует первую микрооперацию ОКМД для генерирования первого пакетного частичного результата для операции с плавающей запятой ОКМД;

инициирует вторую микрооперацию ОКМД для генерирования второго пакетного частичного результата для операции с плавающей запятой ОКМД;

инициирует микрооперацию денормализации ОКМД для комбинирования первого и второго пакетных частичных результатов и для денормализации первого элемента комбинированных первого и второго пакетных частичных результатов для генерирования третьего пакетного результата, имеющего денормализованный элемент;

сохраняет третий пакетный результат для операции с плавающей запятой ОКМД

и

устанавливает флаг, идентифицирующий денормализованный элемент третьего пакетного результата в упомянутом первом пакетном частичном результате.

8. Носитель информации по п.7, который включает в себя данные и инструкции, которые при доступе к ним устройства обеспечивают, что устройство:

инициирует микрооперацию нормализации ОКМД для первого пакетного частичного результата для операции с плавающей запятой ОКМД.

9. Носитель информации по п.7, в котором набор из одного или больше пакетных операндов источника, используемых для формирования первого и второго пакетных частичных результатов для операции с плавающей запятой ОКМД, сохраняют с их исходной шириной представления.

10. Носитель информации по п.7, который включает в себя такие данные и инструкции, которые при доступе к ним устройства обеспечивают, что устройство:

инициирует микрооперацию нормализации ОКМД, если операция с плавающей запятой ОКМД должна быть выполнена, по меньшей мере, частично умножителем с плавающей запятой ОКМД.

11. Носитель информации по п.10, в котором микрооперация нормализации ОКМД нормализует второй элемент в псевдовнутреннее представление с плавающей запятой пакетного операнда для операции с плавающей запятой ОКМД, причем второй элемент соответствует денормализованному элементу пакетного операнда для операции с плавающей запятой ОКМД.

12. Носитель информации по п.11, в котором флаг сохраняют с псевдовнутренним представлением с плавающей запятой пакетного операнда для операции с плавающей запятой ОКМД, идентифицирующей второй элемент как соответствующий упомянутому денормализованному элементу.

13. Устройство для выполнения операции суммирования с плавающей запятой ОКМД, содержащее:

первую схему детектирования денормализованного элемента, предназначенную для детектирования денормализованного первого элемента первого пакетного операнда для операции суммирования с плавающей запятой ОКМД;

вторую схему детектирования денормализованного элемента, предназначенную для детектирования, является ли соответствующий второй элемент второго пакетного операнда для операции суммирования с плавающей запятой ОКМД также денормализованным;

схему совмещения, предназначенную для совмещения мантиссы денормализованного первого элемента с мантиссой соответствующего второго элемента в соответствии с несмещенной разностью показателя степени, если соответствующий второй элемент не является также денормализованным элементом;

схему сумматора, предназначенную для суммирования мантиссы первого элемента и мантиссы второго элемента и для нормализации полученной суммы, если определяют, что получаемая в результате сумма может присутствовать как нормальный элемент полученного результата пакетного результата для операции суммирования с плавающей запятой ОКМД; и

схему сохранения результата, предназначенную для сохранения пакетного результата для операции суммирования с плавающей запятой ОКМД и для сохранения флага, идентифицирующего результат суммирования как денормализованный элемент результата для пакетного результата, если определяют, что полученная в результате сумма не может быть представлена как нормальный элемент результата пакетного результата для операции суммирования с плавающей запятой ОКМД.

14. Устройство по п.13, имеющее режим обработки численных исключений, в котором первый пакетный частичный результат и второй пакетный частичный результат сохраняют для операции суммирования с плавающей запятой ОКМД.

15. Устройство по п.13, содержащее:

схему нормализации, предназначенную для нормализации первого пакетного частичного результата, сохраненного для операции суммирования с плавающей запятой ОКМД.

16. Процессор, содержащий:

файл регистра, предназначенный для сохранения множества пакетных операндов с плавающей запятой и множества пакетных результатов с плавающей запятой для операций с плавающей запятой ОКМД;

схему генерирования исключения, предназначенную для идентификации численного исключения для первой операции с плавающей запятой ОКМД;

обработчик исключения микрокода, который реагирует на численное исключение, инициируя первую микрооперацию ОКМД, для генерирования первого пакетного результата для операции с плавающей запятой ОКМД;

обработчик исключения микрокода, дополнительно реагирующий на числовое исключение, для инициирования второй микрооперации ОКМД, для генерирования второго пакетного результата для операции с плавающей запятой ОКМД;

обработчик исключения микрокода, дополнительно реагирующий на числовые исключения, для инициирования микрооперации денормализации ОКМД: для комбинирования первого и второго пакетных результатов, для денормализации элемента комбинированных первого и второго пакетных результатов, для генерирования третьего пакетного результата, имеющего денормализованный элемент, для сохранения третьего пакетного результата для операции с плавающей запятой ОКМД и для установки флага, идентифицирующего денормализованный первый элемент третьего пакетного результата в упомянутом первом пакетном результате.

17. Процессор по п.16, в котором первый пакетный результат и второй пакетный результат содержат пару пакетных частичных результатов, имеющих биты суммирования показателя степени и биты мантиссы при поддержке операций с плавающей запятой ОКМД, которые формируют или потребляют пакетные данные, имеющие денормализованные элементы.

18. Процессор по п.16, дополнительно содержащий модуль суммирования с плавающей запятой ОКМД для:

детектирования денормализованного первого элемента первого пакетного операнда для операции суммирования с плавающей запятой ОКМД;

детектирования, является ли соответствующий второй элемент второго пакетного операнда для операции суммирования с плавающей запятой ОКМД также денормализованным элементом;

выравнивают мантиссу денормализованного первого элемента с мантиссой соответствующего второго элемента в соответствии с несмещенной разностью показателя степени, если соответствующий элемент не является также ненормализованным;

суммируют мантиссы первого и мантиссы второго элементов и для нормализации результата суммирования, если он определяет, что результат суммирования может представлять нормальный элемент - результат для пакетного результата операции суммирования с плавающей запятой ОКМД;

сохраняют пакетный результат для операции суммирования с плавающей запятой ОКМД и

устанавливают флаг, обозначающий результат суммирования как нормальный элемент - результат для пакетного результата, если определяют, что результат суммирования может представлять нормальный элемент - результат.

19. Процессор по п.16, причем обработчик исключения микрокода дополнительно реагирует на числовые исключения для инициирования микрооперации нормализации ОКМД, если операция с плавающей запятой ОКМД должна быть выполнена, по меньшей мере, частично умножителем с плавающей запятой ОКМД.

20. Процессор по п.19, в котором пакетные результаты микрооперации нормализации ОКМД сохраняют с их исходной шириной представления.

21. Процессор по п.19, в котором микрооперация нормализации ОКМД нормализует первый элемент в псевдовнутреннее представление с плавающей запятой пакетного операнда для операции с плавающей запятой ОКМД, причем первый элемент соответствует денормализованному элементу пакетного операнда для операции с плавающей запятой ОКМД.

22. Процессор по п.21, в котором флаг сохраняют с псевдовнутренним представлением плавающей запятой пакетного операнда для операции с плавающей запятой ОКМД, идентифицирующей первый элемент как соответствующий упомянутому денормализованному элементу.

| Импульсный конденсаторный частотомер | 1956 |

|

SU113220A1 |

| 1968 |

|

SU412690A3 | |

| US 7337307 B1, 26.02.2008 | |||

| US 2005193156 A1, 01.09.2005 | |||

| CN 101221492 A, 16.07.2008. | |||

Авторы

Даты

2011-08-27—Публикация

2009-06-29—Подача