Изобретение относится к области радиоэлектроники и может быть использовано в качестве прецизионного устройства усиления широкополосных сигналов.

В современной радиоэлектронной аппаратуре находят применение дифференциальные операционные усилители (ОУ) и трансимпедансные преобразователи, выполненные на базе входного дифференциального каскада (ДК) с активной нагрузкой в виде классических токовых зеркал [1-8], в т.ч. так называемых токовых зеркал Вильсона [9-12]. ОУ с такой архитектурой, в т.ч. с входными полевыми транзисторами, широко применяются в составе микросхем, выпускаемых как отечественными, так и зарубежными фирмами (СА3078, LM13600, LM13700, NE5517, AU5517) [9-12]. В них токовые зеркала обеспечивают высокую стабильность статического режима выходных транзисторов промежуточного каскада (ПК) ОУ, обеспечивающего основное усиление, и фактически преобразуют изменения выходных токов входного ДК в соответствующие приращения выходного тока ПК. Однако в схемах ОУ с данной архитектурой общий коэффициент усиления по напряжению (Kу) получается небольшим. Это связано с тем, что входное сопротивление классических токовых зеркал, на котором выделяются выходные напряжения входного ДК, не велико (десятки Ом) и, как следствие, входной каскад работает только в режиме преобразователя «напряжение-ток» и имеет малый коэффициент усиления по напряжению (KДК<1).

Ближайшим прототипом заявляемого устройства является операционный усилитель по патенту US 3.921.090, fig. 1. Кроме этого, данная архитектура ОУ приведена в других патентах [1-8] и справочниках [9-12].

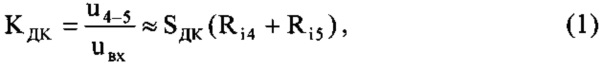

ОУ-прототип содержит (фиг. 1) входной дифференциальный каскад 1, согласованный по общей эмиттерной цепи 2 с первой 3 шиной источника питания, первый 4 и второй 5 противофазные токовые выходы входного дифференциального каскада 1, первый 6 выходной транзистор, коллектор которого связан со входом токового зеркала 7, согласованного с первой 3 шиной источника питания, второй 8 выходной транзистор, коллектор которого подключен к выходу токового зеркала 7 и токовому выходу устройства 9, первый 10 вспомогательный транзистор, коллектор которого подключен к первому 4 токовому выходу входного дифференциального каскада 1, эмиттер соединен со второй 11 шиной источника питания, а база связана с базой второго 12 вспомогательного транзистора, эмиттер которого соединен со второй 11 шиной источника питания, третий 13 вспомогательный транзистор, коллектор которого подключен ко второму 5 токовому выходу входного дифференциального каскада 1, эмиттер соединен со второй 11 шиной источника питания, а база связана с базой четвертого 14 вспомогательного транзистора, эмиттер которого соединен со второй 11 шиной источника питания.

Существенный недостаток известного ОУ состоит в том, что в нем невозможно получить повышенный коэффициент усиления по напряжению, т.к. его входной каскад не дает усиления по напряжению.

Основная задача предлагаемого изобретения состоит в повышении коэффициента усиления по напряжению (Ку) двухкаскадного разомкнутого ОУ при сохранении высокой температурной и радиационной стабильности напряжения смещения нуля.

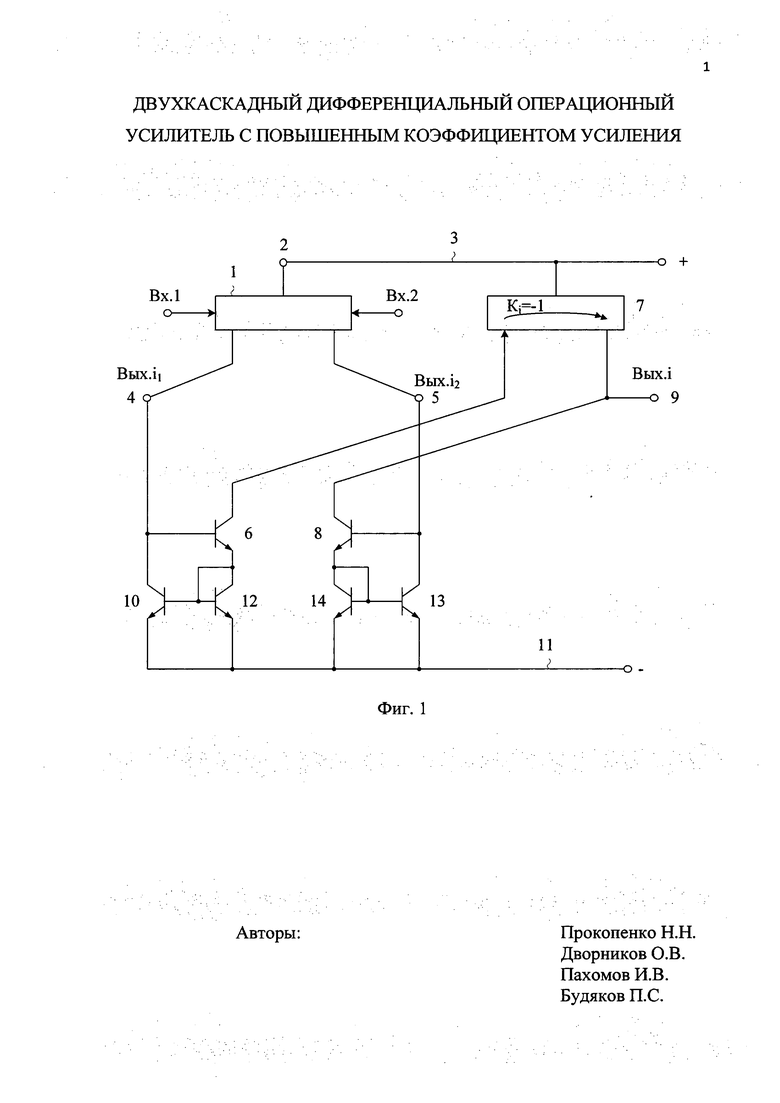

Поставленная задача достигается тем, что в дифференциальном операционном усилителе (фиг. 1), содержащем входной дифференциальный каскад 1, согласованный по общей эмиттерной цепи 2 с первой 3 шиной источника питания, первый 4 и второй 5 противофазные токовые выходы входного дифференциального каскада 1, первый 6 выходной транзистор, коллектор которого связан со входом токового зеркала 7, согласованного с первой 3 шиной источника питания, второй 8 выходной транзистор, коллектор которого подключен к выходу токового зеркала 7 и токовому выходу устройства 9, первый 10 вспомогательный транзистор, коллектор которого подключен к первому 4 токовому выходу входного дифференциального каскада 1, эмиттер соединен со второй 11 шиной источника питания, а база связана с базой второго 12 вспомогательного транзистора, эмиттер которого соединен со второй 11 шиной источника питания, третий 13 вспомогательный транзистор, коллектор которого подключен ко второму 5 токовому выходу входного дифференциального каскада 1, эмиттер соединен со второй 11 шиной источника питания, а база связана с базой четвертого 14 вспомогательного транзистора, эмиттер которого соединен со второй 11 шиной источника питания, предусмотрены новые элементы и связи - первый 4 токовый выход входного дифференциального каскада 1 связан с базой первого 10 вспомогательного, а также базами первого 6 выходного и второго 12 вспомогательного транзисторов через первый 15 дополнительный повторитель напряжения, второй 5 токовый выход входного дифференциального каскада 1 связан с базой третьего 13 вспомогательного, а также базами второго 8 выходного и четвертого 14 вспомогательного транзисторов через второй 16 дополнительный повторитель напряжения, коллектор четвертого 14 вспомогательного транзистора соединен с первым 4 токовым выходом входного дифференциального каскада 1, коллектор второго 12 вспомогательного транзистора подключен ко второму 5 токовому выходу входного дифференциального каскада 1, причем эмиттеры первого 6 и второго 8 выходных транзисторов соединены со второй 11 шиной источника питания.

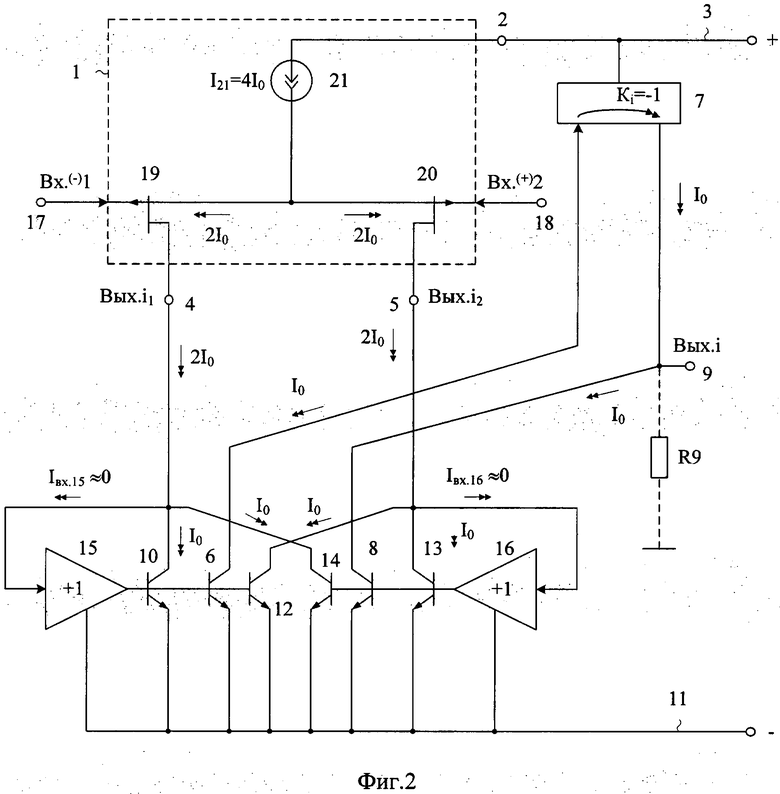

На фиг. 1 показана схема ОУ-прототипа для случая, когда токовые зеркала Вильсона, являющиеся нагрузкой входного ДК1, реализованы на n-p-n-транзисторах 6, 10, 12 и 8, 13, 14, а на чертеже фиг. 2 - схема заявляемого устройства в соответствии с формулой изобретения.

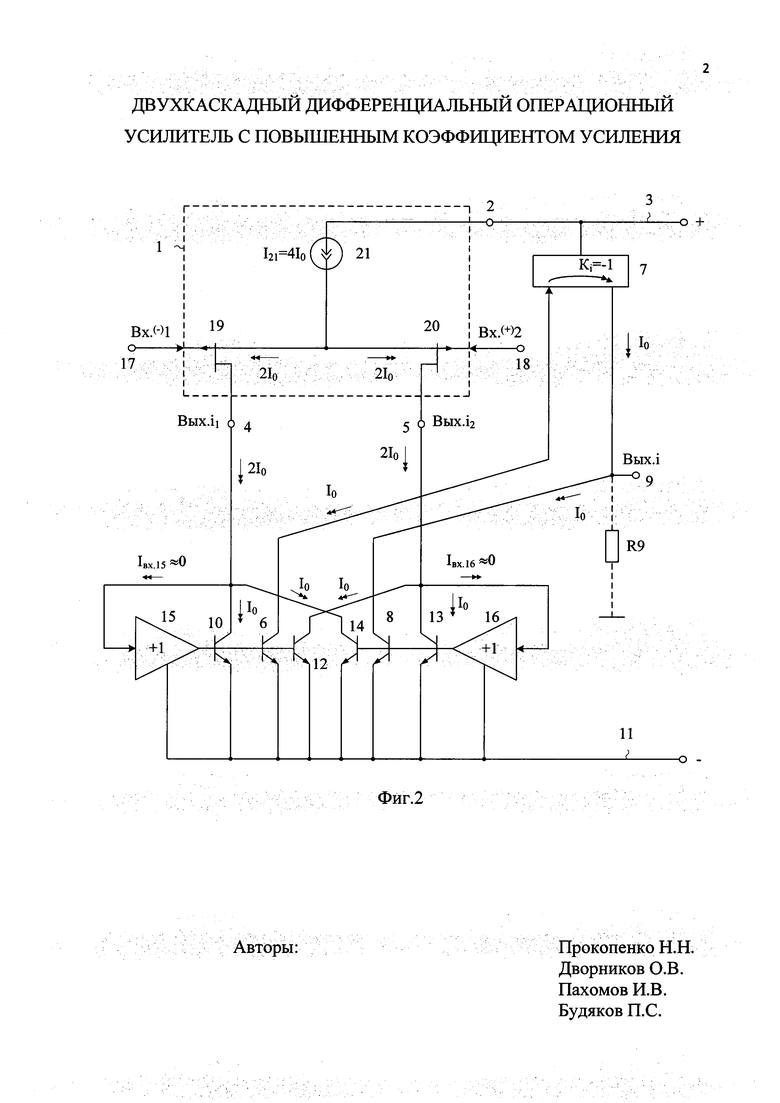

На фиг. 3 приведена схема фиг.2 с конкретным выполнением первого 15 и второго 16 дополнительных повторителей напряжения.

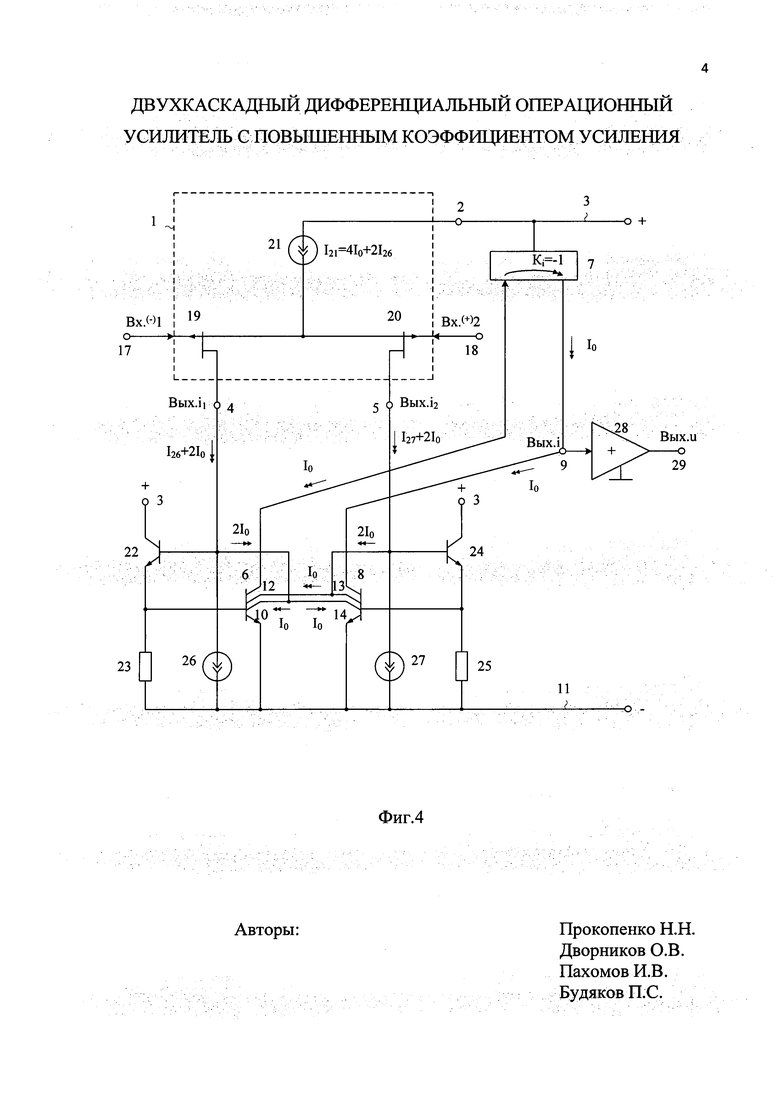

В схеме фиг. 4 первый 6 выходной транзистор, первый 10 и второй 12 вспомогательные транзисторы, второй 8 выходной транзистор, третий 13 и четвертый 14 вспомогательные транзисторы выполнены в виде активных элементов с несколькими коллекторами и объединены в единую интегральную структуру. Для расширения вариантов установления статического режима транзисторов здесь могут использоваться вспомогательные источники опорного тока 26 и 27. Кроме этого, в данной схеме предусмотрен классический буферный усилитель 28, обеспечивающий низкоомный выход устройства 29.

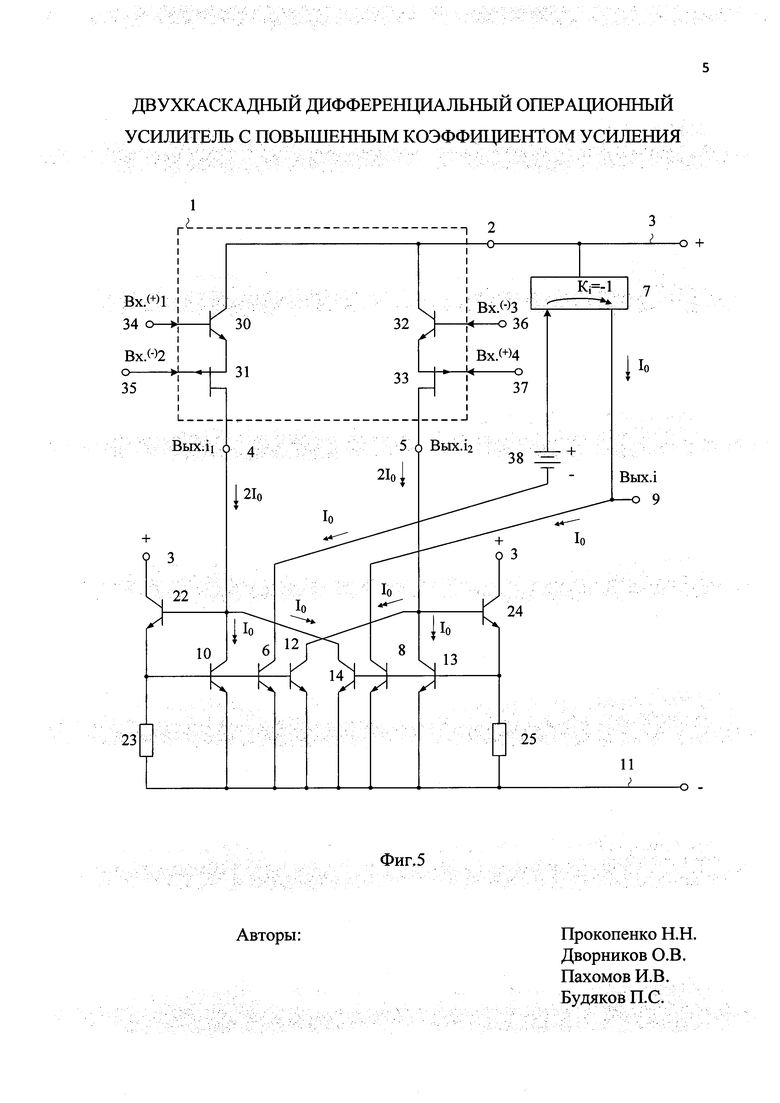

В схеме фиг. 5 входной дифференциальный каскад 1 имеет 4 входа, что позволяет реализовать на базе данной структуры так называемый мультидифференциальный операционный усилитель, имеющий ряд неоспоримых преимуществ в сравнении с классическими ОУ [13].

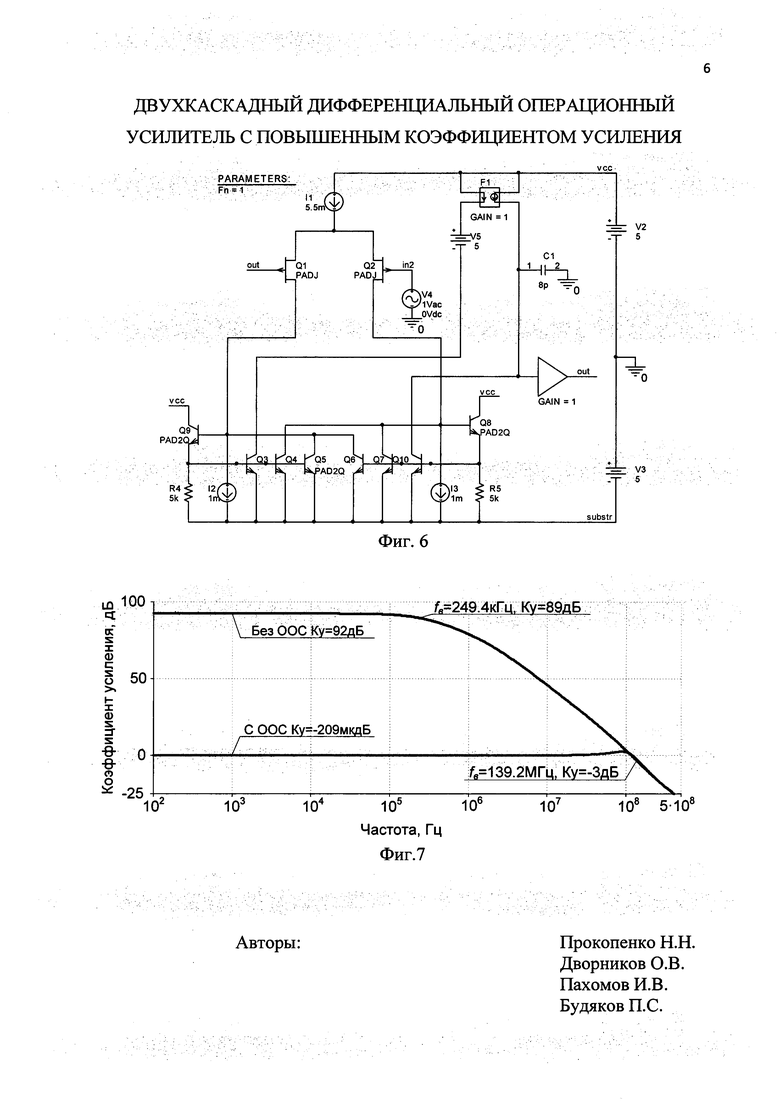

На фиг. 6 приведена схема ОУ фиг. 4 в среде PSpice на моделях интегральных транзисторов АБМК_1_4 ОАО «Интеграл» (г. Минск).

На фиг. 7 показана амплитудно-частотная характеристика коэффициента усиления по напряжению ОУ фиг. 6 без отрицательной обратной связи (верхний график) и с отрицательной обратной связью (нижний график).

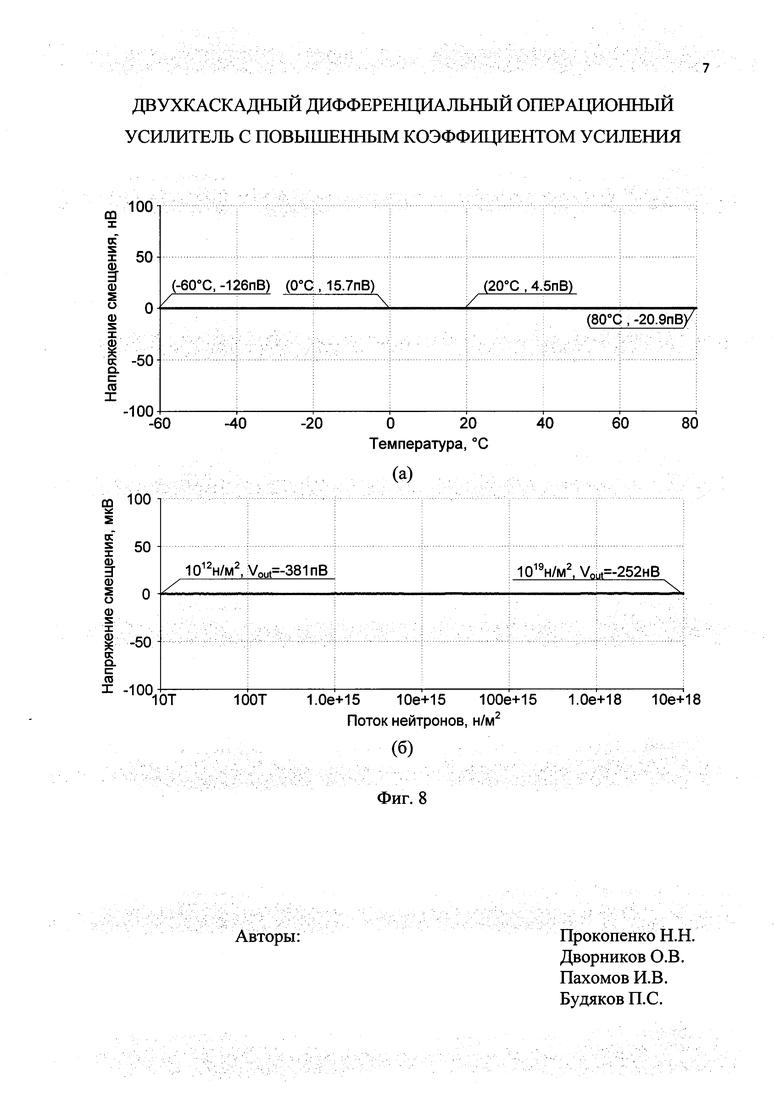

На фиг. 8 приведена зависимость систематической составляющей напряжения смещения нуля (Uсм) ОУ фиг. 6 от температуры в диапазоне минус 60÷+80°С (а) и потока нейтронов (б) для случая, когда транзисторы ОУ не имеют разброса параметров, а токовое зеркало 7 и буферный усилитель 28 идеальны. Это позволяет оценить предельные возможности архитектуры предлагаемого устройства, к которым можно стремиться.

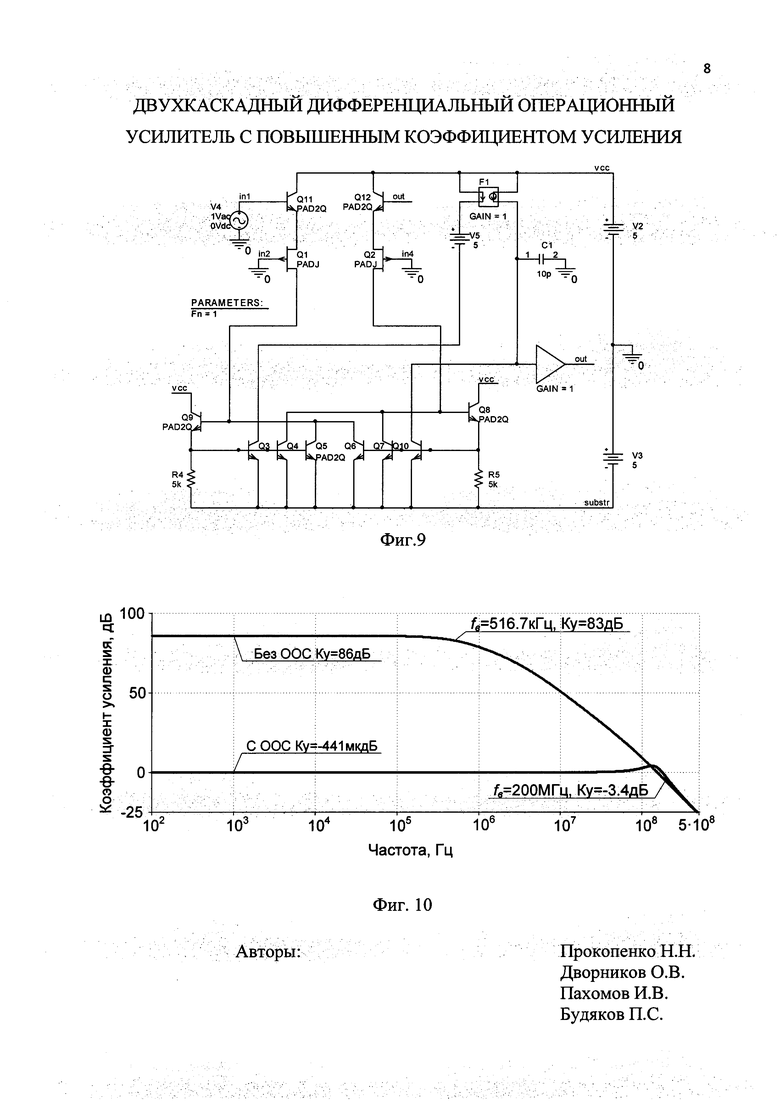

На фиг. 9 приведена схема ОУ фиг. 5 в среде PSpice на моделях интегральных транзисторов АБМК_1_4 ОАО «Интеграл» (г. Минск).

На фиг. 10 показана амплитудно-частотная характеристика коэффициента усиления по напряжению ОУ фиг. 9 без отрицательной обратной связи и со 100% отрицательной обратной связью.

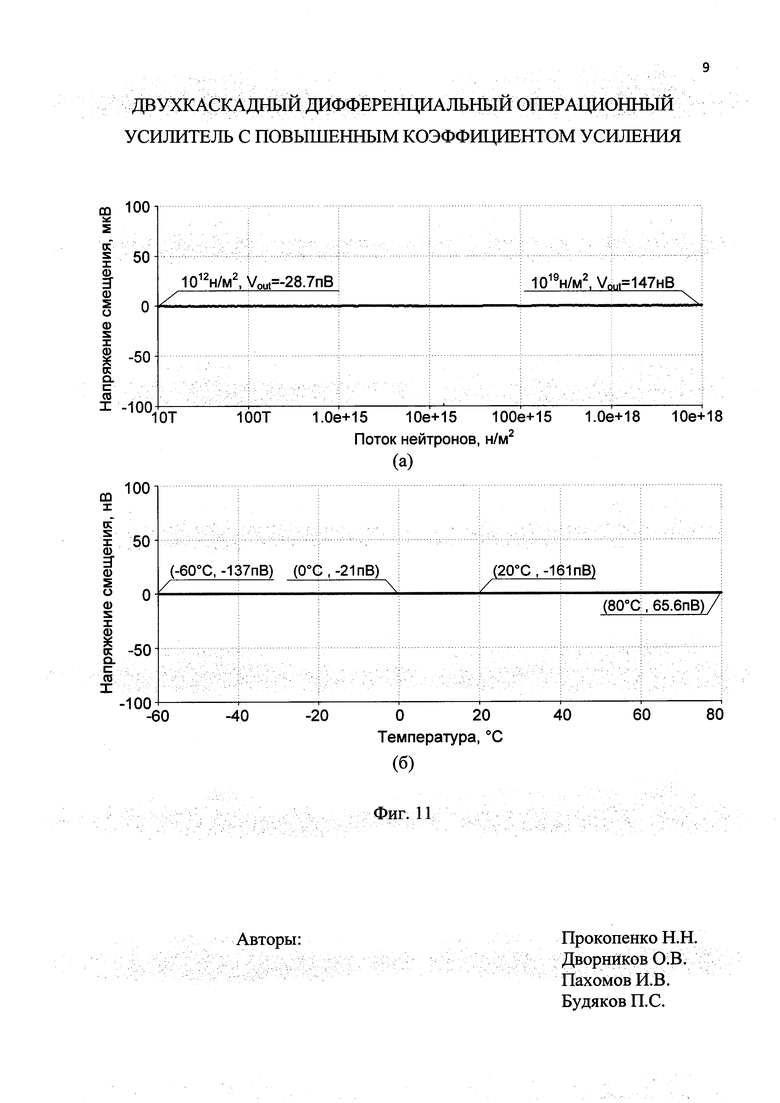

На фиг. 11 приведена зависимость систематической составляющей напряжения смещения нуля (Uсм) схемы фиг.9 от температуры (а) и потока нейтронов (б) без учета разброса параметров элементов, а также идеальном токовом зеркале 7 и буферном усилителе 28.

Двухкаскадный дифференциальный операционный усилитель с повышенным коэффициентом усиления (фиг. 2) содержит входной дифференциальный каскад 1, согласованный по общей эмиттерной цепи 2 с первой 3 шиной источника питания, первый 4 и второй 5 противофазные токовые выходы входного дифференциального каскада 1, первый 6 выходной транзистор, коллектор которого связан со входом токового зеркала 7, согласованного с первой 3 шиной источника питания, второй 8 выходной транзистор, коллектор которого подключен к выходу токового зеркала 7 и токовому выходу устройства 9, первый 10 вспомогательный транзистор, коллектор которого подключен к первому 4 токовому выходу входного дифференциального каскада 1, эмиттер соединен со второй 11 шиной источника питания, а база связана с базой второго 12 вспомогательного транзистора, эмиттер которого соединен со второй 11 шиной источника питания, третий 13 вспомогательный транзистор, коллектор которого подключен ко второму 5 токовому выходу входного дифференциального каскада 1, эмиттер соединен со второй 11 шиной источника питания, а база связана с базой четвертого 14 вспомогательного транзистора, эмиттер которого соединен со второй 11 шиной источника питания. В схему введены: первый 4 токовый выход входного дифференциального каскада 1 связан с базой первого 10 вспомогательного, а также базами первого 6 выходного и второго 12 вспомогательного транзисторов через первый 15 дополнительный повторитель напряжения, второй 5 токовый выход входного дифференциального каскада 1 связан с базой третьего 13 вспомогательного, а также базами второго 8 выходного и четвертого 14 вспомогательного транзисторов через второй 16 дополнительный повторитель напряжения, коллектор четвертого 14 вспомогательного транзистора соединен с первым 4 токовым выходом входного дифференциального каскада 1, коллектор второго 12 вспомогательного транзистора подключен ко второму 5 токовому выходу входного дифференциального каскада 1, причем эмиттеры первого 6 и второго 8 выходных транзисторов соединены со второй 11 шиной источника питания.

Кроме этого, в схеме фиг. 2 входной дифференциальный каскад 1 имеет противофазные входы 17 и 18, причем его схема включает входные полевые транзисторы 19, 20, статический режим которых устанавливается источником опорного тока 21.

В схеме фиг. 3 первый 15 и второй 16 дополнительные повторители напряжения выполнены соответственно на транзисторе 22 и резисторе 23, а также транзисторе 24 и резисторе 25.

На фиг. 4, который соответствует фиг. 3, используются вспомогательные источники опорного тока 26 и 27, а также выходной буферный усилитель 28, вход которого соединен с токовым выходом устройства 9, а выход 29 обеспечивает низкоомный потенциальный выход устройства.

В схеме фиг. 5, которая соответствует схеме фиг. 2, входной дифференциальный каскад 1 реализован на дополнительных входных транзисторах 30, 31, 32, 33, причем база дополнительного транзистора 30 соединена с первым неинвертирующим входом 34 ОУ, затвор дополнительного транзистора 31 подключен к инвертирующему входу 35 ОУ, база транзистора 32 соединена с инвертирующим входом 36 ОУ, а затвор транзистора 33 связан с четвертым неинвертирующим входом устройства.

Для уменьшения влияния напряжения Эрли первого 6 и второго 8 выходных транзисторов на напряжение смещения нуля ОУ в схеме фиг. 5 предусмотрена цепь смещения 38, реализуемая в виде источника опорного напряжения, вспомогательного резистора и т.п.

Рассмотрим работу ОУ фиг. 2.

Статический режим по току транзисторов ОУ фиг. 2 устанавливается источником опорного тока 21, входящим в структуру входного дифференциального каскада 1. При этом токи коллекторов транзисторов схемы (Iкi), токи первого 4 и второго 5 выходов ДК принимают значения: I21=4I0, I4=2I0, Iк10=Iк14=I0, I5=2I0, Iк12=I0, Iк13=I0, Iк6=I0, Iк8=I0, где I4=I5 - статические токи первого 4 и второго 5 выходов входного дифференциального каскада 1.

Если принять I20=4I0, то коллекторные токи всех транзисторов схемы будут равны некоторому опорному току I0, который выбирается разработчиком, например I0=1 мА.

Таким образом, в заявляемой схеме, также как и в ОУ-прототипе, обеспечивается высокая стабильность статического режима транзисторов промежуточного каскада (первый 6 и второй 8 выходные транзисторы), которая определяется единственным в схеме ОУ источником опорного тока 21.

За счет применения в схеме фиг. 2 первого 15 и второго 16 дополнительных повторителей напряжения и цепей взаимной компенсации эквивалентных сопротивлений (Ri4, Ri5) в цепи токовых выходов 4 и 5 входного ДК, которая обеспечивается четвертым 14 и вторым 12 вспомогательными транзисторами, эквивалентные сопротивления в цепи токовых выходов 4 (Ri4) и 5 (Ri5) существенно возрастают. Это приводит к существенному увеличению коэффициентов усиления по напряжению входного дифференциального каскада 1

где u4-5 - напряжение между первым 4 и вторым 5 токовыми выходами;

uвх - входное напряжение ОУ (напряжение между узлами 17, 18);

SДК - крутизна преобразования входного напряжения ДК (uвх) в приращения выходных токов первого 4 и второго 5 токовых выходов ДК в режиме их короткого замыкания.

В ОУ-прототипе этот коэффициент усиления (KДК) не превышает единицы, т.к. здесь Ri4≈Ri5=25÷50 Ом, а крутизна SДК в схемах с полевыми транзисторами всегда мала.

Результаты компьютерного моделирования (фиг. 7, фиг. 10) показывают, что предлагаемая схема ОУ имеет усиление по напряжению порядка 100 дБ (100000 раз) без введения каких-либо дополнительных каскадов усиления. Это повышает общее усиление разомкнутого ОУ.

При 100% отрицательной обратной связи на вход 36 и введении входного сигнала на вход 35 схемы фиг. 5 ОУ фиг. 5 является инвертирующим повторителем входного напряжения с Kу≈-1. Следует заметить, что на базе известного ОУ-прототипа такой режим без резисторов отрицательной обратной связи не реализуется [13].

Предлагаемые схемотехнические решения ОУ имеют малые значения систематической составляющей напряжения смещения нуля (Uсм) при температурных и радиационных воздействиях (фиг. 8, фиг. 9). Это свидетельствует о высокой стабильности статического режима транзисторов схемы ОУ.

Таким образом, предлагаемое двухкаскадное устройство имеет существенные преимущества в сравнении с известными, обеспечивает разомкнутое усиление по напряжению порядка Kу≈100000 и может найти широкое применение в системах преобразования радиотехнических сигналов.

ИСТОЧНИКИ ИНФОРМАЦИИ

1. Патент US 5.371.476, fig. 1.

2. Патент US 4.348.602, fig. 2.

3. Патент US 6.657.465.

4. Патент US 7.786.799, fig. 3.

5. Патент Японии JP 61-140210, fig. 1.

6. Патент US 7.411.451, fig. 2.

7. Патент US 4.607.232.

8. Патент US 5.936.468.

9. Справочник: операционные усилители и компараторы (Авербух В.Д. и др.). - М.: Изд-во «Додэка-ХХ1», 2001, С. 106 (микросхема СА3078).

10. Микросхема LM13600

http://www.komponenten.es.aau.dk/fileadmin/komponenten/Data_Sheet/Linear/LM13600.pdf

11. Микросхема LM13700 http://pdf1.alldatasheet.com/datasheet-pdf/view/549473/TI1/LM13700MX.html

12. Микросхема NF5517 http://pdf1.alldatasheet.com/datasheet-pdf/view/175236/ONSEMI/NE5517.html

13. Основные свойства, параметры и базовые схемы включения мультидифференциальных операционных усилителей с высокоимпедансным узлом / Н.Н. Прокопенко, О.В. Дворников, П.С. Будяков // Электронная техника. Серия 2. Полупроводниковые приборы. Выпуск 2 (233), Москва, ОАО «Пульсар», 2014 г. С. 53-64.

| название | год | авторы | номер документа |

|---|---|---|---|

| КАСКОДНЫЙ ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ С ПОВЫШЕННОЙ СТАБИЛЬНОСТЬЮ НУЛЕВОГО УРОВНЯ | 2010 |

|

RU2419187C1 |

| КАСКОДНЫЙ ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ | 2009 |

|

RU2416145C1 |

| ДИФФЕРЕНЦИАЛЬНЫЙ ОПЕРАЦИОННЫЙ УСИЛИТЕЛЬ С МАЛЫМ НАПРЯЖЕНИЕМ ПИТАНИЯ | 2015 |

|

RU2613842C1 |

| ПРЕЦИЗИОННЫЙ ОПЕРАЦИОННЫЙ УСИЛИТЕЛЬ | 2011 |

|

RU2449466C1 |

| ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ С МАЛЫМ НАПРЯЖЕНИЕМ СМЕЩЕНИЯ НУЛЯ | 2009 |

|

RU2401507C1 |

| ОПЕРАЦИОННЫЙ УСИЛИТЕЛЬ С НИЗКООМНОЙ НАГРУЗКОЙ | 2011 |

|

RU2444114C1 |

| ДИФФЕРЕНЦИАЛЬНЫЙ ОПЕРАЦИОННЫЙ УСИЛИТЕЛЬ | 2009 |

|

RU2412538C1 |

| ДИФФЕРЕНЦИАЛЬНЫЙ ОПЕРАЦИОННЫЙ УСИЛИТЕЛЬ | 2015 |

|

RU2616573C1 |

| ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ С ПОВЫШЕННЫМ ОСЛАБЛЕНИЕМ ВХОДНОГО СИНФАЗНОГО СИГНАЛА | 2005 |

|

RU2293433C1 |

| ДИФФЕРЕНЦИАЛЬНЫЙ ОПЕРАЦИОННЫЙ УСИЛИТЕЛЬ С МАЛЫМ НАПРЯЖЕНИЕМ СМЕЩЕНИЯ НУЛЯ | 2010 |

|

RU2421884C1 |

Изобретение относится к области радиоэлектроники и может быть использовано в качестве прецизионного устройства усиления широкополосных сигналов. Технический результат: повышение коэффициента усиления по напряжению (Ку) при сохранении высокой температурной и радиационной стабильности напряжения смещения нуля. Двухкаскадный дифференциальный операционный усилитель с повышенным коэффициентом усиления содержит входной дифференциальный каскад, первый выходной транзистор, коллектор которого связан со входом токового зеркала, источник питания, второй выходной транзистор, первый вспомогательный транзистор, второй вспомогательный транзистор, третий вспомогательный транзистор, первый дополнительный повторитель напряжения, четвертый вспомогательный транзистор и второй дополнительный повторитель напряжения. 11 ил.

Двухкаскадный дифференциальный операционный усилитель с повышенным коэффициентом усиления, содержащий входной дифференциальный каскад, согласованный по общей эмиттерной цепи с первой шиной источника питания, первый и второй противофазные токовые выходы входного дифференциального каскада, первый выходной транзистор, коллектор которого связан со входом токового зеркала, согласованного с первой шиной источника питания, второй выходной транзистор, коллектор которого подключен к выходу токового зеркала и токовому выходу устройства, первый вспомогательный транзистор, коллектор которого подключен к первому токовому выходу входного дифференциального каскада, эмиттер соединен со второй шиной источника питания, а база связана с базой второго вспомогательного транзистора, эмиттер которого соединен со второй шиной источника питания, третий вспомогательный транзистор, коллектор которого подключен ко второму токовому выходу входного дифференциального каскада, эмиттер соединен со второй шиной источника питания, а база связана с базой четвертого вспомогательного транзистора, эмиттер которого соединен со второй шиной источника питания, отличающийся тем, что первый токовый выход входного дифференциального каскада связан с базой первого вспомогательного транзистора, а также базами первого выходного и второго вспомогательного транзисторов через первый дополнительный повторитель напряжения, второй токовый выход входного дифференциального каскада связан с базой третьего вспомогательного транзистора, а также с базами второго выходного и четвертого вспомогательного транзисторов через второй дополнительный повторитель напряжения, коллектор четвертого вспомогательного транзистора соединен с первым токовым выходом входного дифференциального каскада, коллектор второго вспомогательного транзистора подключен ко второму токовому выходу входного дифференциального каскада, причем эмиттеры первого и второго выходных транзисторов соединены со второй шиной источника питания.

| МУЛЬТИДИФФЕРЕНЦИАЛЬНЫЙ ОПЕРАЦИОННЫЙ УСИЛИТЕЛЬ | 2013 |

|

RU2523124C1 |

| ДИФФЕРЕНЦИАЛЬНЫЙ ОПЕРАЦИОННЫЙ УСИЛИТЕЛЬ | 2009 |

|

RU2416155C1 |

| ДИФФЕРЕНЦИАЛЬНЫЙ ОПЕРАЦИОННЫЙ УСИЛИТЕЛЬ | 2009 |

|

RU2416152C1 |

| US 5432476 A, 11.07.1995. | |||

Авторы

Даты

2017-06-01—Публикация

2015-12-17—Подача