Изобретение относится к устройствам обработки цифровых данных с помощью электрических устройств, в частности к средствам для подвода и регулирования питания, и предназначено для применения в качестве функционального блока в микросхемах сверхбольшой степени интеграции, а также в качестве самостоятельного устройства в интегральном исполнении, предназначенного для решения различного рода вычислительных задач, например, обработки сигналов, в составе серверов и рабочих станций, а также аппаратуры с автономным питанием и других устройств, критичных к энергопотреблению.

В настоящее время при разработке автономных цифровых устройств на первый план выходит фактор энергетической эффективности вычислений. При этом улучшение проектных норм недостаточно для удовлетворения противоречивым требованиям высокого быстродействия при низком энергопотреблении. Несмотря на то что используемая в настоящее время синхронная методология проектирования обладает рядом важных достоинств, одним из которых является структурированный детерминистический подход к управлению множеством событий, происходящих в цифровой схеме, она имеет ряд недостатков, связанных с особенностями построения схемотехники цепей тактовых сигналов, в том числе наличие помех по цепям питания, возникающих вследствие того, что все тактовые сигналы совершают переходы в очень короткий промежуток времени; зависимость скорости работы цифровой схемы от задержки самого медленного участка для наихудших условий функционирования, таких как низкое напряжение питания, высокая температура, наихудшие параметры технологического процесса изготовления микросхемы.

Одним из способов разрешения этих недостатков является использование самосинхронного подхода [1] с полным отказом от использования тактовых сигналов. При таком построении схем скорость работы схемы определяется только длительностью протекания переходных процессов; не требуются дополнительные ресурсы для распространения тактовых сигналов. Самосинхронный подход к построению схем позволяет также снизить потребляемую мощность, увеличить надежность и существенно улучшить электромагнитную совместимость интегральных схем.

Мощность, потребляемая самосинхронным устройством обработки информации, определяется напряжением питания и скоростью поступления данных [1]. В зависимости от требований к быстродействию возможно снижение питающего напряжения самосинхронного вычислительного ядра вплоть до минимального уровня, обеспечивающего переключательную способность транзисторов. Такой подход позволяет существенно снизить энергопотребление устройства, не ограничивая его быстродействия.

Вследствие того что все блоки в самосинхронной схеме связаны между собой, то устанавливается средний темп обработки данных, который зависит от их содержимого. Элементы схемы, обладающие технологическим запасом по быстродействию, полностью его не используют, так как завязаны в общую цепь с другими элементами, обрабатывающими данные и работающими на более низкой скорости. При снижении питающего напряжения элементов схемы, обладающих повышенным быстродействием, общий темп обработки данных не изменится, однако снизится энергопотребление за счет уменьшения токов утечки транзисторов.

Следовательно, в зависимости от требований к быстродействию возможно снижение питающего напряжения самосинхронного вычислительного ядра вплоть до минимального уровня, обеспечивающего переключательную способность транзисторов. Такой подход позволяет существенно снизить энергопотребление устройства, не ограничивая его быстродействия.

Известно устройство «Dynamic control of power consumption in self-timed circuits» (патент US 5737614 от 7.04.1998) [2] того же назначения, что и предлагаемое, но не имеющее с ним общих признаков и состоящее из датчика потребляемой мощности (Sensor), инвертора сигнала индикации низкого уровня потребляемой мощности и последовательно соединенных идентичных каскадов, каждый из которых состоит из последовательно соединенных управляющего элемента (Control element) и каскада конвейера обработки данных (Pipeline stage), элемента «2ИЛИ-НЕ», последовательно соединенных блока управления задержкой (Delay control) и выходного инвертора, причем выходы каскада конвейера обработки данных соединены с первым и вторым входами элемента «2ИЛИ-НЕ» соответственно, выход которого соединен со вторым входом блока управления включением задержки, первый и третий входы которого соединены с выходом датчика потребляемой мощности и выходом инвертора сигнала индикации низкого уровня потребляемой мощности соответственно.

Недостатками данного устройства являются: ограничение быстродействия конвейера обработки данных при регулировании потребляемой мощности; не производится снижения потребляемой мощности в статическом состоянии последнего; регулирование напряжения питания на фиксированную величину, что недостаточно эффективно.

Известно устройство «Data processing circuit with self-timed instruction execution and power regulation)) (патент US 6014749 от 11.01.2000) [3] того же назначения, что и состоящее из последовательно соединенных осциллятора (Oscillator) и счетчика временных интервалов (Time interval counter), блока формирования управляющих сигналов (Sequencing unit), регулятора напряжения (Voltage regulator) и блока обработки данных (Processing unit), причем первый выход счетчика временных интервалов соединен с первым входом регулятора напряжения, а второй выход - с первым входом блока формирования управляющих сигналов, первый выход которого соединен с первым входом блока обработки данных, а второй - со вторым входом регулятора напряжения, который соединен со вторым входом блока обработки данных, выход которого соединен со вторым входом блока формирования управляющих сигналов, причем блок формирования управляющих сигналов состоит из последовательно соединенных счетчика и элемента «И».

Недостатком данного устройства является наличие дополнительной площади, занимаемой на кристалле при реализации схемы управления питанием вследствие использования локального осциллятора, а также отсутствие снижения потребляемой мощности в режиме простоя.

По схожести выполняемой функции и большинства признаков данное устройство выбрано за прототип.

Сущностью изобретения является самосинхронное вычислительное устройство с адаптивным питанием ядра, принцип работы которого основан на оценке текущей скорости поступления данных на вход устройства с последующим изменением питающего напряжения.

Достигаемый технический результат заключается в существенном снижении энергопотребления самосинхронного вычислительного ядра и блока операций с плавающей запятой без ограничения их быстродействия путем динамического изменения напряжения питания в зависимости от скорости поступления входных данных.

Сопоставительный анализ с прототипом показывает, что предлагаемое устройство отличается тем, что к самосинхронному вычислительному ядру подсоединены контроллер прерываний, блок операций с плавающей запятой, самосинхронная шина, соединенная с контроллером прямого доступа к памяти и блоком управления внешней шиной, подсоединен блок управления питанием, соединенный с блоком операций с плавающей запятой и состоящий из последовательно соединенных: схемы коммутации, RC-фильтра и драйвера напряжения, причем интерфейс соединения самосинхронного вычислительного ядра с контроллером прерываний, блоком операций с плавающей запятой, самосинхронной шиной и блоком управления питанием, а также самосинхронной шины с контроллером прямого доступа к памяти и блоком управления внешней шиной является четырехфазным протоколом обмена данными между самосинхронными устройствами.

Изобретение поясняется следующим графическим материалом:

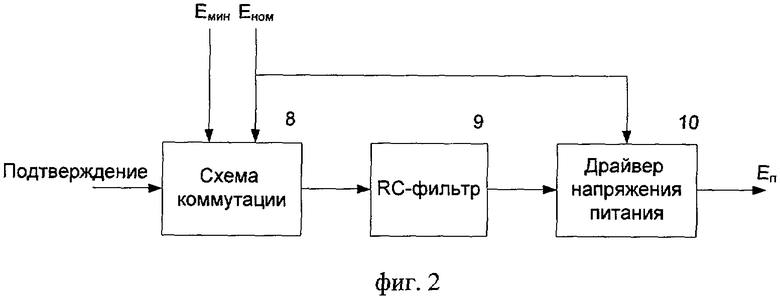

фиг.1 - структурная схема самосинхронного вычислительного устройства с адаптивным режимом питания ядра;

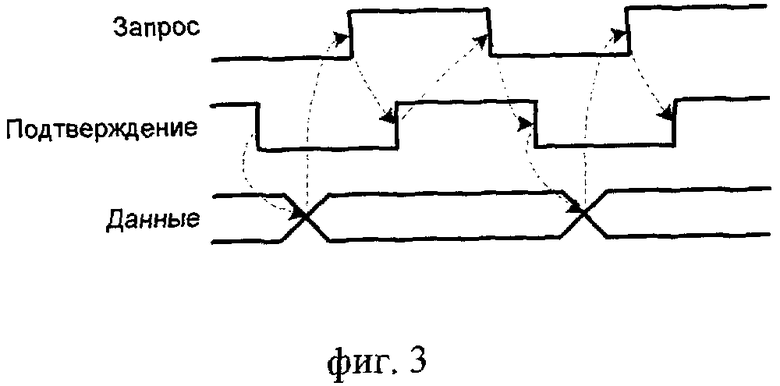

фиг.2 - структурная схема блока управления питанием;

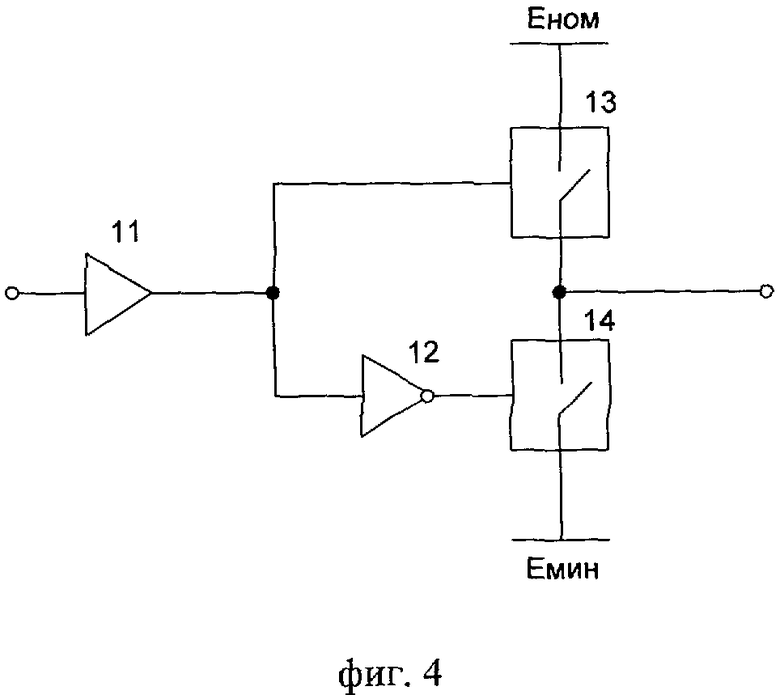

фиг.3 - временная диаграмма, поясняющая четырехфазный протокол обмена данными между самосинхронными устройствами;

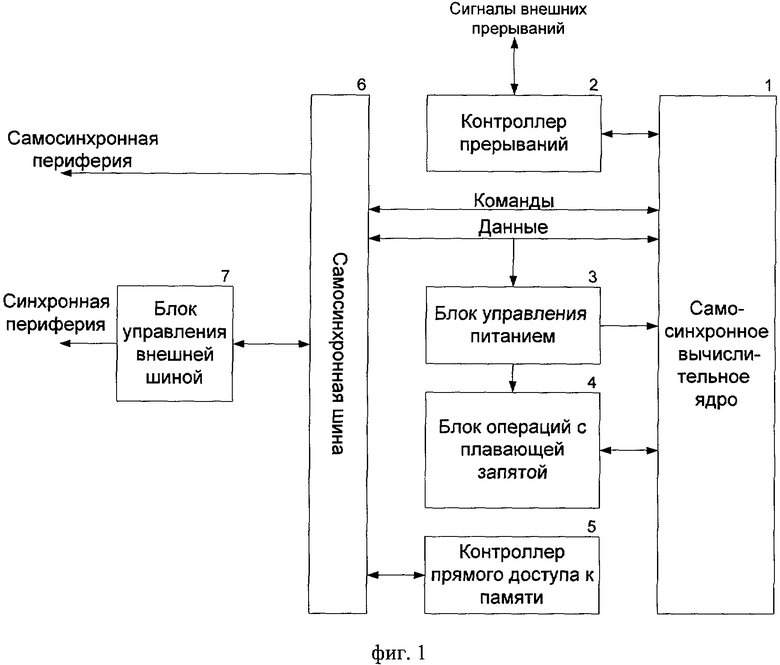

фиг.4 - вариант реализации схемы коммутации.

Самосинхронное вычислительное устройство с адаптивным режимом питания ядра (фиг.1) состоит из контроллера прерываний 2, блока операций с плавающей запятой 4, самосинхронной шины 6 и блока управления питанием 3, соединенных с самосинхронным вычислительным ядром 1; контроллера прямого доступа к памяти 5 и блока управления внешней шиной 7, соединенных с самосинхронной шиной 6, причем блок управления питанием 3 соединен с блоком операций с плавающей запятой 4 и состоит из последовательно соединенных схемы коммутации 8, RC-фильтра 9 и драйвера напряжения 10, а интерфейс соединения самосинхронного вычислительного ядра 1 с контроллером прерываний 2, блоком операций с плавающей запятой 4, самосинхронной шиной 6 и блоком управления питанием 3, а также самосинхронной шины 6 с контроллером прямого доступа к памяти 5 и блоком управления внешней шиной 7 является четырехфазным протоколом обмена данными между самосинхронными устройствами.

Самосинхронное вычислительное ядро 1 предназначено для выполнения вычислительных, логических и других операций по заранее заданной программе, а также организации обмена данными и командами между блоками, входящими в состав устройства.

Блок управления внешней шиной 7 предназначен для связи самосинхронного вычислительного устройства с синхронными периферийными устройствами. Его наличие позволяет самосинхронному вычислительному устройству работать как в составе синхронного, так и в составе самосинхронного окружения.

Самосинхронная шина 6 предназначена для обеспечения доступа самосинхронного вычислительного ядра 1 к адресному пространству внешней памяти.

Контроллер прямого доступа к памяти 5 предназначен для организации быстрого обмена самосинхронного вычислительного устройства с адаптивным питанием ядра с внешней памятью.

Контроллер прерываний 2 предназначен для обслуживания внешних прерываний.

Блок операций с плавающей запятой 4 предназначен для выполнения вычислительных операций с использованием соответствующей арифметики.

Блок управления питанием 3 предназначен для формирования питающего напряжения самосинхронного вычислительного ядра 1 в соответствии с темпом поступления обрабатываемых данных.

В четырехфазном протоколе обмена данными между самосинхронными устройствами предусмотрены следующие сигналы (фиг.4): «Запрос» - для индикации присутствия корректных установившихся данных на шине; «Подтверждение» - для индикации завершения цикла обработки данных; «Данные» - шина данных. Протокол подразумевает, что все управляющие сигналы возвращаются в исходное состояние перед началом каждого цикла обработки.

Логическая взаимосвязь между сигналами заключается в следующем: по заднему фронту сигнала «Подтверждение» источник выставляет на шину данные и устанавливает сигнал «Запрос» в лог.«1». Устройство-получатель по переднему фронту сигнала «Запрос» считывает данные с шины и производит их обработку, после чего получатель устанавливает сигнал подтверждение в лог.«1». Изменение уровня сигнала «Подтверждение» с лог.«0» на «1» индицирует отправителю о завершении обработки, после чего отправителем устанавливается сигнал «Запрос» в лог.«0». Получатель после изменения уровня сигнала «Запрос» с лог.«1» на «0» устанавливает сигнал «Подтверждение» в лог.«0», тем самым сигнализируя отправителю о готовности принять новые данные.

Блок управления питанием 3 функционирует следующим образом. Схема коммутации 8, в зависимости от сигнала «Подтверждение» на входе (фиг.2), формирует на выходе номинальное для заданной элементной базы напряжение питания ЕНОМ, если сигнал «Подтверждение» находится в состоянии лог.«1», и минимальное напряжение ЕМИН, обеспечивающее переключательные свойства элементов самосинхронного вычислительного ядра процессора 1 и блока операций с плавающей запятой 4, - в состоянии лог.«0». RC-фильтр 9 формирует выходное напряжение, пропорциональное отношению длительности импульсов «Подтверждение» на входе логики 8 к периоду их повторения. Выходное напряжение RC-фильтра 9 является опорным для драйвера питающего напряжения 10, производящего усиление питающего тока.

Таким образом, напряжение на выходе блока управления питанием 3 будет уменьшаться с уменьшением и увеличиваться - с увеличением частоты следования входных данных.

Схема коммутации 8 зависит от технологии изготовления микросхемы и может быть построена, как предложено ниже, и состоять из повторителя 11, соединенного с управляющим входом первого аналогового ключа 13 и инвертором 12, соединенным с управляющим входом второго аналогового ключа 14, причем вход первого аналогового ключа 13 является входом для подачи номинального ЕНОМ, вход второго аналогового ключа 14 - входом для подачи минимального ЕМИН напряжения питания ЕНОМ для заданной технологии, а выходы первого 13 и второго 14 аналоговых ключей соединены между собой и объединены с выходом схемы коммутации 8. Последняя работает следующим образом. При подаче на вход схемы лог.«1» на управляющем входе первого аналогового ключа 13 будет присутствовать сигнал лог.«1», а на выходе инвертора 12 и соответственно на управляющем входе второго аналогового ключа 14 - лог.«0». При этом первый (13) будет открыт, а второй аналоговый ключ 14 - закрыт и на выход будет подано номинальное напряжение питания ЕНОМ; при подаче на вход схемы лог.«0» на управляющем входе первого аналогового ключа 13 будет присутствовать сигнал лог.«0», а на выходе инвертора 12 и соответственно на управляющем входе второго аналогового ключа 14 - лог.«1». При этом первый будет закрыт, а второй аналоговый ключ 13 - закрыт, и на выход схемы будет подано минимальное напряжение питания ЕМИН для заданной технологии.

Параметры RC-фильтра 9 и регулировочная характеристика драйвера питающего напряжения 10 выбираются таким образом, чтобы при номинальной частоте работы самосинхронного микропроцессора напряжение на выходе блока управления питанием 3 составляло величину номинального напряжения питания, а снижение питания не приводило к увеличению времени выполнения команд свыше периода следования данных.

Драйвер напряжения 10 выполняет функцию усилителя питающего тока ядра и является стандартным аналоговым устройством.

В результате снижается энергопотребление самосинхронного вычислительного ядра и блока операций с плавающей запятой без ограничения их быстродействия в широком диапазоне скоростей поступления входных данных.

Источники информации

1. Jens Sparsø. Asynchronous Circuit Design Tutorial. Technical university of Denmark, 2006.

2. Патент US 5737614 от 7.04.1998 «Dynamic control of power consumption in self-timed circuits».

3. Патент US 6014749 от 11.01.2000 «Data processing circuit with self-timed instruction execution and power regulation».

| название | год | авторы | номер документа |

|---|---|---|---|

| САМОСИНХРОННОЕ УСТРОЙСТВО С АВТОМАТИЧЕСКИМ РЕГУЛИРОВАНИЕМ ПОТРЕБЛЯЕМОЙ МОЩНОСТИ | 2009 |

|

RU2409832C1 |

| УСТРОЙСТВО ОБМЕНА ДАННЫМИ МЕЖДУ ЧЕТЫРЕХФАЗНЫМ САМОСИНХРОННЫМ И СИНХРОННЫМ ПАРАЛЛЕЛЬНЫМ ИНТЕРФЕЙСОМ | 2009 |

|

RU2402802C1 |

| СПОСОБ, УСТРОЙСТВО И СИСТЕМА ДЛЯ ПРЕДВАРИТЕЛЬНОЙ РАСПРЕДЕЛЕННОЙ ОБРАБОТКИ СЕНСОРНЫХ ДАННЫХ И УПРАВЛЕНИЯ ОБЛАСТЯМИ ИЗОБРАЖЕНИЯ | 2013 |

|

RU2595760C2 |

| АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ С ПЛАВАЮЩЕЙ ЗАПЯТОЙ | 1991 |

|

RU2007024C1 |

| СПОСОБ ФОРМИРОВАНИЯ 4-КАНАЛЬНОЙ ОТКАЗОУСТОЙЧИВОЙ СИСТЕМЫ БОРТОВОГО КОМПЛЕКСА УПРАВЛЕНИЯ ПОВЫШЕННОЙ ЖИВУЧЕСТИ И ЭФФЕКТИВНОГО ЭНЕРГОПОТРЕБЛЕНИЯ И ЕГО РЕАЛИЗАЦИЯ ДЛЯ КОСМИЧЕСКИХ ПРИМЕНЕНИЙ | 2011 |

|

RU2449352C1 |

| УНИВЕРСАЛЬНО-РАСПРЕДЕЛЕННАЯ ГИБРИДНАЯ СИСТЕМА УПРАВЛЕНИЯ МАРКИРАТОРАМИ С ОБРАТНОЙ СВЯЗЬЮ | 2017 |

|

RU2657919C1 |

| УНИВЕРСАЛЬНО-РАСПРЕДЕЛЕННАЯ ГИБРИДНАЯ СИСТЕМА УПРАВЛЕНИЯ КОЛЛАБОРАТИВНЫМ МНОГОЦЕЛЕВЫМ РОБОТОМ С МАШИННЫМ ЗРЕНИЕМ | 2018 |

|

RU2710709C1 |

| СИСТЕМА И СПОСОБ РАБОТЫ РЕГУЛЯТОРА С ПОНИЖЕННЫМ ЭНЕРГОПОТРЕБЛЕНИЕМ | 2002 |

|

RU2292577C2 |

| Схема кардиомонитора CardioQVARK | 2015 |

|

RU2631643C2 |

| СПОСОБ УПРАВЛЕНИЯ ЧЕТЫРЕХКВАДРАНТНЫМ ПРЕОБРАЗОВАТЕЛЕМ С ВЫЧИСЛЕНИЕМ ФАЗ КОММУТАЦИИ И МИКРОПРОЦЕССОРНОЕ УСТРОЙСТВО ЕГО РЕАЛИЗУЮЩЕЕ | 2006 |

|

RU2327276C1 |

Изобретение относится к устройствам обработки цифровых данных с помощью электрических устройств и, в частности, к средствам регулирования питания. Достигаемый технический результат - снижение энергопотребления самосинхронного вычислительного ядра и блока операций с плавающей запятой без ограничения их быстродействия путем динамического изменения напряжения питания в зависимости от скорости поступления входных данных. Устройство состоит из самосинхронного вычислительного ядра, блока операций с плавающей запятой, контроллера прерываний, контроллера прямого доступа к памяти, блока управления внешней шиной, самосинхронной шины и блока управления питанием, состоящего из схемы коммутации, RC-фильтра и драйвера напряжения. 4 ил.

Самосинхронное вычислительное устройство с адаптивным питанием ядра, состоящее из контроллера прерываний, блока операций с плавающей запятой, самосинхронной шины и блока управления питанием, соединенных с самосинхронным вычислительным ядром, контроллера прямого доступа к памяти и блока управления внешней шиной, соединенных с самосинхронной шиной, причем блок управления питанием соединен с блоком операций с плавающей запятой, отличающееся тем, что блок управления питанием состоит из последовательно соединенных схемы коммутации, RC-фильтра и драйвера напряжения, а интерфейс соединения самосинхронного вычислительного ядра с контроллером прерываний, блоком операций с плавающей запятой, самосинхронной шиной и блоком управления питанием, а также самосинхронной шины с контроллером прямого доступа к памяти и блоком управления внешней шиной является четырехфазным протоколом обмена данными между самосинхронными устройствами, состоящим из логических сигналов: Запрос, Подтверждение, Данные, вход блока управления питанием соединен с сигналом Подтверждение четырехфазного протокола обмена данными между самосинхронными устройствами, схема коммутации имеет управляющий вход, являющийся входом блока управления питанием, первый и второй сигнальные входы, соответственно соединенные с источниками номинального и минимального напряжений питания для заданной технологии и выход, являющийся выходом блока управления питанием, причем схема коммутации работает по алгоритму: если на управляющем входе установлена логическая единица, выход является первым, а если логический нуль - вторым сигнальным входом.

| US 6014749, 11.01.2000 | |||

| СПОСОБ И СИСТЕМА ДЛЯ УПРАВЛЕНИЯ ЭНЕРГОПОТРЕБЛЕНИЕМ СЕТЕВОГО ИНТЕРФЕЙСНОГО МОДУЛЯ В БЕСПРОВОДНОМ ВЫЧИСЛИТЕЛЬНОМ УСТРОЙСТВЕ | 2003 |

|

RU2313123C2 |

| RU 96109859 A, 10.08.1998. | |||

Авторы

Даты

2011-06-20—Публикация

2009-06-15—Подача