Изобретение относится к устройствам обработки цифровых данных с помощью электрических устройств, в частности к средствам для подвода и регулирования питания, и может быть использовано в интегральных схемах большой и сверхбольшой степени интеграции (соответственно БИС и СБИС), включающих функциональные блоки, работающие по самосинхронному принципу [1], для автоматического управления энергопотреблением.

Принцип работы самосинхронных цифровых устройств предусматривает наличие двух основных режимов: функционирования и ожидания. В режиме функционирования самосинхронное устройство производит обработку поступающей цифровой информации, и мощность, потребляемая устройством, определяется напряжением питания и скоростью поступления данных; в режиме ожидания устройство находится в статическом состоянии потребления постоянной мощности.

Самосинхронные цифровые устройства часто используются в СБИС для построения конвейерных вычислителей, содержащих большое количество самосинхронных функциональных блоков. При этом часть из них определенный сегмент времени не задействована в вычислительном процессе. Снижение потребляемой мощности блоков, находящихся в режиме ожидания, позволяет получить существенный выигрыш в энергопотреблении всего устройства.

Существующие в настоящее время устройства автоматического контроля энергопотребления самосинхронных блоков обладают существенным недостатком, выражающимся в повышенном энергопотреблении, что вызвано отсутствием регулирования напряжения питания в режиме ожидания.

Известно устройство «Dynamic control of power consumption in self-timed circuits» (патент US 5737614 от 7.04.1998) [2] того же назначения, что и предлагаемое, но не имеющее с ним общих признаков и состоящее из датчика потребляемой мощности (Sensor), инвертора сигнала индикации низкого уровня потребляемой мощности и N последовательно соединенных идентичных каскадов, каждый из которых состоит из последовательно соединенных управляющего элемента (Control element) и каскада конвейера обработки данных (Pipeline stage), элемента «2ИЛИ-НЕ», последовательно соединенных блока управления задержкой (Delay control) и выходного инвертора, причем выходы каскада конвейера обработки данных соединены с первым и вторым входами элемента «2ИЛИ-НЕ» соответственно, выход которого соединен со вторым входом блока управления включением задержки, первый и третий входы которого соединены с выходом датчика потребляемой мощности и выходом инвертора сигнала индикации низкого уровня потребляемой мощности соответственно.

Недостатком данного устройства является низкая эффективность регулирования потребляемой мощности, обусловленная тем, что последнее производится посредством изменения скорости работы устройства, для чего использованы линии задержки фиксированной длины, активизируемые только при превышении регулируемой величиной некоторого порогового уровня. Другим недостатком является повышенное энергопотребление благодаря отсутствию регулирования напряжения питания в режиме ожидания.

Известно устройство «Data processing circuit with self-timed instruction execution and power regulation)) (патент US 6014749 от 11.01.2000) [3] того же назначения, что и состоящее из последовательно соединенных осциллятора (Oscillator) и счетчика временных интервалов (Time interval counter), блока формирования управляющих сигналов (Sequencing unit), регулятора напряжения (Voltage regulator) и блока обработки данных (Processing unit), причем первый выход счетчика временных интервалов соединен с первым входом регулятора напряжения, а второй выход - с первым входом блока формирования управляющих сигналов, первый выход которого соединен с первым входом блока обработки данных, а второй - со вторым входом регулятора напряжения, который соединен со вторым входом блока обработки данных, выход которого соединен со вторым входом блока формирования управляющих сигналов, причем блок формирования управляющих сигналов состоит из последовательно соединенных счетчика и элемента «И». По схожести выполняемой функции и большинства признаков данное устройство выбрано за прототип.

Недостатком данного устройства является отсутствие регулирования потребления мощности во время режима ожидания и ограничение быстродействия в режиме функционирования, обусловленное использованным в нем способом регулирования.

Сущностью изобретения является самосинхронное устройство с автоматическим регулированием потребляемой мощности, принцип работы которого основан на идентификации моментов ожидания при работе самосинхронного конвейерного вычислительного блока и последующего снижения питающего напряжения до минимального уровня, сохраняющего переключательную способность транзисторов, входящих в состав устройства.

Достигаемый технический результат заключается в существенном снижении энергопотребления самосинхронного конвейерного вычислительного блока путем снижения питающего напряжения до минимально возможного уровня в режиме ожидания и отсутствии ограничения быстродействия в режиме функционирования.

Сопоставительный анализ с прототипом показывает, что предлагаемое устройство отличается тем, что к входу блока управления напряжением питания и выходу самосинхронного конвейерного вычислительного блока, последовательно соединенных между собой, подсоединен блок формирования управляющих сигналов, состоящий из генератора прямоугольных импульсов, соединенного с первым входом первого элемента «И», выход которого подключен к декрементирующему входу двоичного реверсивного счетчика, ко входу установки которого подключен второй элемент «ИЛИ», а выход переноса соединен с первым входом элемента «3И», соединенного со входом установки второго RS-триггера, вход сброса которого соединен с выходом второго элемента «2И-ИЛИ», инвертирующий выход - со вторым входом первого элемента «И», а неинвертирующий выход - со вторым входом блока «И» второго элемента «2И-ИЛИ», со вторым входом второго элемента «И» и последовательно соединенными элементами «НЕ»: вторым, третьим и четвертым, выход которого соединен с первым входом второго элемента «И»; первого элемента «НЕ», выход которого соединен с вторым входом элемента «3И» и вторым входом блока «И» первого элемента «2И-ИЛИ», выход которого соединен со входом установки первого RS-триггера; первого элемента «ИЛИ», первый вход которого объединен со входом первого элемента «НЕ» и первым входом блока «И» второго элемента «2И-ИЛИ», второй вход соединен с выходом второго элемента «И», а выход соединен со входом сброса первого RS-триггера, неинвертирующий выход которого соединен с третьим входом элемента «3И»; второго элемента «ИЛИ», соединенного со входом установки двоичного реверсивного счетчика.

Следовательно, устройство удовлетворяет критерию «новизна».

Сравнение с другими техническими решениями показывает, что алгоритм энергосбережения предлагаемого устройства не ограничивает быстродействие самосинхронного конвейерного вычислительного блока в режиме функционирования и существенно снижается энергопотребление последнего в режиме ожидания.

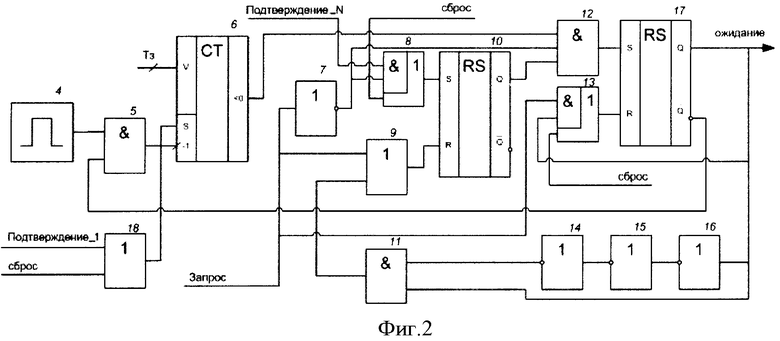

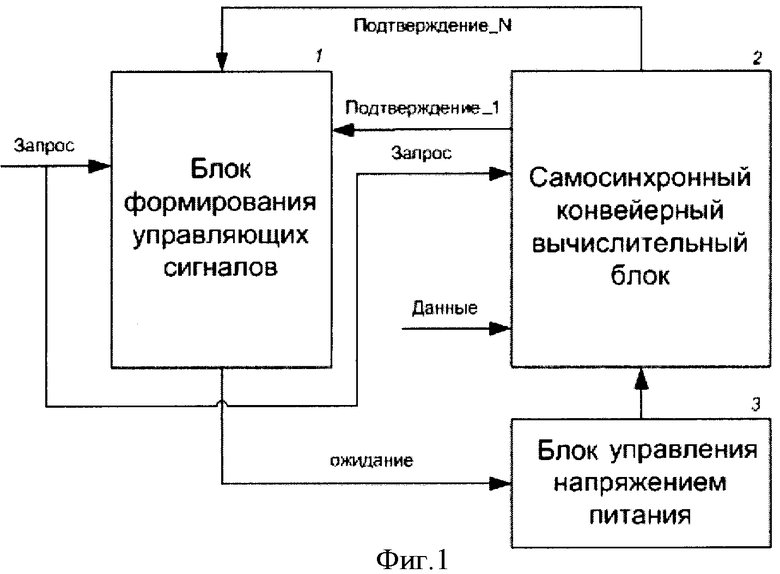

Изобретение поясняется следующими графическими материалами:

фиг.1 - структурная схема самосинхронного устройства с автоматическим управлением потреблением мощности;

фиг.2 - функциональная схема блока формирования управляющих сигналов.

Самосинхронное устройство с автоматическим регулированием потребляемой мощности (фиг.1) состоит из последовательно соединенных блока управления напряжением питания 3, самосинхронного конвейерного вычислительного блока 2, соединенного со входами Подтверждение_1 и Подтверждение_N блока формирования управляющих сигналов 1, выход Ожидание которого соединен со входом блока управления напряжением питания 3, а вход Запрос совмещен с одноименным входом самосинхронного конвейерного вычислительного блока 2 и одноименным входом устройства, причем блок формирования управляющих сигналов 1 состоит из генератора прямоугольных импульсов 4, соединенного с первым входом первого элемента «И» 5, выход которого подключен к декрементирующему входу двоичного реверсивного счетчика 6, ко входу установки которого подключен второй элемент «ИЛИ» 18, а выход переноса «<0» - соединен с первым входом элемента «3И» 12, соединенного со входом установки S второго RS-триггера 17, вход сброса R которого соединен с выходом второго элемента «2И-ИЛИ» 13, инвертирующий выход  соединен со вторым входом первого элемента «И» 5, а неинвертирующий выход Q является выходом Ожидание и соединен со вторым входом блока «И» второго элемента «2И-ИЛИ» 13, со вторым входом второго элемента «И» 11 и последовательно соединенными элементами «НЕ»: вторым 16, третьим 15 и четвертым 14, выход которого соединен с первым входом второго элемента «И» 11, а вход блока «ИЛИ» второго элемента «2И-ИЛИ» 13 совмещен со входом Сброс; первого элемента «НЕ» 7, вход которого совмещен со входом Запрос, а выход соединен со вторым входом элемента «3И» 12 и вторым входом блока «И» первого элемента «2И-ИЛИ» 8, первый вход блока «И» которого совмещен со входом Подтверждение_N, вход блока «ИЛИ» совмещен со входом Сброс, а выход соединен со входом установки S первого RS-триггера 10; первого элемента «ИЛИ» 9, первый вход которого объединен со входом первого элемента «НЕ» 7 и первым входом блока «И» второго элемента «2И-ИЛИ» 13, второй вход соединен с выходом второго элемента «И» 11, а выход соединен со входом сброса R первого RS-триггера 10, не-инвертирующий выход Q которого соединен с третьим входом элемента «3И» 12; второго элемента «ИЛИ» 18, первый и второй входы являются сигналами Подтверждение_1 и Сброс, соединенного со входом установки S двоичного реверсивного счетчика 6.

соединен со вторым входом первого элемента «И» 5, а неинвертирующий выход Q является выходом Ожидание и соединен со вторым входом блока «И» второго элемента «2И-ИЛИ» 13, со вторым входом второго элемента «И» 11 и последовательно соединенными элементами «НЕ»: вторым 16, третьим 15 и четвертым 14, выход которого соединен с первым входом второго элемента «И» 11, а вход блока «ИЛИ» второго элемента «2И-ИЛИ» 13 совмещен со входом Сброс; первого элемента «НЕ» 7, вход которого совмещен со входом Запрос, а выход соединен со вторым входом элемента «3И» 12 и вторым входом блока «И» первого элемента «2И-ИЛИ» 8, первый вход блока «И» которого совмещен со входом Подтверждение_N, вход блока «ИЛИ» совмещен со входом Сброс, а выход соединен со входом установки S первого RS-триггера 10; первого элемента «ИЛИ» 9, первый вход которого объединен со входом первого элемента «НЕ» 7 и первым входом блока «И» второго элемента «2И-ИЛИ» 13, второй вход соединен с выходом второго элемента «И» 11, а выход соединен со входом сброса R первого RS-триггера 10, не-инвертирующий выход Q которого соединен с третьим входом элемента «3И» 12; второго элемента «ИЛИ» 18, первый и второй входы являются сигналами Подтверждение_1 и Сброс, соединенного со входом установки S двоичного реверсивного счетчика 6.

В принцип работы самосинхронного устройства с автоматическим регулированием потребляемой мощности заложено определение моментов ожидания при работе самосинхронного конвейерного вычислительного блока и последующего снижения питающего напряжения до минимального уровня, при котором сохраняется переключательная способность транзисторов, входящих в состав логических элементов.

Устройство работает следующим образом.

На вход блока формирования управляющих сигналов 1 поступает сигнал со входа Запрос, адресованный первому каскаду самосинхронного конвейерного вычислительного блока 2, и сигналы со входов Подтверждение_1 и Подтверждение_N самосинхронного конвейерного вычислительного блока 2. Блок формирования управляющих сигналов 2 анализирует входные сигналы и формирует выходной сигнал на выходе Ожидание, который подается на вход блока управления напряжением питания 3. Сигнал на выходе Ожидание соответствует лог.«1», если блок формирования управляющих сигналов 1 идентифицировал простой в работе самосинхронного конвейерного вычислительного блока 3 и лог.«0» - в противном случае. При поступлении на вход блока управления напряжением питания 3 лог.«1» последний снижает напряжение питания самосинхронного конвейерного вычислительного блока 3 до минимально возможного уровня, при котором сохраняется переключательная способность транзисторов, входящих в его состав. При поступлении на вход блока управления напряжением питания 3 лог. «0» последний устанавливает номинальное напряжение питания для элементной базы самосинхронного конвейерного вычислительного блока 3. Номинальные напряжения питания определяются технологией изготовления самосинхронного устройства.

В качестве самосинхронного конвейерного вычислительного блока 2 могут быть, например, использованы устройства, подробно описанные в [1], стр.16-18.

Блок формирования управляющих сигналов 1 (фиг.2) выполняет функции определения режима работы самосинхронного конвейерного вычислительного блока 2 и генерации управляющего сигнала для регулирования напряжения питания последнего и работает следующим образом. По сигналу входа Подтверждение_1 происходит запуск реверсивного счетчика 6, в который предварительно записано значение, определяющее временной интервал, по прошествии которого при отсутствии работы самосинхронного конвейерного вычислительного блока 3 происходит установка сигнала выхода Ожидание и перевод устройства в режим пониженного энергопотребления. Реверсивный счетчик 6 производит подсчет сигналов генератора прямоугольных импульсов 4, которые стробируются сигналом с инверсного выхода второго RS-триггера 17, наличие лог.«1» на котором индицирует о том, что устройство не находится в режиме пониженного энергопотребления. По достижении нуля реверсивный счетчик 6 формирует выходной сигнал переноса «<0», который подается на первый вход элемента «3И» 12. По приходу сигнала со входа Подтверждение_1, характеризующего окончание цикла обработки данных самосинхронным конвейерным вычислительным блоком 2, и наличии сигнала лог.«1» на выходе первого элемента «НЕ» 7, характеризующего отсутствие начала нового цикла обработки данных, на выходе первого RS-триггера 10 устанавливается сигнал лог.«1», сигнализирующий об окончании текущего и отсутствии начала нового цикла обработки данных. На второй вход элемента «3И» в этот момент времени подается сигнал лог.«1», вследствие того что новый цикл обработки данных еще не начался, или вход Запрос соответствует лог.«0»; на первый и третий входы элемента «3И» 12 подаются сигналы лог.«1», в результате чего на выходе второго RS-триггера 17 формируется сигнал лог.«1», сигнализирующий о том, что устройство находится в режиме ожидания, который подается на второй вход второго элемента «2И-ИЛИ» 13, разрешая сброс триггера сигналом со входа Запрос. Одновременно на инверсном выходе второго RS-триггера 17 устанавливается лог.«0», устанавливающий на выходе первого элемента «2И» 5 лог.«0» для обеспечения пониженного энергопотребления во время простоя устройства. Сигнал лог.«1» с прямого выхода Q второго RS-триггера 17 подается на инвертирующую линию задержки, состоящую из элементов «НЕ»: второго 16, третьего 15, четвертого 14, и второй элемент «2И» 11, в результате чего на выходе первого элемента «ИЛИ» 9 формируется короткий импульс, сбрасывающий первый RS-триггер 10, запрещая, таким образом, установку второго RS-триггера 17 во время, когда устройство находится в режиме ожидания. Первый RS-триггер 10 также сбрасывается по сигналу со входа Запрос для предотвращения некорректной установки второго RS-триггера 17. Сигнал со входа Сброс сбрасывает второй RS-триггер 17 (когда устройство не находится в режиме ожидания), устанавливает сигнал на прямом выходе первого RS-триггера 10 в лог.«1», запускает реверсивный счетчик 13, по сигналу которого устройство будет переведено в режим ожидания, если за заданный промежуток времени на вход блока формирования управляющих сигналов 1 не будет подан сигнал со входа Запрос. В результате подачи сигнала на вход Подтверждение_1 реверсивный счетчик 13 перезапускается, начиная новый отсчет временного интервала, определяющего длительность режима ожидания устройства. Фиксация окончания циклов обработки данных первым RS-триггером 10 необходима для исключения ситуации перевода устройства в режим пониженного потребления до окончания работы самосинхронного конвейерного вычислительного блока 2. Таким образом, блок формирования управляющих сигналов 1 осуществляет анализ временного интервала между сигналами на входе Подтверждение_1 самосинхронного конвейерного вычислительного блока 2, период следования которых характеризует интенсивность работы последнего и вырабатывает управляющий сигнал на выходе Ожидание, подаваемый на вход блока управления напряжением питания 3.

Блок управления напряжением питания 3 построен по принципу коммутатора напряжений, предназначен для формирования напряжения питания самосинхронного конвейерного вычислительного блока 2 и работает по следующему алгоритму. При установлении сигнала лог.«1» на его входе (выходе Ожидание блока формирования управляющих сигналов 1) на выход подается минимальное напряжение цепей питания, при котором сохраняется переключательная способность транзисторов, входящих в состав самосинхронного конвейерного вычислительного блока 2; при установлении лог.«0» - номинальное напряжение, определяемое элементной базой и технологией изготовления управляемого устройства.

Таким образом, блок управления напряжением питания 3 осуществляет коммутацию напряжений питания самосинхронного конвейерного вычислительного блока 2 в зависимости от режима его работы устройства.

В результате существенно снижается энергопотребление самосинхронного конвейерного вычислительного блока в режиме ожидания и при этом отсутствует ограничение его быстродействия в режиме функционирования.

Источники информации

1. Jens Sparso, Steve Furber. Principles Of Asynchronous Circuit Design - A System Perspective. Kluwer Academic Publishers, Boston/Dorderecht/London, 2006. ISBN 0-7923-7613-7.

2. Патент US «Dynamic control of power consumption in self-timed circuits» №5737614 от 7.04.1998.

3. Патент US «Data processing circuit with self-timed instruction execution and power regulation», №6014749 от 11.01.2000.

| название | год | авторы | номер документа |

|---|---|---|---|

| САМОСИНХРОННОЕ ВЫЧИСЛИТЕЛЬНОЕ УСТРОЙСТВО С АДАПТИВНЫМ РЕЖИМОМ ПИТАНИЯ ЯДРА | 2009 |

|

RU2421772C2 |

| УСТРОЙСТВО ОБМЕНА ДАННЫМИ МЕЖДУ ЧЕТЫРЕХФАЗНЫМ САМОСИНХРОННЫМ И СИНХРОННЫМ ПАРАЛЛЕЛЬНЫМ ИНТЕРФЕЙСОМ | 2009 |

|

RU2402802C1 |

| САМОСИНХРОННЫЙ D-ТРИГГЕР С ИНДИКАЦИЕЙ ОТКАЗА | 2008 |

|

RU2391771C1 |

| АРИФМЕТИЧЕСКОЕ УСТРОЙСТВО ДЛЯ ВЫПОЛНЕНИЯ ДИСКРЕТНОГО ПРЕОБРАЗОВАНИЯ ФУРЬЕ | 1991 |

|

RU2015550C1 |

| Электропривод постоянного тока | 1990 |

|

SU1741247A1 |

| УСТРОЙСТВО ДЛЯ УПРАВЛЕНИЯ M-ФАЗНЫМ ВЕНТИЛЬНЫМ ПРЕОБРАЗОВАТЕЛЕМ | 1991 |

|

RU2027294C1 |

| МНОГОКАНАЛЬНАЯ СИСТЕМА ДЛЯ РЕГИСТРАЦИИ ФИЗИЧЕСКИХ ВЕЛИЧИН | 1991 |

|

RU2037190C1 |

| МНОГОКАНАЛЬНАЯ ТЕЛЕМЕТРИЧЕСКАЯ СЕЙСМОРАЗВЕДОЧНАЯ СИСТЕМА | 1994 |

|

RU2107312C1 |

| Электронные часы со звуковой сигнализацией | 1986 |

|

SU1377817A1 |

| СПОСОБ ПАРИРОВАНИЯ ПЕРЕГРУЗОК ПО ТОКУ В ЭЛЕКТРОННОМ БЛОКЕ КОСМИЧЕСКОГО АППАРАТА, ОБУСЛОВЛЕННЫХ ВНЕШНИМИ ВОЗДЕЙСТВУЮЩИМИ ФАКТОРАМИ, ВКЛЮЧАЯ ТИРИСТОРНЫЙ ЭФФЕКТ, И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 2015 |

|

RU2599089C1 |

Изобретение относится к устройствам обработки цифровых данных с помощью электрических устройств, в частности к средствам для подвода и регулирования питания, и может быть использовано в цифровых интегральных схемах, работающих по самосинхронному принципу, для автоматического контроля энергопотребления устройства или его отдельных функциональных блоков. Достигаемый технический результат заключается в снижении энергопотребления самосинхронного устройства без ограничения его быстродействия путем снижения питающего напряжения в режиме ожидания до минимально возможного уровня, при котором сохраняется его чувствительность к входным сигналам. Устройство состоит из блока управления напряжением питания, самосинхронного конвейерного вычислительного блока и блока формирования управляющих сигналов. 2 ил.

Самосинхронное устройство с автоматическим регулированием потребляемой мощности, содержащее последовательно соединенные блок управления напряжением питания, самосинхронный конвейерный вычислительный блок, соединенный со входами «Подтверждение_1» и «Подтверждение_N» блока формирования управляющих сигналов, выход которого соединен со входом блока управления напряжением питания, а вход «ЗАПРОС» совмещен с одноименным входом самосинхронного конвейерного вычислительного блока, при этом блок формирования управляющих сигналов состоит из генератора прямоугольных импульсов, соединенного с первым входом первого элемента «И», выход которого подключен к декрементирующему входу двоичного реверсивного счетчика, выход переноса которого соединен с первым входом элемента «3И», соединенного со входом установки второго RS-триггера, вход сброса которого соединен с выходом второго элемента «2И-ИЛИ», инвертирующий выход - со вторым входом первого элемента «И», а неинвертирующий выход является выходом блока формирования управляющих сигналов и соединен со вторым входом блока «И» второго элемента «2И-ИЛИ», со вторым входом второго элемента «И» и последовательно соединенными элементами «НЕ»: вторым, третьим и четвертым, выход которого соединен с первым входом второго элемента «И»; первого элемента «НЕ», выход которого соединен с вторым входом элемента «3И» и вторым входом блока «И» первого элемента «2И-ИЛИ», выход которого соединен со входом установки первого RS-триггера; первого элемента «ИЛИ», первый вход которого объединен со входом первого элемента «НЕ» и первым входом блока «И» второго элемента «2И-ИЛИ», второй вход соединен с выходом второго элемента «И», а выход соединен со входом сброса первого RS-триггера, неинвертирующий выход которого соединен с третьим входом элемента «3И»; второго элемента «ИЛИ», соединенного со входом установки двоичного реверсивного счетчика, первый вход второго элемента «ИЛИ» является входом «Подтверждение_1» блока формирования управляющих сигналов, а второй вход входом сброса блока формирования управляющих сигналов, вход первого элемента НЕ является входом «Запрос» блока формирования управляющих сигналов, первый вход блока И первого элемента «2И-ИЛИ» является входом «Подтверждение_N» блока формирования управляющих сигналов, а второй вход блока ИЛИ первого элемента «2И-ИЛИ» и второй вход блока ИЛИ второго элемента «2И-ИЛИ» являются входом сброса блока формирования управляющих сигналов, при этом блок управления напряжением питания построен по принципу коммутатора напряжений.

| US 6014749, 11.01.2000 | |||

| СПОСОБ И СИСТЕМА ДЛЯ УПРАВЛЕНИЯ ЭНЕРГОПОТРЕБЛЕНИЕМ СЕТЕВОГО ИНТЕРФЕЙСНОГО МОДУЛЯ В БЕСПРОВОДНОМ ВЫЧИСЛИТЕЛЬНОМ УСТРОЙСТВЕ | 2003 |

|

RU2313123C2 |

| RU 96109859 A, 10.08.1998 | |||

| US 5737614, 07.04.1998. | |||

Авторы

Даты

2011-01-20—Публикация

2009-06-05—Подача