Изобретение относится к области радиотехники и связи и может быть использовано в качестве устройства усиления аналоговых сигналов, в структуре аналоговых микросхем различного функционального назначения (например, широкополосных усилителях ВЧ и СВЧ диапазонов).

В современной микроэлектронике находят широкое применение классические усилители переменного тока на основе параллельно-балансных дифференциальных усилителей (ДУ), в эмиттерную цепь входных транзисторов которых включены p-n переходы [1-8]. В зависимости от стоящих задач эти p-n переходы могут уменьшать крутизну усиления ДУ, выполнять защитные функции при больших уровнях входного сигнала, расширять диапазон линейной работы ДУ и т.п.

Наиболее близкой по технической сущности к заявляемому устройству является схема по патенту США 3.541.464, fig.1.

Существенный недостаток известного ДУ, архитектура которого присутствует также в других усилительных каскадах [1-8], состоит в том, что при ограничениях на напряжение питания (Еп), характерных для SiGe технологических процессов (Еп≤2,0÷2,5 В), его коэффициент усиления по напряжению (Kу) в диапазоне средних частот получается небольшим (Kуmax=10÷20). В первую очередь это обусловлено ограничениями на сопротивления резисторов коллекторной нагрузки, которые из-за малых Еп не могут выбираться высокоомными.

Основная задача предлагаемого изобретения состоит в повышении предельных значений коэффициента усиления по напряжению ДУ для переменных ВЧ и СВЧ сигналов при низковольтном питании.

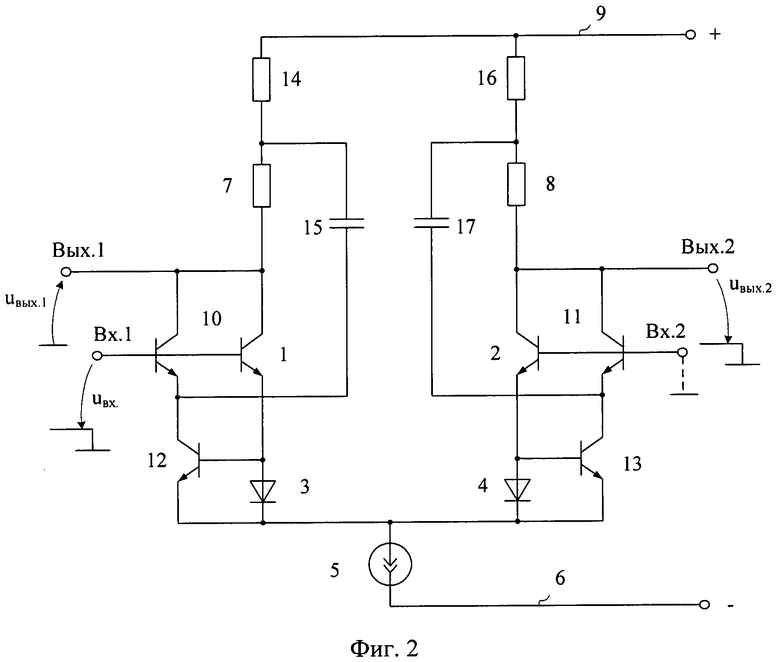

Поставленная задача решается тем, что в дифференциальном усилителе фиг.1, содержащем первый 1 и второй 2 входные транзисторы, в эмиттеры которых включены первый 3 и второй 4 p-n переходы, токостабилизирующий двухполюсник 5, включенный между общим узлом первого 3 и второго 4 p-n переходов и первой 6 шиной источников питания, первый 7 резистор коллекторной нагрузки, первый вывод которого соединен с коллектором первого 1 входного транзистора и первым выходом устройства, второй 8 резистор коллекторной нагрузки, первый вывод которого соединен с коллектором второго 2 входного транзистора и вторым выходом устройства, вторую 9 шину источников питания, предусмотрены новые элементы и связи - в схему введены первый 10, второй 11, третий 12 и четвертый 13 дополнительные транзисторы, база первого 10 дополнительного транзистора соединена с базой первого 1 входного транзистора, коллектор первого 10 дополнительного транзистора подключен к коллектору первого 1 входного транзистора, база второго 11 дополнительного транзистора соединена с базой второго 2 входного транзистора, коллектор второго 11 дополнительного транзистора подключен к коллектору второго 2 входного транзистора, эмиттер первого 10 дополнительного транзистора подключен к коллектору третьего 12 дополнительного транзистора, база третьего 12 дополнительного транзистора подключена к эмиттеру первого 1 входного транзистора, эмиттер третьего 12 дополнительного транзистора соединен с токостабилизирующим двухполюсником 5, эмиттер второго 11 дополнительного транзистора подключен к коллектору четвертого 13 дополнительного транзистора, база четвертого 13 дополнительного транзистора соединена с эмиттером второго 2 входного транзистора, эмиттер четвертого 13 дополнительного транзистора соединен с токостабилизирующим двухполюсником 5, второй вывод первого 7 резистора коллекторной нагрузки соединен со второй 9 шиной источников питания через первый 14 дополнительный резистор и через первый 15 дополнительный конденсатор подключен к эмиттеру первого 10 дополнительного транзистора, второй вывод второго 8 резистора коллекторной нагрузки соединен со второй 9 шиной источников питания через второй 16 дополнительный резистор и через второй 17 дополнительный конденсатор подключен к эмиттеру второго 11 дополнительного транзистора.

На фиг.1 показана схема ДУ-прототипа.

Схема заявляемого устройства, соответствующего формуле изобретения, показана на фиг.2.

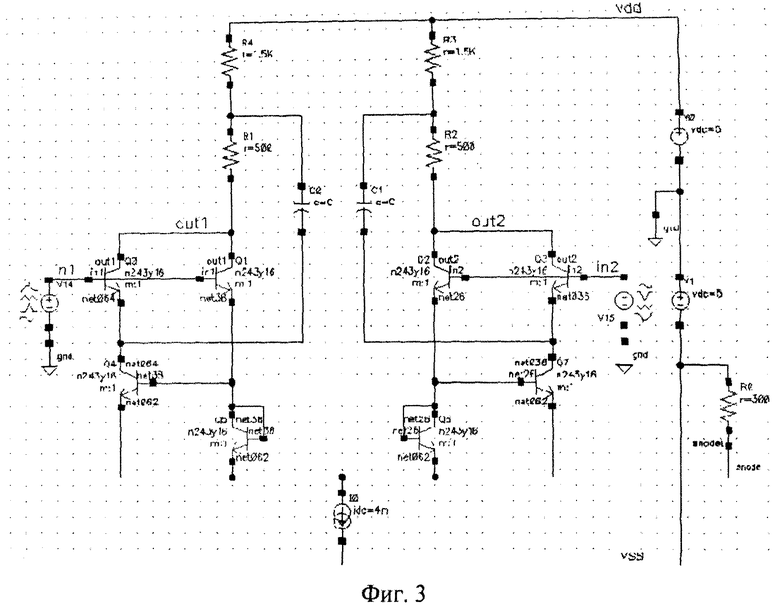

На фиг.3 представлена схема заявляемого ДУ фиг.2 в среде компьютерного моделирования Cadence на моделях интегральных транзисторов HJW.

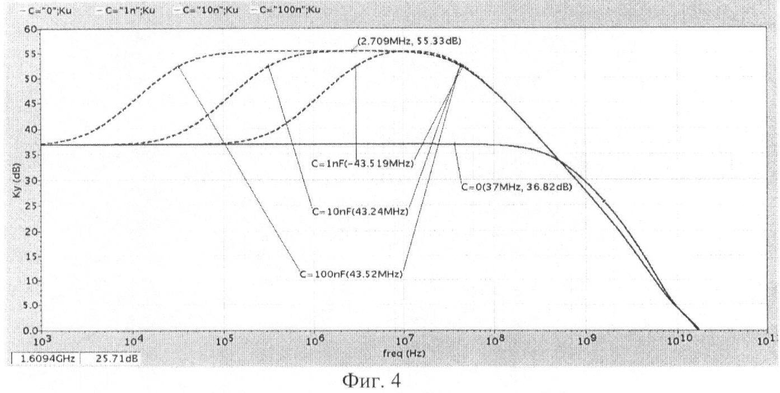

Графики фиг.4 характеризуют зависимость коэффициента усиления по напряжению (Kу) ДУ фиг.3 от численных значений емкости конденсаторов С0=C1=ϑar, полученную в результате моделирования.

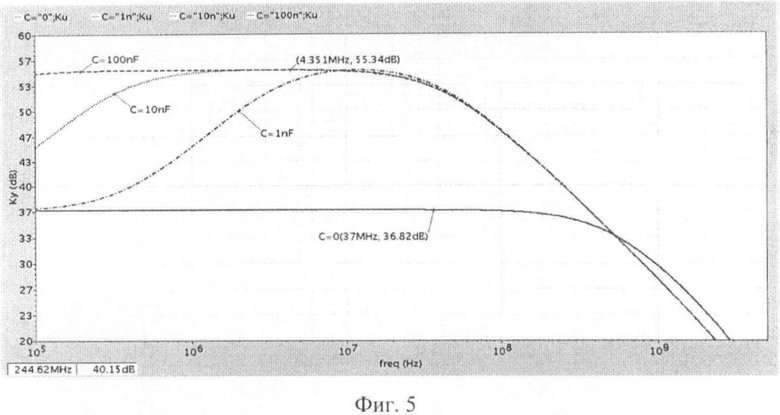

На фиг.5 показаны графики зависимости Kу схемы фиг.3 в укрупненном масштабе. Из их рассмотрения следует, что в схеме фиг.3 Kуmax=55,3 дБ, в то время как в ДУ фиг.3 при C0=C11=0 коэффициент усиления значительно меньше - 36,8 дБ.

Дифференциальный усилитель фиг.2 содержит входной первый 1 и второй 2 входные транзисторы, в эмиттеры которых включены первый 3 и второй 4 p-n переходы, токостабилизирующий двухполюсник 5, включенный между общим узлом первого 3 и второго 4 p-n переходов и первой 6 шиной источников питания, первый 7 резистор коллекторной нагрузки, первый вывод которого соединен с коллектором первого 1 входного транзистора и первым выходом устройства, второй 8 резистор коллекторной нагрузки, первый вывод которого соединен с коллектором второго 2 входного транзистора и вторым выходом устройства, вторую 9 шину источников питания. В схему введены первый 10, второй 11, третий 12 и четвертый 13 дополнительные транзисторы, база первого 10 дополнительного транзистора соединена с базой первого 1 входного транзистора, коллектор первого 10 дополнительного транзистора подключен к коллектору первого 1 входного транзистора, база второго 11 дополнительного транзистора соединена с базой второго 2 входного транзистора, коллектор второго 11 дополнительного транзистора подключен к коллектору второго 2 входного транзистора, эмиттер первого 10 дополнительного транзистора подключен к коллектору третьего 12 дополнительного транзистора, база третьего 12 дополнительного транзистора подключена к эмиттеру первого 1 входного транзистора, эмиттер третьего 12 дополнительного транзистора соединен с токостабилизирующим двухполюсником 5, эмиттер второго 11 дополнительного транзистора подключен к коллектору четвертого 13 дополнительного транзистора, база четвертого 13 дополнительного транзистора соединена с эмиттером второго 2 входного транзистора, эмиттер четвертого 13 дополнительного транзистора соединен с токостабилизирующим двухполюсником 5, второй вывод первого 7 резистора коллекторной нагрузки соединен со второй 9 шиной источников питания через первый 14 дополнительный резистор и через первый 15 дополнительный конденсатор подключен к эмиттеру первого 10 дополнительного транзистора, второй вывод второго 8 резистора коллекторной нагрузки соединен со второй 9 шиной источников питания через второй 16 дополнительный резистор и через второй 17 дополнительный конденсатор подключен к эмиттеру второго 11 дополнительного транзистора.

Рассмотрим работу ДУ фиг.2 на переменном токе.

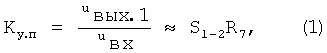

Предельный коэффициент усиления по напряжению дифференциального каскада фиг.2 по первому выходу при емкости дополнительного конденсатора 15 (C15), равной нулю, определяется сопротивлением первого 7 резистора коллекторной нагрузки (R7>>R14):

где S1-2=2(rэ1+rэ2+rэ3+rэ4)-1 - крутизна усиления ДУ в режиме короткого замыкания по выходу «Вых.1», зависящая от сопротивлений эмиттерных переходов (rэ1, rэ2) транзисторов 1, 2 и дифференциальных сопротивлений p-n переходов 3 и 4 (rэ3, rэ4).

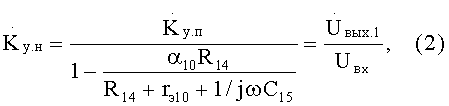

В предлагаемом ДУ фиг.2 комплексный коэффициент усиления по напряжению для выхода «Вых.1» определяется формулой:

где α10≈0,98÷0,99 - коэффициент усиления по току эмиттера транзистора 10;

rэ10 - сопротивление эмиттерного перехода транзистора 10;

R14 - сопротивление двухполюсника 14;

Kу.п - коэффициент усиления по нагрузке ДУ-прототипа;

С15 - емкость конденсатора 15.

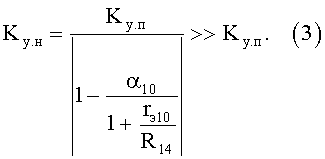

В области средних частот, когда влиянием конденсатора 15 можно пренебречь, а rэ10<<R14:

Если учесть, что типовые значения α10=0,98-0,99, а rэ10=25÷30 Oм<<R14, то из (3) следует, что предлагаемая схема ДУ имеет более высокий коэффициент усиления по напряжению в диапазоне средних частот (в пределах которого влиянием емкости С15 на Kу можно пренебречь).

Данные выводы подтверждаются результатами компьютерного моделирования (фиг.4 и фиг.5).

Таким образом, в предлагаемом ДУ фиг.2 при низкоомных резисторах коллекторной нагрузки 7 и 8 реализуются более высокие значения коэффициента усиления по напряжению.

Заявляемая схема особенно перспективна для использования в микроэлектронных SiGe изделиях СВЧ устройств, реализованных по технологии SG25VD.

Источники информации

1. Патент США №5.339.044 (1:1).

2. Патент США №3.541.464.

3. Патент США №3.801.923, fig.1.

4. Патент Японии №53-78151, fig.1.

5. Патент Японии №55030218.

6. Ав.св. СССР №593301.

7. Патент США №4.8913.604, fig.4.

8. Достал, И. Операционные усилители [Текст] / И.Достал. - М.: Мир, 1982. - С. 84, рис.3.18в.

| название | год | авторы | номер документа |

|---|---|---|---|

| ДИФФЕРЕНЦИАЛЬНЫЙ ОПЕРАЦИОННЫЙ УСИЛИТЕЛЬ С ПАРАФАЗНЫМ ВЫХОДОМ | 2011 |

|

RU2439781C1 |

| КАСКОДНЫЙ ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ | 2011 |

|

RU2469465C1 |

| ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ С ПОВЫШЕННЫМ КОЭФФИЦИЕНТОМ УСИЛЕНИЯ ПО НАПРЯЖЕНИЮ | 2011 |

|

RU2439783C1 |

| ДИФФЕРЕНЦИАЛЬНЫЙ ОПЕРАЦИОННЫЙ УСИЛИТЕЛЬ С ПАРАФАЗНЫМ ВЫХОДОМ | 2010 |

|

RU2432668C1 |

| КАСКОДНЫЙ ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ | 2011 |

|

RU2439780C1 |

| ДИФФЕРЕНЦИАЛЬНЫЙ ОПЕРАЦИОННЫЙ УСИЛИТЕЛЬ С МАЛЫМ НАПРЯЖЕНИЕМ ПИТАНИЯ | 2010 |

|

RU2432666C1 |

| КАСКОДНЫЙ ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ С ВЫСОКОЧАСТОТНОЙ КОРРЕКЦИЕЙ | 2010 |

|

RU2423778C1 |

| ДИФФЕРЕНЦИАЛЬНЫЙ ОПЕРАЦИОННЫЙ УСИЛИТЕЛЬ С МАЛЫМ НАПРЯЖЕНИЕМ ПИТАНИЯ | 2010 |

|

RU2432665C1 |

| ДИФФЕРЕНЦИАЛЬНЫЙ ОПЕРАЦИОННЫЙ УСИЛИТЕЛЬ С ПАРАФАЗНЫМ ВЫХОДОМ | 2010 |

|

RU2439778C1 |

| ВХОДНОЙ КАСКАД БЫСТРОДЕЙСТВУЮЩЕГО ОПЕРАЦИОННОГО УСИЛИТЕЛЯ | 2012 |

|

RU2509406C1 |

Изобретение относится к области радиотехники и связи и может быть использовано в качестве устройства усиления аналоговых сигналов, в структуре аналоговых микросхем различного функционального назначения (например, широкополосных усилителях ВЧ и СВЧ диапазонов). Технический результат: повышение предельных значений коэффициента усиления по напряжению ДУ для переменных ВЧ и СВЧ сигналов при низковольтном питании. Дифференциальный усилитель содержит первый (1) и второй (2) входные транзисторы, в эмиттеры которых включены первый (3) и второй (4) p-n переходы, токостабилизирующий двухполюсник (5), включенный между общим узлом первого (3) и второго (4) p-n переходов и первой (6) шиной источников питания, первый (7) резистор коллекторной нагрузки, первый вывод которого соединен с коллектором первого (1) входного транзистора и первым выходом устройства, второй (8) резистор коллекторной нагрузки, первый вывод которого соединен с коллектором второго (2) входного транзистора и вторым выходом устройства, вторую (9) шину источников питания. В схему введены первый (10), второй (11), третий (12) и четвертый (13) дополнительные транзисторы, база первого (10) дополнительного транзистора соединена с базой первого (1) входного транзистора, коллектор первого (10) дополнительного транзистора подключен к коллектору первого (1) входного транзистора, база второго (11) дополнительного транзистора соединена с базой второго (2) входного транзистора, коллектор второго (11) дополнительного транзистора подключен к коллектору второго (2) входного транзистора, эмиттер первого (10) дополнительного транзистора подключен к коллектору третьего (12) дополнительного транзистора, база третьего (12) дополнительного транзистора подключена к эмиттеру первого (1) входного транзистора, эмиттер третьего (12) дополнительного транзистора соединен с токостабилизирующим двухполюсником (5), эмиттер второго (11) дополнительного транзистора подключен к коллектору четвертого (13) дополнительного транзистора, база четвертого (13) дополнительного транзистора соединена с эмиттером второго (2) входного транзистора, эмиттер четвертого (13) дополнительного транзистора соединен с токостабилизирующим двухполюсником (5), второй вывод первого (7) резистора коллекторной нагрузки соединен со второй (9) шиной источников питания через первый (14) дополнительный резистор и через первый (15) дополнительный конденсатор подключен к эмиттеру первого (10) дополнительного транзистора, второй вывод второго (8) резистора коллекторной нагрузки соединен со второй (9) шиной источников питания через второй (16) дополнительный резистор и через второй (17) дополнительный конденсатор подключен к эмиттеру второго (11) дополнительного транзистора. 5 ил.

Дифференциальный усилитель, содержащий первый (1) и второй (2) входные транзисторы, в эмиттеры которых включены первый (3) и второй (4) p-n переходы, токостабилизирующий двухполюсник (5), включенный между общим узлом первого (3) и второго (4) p-n переходов и первой (6) шиной источников питания, первый (7) резистор коллекторной нагрузки, первый вывод которого соединен с коллектором первого (1) входного транзистора и первым выходом устройства, второй (8) резистор коллекторной нагрузки, первый вывод которого соединен с коллектором второго (2) входного транзистора и вторым выходом устройства, вторую (9) шину источников питания, отличающийся тем, что в схему введены первый (10), второй (11), третий (12) и четвертый (13) дополнительные транзисторы, база первого (10) дополнительного транзистора соединена с базой первого (1) входного транзистора, коллектор первого (10) дополнительного транзистора подключен к коллектору первого (1) входного транзистора, база второго (11) дополнительного транзистора соединена с базой второго (2) входного транзистора, коллектор второго (11) дополнительного транзистора подключен к коллектору второго (2) входного транзистора, эмиттер первого (10) дополнительного транзистора подключен к коллектору третьего (12) дополнительного транзистора, база третьего (12) дополнительного транзистора подключена к эмиттеру первого (1) входного транзистора, эмиттер третьего (12) дополнительного транзистора соединен с токостабилизирующим двухполюсником (5), эмиттер второго (11) дополнительного транзистора подключен к коллектору четвертого (13) дополнительного транзистора, база четвертого (13) дополнительного транзистора соединена с эмиттером второго (2) входного транзистора, эмиттер четвертого (13) дополнительного транзистора соединен с токостабилизирующим двухполюсником (5), второй вывод первого (7) резистора коллекторной нагрузки соединен со второй (9) шиной источников питания через первый (14) дополнительный резистор и через первый (15) дополнительный конденсатор подключен к эмиттеру первого (10) дополнительного транзистора, второй вывод второго (8) резистора коллекторной нагрузки соединен со второй (9) шиной источников питания через второй (16) дополнительный резистор и через второй (17) дополнительный конденсатор подключен к эмиттеру второго (11) дополнительного транзистора.

| US 3541464 А, 17.11.1970 | |||

| ВЫСОКОЧАСТОТНЫЙ УСИЛИТЕЛЬ НА ТРАНЗИСТОРЕ ПО СХЕМЕ С ОБЩЕЙ БАЗОЙ | 2007 |

|

RU2365028C1 |

| Дифференциальный усилитель с защитой от перегрузок | 1972 |

|

SU593301A1 |

| US 6825723 B2, 30.11.2004. | |||

Авторы

Даты

2011-06-20—Публикация

2010-05-11—Подача