Предлагаемое изобретение относится к области радиотехники и связи и может быть использовано в устройствах автоматической регулировки усиления, фазовых детекторах и модуляторах, в системах фазовой автоподстройки и умножения частоты или в качестве усилителя, коэффициент передачи по напряжению которого зависит от уровня сигнала управления. Управляемый усилитель является базовым узлом современных систем приема и обработки сигналов ВЧ- и СВЧ-диапазонов, аналоговой вычислительной и измерительной техники.

В настоящее время в аналоговой микросхемотехнике в составе систем электронной регулировки усиления, смешения или перемножения сигналов широкое применение находят схемы управляемых усилителей на основе дифференциальных каскадов с изменяющимся статическим режимом. Такая структура стала основой построения практически всех известных в настоящее время прецизионных управляемых усилителей и аналоговых перемножителей сигналов. В этой связи задача улучшения параметров этого функционального узла для РЭА нового поколения относится к числу достаточно актуальных задач современной микроэлектроники.

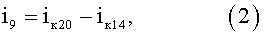

Существует несколько базовых архитектур дифференциальных каскадов (ДК). Одна из них (фиг.1), которая относится к классической архитектуре, была впервые использована в операционном усилителе µA741. В связи с высокой популярностью такого ДК на его модификации выдано более 30 патентов разных стран, например [1-30].

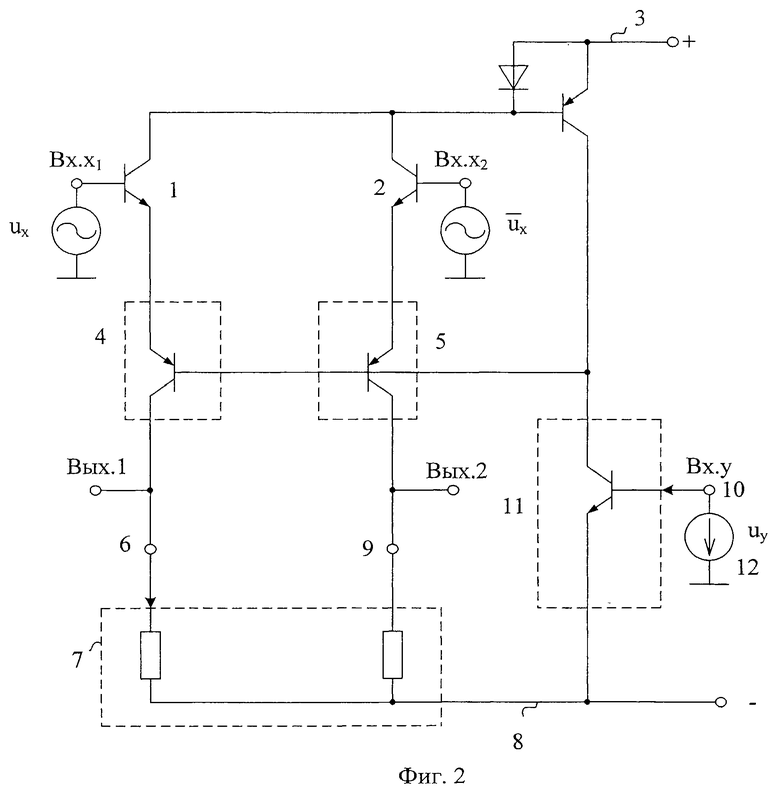

Ближайшим прототипом (фиг.1) заявляемого устройства является управляемый комплементарный усилитель, описанный в патенте США №4.059.808 fig.1, содержащий первый 1 и второй 2 входные транзисторы, коллекторы которых связаны с первым 3 источником питания, первый 4 и второй 5 выходные трехполюсники, базовые входы которых соединены друг с другом, коллекторный выход первого 4 выходного трехполюсника соединен с первым 6 входом цепи нагрузки 7, согласованной со вторым 8 источником питания, коллекторный выход второго 5 выходного трехполюсника подключен ко второму 9 входу цепи нагрузки, эмиттер первого 1 входного транзистора соединен с эмиттерным входом первого 4 выходного трехполюсника, эмиттер второго 2 входного транзистора соединен с эмиттерным входом второго 5 выходного трехполюсника, причем управляющий вход 10 управляемого источника опорного тока 11 соединен с источником управляющего напряжения 12.

Первый существенный недостаток известного управляемого усилителя состоит в том, что в рабочем диапазоне частот фаза его выходного напряжения не изменяется в зависимости от величины напряжения управления uy. Это не позволяет известному устройству выполнять функции четырехквадрантного перемножителя сигналов ux и uy.

Второй существенный недостаток известного устройства состоит в том, что управляющий вход 10 его управляемого источника опорного тока 11, обеспечивающий электронное управление коэффициентом усиления по напряжению, не «привязан» к общей шине источников питания 3 и 8. Это существенно сужает область его использования.

Основная цель предлагаемого изобретения состоит в расширении функциональных возможностей управляемого усилителя - создании условий, при которых его выходное напряжение может под действием управляющего сигнала uy менять не только свою амплитуду, но и фазу. Это позволит выполнить на базе заявляемого устройства аналоговый перемножитель сигналов ux и uy.

Вторая цель предлагаемого изобретения состоит в создании условий для электронного управления коэффициентом усиления по напряжению, при котором управляющее напряжение uy подает относительно общей шины источников питания. Реализация этой цели позволяет выполнять на базе заявляемого устройства не только широкополосные ВЧ- и СВЧ-усилители с регулируемыми параметрами, но создавать на его основе более сложные функциональные узлы, например аналоговые перемножители сигналов.

Третья дополнительная цель - создание архитектуры управляемого усилителя с малым напряжением питания и электронным управлением его коэффициента усиления по напряжению, а также обеспечение возможности практической реализации устройства по SiGe технологии SG25H2 (рабочее напряжение для n-р-n транзисторов Up=1,9 B; для р-n-р транзисторов Uп=2,8 B).

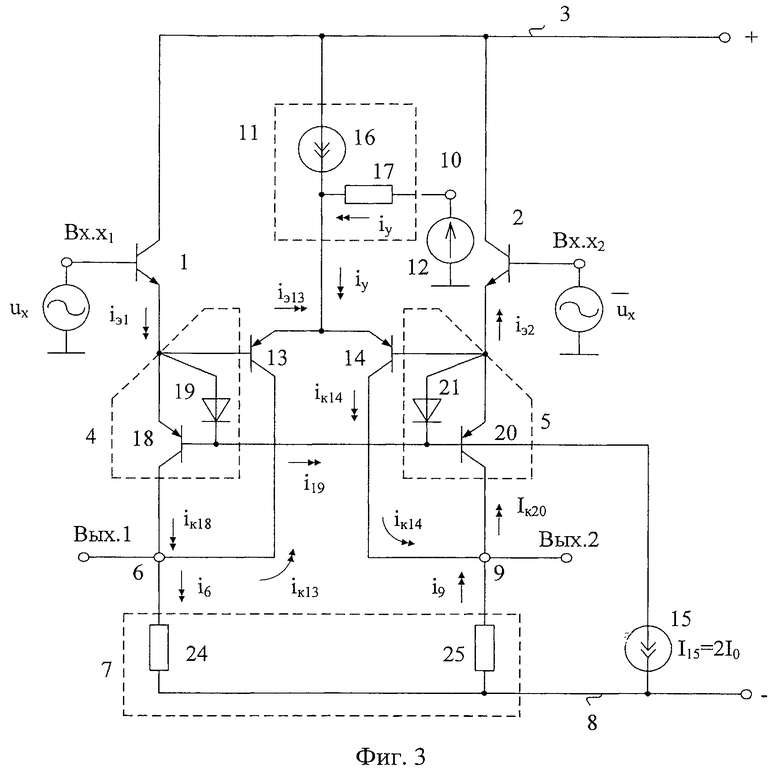

Поставленные цели достигаются тем, что в управляемый комплементарном усилителе фиг.1, содержащем первый 1 и второй 2 входные транзисторы, коллекторы которых связаны с первым 3 источником питания, первый 4 и второй 5 выходные трехполюсники, базовые входы которых соединены друг с другом, коллекторный выход первого 4 выходного трехполюсника соединен с первым 6 входом цепи нагрузки 7, согласованной со вторым 8 источником питания, коллекторный выход второго 5 выходного трехполюсника подключен ко второму 9 входу цепи нагрузки, эмиттер первого 1 входного транзистора соединен с эмиттерным входом первого 4 выходного трехполюсника, эмиттер второго 2 входного транзистора соединен с эмиттерным входом второго 5 выходного трехполюсника, причем управляющий вход 10 управляемого источника опорного тока 11 соединен с источником управляющего напряжения 12, предусмотрены новые элементы и связи - в схему введены первый 13 и второй 14 дополнительные транзисторы и дополнительный источник опорного тока 15, включенный между объединенными базовыми входами первого 4 и второго 5 выходных трехполюсников и вторым 8 источником питания, причем управляемый источник опорного тока 11 включен между первым 3 источником питания и объединенными эмиттерами первого 13 и второго 14 дополнительных транзисторов, база первого 13 дополнительного транзистора соединена с эмиттером первого 1 входного транзистора, база второго 14 дополнительного транзистора подключена к эмиттеру второго 2 входного транзистора, коллектор первого 13 дополнительного транзистора соединен с коллекторным выходом первого 4 выходного трехполюсника, коллектор второго 14 дополнительного транзистора соединен с коллекторным выходом второго 5 выходного трехполюсника.

Схема усилителя-прототипа в двух его модификациях представлена на фиг.1 и фиг.2. На фиг.3 показано заявляемое устройство в соответствии с п.1, п.2 и п.3 формулы изобретения.

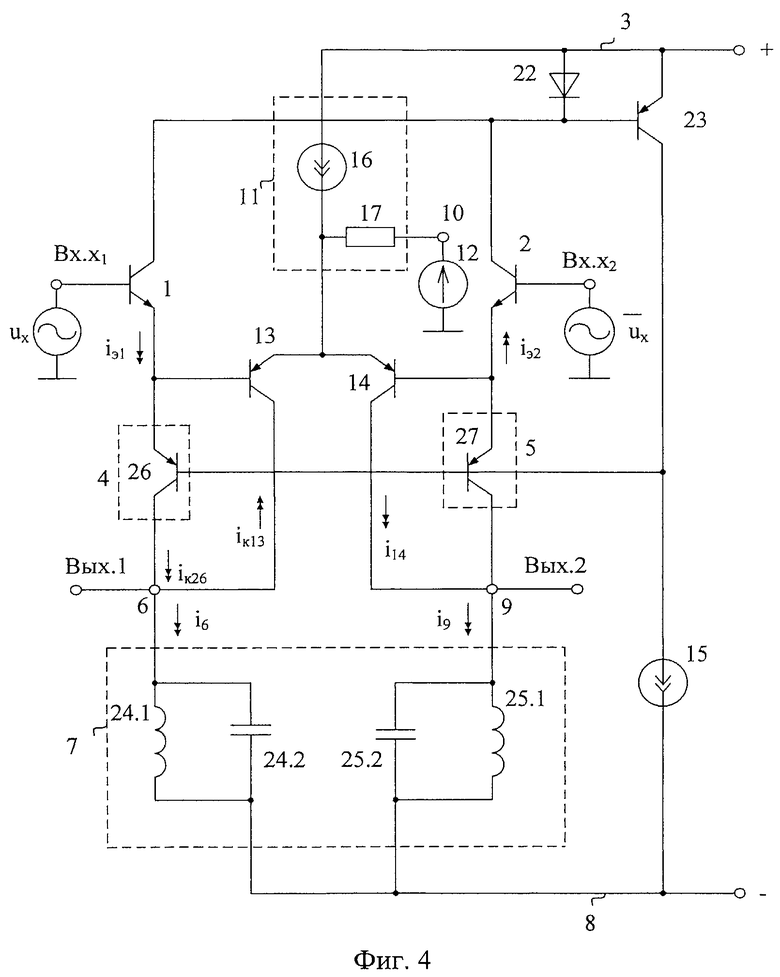

На фиг.4 приведена схема управляемого усилителя, соответствующего п.4, п.5 и п.6 формулы изобретения.

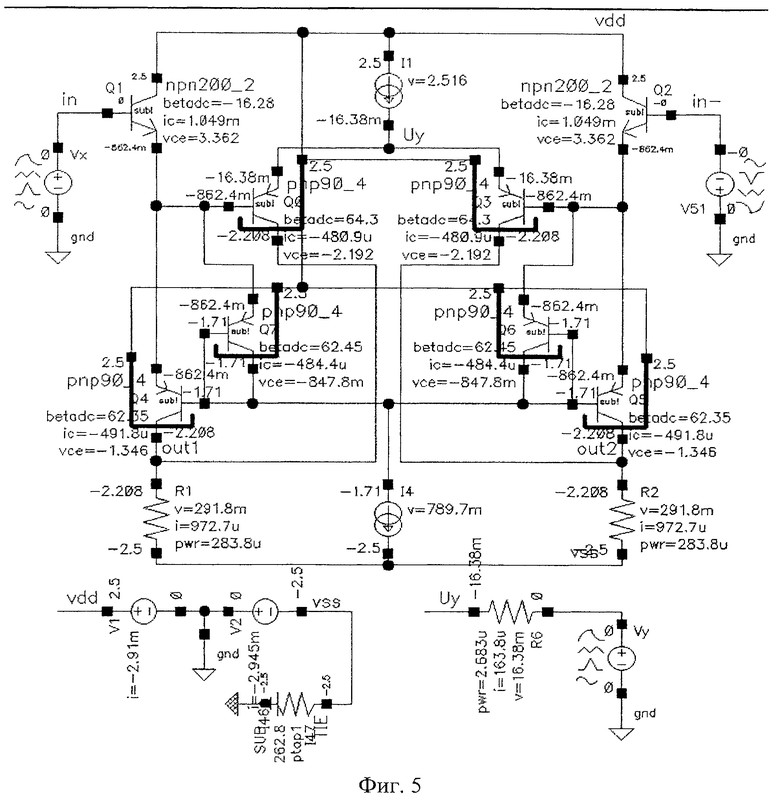

На фиг.5 показана схема заявляемого устройства в соответствии с п.1 формулы изобретения в среде компьютерного моделирования Cadence на моделях интегральных транзисторов ФГУП НПП «Пульсар».

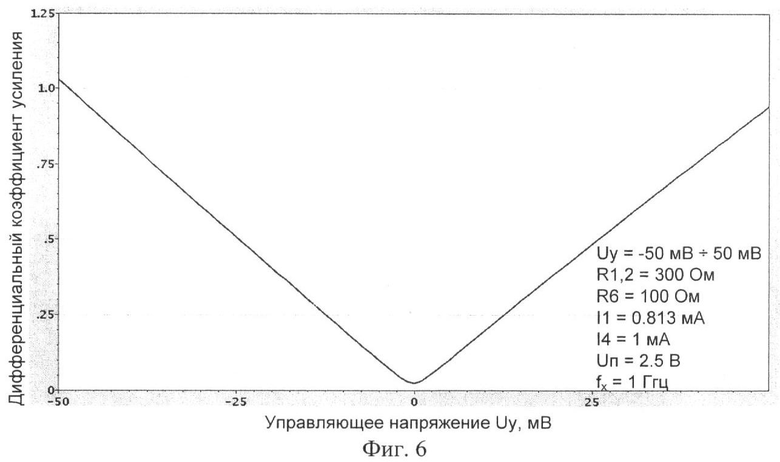

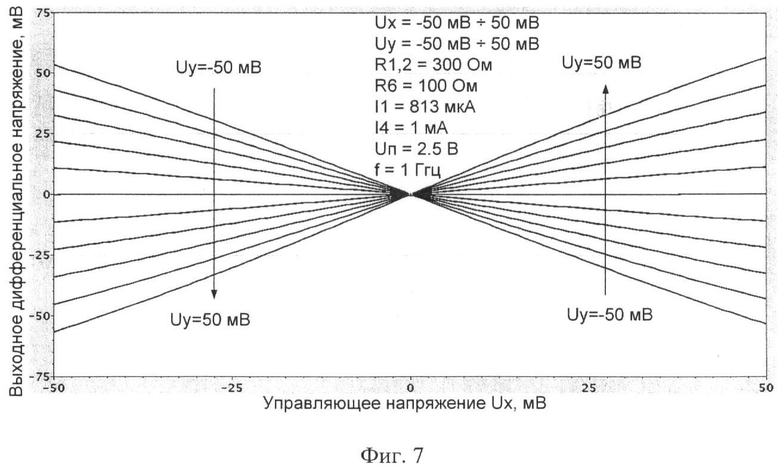

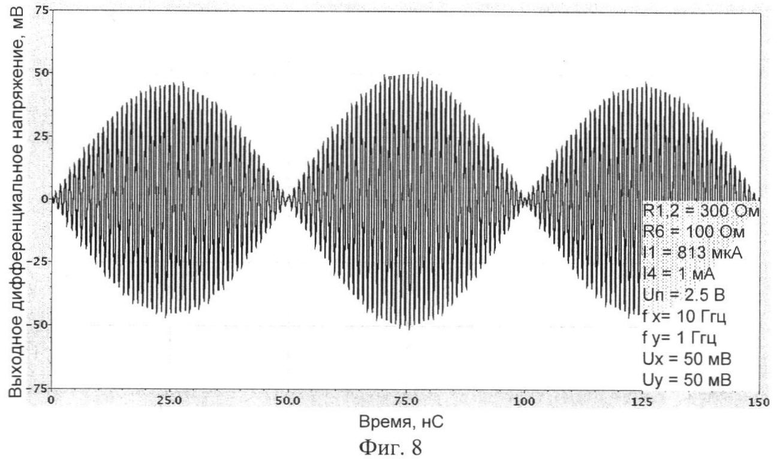

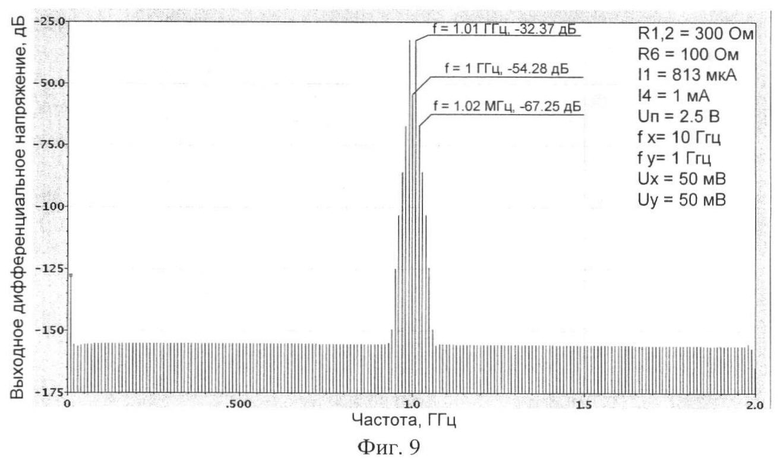

На фиг.6 - фиг.9 показаны результаты компьютерного моделирования схемы фиг.5:

- зависимость модуля коэффициента усиления Ku от напряжения управления uy в диапазоне частот (фиг.6);

- зависимость выходного дифференциального напряжения управляемого усилителя от напряжений ux и uy (фиг.7).

- временная зависимость выходного напряжения при одновременном воздействии двух входных синусоидальных напряжений ux и uy;

- спектр выходных сигналов управляемого усилителя в режиме смесителя ux и uy при fx=10 ГГц и fy=1 ГГц.

Управляемый комплементарный дифференциальный усилитель фиг.2 содержит первый 1 и второй 2 входные транзисторы, коллекторы которых связаны с первым 3 источником питания, первый 4 и второй 5 выходные трехполюсники, базовые входы которых соединены друг с другом, коллекторный выход первого 4 выходного трехполюсника соединен с первым 6 входом цепи нагрузки 7, согласованной со вторым 8 источником питания, коллекторный выход второго 5 выходного трехполюсника подключен ко второму 9 входу цепи нагрузки, эмиттер первого 1 входного транзистора соединен с эмиттерным входом первого 4 выходного трехполюсника, эмиттер второго 2 входного транзистора соединен с эмиттерным входом второго 5 выходного трехполюсника, причем управляющий вход 10 управляемого источника опорного тока 11 соединен с источником управляющего напряжения 12. В схему введены первый 13 и второй 14 дополнительные транзисторы и дополнительный источник опорного тока 15, включенный между объединенными базовыми входами первого 4 и второго 5 выходных трехполюсников и вторым 8 источником питания, причем управляемый источник опорного тока 11 включен между первым 3 источником питания и объединенными эмиттерами первого 13 и второго 14 дополнительных транзисторов, база первого 13 дополнительного транзистора соединена с эмиттером первого 1 входного транзистора, база второго 14 дополнительного транзистора подключена к эмиттеру второго 2 входного транзистора, коллектор первого 13 дополнительного транзистора соединен с коллекторным выходом первого 4 выходного трехполюсника, коллектор второго 14 дополнительного транзистора соединен с коллекторным выходом второго 5 выходного трехполюсника.

На фиг.2, в соответствии с п.2 формулы изобретения, управляемый источник опорного тока 11 содержит первый 16 токостабилизирующий двухполюсник, включенный между первым 3 источником питания и объединенными эмиттерами первого 13 и второго 14 дополнительных транзисторов, а также масштабирующий резистор 17, включенный между управляющим входом 10 управляемого источника тока 11 и объединенными эмиттерами первого 13 и второго 14 дополнительных транзисторов.

На фиг.3, в соответствии с п.3 формулы изобретения, первый 4 выходной трехполюсник содержит первый 18 вспомогательный транзистор, эмиттер которого соединен с эмиттером первого 1 входного транзистора и является эмиттерным входом первого 4 выходного трехполюсника, а коллектор подключен к первому 6 входу цепи нагрузки 7 и является коллекторным выходом первого 4 выходного трехполюсника, первый вспомогательный р-n переход 19, включенный между эмиттером и базой первого вспомогательного транзистора 18, база которого является базовым входом первого 4 выходного трехполюсника, второй 5 выходной трехполюсник содержит второй 20 вспомогательный транзистор, эмиттер которого соединен с эмиттером второго 2 входного транзистора и является эмиттерным входом второго 5 выходного трехполюсника, а коллектор подключен ко второму 9 входу цепи нагрузки 7 и является коллекторным выходом второго 5 выходного трехполюсника, второй вспомогательный р-n переход 21, включенный между эмиттером и базой второго 20 вспомогательного транзистора, база которого является базовым входом второго 5 выходного трехполюсника.

На фиг.4, в соответствии с п.4 формулы изобретения, коллекторы первого 1 и второго 2 входных транзисторов связаны с первым 3 источником питания через третий 22 вспомогательный р-n переход и, кроме этого, подключены к базе третьего 23 вспомогательного транзистора, эмиттер которого соединен с первым 3 источником питания, а коллектор связан с объединенными базовыми входами первого 4 и второго 5 выходных трехполюсников.

Кроме этого, на фиг.4, в соответствии с п.5 формулы изобретения, цепь нагрузки 7 содержит первый 24 и второй 25 LC-элементы нагрузки, включенные соответственно между первым 6 входом цепи нагрузки и вторым 8 источником питания, а также между вторым 9 входом цепи нагрузки 7 и вторым 8 источником питания.

Кроме этого, на фиг.4, в соответствии с п.6 формулы изобретения, первый 4 выходной трехполюсник содержит четвертый 26 вспомогательный транзистор, эмиттер которого является эмиттерным входом первого 4 выходного трехполюсника, база - его базовым входом, а коллектор - коллекторным выходом первого 4 выходного трехполюсника, второй 5 выходной трехполюсник содержит пятый 27 вспомогательный транзистор, эмиттер которого является эмиттерным входом второго 5 выходного трехполюсника, база - его базовым входом, а коллектор - коллекторным выходом второго 5 выходного трехполюсника.

Рассмотрим работу заявляемого устройства в режиме управляемого усилителя напряжения ux (фиг.3).

В статическом режиме при нулевом напряжении управления (uy=0) токи через масштабирующий резистор 17 близок к нулю.

Каждый из переменных токов первого 6 и второго 9 входов цепи нагрузки 7 складывается из двух противофазных составляющих:

где iк18, iк13, iк20, iк14 - коллекторные токи транзисторов 18, 13, 20 и 14 при положительном приращении ux на входе Вх.1.

За счет выбора статических токов двухполюсников 11 и 15, определяющих усиление на переменном токе дифференциальных каскадов на транзисторах 1, 2, 13-14 и дифференциального каскада на транзисторах 1, 2, 18, 20 можно получить нулевое значение выходного дифференциального напряжения управляемого усилителя фиг.3

где R24=R25 - сопротивления двухполюсников 24 и 25 цепи нагрузки 7 (в частном случае - резисторов).

Если управляющее напряжение uy (12) получает положительное приращение uy>0, то это вызывает увеличение суммарного тока общей эмиттерной цепи транзисторов 13 и 14 на величину iy и, как следствие, увеличение коэффициента усиления по напряжению дифференциального каскада на транзисторах 1, 2, 13, 14, инвертирующего фазу ux к выходу Вых.1. Поэтому в формулах (1) и (2) токи iк13 и iк14 начинают превышать соответствующее значение токов iк18 и iк20, которые не зависят от uy, a выходное дифференциальное напряжение управляемого усилителя будет иметь фазу φΣ=φх+180°, где φх - фаза входного напряжения ux. Амплитуда выходного дифференциального напряжения в этом случае при ux=const будет также возрастать пропорционально uy (фиг.6).

Если напряжение uy отрицательно, то суммарный ток общей эмиттерной цепи транзисторов 13 и 14 уменьшается. В схеме фиг.3 в этом случае начинают преобладать токи iк18 и iк20, а выходное дифференциальное напряжение усилителя будет иметь такую же фазу, что и выходное напряжение ux на входе Вх.1.

Таким образом, выходное напряжение в заявляемом устройстве изменяется в зависимости от uy не только по амплитуде, но и по фазе, что является одним из условий реализации на его базе не только управляемого усилителя, но перемножителя двух сигналов ux и uy (фиг.7, фиг.8) или их смесителя (фиг.9).

Аналогично работает схема фиг.4, в которой цепь нагрузки 7 содержит LC-колебательные контуры, выделяющие необходимые спектральные составляющие после смешения сигналов ux и uy (фиг.9).

Замечательная особенность схем фиг.3, фиг.4 - подавление передачи сигнала управления uy на дифференциальный выход управляемого усилителя, что весьма важно для построения смесителя и/или перемножителя сигналов ux и uy.

Коэффициент подавления сигнала управления может иметь особенно высокие значения при специальном построении управляемого источника опорного тока 10, при котором изменения тока iy через резистор 17 передаются по параллельному (не зависящему от ux) каналу в цепь нагрузки 7 и компенсируют приращения токов iy/2 в коллекторных цепях транзисторов 13-14.

Таким образом, заявляемый комплементарный дифференциальный усилитель имеет электронное управление коэффициентом усиления, фаза которого изменяется в зависимости от величины uy (фиг.6). Причем сигнал управления uy, как и входной сигнал ux подаются на соответствующие входы относительно общей шины (без разделительных конденсаторов).

Как следует из рассмотрения графиков фиг.7, фиг.8, фиг.9, заявляемое устройство выполняет функции аналогового перемножителя малых сигналов ux и uy.

Диапазон перемножения по каналу «X» может быть расширен традиционным способом - применением входных логарифмирующих диодов.

БИБЛИОГРАФИЧЕСКИЙ СПИСОК

1. Патент США №3.786.362

2. Патент США №4.030.044

3. Патент США №4.059.808, фиг.5

4. Патент США №4.286.227

5. Авт. свид. СССР №375754, H03f 3/38

6. Авт. свид. СССР №843164, H03f 3/30

7. Патент США №3.660.773

8. Патент США №4.560.948

9. Патент РФ №2930041, H03f 1/32

10. Патент Японии №57-5364, H03f 3/343

11. Патент ЧССР №134845, кл. 21a2 18/08

12. Патент ЧССР №134849, кл. 21a2 18/08

13. Патент ЧССР №135326, кл. 21а2 18/08

14. Патент США №4.389.579

15. Патент Англии №1543361, Н3Т

16. Патент США №5.521.552 (фиг.3а)

17. Патент США №4.059.808

18. Патент США №5.789.949

19. Патент США №4.453.134

20. Патент США №4.760.286

21. Авт. свид. СССР №1283946

22. Патент РФ №2019019

23. Патент США №4.3 89.579

24. Патент США №4.453.092

25. Патент США №3.566.289

26. Патент США №4.059.808 (фиг.2)

27. Патент США №3.649.926

28. Патент США №4.714.894 (фиг.1)

29. Матавкин В.В. Быстродействующие операционные усилители. - М.: Радио и связь, 1989.

30. Херпи М. Аналоговые интегральные схемы. - М.: Радио и связь, 1983, стр.174, рис.5.52.

| название | год | авторы | номер документа |

|---|---|---|---|

| УПРАВЛЯЕМЫЙ УСИЛИТЕЛЬ И АНАЛОГОВЫЙ СМЕСИТЕЛЬ СИГНАЛОВ | 2013 |

|

RU2530259C1 |

| КОМПЛЕМЕНТАРНЫЙ ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ С УПРАВЛЯЕМЫМ УСИЛЕНИЕМ | 2008 |

|

RU2384937C1 |

| КАСКОДНЫЙ ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ С УПРАВЛЯЕМЫМ УСИЛЕНИЕМ | 2008 |

|

RU2389130C1 |

| АНАЛОГОВЫЙ ПЕРЕМНОЖИТЕЛЬ НАПРЯЖЕНИЙ | 2008 |

|

RU2396595C2 |

| УПРАВЛЯЕМЫЙ УСИЛИТЕЛЬ И СМЕСИТЕЛЬ АНАЛОГОВЫХ СИГНАЛОВ НА БАЗЕ ДИФФЕРЕНЦИАЛЬНОГО КАСКАДА ДАРЛИНГТОНА | 2013 |

|

RU2519348C1 |

| КОМПЛЕМЕНТАРНЫЙ КАСКОДНЫЙ ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ С УПРАВЛЯЕМЫМ УСИЛЕНИЕМ | 2008 |

|

RU2388137C1 |

| КОМПЛЕМЕНТАРНЫЙ ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ С УПРАВЛЯЕМЫМ УСИЛЕНИЕМ | 2008 |

|

RU2384938C1 |

| КАСКОДНЫЙ ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ С УПРАВЛЯЕМЫМ УСИЛЕНИЕМ | 2008 |

|

RU2388139C1 |

| АНАЛОГОВЫЙ ПЕРЕМНОЖИТЕЛЬ НАПРЯЖЕНИЙ | 2008 |

|

RU2383054C1 |

| Безрезистивный арсенид-галлиевый дифференциальный каскад и операционный усилитель на его основе с малым напряжением смещения нуля | 2023 |

|

RU2815912C1 |

Изобретение относится к области радиотехники и связи и может быть использовано в устройствах автоматической регулировки усиления, фазовых детекторах и модуляторах, в системах фазовой автоподстройки и умножения частоты или в качестве усилителя, коэффициент передачи по напряжению которого зависит от уровня сигнала управления. Управляемый усилитель является базовым узлом современных систем приема и обработки сигналов ВЧ- и СВЧ-диапазонов, аналоговой вычислительной и измерительной техники. Технический результат: расширение функциональных возможностей управляемого усилителя - создание условий, при которых его выходное напряжение может под действием управляющего сигнала uу менять не только свою амплитуду, но и фазу. Это позволит выполнить на базе заявляемого устройства аналоговый перемножитель сигналов ux и uу. Управляемый комплементарный дифференциальный усилитель содержит первый (1) и второй (2) входные транзисторы, коллекторы которых связаны с первым (3) источником питания, первый (4) и второй (5) выходные трехполюсники, базовые входы которых соединены друг с другом, коллекторный выход первого (4) выходного трехполюсника соединен с первым (6) входом цепи нагрузки (7), согласованной со вторым (8) источником питания, коллекторный выход второго (5) выходного трехполюсника подключен ко второму (9) входу цепи нагрузки, эмиттер первого (1) входного транзистора соединен с эмиттерным входом первого (4) выходного трехполюсника, эмиттер второго (2) входного транзистора соединен с эмиттерным входом второго (5) выходного трехполюсника, причем управляющий вход (10) управляемого источника опорного тока (11) соединен с источником управляющего напряжения (12). В схему введены первый (13) и второй (14) дополнительные транзисторы и дополнительный источник опорного тока (15), включенный между объединенными базовыми входами первого (4) и второго (5) выходных трехполюсников и вторым (8) источником питания, причем управляемый источник опорного тока (11) включен между первым (3) источником питания и объединенными эмиттерами первого (13) и второго (14) дополнительных транзисторов, база первого (13) дополнительного транзистора соединена с эмиттером первого (1) входного транзистора, база второго (14) дополнительного транзистора подключена к эмиттеру второго (2) входного транзистора, коллектор первого (13) дополнительного транзистора соединен с коллекторным выходом первого (4) выходного трехполюсника, коллектор второго (14) дополнительного транзистора соединен с коллекторным выходом второго (5) выходного трехполюсника. 5 з.п. ф-лы, 9 ил.

1. Управляемый комплементарный дифференциальный усилитель, содержащий первый (1) и второй (2) входные транзисторы, коллекторы которых связаны с первым (3) источником питания, первый (4) и второй (5) выходные трехполюсники, базовые входы которых соединены друг с другом, коллекторный выход первого (4) выходного трехполюсника соединен с первым (6) входом цепи нагрузки (7), согласованной со вторым (8) источником питания, коллекторный выход второго (5) выходного трехполюсника подключен ко второму (9) входу цепи нагрузки, эмиттер первого (1) входного транзистора соединен с эмиттерным входом первого (4) выходного трехполюсника, эмиттер второго (2) входного транзистора соединен с эмиттерным входом второго (5) выходного трехполюсника, причем управляющий вход (10) управляемого источника опорного тока (11) соединен с источником управляющего напряжения (12), отличающийся тем, что в схему введены первый (13) и второй (14) дополнительные транзисторы и дополнительный источник опорного тока (15), включенный между объединенными базовыми входами первого (4) и второго (5) выходных трехполюсников и вторым (8) источником питания, причем управляемый источник опорного тока (11) включен между первым (3) источником питания и объединенными эмиттерами первого (13) и второго (14) дополнительных транзисторов, база первого (13) дополнительного транзистора соединена с эмиттером первого (1) входного транзистора, база второго (14) дополнительного транзистора подключена к эмиттеру второго (2) входного транзистора, коллектор первого (13) дополнительного транзистора соединен с коллекторным выходом первого (4) выходного трехполюсника, коллектор второго (14) дополнительного транзистора соединен с коллекторным выходом второго (5) выходного трехполюсника.

2. Управляемый комплементарный дифференциальный усилитель по п.1, отличающийся тем, что управляемый источник опорного тока (11) содержит первый (16) токостабилизирующий двухполюсник, включенный между первым (3) источником питания и объединенными эмиттерами первого (13) и второго (14) дополнительных транзисторов, а также масштабирующий резистор (17), включенный между управляющим входом (10) управляемого источника тока (11) и объединенными эмиттерами первого (13) и второго (14) дополнительных транзисторов.

3. Управляемый комплементарный дифференциальный усилитель по п.1, отличающийся тем, что первый (4) выходной трехполюсник содержит первый (18) вспомогательный транзистор, эмиттер которого соединен с эмиттером первого (1) входного транзистора и является эмиттерным входом первого (4) выходного трехполюсника, а коллектор подключен к первому (6) входу цепи нагрузки (7) и является коллекторным выходом первого (4) выходного трехполюсника, первый вспомогательный р-n переход (19), включенный между эмиттером и базой первого вспомогательного транзистора (18), база которого является базовым входом первого (4) выходного трехполюсника, второй (5) выходной трехполюсник содержит второй (20) вспомогательный транзистор, эмиттер которого соединен с эмиттером второго (2) входного транзистора и является эмиттерным входом второго (5) выходного трехполюсника, а коллектор подключен ко второму (9) входу цепи нагрузки (7) и является коллекторным выходом второго (5) выходного трехполюсника, второй вспомогательный р-n переход (21), включенный между эмиттером и базой второго (20) вспомогательного транзистора, база которого является базовым входом второго (5) выходного трехполюсника.

4. Управляемый комплементарный дифференциальный усилитель по п.1, отличающийся тем, что коллекторы первого (1) и второго (2) входных транзисторов связаны с первым (3) источником питания через третий (22) вспомогательный р-n переход и, кроме этого, подключены к базе третьего (23) вспомогательного транзистора, эмиттер которого соединен с первым (3) источником питания, а коллектор связан с объединенными базовыми входами первого (4) и второго (5) выходных трехполюсников.

5. Управляемый комплементарный дифференциальный усилитель по п.1, отличающийся тем, что цепь нагрузки (7) содержит первый (24) и второй (25) LC-элементы нагрузки, включенные соответственно между первым (6) входом цепи нагрузки и вторым (8) источником питания, а также между вторым (9) входом цепи нагрузки (7) и вторым (8) источником питания.

6. Управляемый комплементарный дифференциальный усилитель по п.4, отличающийся тем, что первый (4) выходной трехполюсник содержит четвертый (26) вспомогательный транзистор, эмиттер которого является эмиттерным входом первого (4) выходного трехполюсника, база - его базовым входом, а коллектор - коллекторным выходом первого (4) выходного трехполюсника, второй (5) выходной трехполюсник содержит пятый (27) вспомогательный транзистор, эмиттер которого является эмиттерным входом второго (5) выходного трехполюсника, база - его базовым входом, а коллектор - коллекторным выходом второго (5) выходного трехполюсника.

| US 4059808 А, 22.11.1977 | |||

| ОПЕРАЦИОННЫЙ УСИЛИТЕЛЬ | 0 |

|

SU375754A1 |

| Усилитель низкой частоты | 1977 |

|

SU843164A1 |

| US 3786362 А, 15.01.1974. | |||

Авторы

Даты

2011-06-20—Публикация

2010-03-24—Подача