Предполагаемое изобретение относится к области радиотехники и может использоваться в качестве базового функционального узла (операционного усилителя) многих устройств автоматики, вычислительной техники, систем связи и приборостроения.

Введение отрицательной обратной связи по синфазному сигналу в симметричных активных нагрузках на двух транзисторных источниках опорного тока входного дифференциального каскада операционного усилителя (ОУ) широко используется в современной микросхемотехнике [1-4], в т.ч. в серийных ОУ фирмы AnalogDevicesAD4041, AD4042, а также в патентах фирм TexasInstrumentsUS 7411451, 2008 г., фиг. 2 и MaximIntegratedProductsUS 5952882, фиг. 9, 1999 г.

В практических схемах ОУ транзисторные источники опорного тока в динамических нагрузках входного дифференциального каскада ОУ реализуются как на p-n-p [1], так и на n-p-n [2] биполярных транзисторах, что определяется используемыми технологическими процессами. Однако, перспективный арсенид-галлиевый техпроцесс [5], осваиваемый Минским НИИ радиоматериалов (https://mniirm.by/)в интересах Союзного государства, обеспечивает создание только p-n-p биполярных и nJFet полевых транзисторов. Отсутствие n-p-n транзисторов создает схемотехнические проблемы построения GaAs ОУ. Это не позволяет выпускать высокотемпературные GaAs ОУ, востребованные в ряде важных отраслей науки и техники - космическом приборостроении, нефтегазовой, автомобильной и авиационной промышленности.

Ближайшим прототипом (фиг. 1) заявляемого устройства является операционный усилитель, представленный в монографии «Архитектура и схемотехника дифференциальных усилителей с повышенным ослаблением синфазных сигналов : монография / Н.Н. Прокопенко, С.В. Крюков. – Шахты : ГОУ ВПО «ЮРГУЭС», 2008. – С. 25, рис. 1.26». Он содержит первый 1 и второй 2 входы, первый 3 и второй 4 входные трехполюсники, базовый вход 5 первого 3 входного трехполюсника соединен с первым 1 входом устройства, базовый вход 6 второго 4 входного трехполюсника соединен со вторым 2 входом устройства, эмиттерный вход 7 первого 3 входного трехполюсника соединен с эмиттерным входом 8 второго 4 входного трехполюсника и через токостабилизирующий двухполюсник 9 соединен с первой 10 шиной источника питания, коллекторный вход 11 первого 3 транзисторного входного трехполюсника подключен к коллектору первого 12 выходного транзистора и соединен с базой второго 13 выходного транзистора, коллекторный выход 14 второго 4 входного трехполюсника соединен с коллектором третьего 15 выходного транзистора и базой четвертого 16 выходного транзистора, объединенные эмиттеры второго 13 и четвертого 16 выходных транзисторов соединены с базами первого 12 и третьего 15 выходных транзисторов и через согласующий двухполюсник 17 соединены со второй 18 шиной источника питания, к которой подключены эмиттеры первого 12 и третьего 15 выходных транзисторов, коллектор второго 13 выходного транзистора соединен с первым 19 токовым выходом устройства, а коллектор четвертого 16 выходного транзистора связан со вторым 20 токовым выходом устройства.

Существенный недостаток ОУ – прототипа состоит в том, что он не реализуется, например, в рамках арсенид-галлиевого технологического процесса, осваиваемого Минским НИИ радиоматериалов, из-за отсутствия n-p-n арсенид-галлиевых транзисторов, без которых невозможна реализация n-p-n токовых зеркал, подключаемых к первому 19 и второму 20 токовым выходам, и других функциональных узлов ОУ с традиционной схемотехникой.

Основная задача предполагаемого изобретения состоит в создании схемы входного дифференциального каскада и операционного усилителя на его основе, которая реализуется в рамках совмещенного GaAs технологического процесса, позволяющего создавать только p-n-p биполярные и nJFet полевые транзисторы. Первая дополнительная задача – создание схемы ОУ с малым уровнем систематической составляющей напряжения смещения нуля (Uсм) без применения токовых зеркал на n-p-n или nJFet транзисторах. Вторая дополнительная задача – построение схемы ОУ только на арсенид-галлиевых транзисторах – без применения интегральных резисторов, которые неудовлетворительно работают при высоких температурах.

Поставленные задачи достигаются тем, что в дифференциальном каскаде фиг. 1, содержащем первый 1 и второй 2 входы, первый 3 и второй 4 входные трехполюсники, базовый вход 5 первого 3 входного трехполюсника соединен с первым 1 входом устройства, базовый вход 6 второго 4 входного трехполюсника соединен со вторым 2 входом устройства, эмиттерный вход 7 первого 3 входного трехполюсника соединен с эмиттерным входом 8 второго 4 входного трехполюсника и через токостабилизирующий двухполюсник 9 соединен с первой 10 шиной источника питания, коллекторный вход 11 первого 3 транзисторного входного трехполюсника подключен к коллектору первого 12 выходного транзистора и соединен с базой второго 13 выходного транзистора, коллекторный выход 14 второго 4 входного трехполюсника соединен с коллектором третьего 15 выходного транзистора и базой четвертого 16 выходного транзистора, объединенные эмиттеры второго 13 и четвертого 16 выходных транзисторов соединены с базами первого 12 и третьего 15 выходных транзисторов и через согласующий двухполюсник 17 соединены со второй 18 шиной источника питания, к которой подключены эмиттеры первого 12 и третьего 15 выходных транзисторов, коллектор второго 13 выходного транзистора соединен с первым 19 токовым выходом устройства, а коллектор четвертого 16 выходного транзистора связан со вторым 20 токовым выходом устройства, предусмотрены новые элементы и связи - согласующий двухполюсник17 выполнен в виде двух параллельно включенных эмиттерных p-n переходов биполярных транзисторов, первый 19 токовый выход устройства связан с общей шиной источников питания, токостабилизирующий двухполюсник 9 выполнен в виде двух идентичных и параллельно включенных первого 21 и второго 22 источников опорного тока на арсенид-галлиевых полевых транзисторах, второй 20 токовый выход устройства связан с первой 10 шиной источника питания через выходной источник опорного тока 23 на арсенид-галлиевых полевых транзисторах, схема которого идентична схемам первого 21 и второго 22 источников опорного тока, первый 3 и второй 4 входные трехполюсники реализованы на арсенид-галлиевых каскодных составных полевых транзисторах 26 и 27.

На фиг. 1 показана схема операционного усилителя – прототипа.

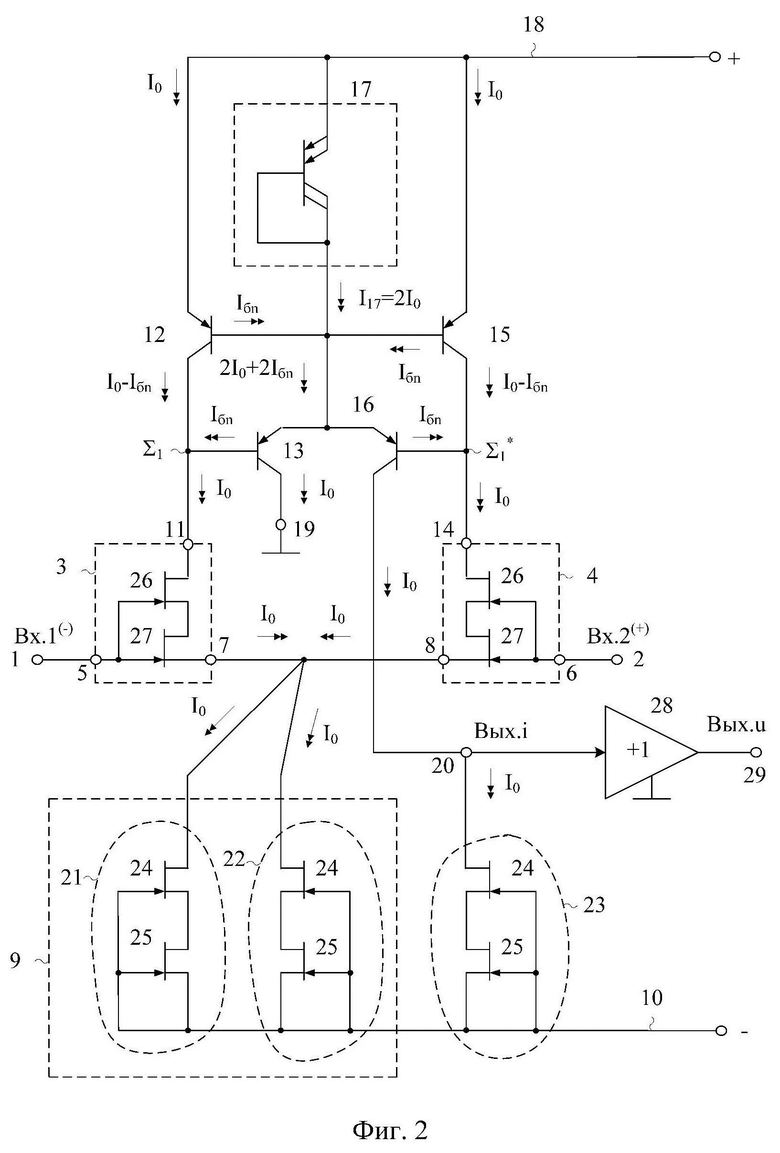

На фиг. 2 представлена схема заявляемого операционного усилителя в соответствии с формулой изобретения.

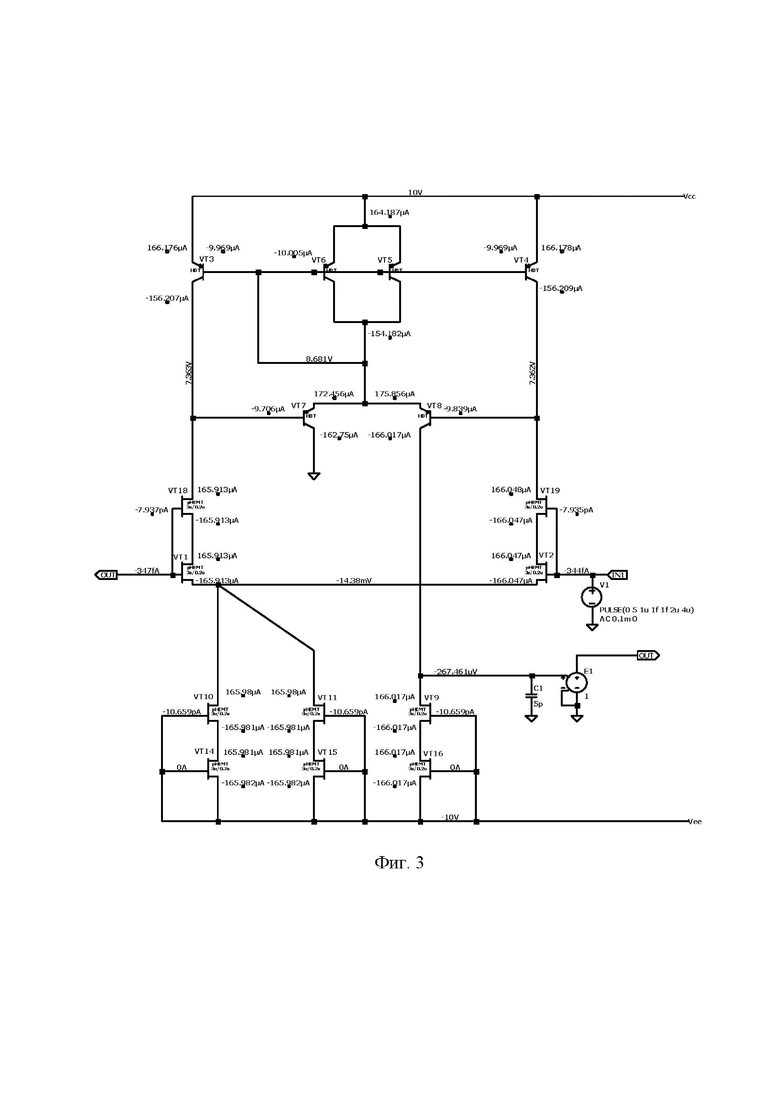

На фиг. 3 приведен статический режим безрезистивного ОУ фиг. 2 в среде LTspice при t=27 °C, Vcc=10 В, Vee=-10 В, Cк=5 пФ, ширине канала JFet транзисторов 3 мкм.

На чертеже фиг. 4 показана логарифмическая амплитудно-частотная характеристика безрезистивного ОУ фиг. 3 в среде LTspice при t=27 °C, Vcc=10 В, Vee=-10 В, Cк=5 пФ и ширине канала JFET транзисторов 3 мкм.

Безрезистивный арсенид-галлиевый операционный усилитель на основе дифференциального каскада с малым напряжением смещения нуля фиг. 2 содержит первый 1 и второй 2 входы, первый 3 и второй 4 входные трехполюсники, базовый вход 5 первого 3 входного трехполюсника соединен с первым 1 входом устройства, базовый вход 6 второго 4 входного трехполюсника соединен со вторым 2 входом устройства, эмиттерный вход 7 первого 3 входного трехполюсника соединен с эмиттерным входом 8 второго 4 входного трехполюсника и через токостабилизирующий двухполюсник 9 соединен с первой 10 шиной источника питания, коллекторный вход 11 первого 3 транзисторного входного трехполюсника подключен к коллектору первого 12 выходного транзистора и соединен с базой второго 13 выходного транзистора, коллекторный выход 14 второго 4 входного трехполюсника соединен с коллектором третьего 15 выходного транзистора и базой четвертого 16 выходного транзистора, объединенные эмиттеры второго 13 и четвертого 16 выходных транзисторов соединены с базами первого 12 и третьего 15 выходных транзисторов и через согласующий двухполюсник 17 соединены со второй 18 шиной источника питания, к которой подключены эмиттеры первого 12 и третьего 15 выходных транзисторов, коллектор второго 13 выходного транзистора соединен с первым 19 токовым выходом устройства, а коллектор четвертого 16 выходного транзистора связан со вторым 20 токовым выходом устройства, отличающийся тем, что согласующий двухполюсник17 выполнен в виде двух параллельно включенных эмиттерных p-n переходов биполярных транзисторов, первый 19 токовый выход устройства связан с общей шиной источников питания, токостабилизирующий двухполюсник 9 выполнен в виде двух идентичных и параллельно включенных первого 21 и второго 22 источников опорного тока на арсенид-галлиевых полевых транзисторах, второй 20 токовый выход устройства связан с первой 10 шиной источника питания через выходной источник опорного тока 23 на арсенид-галлиевых полевых транзисторах, схема которого идентична схемам первого 21 и второго 22 источников опорного тока, первый 3 и второй 4 входные трехполюсники реализованы на арсенид-галлиевых каскодных составных полевых транзисторах 26 и 27.

На чертеже фиг. 2, в соответствии с п. 2 формулы изобретения, второй 20 токовый выход устройства связан со входом буферного усилителя 28, выход которого 29 является потенциальным выходом операционного усилителя.

Рассмотрим работу заявляемого ОУ фиг. 2.

Статический режим операционного усилителя фиг. 2 устанавливается идентичными источниками опорного тока 21, 22 и 23, выходные токи которых (I0 и 2I0) выбираются разработчиком и зависят от ширины канала входного 25 и выходного 24 полевых транзисторов.

Для токов, протекающих в элементах схемы, справедливы следующие уравнения Кирхгофа:

где Iбn – ток базы первого 12, третьего 15, второго 13, четвертого 16 выходных p-n-p транзисторов, который определяется их коэффициентом усиления по току базы  , причем

, причем

где  - ток эмиттера p-n-p транзистора.

- ток эмиттера p-n-p транзистора.

При нулевом входном токе буферного усилителя 28 разностный ток  в высокоимпедансном узле 20 определяется уравнением

в высокоимпедансном узле 20 определяется уравнением

Поэтому систематическая составляющая напряжения смещения нуля ОУ на чертеже фиг.2 (при идентичных первом 3 и втором 4 входных трехполюсниках) близка к нулю

где  крутизна усиления входного дифференциального каскада со входов 1, 2 к высокоимпедансному узлу 20.

крутизна усиления входного дифференциального каскада со входов 1, 2 к высокоимпедансному узлу 20.

Результаты компьютерного моделирования фиг. 3 показывают, что систематическая составляющая напряжения смещения нуля предлагаемого ОУ, который не содержит токовых зеркал на n-p-n транзисторах, принимает небольшие значения (порядка 267 мкВ), которые определяются эффектами второго порядка малости.

Таким образом, заявляемое устройство не содержит интегральных резисторов, неудовлетворительно работающих при высоких температурах, имеет существенные преимущества по напряжению смещения нуля в сравнении с ОУ-прототипом. Рассмотренные схемотехнические решения могут использоваться для построения высокотемпературных микросхем на GaAs и на других широкозонных полупроводниках (GaN, SiC).

БИБЛИОГРАФИЧЕСКИЙ СПИСОК

1. Архитектура и схемотехника дифференциальных усилителей с повышенным ослаблением синфазных сигналов : монография / Н.Н. Прокопенко, С.В. Крюков. – Шахты : ГОУ ВПО «ЮРГУЭС», 2008. – С. 25, рис. 1.26.

2. Патент фирмы Texas Instruments US 7411451, фиг. 2, 2008 г.

3. Патент фирмы Maxim Integrated Products US 5952882, фиг. 9, 1999 г.

4. Полонников Д.Е. Операционные усилители. Принципы построения, теория, схемотехника. – М.: Энергоатомиздат, 1983. – С. 130, рис. 4.4.

5. Унифицированные схемотехнические решения аналоговых арсенид-галлиевых микросхем / Дворников О.В., Павлючик А.А., Прокопенко Н.Н., Чеховский В.А., Кунц А.В., Чумаков В.Е. // Известия вузов. Электроника. 2022. Т. 27. № 4. С. 475–488. DOI: https://doi.org/10.24151/1561-5405-2022-27-4-475-488.

| название | год | авторы | номер документа |

|---|---|---|---|

| Безрезистивный арсенид-галлиевый операционный усилитель с малым уровнем систематической составляющей напряжения смещения нуля | 2023 |

|

RU2814681C1 |

| Арсенид-галлиевый операционный усилитель на p-n-p биполярных и полевых транзисторах с управляющим p-n переходом | 2023 |

|

RU2813281C1 |

| Операционный усилитель на основе широкозонных полупроводников | 2023 |

|

RU2822157C1 |

| Арсенид-галлиевый операционный усилитель | 2023 |

|

RU2813140C1 |

| ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ НА АРСЕНИД-ГАЛЛИЕВЫХ ПОЛЕВЫХ ТРАНЗИСТОРАХ | 2021 |

|

RU2770912C1 |

| БИПОЛЯРНО-ПОЛЕВОЙ АРСЕНИД-ГАЛЛИЕВЫЙ БУФЕРНЫЙ УСИЛИТЕЛЬ | 2023 |

|

RU2796638C1 |

| Многоканальный дифференциальный усилитель на арсенид-галлиевых полевых и биполярных транзисторах | 2022 |

|

RU2792710C1 |

| АРСЕНИД-ГАЛЛИЕВЫЙ ВЫХОДНОЙ КАСКАД БЫСТРОДЕЙСТВУЮЩЕГО ОПЕРАЦИОННОГО УСИЛИТЕЛЯ | 2022 |

|

RU2773912C1 |

| НЕИНВЕРТИРУЮЩИЙ УСИЛИТЕЛЬ ТОКА КЛАССА "АВ" | 2022 |

|

RU2783042C1 |

| Прецизионный арсенид-галлиевый операционный усилитель с малым уровнем систематической составляющей напряжения смещения нуля и повышенным коэффициентом усиления | 2023 |

|

RU2813370C1 |

Изобретение относится к области радиотехники. Технический результат: создание схемы ОУ с малым уровнем систематической составляющей напряжения смещения нуля без применения токовых зеркал на n-p-n или nJFet транзисторах. Для этого предложен безрезистивный арсенид-галлиевый операционный усилитель на основе дифференциального каскада с малым напряжением смещения нуля, в котором согласующий двухполюсник (17) выполнен в виде двух параллельно включенных эмиттерных p-n переходов биполярных транзисторов, первый (19) токовый выход устройства связан с общей шиной, токостабилизирующий двухполюсник (9) выполнен в виде двух идентичных и параллельно включенных первого (21) и второго (22) источников опорного тока, второй (20) токовый выход устройства связан с первой (10) шиной через выходной источник опорного тока (23), схема которого идентична схемам первого (21) и второго (22) источников опорного тока, первый (3) и второй (4) входные трехполюсники реализованы на арсенид-галлиевых каскодных составных полевых транзисторах (26) и (27). 1 з.п. ф-лы, 4 ил.

1. Безрезистивный арсенид-галлиевый операционный усилитель на основе дифференциального каскада с малым напряжением смещения нуля, содержащий первый (1) и второй (2) входы, первый (3) и второй (4) входные трехполюсники, базовый вход (5) первого (3) входного трехполюсника соединен с первым (1) входом устройства, базовый вход (6) второго (4) входного трехполюсника соединен со вторым (2) входом устройства, эмиттерный вход (7) первого (3) входного трехполюсника соединен с эмиттерным входом (8) второго (4) входного трехполюсника и через токостабилизирующий двухполюсник (9) соединен с первой (10) шиной источника питания, коллекторный вход (11) первого (3) транзисторного входного трехполюсника подключен к коллектору первого (12) выходного транзистора и соединен с базой второго (13) выходного транзистора, коллекторный выход (14) второго (4) входного трехполюсника соединен с коллектором третьего (15) выходного транзистора и базой четвертого (16) выходного транзистора, объединенные эмиттеры второго (13) и четвертого (16) выходных транзисторов соединены с базами первого (12) и третьего (15) выходных транзисторов и через согласующий двухполюсник (17) соединены со второй (18) шиной источника питания, к которой подключены эмиттеры первого (12) и третьего (15) выходных транзисторов, коллектор второго (13) выходного транзистора соединен с первым (19) токовым выходом устройства, а коллектор четвертого (16) выходного транзистора связан со вторым (20) токовым выходом устройства, отличающийся тем, что согласующий двухполюсник (17) выполнен в виде двух параллельно включенных эмиттерных p-n переходов биполярных транзисторов, первый (19) токовый выход устройства связан с общей шиной источников питания, токостабилизирующий двухполюсник (9) выполнен в виде двух идентичных и параллельно включенных первого (21) и второго (22) источников опорного тока на арсенид-галлиевых полевых транзисторах, второй (20) токовый выход устройства связан с первой (10) шиной источника питания через выходной источник опорного тока (23) на арсенид-галлиевых полевых транзисторах, схема которого идентична схемам первого (21) и второго (22) источников опорного тока, первый (3) и второй (4) входные трехполюсники реализованы на арсенид-галлиевых каскодных составных полевых транзисторах (26) и (27).

2. Безрезистивный арсенид-галлиевый операционный усилитель на основе дифференциального каскада с малым напряжением смещения нуля по п. 1, отличающийся тем, что второй (20) токовый выход устройства связан со входом буферного усилителя (28), выход которого (29) является потенциальным выходом операционного усилителя.

| Н.Н | |||

| ПРОКОПЕНКО, С.В | |||

| КРЮКОВ Архитектура и схемотехника дифференциальных усилителей с повышенным ослаблением синфазных сигналов: монография, Шахты: ГОУ ВПО "ЮРГУЭС", 2008, рис | |||

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| БЫСТРОДЕЙСТВУЮЩИЙ ДИФФЕРЕНЦИАЛЬНЫЙ ОПЕРАЦИОННЫЙ УСИЛИТЕЛЬ | 2017 |

|

RU2652504C1 |

| БЫСТРОДЕЙСТВУЮЩИЙ ОПЕРАЦИОННЫЙ УСИЛИТЕЛЬ НА ОСНОВЕ ДВУХТАКТНОГО «ПЕРЕГНУТОГО» КАСКОДА | 2022 |

|

RU2786422C1 |

| US 4600893 A1, 15.07.1986. | |||

Авторы

Даты

2024-03-25—Публикация

2023-11-03—Подача