Предлагаемое изобретение относится к области радиотехники и связи и может быть использовано в устройствах автоматической регулировки усиления, фазовых детекторах и модуляторах, в системах фазовой автоподстройки и умножения частоты или в качестве усилителя, коэффициент передачи по напряжению которого зависит от уровня сигнала управления. Управляемый усилитель является базовым узлом современных систем приема и обработки сигналов ВЧ- и СВЧ-диапазонов, аналоговой вычислительной и измерительной техники.

В настоящее время в аналоговой микросхемотехнике в составе систем электронной регулировки усиления, смешения или перемножения сигналов широкое применение находят схемы управляемых усилителей на основе дифференциальных каскадов с изменяющимся статическим режимом. Такая структура стала основой построения практически всех известных в настоящее время прецизионных управляемых усилителей и аналоговых перемножителей сигналов. В этой связи задача улучшения параметров этого функционального узла РЭА нового поколения относится к числу достаточно актуальных задач современной микроэлектроники.

Известны схемы комплементарных дифференциальных усилителей (КДУ), реализованных на основе двух параллельно включенных дифференциальных каскадов (ДК) с источниками опорного тока в эмиттерных цепях входных транзисторов (так называемые «dual input stage») [1-20]. По такой архитектуре, на модификации которой выдано более 50 патентов различных стран, выполнены микросхемы ведущих микроэлектронных фирм (НА5190, НА2539 и др. [16, 18]). Все варианты построения дифференциальных усилителей «dual input stage» можно разбить на два больших класса. В усилителях первого класса передача сигнала от параллельно включенных по входу дифференциальных каскадов на выход осуществляется через сумматоры выходных токов, реализованные в виде двух токовых зеркал [1-13]. В усилителях второго класса сигнал от входных дифференциальных каскадов передается на выход дифференциального усилителя через сумматор выходных токов, реализованный в виде транзисторных каскадов по схеме с общей базой [14-20].

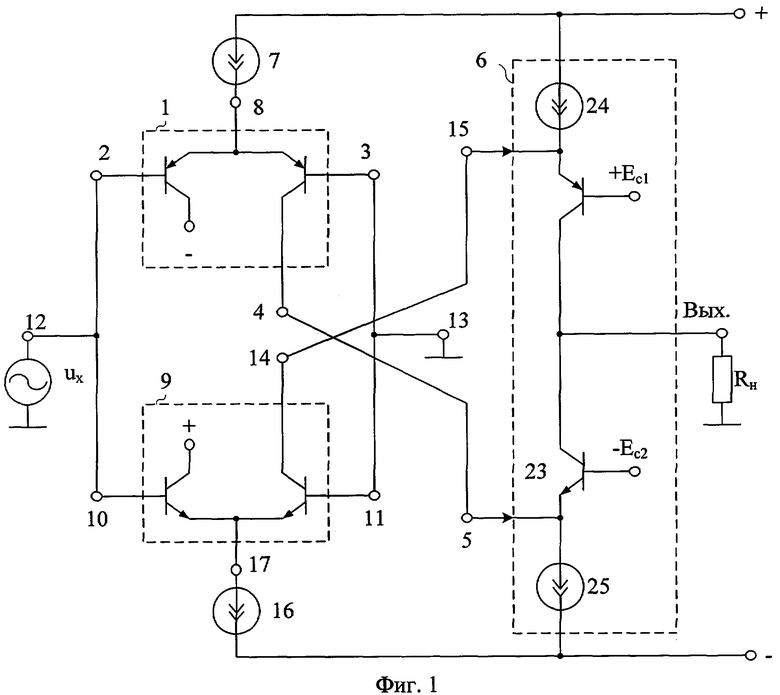

Ближайшим прототипом (фиг.1) заявляемого устройства является комплементарный дифференциальный усилитель (КДУ), описанный в патенте США №4.600.893 (фирма Toshiba) фиг.3, содержащий первый 1 дифференциальный каскад, имеющий первый 2 и второй 3 потенциальные входы, токовый выход 4, связанный с первым 5 входом выходного сумматора токов 6, первый 7 источник опорного тока, соединенный с общей эмиттерной цепью 8 первого 1 дифференциального каскада, второй дифференциальный каскад 9, имеющий первый 10 и второй 11 потенциальные входы, связанные с соответствующими первым 2 и вторым 3 потенциальными входами первого дифференциального каскада 1 и первым 12 и вторым 13 входами комплементарного дифференциального усилителя, а также токовый выход 14, связанный со вторым 15 входом выходного сумматора токов 6, второй 16 источник опорного тока, соединенный с общей эмиттерной цепью 17 второго дифференциального каскада 9.

Существенный недостаток известного КДУ состоит в том, что он не имеет специального входа «У» для электронного управления коэффициентом усиления по напряжению, «привязанному» к общей шине источников питания. Это существенно сужает область его использования, не позволяет реализовывать на его основе адаптивные функциональные узлы систем на кристалле, например СВЧ-операционные усилители, у которых петлевое усиление изменяется по заданному алгоритму в зависимости от свойств источников сигнала и цепей обратных связей (см. например, патент РФ №2307393 «Способ управления коэффициентом передачи решающего усилителя с глубокой отрицательной обратной связью»).

Основная цель предлагаемого изобретения состоит в создании условий для электронного управления коэффициентом усиления по напряжению КДУ. При этом управляющее напряжение Uy должно подаваться относительно общей шины источников питания. Реализация этой цели позволяет выполнять на базе заявляемого устройства не только широкополосные ВЧ- и СВЧ-усилители с регулируемыми параметрами, но создавать на его основе более сложные функциональные узлы, например, аналоговые перемножители широкополосных сигналов.

Первая дополнительная цель - создание архитектуры КДУ с малым напряжением питания и электронным управлением его коэффициента усиления по напряжению, а также обеспечение возможности практической реализации устройства по технологии SG25H2 (рабочее напряжение для n-p-n транзисторов Up=1,9В, для p-n-p транзисторов Uп=2,8B).

Вторая дополнительная цель - реализация на базе известного КДУ функции аналогового смесителя двух напряжений.

Поставленная цель достигается тем, что в дифференциальном усилителе фиг.1, содержащем первый 1 дифференциальный каскад, имеющий первый 2 и второй 3 потенциальные входы, токовый выход 4, связанный с первым 5 входом выходного сумматора токов 6, первый 7 источник опорного тока, соединенный с общей эмиттерной цепью 8 первого 1 дифференциального каскада, второй дифференциальный каскад 9, имеющий первый 10 и второй 11 потенциальные входы, связанные с соответствующими первым 2 и вторым 3 потенциальными входами первого дифференциального каскада 1 и первым 12 и вторым 13 входами комплементарного дифференциального усилителя, а также токовый выход 14, связанный со вторым 15 входом выходного сумматора токов 6, второй 16 источник опорного тока, соединенный с общей эмиттерной цепью 17 второго дифференциального каскада 9, предусмотрены новые элементы и связи - в схему введен первый дополнительный транзистор 18, эмиттер которого через первый дополнительный резистор 19 связан с общей эмиттерной цепью 17 второго 9 дифференциального каскада и первым дополнительным 20 источником опорного тока, база - соединена с первым управляющим входом 21 комплементарного дифференциального усилителя, а коллектор - связан с общей эмиттерной цепью 8 первого дифференциального каскада 1.

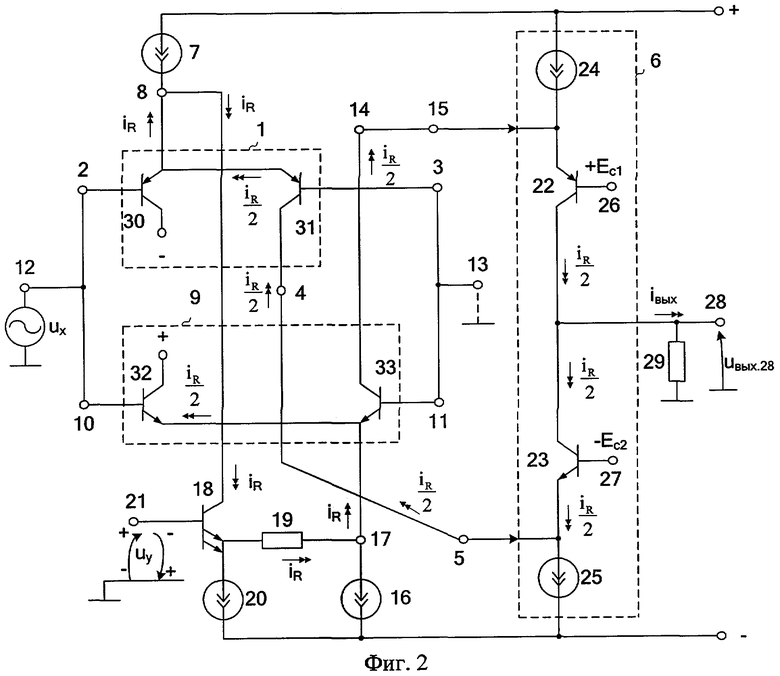

Схема усилителя-прототипа представлена на фиг.1. На фиг.2 показано заявляемое устройство в соответствии с п.1 формулы изобретения.

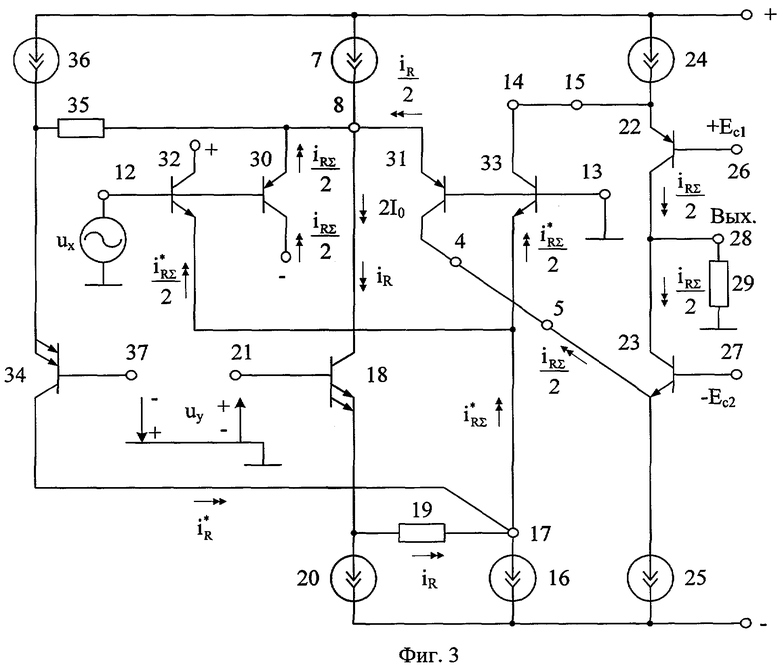

На фиг.3 приведена схема КДУ, соответствующего п.2. формулы изобретения.

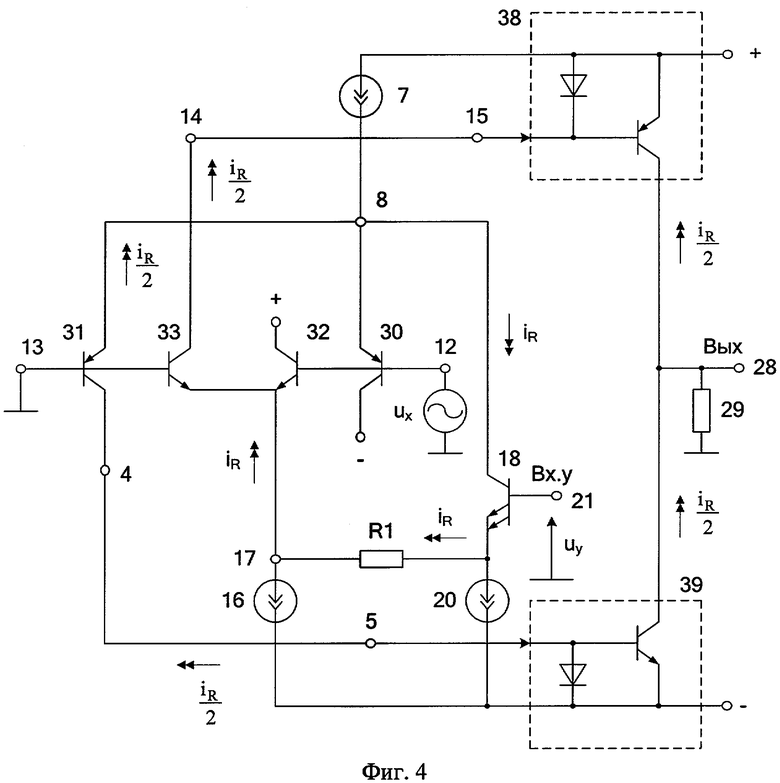

На фиг.4 представлена схема КДУ, в которой выходной сумматор токов 6 реализован на основе токовых зеркал 38 и 39.

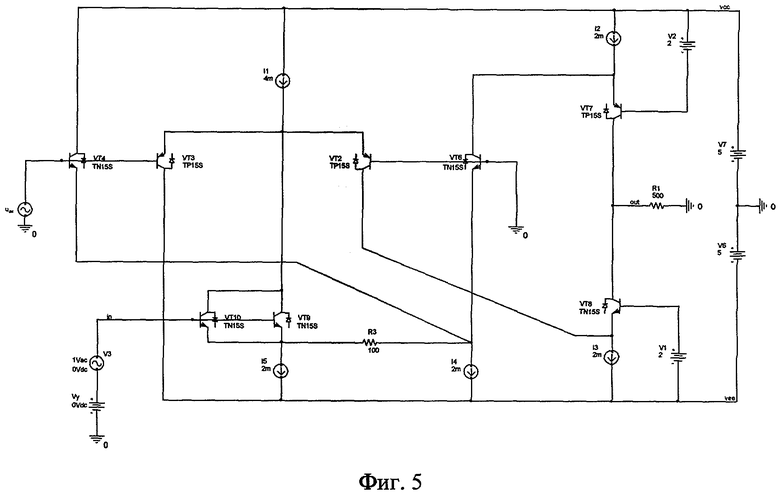

На фиг.5 показана схема заявляемого устройства в среде компьютерного моделирования PSpice на моделях интегральных транзисторов ФГУП НПП «Пульсар».

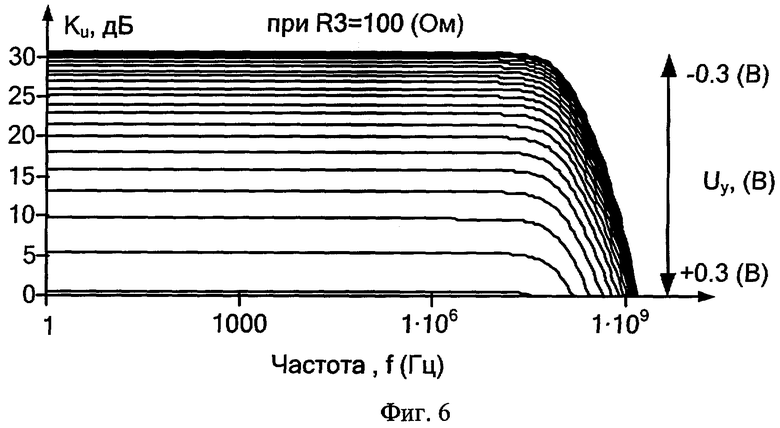

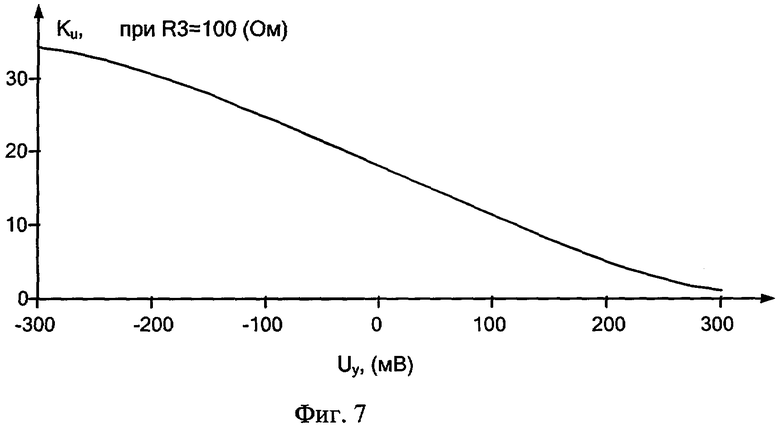

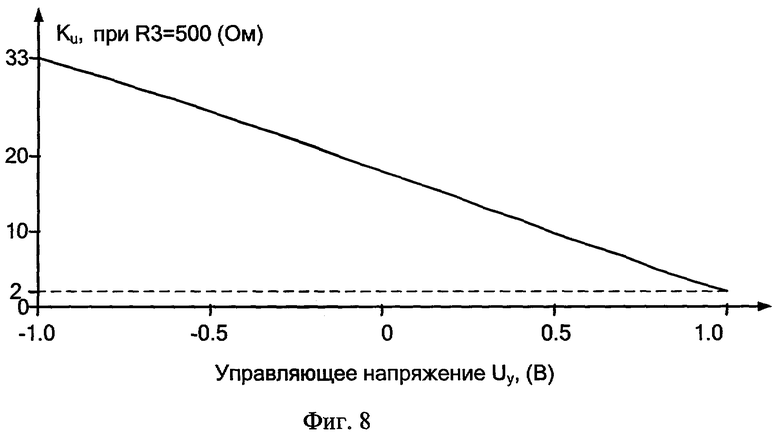

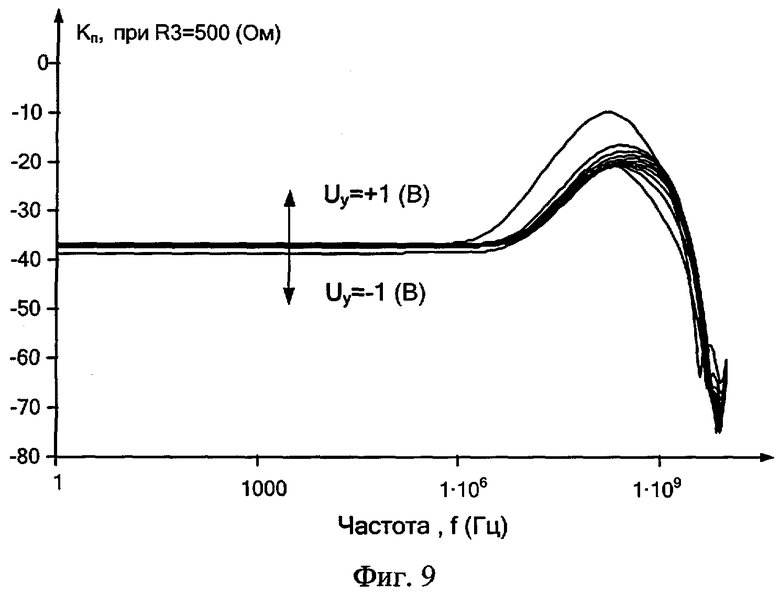

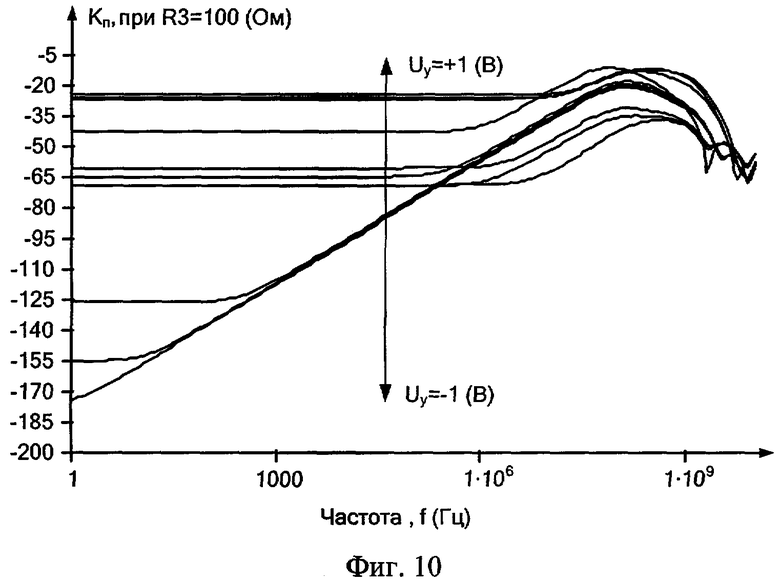

На фиг.6 - фиг.10 показаны результаты компьютерного моделирования схемы фиг.5:

- зависимость коэффициентов усиления по напряжению Ku от напряжения управления Uy (в диапазоне частот фиг.6);

- зависимость коэффициентов усиления по напряжению Ku от напряжения управления Uy при сопротивлении резистора R3=100 Ом (фиг.7);

- зависимость коэффициентов усиления по напряжению Ku от напряжения управления Uy при сопротивлении резистора R3=500 Ом (фиг.8);

- зависимость коэффициента подавления сигнала управления Ku от частоты при различных значениях постоянной составляющей сигнала управления при сопротивлении резистора R3=500 Ом (фиг.9);

- зависимость коэффициента подавления сигнала управления Кп от частоты при различных значениях постоянной составляющей сигнала управления Uy при сопротивлении резистора R3=100 Ом (фиг.10).

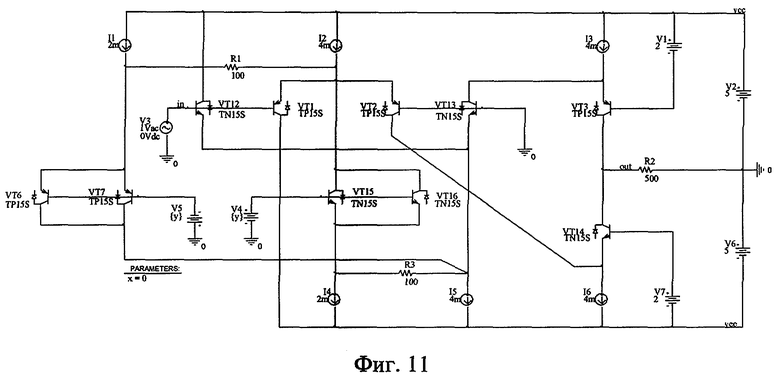

На фиг.11 показана схема заявляемого устройства в соответствии с п.2 формулы изобретения в среде компьютерного моделирования PSpice на моделях интегральных транзисторов ФГУП НПП «Пульсар».

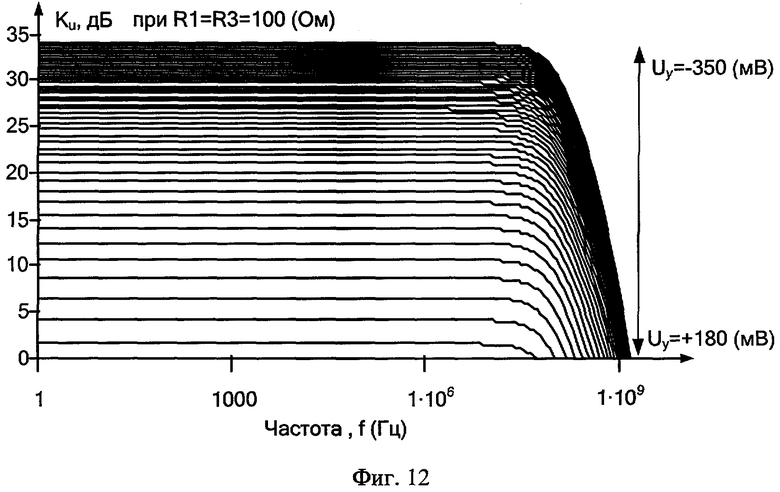

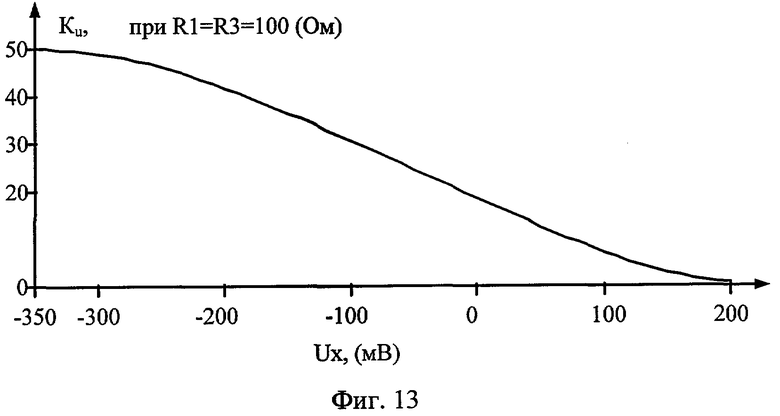

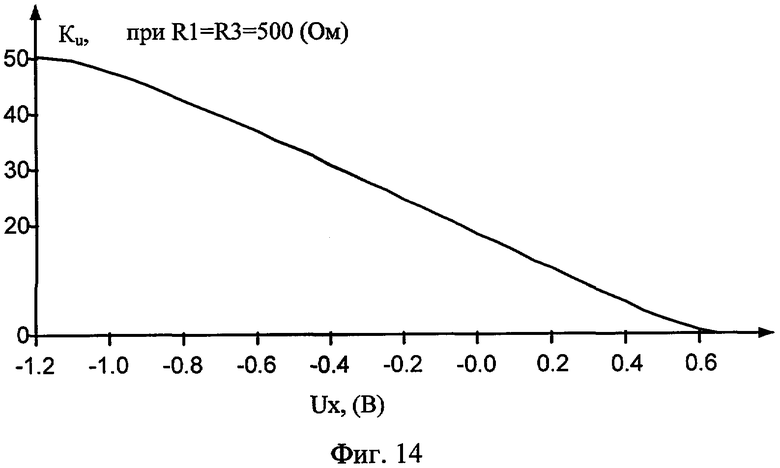

На фиг.12 - фиг.14 показаны результаты компьютерного моделирования схемы фиг.11:

- зависимость коэффициентов усиления Ku от напряжения управления Uy (в диапазоне частот фиг.12);

- зависимость коэффициентов усиления Ku от напряжения управления Uy при сопротивлении резистора R3=100 Ом (фиг.13);

- зависимость коэффициентов усиления Ku от напряжения управления Uy при сопротивлении резистора R3=500 Ом (фиг.14).

Дифференциальный усилитель фиг.2 содержит первый 1 дифференциальный каскад, имеющий первый 2 и второй 3 потенциальные входы, токовый выход 4, связанный с первым 5 входом выходного сумматора токов 6, первый 7 источник опорного тока, соединенный с общей эмиттерной цепью 8 первого 1 дифференциального каскада, второй дифференциальный каскад 9, имеющий первый 10 и второй 11 потенциальные входы, связанные с соответствующими первым 2 и вторым 3 потенциальными входами первого дифференциального каскада 1 и первым 12 и вторым 13 входами комплементарного дифференциального усилителя, а также токовый выход 14, связанный со вторым 15 входом выходного сумматора токов 6, второй 16 источник опорного тока, соединенный с общей эмиттерной цепью 17 второго дифференциального каскада 9. В схему введен первый дополнительный транзистор 18, эмиттер которого через первый дополнительный резистор 19 связан с общей эмиттерной цепью 17 второго 9 дифференциального каскада и первым дополнительным 20 источником опорного тока, база соединена с первым управляющим входом 21 комплементарного дифференциального усилителя, а коллектор связан с общей эмиттерной цепью 8 первого дифференциального каскада 1.

В схеме фиг.2 выходной сумматор токов 6 содержит выходные транзисторы 22 и 23 с объединенными коллекторами, эмиттеры которых подключены к токостабилизирующим двухполюсникам 24 и 25, а также связаны с источниками напряжения смещения 26 (+Ec1) и 27 (-Ес2). Коллекторы транзисторов 22 и 23 соединены с выходом 28 комплементарного дифференциального усилителя и элементом нагрузки 29. Первый 1 и второй 9 дифференциальные каскады в схеме фиг.2 выполнены на p-n-p транзисторах 30 и 31 и n-p-n транзисторах 32 и 33.

В схеме фиг.3, в соответствии с п.2 формулы изобретения, введен второй дополнительный транзистор 34, эмиттер которого через второй 35 дополнительный резистор связан с общей эмиттерной цепью 8 первого дифференциального каскада 1 и вторым 36 дополнительным источником опорного тока, база соединена со вторым 37 управляющим входом комплементарного дифференциального усилителя, а коллектор связан с общей эмиттерной цепью 17 второго дифференциального каскада 9.

В частном случае в схеме фиг.4 выходной сумматор тока 6 реализован на базе инвертирующих токовых зеркал 38 и 39, выходы которых связаны с выходом 28 комплементарного дифференциального усилителя.

Рассмотрим работу заявляемого устройства в режиме управляемого усилителя напряжения, подаваемого на вход 12 «X» (ux) (фиг.2). В статическом режиме при нулевом напряжении управления (uy=0) ток через резистор 19 близок к нулю.

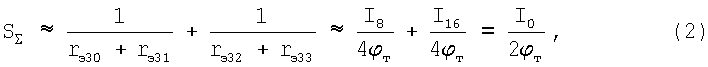

Коэффициент усиления по напряжению Ku для выхода 28 определяется формулой

где R29 - сопротивление резистора нагрузки 29;

S∑ - суммарная крутизна преобразования напряжения ux в выходной ток iвых.

Причем

где φт≈26 мВ - температурный потенциал;

I8, I16 - статистические токи эмиттерных цепей первого (1) второго (9) каскадов

(I8=I16=I0);

rэi=φт/Iэi - сопротивление эмиттерного перехода i-го транзистора схемы при статистическом токе эмиттера Iэi.

Таким образом, при uy - 0 для схемы фиг.2

Если управляющее напряжение Uy на первом управляющем входе 21 получает положительное  приращение, то это приводит к изменению тока

приращение, то это приводит к изменению тока

iR через резистор 19:

где R19 - сопротивление резистора 19 (R19>>rэ32=rэ33)

Этот ток вызывает уменьшение тока в общей эмиттерной цепи транзисторов 32, 33 и 30, 31 на величину iR, что приводит к уменьшению коэффициента усиления по напряжению со входа 12 («X») на выход 28:

При другой фазе напряжения uy коэффициент Ku увеличивается пропорционально величине Uy.

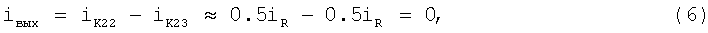

Замечательная особенность схемы фиг.2 - подавление передачи сигнала управления uy на выход 28, что весьма важно для построения смесителя сигналов. Действительно, ток в нагрузке 29

где iK22, iK23 коллекторные токи транзисторов 22 и 23.

Как следствие коэффициент подавления сигнала управления достаточно мал

Данный вывод подтверждается результатами компьютерного моделирования фиг.9 - фиг.10

Таким образом, ток в нагрузке 29 не зависит от сигнала управления Uy. Это является необходимым условием подавления сигнала по входу 21 (Uy)) в смесителях напряжений Ux и Uy.

Полученные выше аналитические соотношения подтверждаются результатами компьютерного моделирования предлагаемых схем КДУ (фиг.6, фиг.7, фиг.8, фиг.9, фиг.10 фиг.12, фиг.13, фиг.14).

Таким образом, заявляемый комплементарный дифференциальный усилитель имеет электронное управление коэффициентами усиления. Причем сигнал управления uy, как и входной сигнал Ux подаются на соответствующие входы относительно общей шины (без разделительных конденсаторов). Кроме этого, при использовании резисторов в качестве двухполюсников 7, 16, 24, 20, 25 схемы фиг.2 - фиг.4 могут иметь напряжение питания на уровне ±1,5 В, что позволяет рекомендовать их для использования в ВЧ- и СВЧ-интегральных схемах.

БИБЛИОГРАФИЧЕСКИЙ СПИСОК

1. - Патент США №3.786.362.

2. - Патент США №4.030.044.

3. - Патент США №4.059.808, фиг.5.

4. - Патент США №4.286.227.

5. - Авт.свид. СССР №375754, H03f 3/38.

6. - Авт.свид. СССР №843164, H03f 3/30.

7. - Патент США №3.660.773.

8. - Патент США №4.560.948.

9. - Патент РФ №2930041, H03f 1/32.

10. - Патент Японии №57-5364, H03f 3/343.

11. - Патент ЧССР №134845, кл. 21а2 18/08.

12. - Патент ЧССР №134849, кл. 21а2 18/08.

13. - Патент ЧССР №13 5326, кл. 21 а2 18/08.

14. - Патент США №4.389.579.

15. - Патент Англии №1543361, Н3Т.

16. - Патент США №5.521.552 (фиг.3а).

17. - Патент США №4.059.808.

18. - Патент США №5.789.949.

19. - Патент США №4.453.134.

20. - Патент США №4.760.286.

21. - Авт.свид. СССР№1283946.

22. - Патент РФ №2019019.

23. - Патент США №4.389.579.

24. - Патент США №4.453.092.

25. - Патент США №3.566.289.

26. - Патент США №4.059.808 (фиг.2).

27. - Патент США №3.649.926.

28. - Патент США №4.714.894 (фиг.1).

29. Матавкин В.В. Быстродействующие операционные усилители. - М.: Радио и связь, 1989.

30. М.Херпи. Аналоговые интегральные схемы. - М.: Радио и связь, 1983, стр.174, рис.5.52.

| название | год | авторы | номер документа |

|---|---|---|---|

| КОМПЛЕМЕНТАРНЫЙ ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ С УПРАВЛЯЕМЫМ УСИЛЕНИЕМ | 2008 |

|

RU2384937C1 |

| АНАЛОГОВЫЙ ПЕРЕМНОЖИТЕЛЬ НАПРЯЖЕНИЙ | 2008 |

|

RU2382483C1 |

| КОМПЛЕМЕНТАРНЫЙ КАСКОДНЫЙ ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ С УПРАВЛЯЕМЫМ УСИЛЕНИЕМ | 2008 |

|

RU2388137C1 |

| УПРАВЛЯЕМЫЙ ДВУХКАСКАДНЫЙ ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ С ОТРИЦАТЕЛЬНОЙ ОБРАТНОЙ СВЯЗЬЮ ПО СИНФАЗНОМУ СИГНАЛУ | 2008 |

|

RU2384936C1 |

| КАСКОДНЫЙ ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ С УПРАВЛЯЕМЫМ УСИЛЕНИЕМ | 2008 |

|

RU2388139C1 |

| КАСКОДНЫЙ ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ С УПРАВЛЯЕМЫМ УСИЛЕНИЕМ | 2008 |

|

RU2389130C1 |

| КОМПЛЕМЕНТАРНЫЙ КАСКОДНЫЙ ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ | 2009 |

|

RU2393629C1 |

| ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ С УПРАВЛЯЕМЫМ КОЭФФИЦИЕНТОМ УСИЛЕНИЯ | 2008 |

|

RU2384935C1 |

| ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ С МАЛЫМ НАПРЯЖЕНИЕМ СМЕЩЕНИЯ НУЛЯ | 2007 |

|

RU2331966C1 |

| КОМПЛЕМЕНТАРНЫЙ ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ | 2006 |

|

RU2319295C1 |

Изобретение относится к области радиотехники и связи и может быть использовано в устройствах автоматической регулировки усиления, фазовых детекторах и модуляторах, в системах фазовой автоподстройки и умножения частоты или в качестве усилителя, коэффициент передачи по напряжению которого зависит от уровня сигнала управления. Управляемый усилитель является базовым узлом современных систем приема и обработки сигналов ВЧ и СВЧ-диапазонов, аналоговой вычислительной и измерительной техники. Комплементарный дифференциальный усилитель (КДУ) содержит первый (1) дифференциальный каскад (ДК), имеющий первый (2) и второй (3) потенциальные входы, токовый выход (4), связанный с первым (5) входом выходного сумматора токов (6), первый (7) источник опорного тока (ИОТ), соединенный с общей эмиттерной цепью (8) первого (1) ДК, второй ДК (9), имеющий первый (10) и второй (11) потенциальные входы, связанные с соответствующими первым (2) и вторым (3) потенциальными входами первого ДК (1) и первым (12) и вторым (13) входами КДУ, а также токовый выход (14), связанный со вторым (15) входом выходного сумматора токов (6), второй (16) ИОТ, соединенный с общей эмиттерной цепью (17) второго ДК (9). В схему введен первый дополнительный транзистор (Т) (18), эмиттер которого через первый дополнительный резистор (19) связан с общей эмиттерной цепью (17) второго ДК (9) и первым дополнительным (20) ИОТ, база - соединена с первым управляющим входом (21) КДУ, а коллектор связан с общей эмиттерной цепью (8) первого ДК (1). 1 з.п. ф-лы, 14 ил.

1. Комплементарный дифференциальный усилитель с управляемым усилением, содержащий первый (1) дифференциальный каскад, имеющий первый (2) и второй (3) потенциальные входы, токовый выход (4), связанный с первым (5) входом выходного сумматора токов (6), первый (7) источник опорного тока, соединенный с общей эмиттерной цепью (8) первого (1) дифференциального каскада, второй дифференциальный каскад (9), имеющий первый (10) и второй (11) потенциальные входы, связанные с соответствующими первым (2) и вторым (3) потенциальными входами первого дифференциального каскада (1) и первым (12) и вторым (13) входами комплементарного дифференциального усилителя, а также токовый выход (14), связанный со вторым (15) входом выходного сумматора токов (6), второй (16) источник опорного тока, соединенный с общей эмиттерной цепью (17) второго дифференциального каскада (9), отличающийся тем, что в схему введен первый дополнительный транзистор (18), эмиттер которого через первый дополнительный резистор (19) связан с общей эмиттерной цепью (17) второго (9) дифференциального каскада и первым дополнительным (20) источником опорного тока, база соединена с первым управляющим входом (21) комплементарного дифференциального усилителя, а коллектор связан с общей эмиттерной цепью (8) первого дифференциального каскада (1).

2. Устройство по п.1, отличающееся тем, что в схему введен второй дополнительный транзистор (34), эмиттер которого через второй (35) дополнительный резистор связан с общей эмиттерной цепью (8) первого дифференциального каскада (1) и вторым (36) дополнительным источником опорного тока, база соединена со вторым (37) управляющим входом комплементарного дифференциального усилителя, а коллектор связан с общей эмиттерной цепью (17) второго дифференциального каскада (9).

| US 4600893 A, 15.07.1986 | |||

| US 4286226, 25.08.1981 | |||

| Дифференциальный усилитель с регулируемым коэффициентом усиления | 1990 |

|

SU1748227A1 |

| US 4621238 A, 04.11.1986 | |||

| ЛИНЕЙНЫЙ ЭЛЕКТРОДВИГАТЕЛЬ | 1995 |

|

RU2108651C1 |

Авторы

Даты

2010-03-20—Публикация

2008-08-20—Подача