Предлагаемое изобретение относится к области радиотехники и связи и может быть использовано в устройствах автоматической регулировки усиления, фазовых детекторах и модуляторах, в системах фазовой автоподстройки и умножения частоты или в качестве усилителя, коэффициент передачи по напряжению которого зависит от уровня сигнала управления. Управляемый усилитель и аналоговый перемножитель являются базовыми узлами современных систем приема и обработки сигналов ВЧ и СВЧ-диапазонов аналоговой вычислительной и измерительной техники.

В настоящее время в аналоговой микросхемотехнике в составе управляемых усилителей, систем электронной регулировки усиления, смешения или перемножения широкое применение находят схемы на основе дифференциальных каскадов с изменяющимся статическим режимом. Такая структура стала основой построения практически всех известных в настоящее время прецизионных управляемых усилителей и аналоговых перемножителей сигналов. В этой связи задача улучшения параметров этого функционального узла относится к числу достаточно актуальных задач современной микроэлектроники.

В цифровых интегральных микросхемах результатом увеличения скорости обработки информации стали тенденции постоянного уменьшения напряжения питания, что является «анафемой» в аналоговом проектировании с высокими характеристиками. При технологических нормах 350 нм (напряжение питания 3.3 В) по-прежнему достаточно схемотехнических возможностей для аналоговых проектирований с высокими характеристиками, хотя наличие 5 В питания было бы предпочтительнее. При нормах 180 нм (1.8 В) процесс усложняется и статические характеристики аналоговых устройств страдают. При 90÷130 нм технологии необходимо развитие новых подходов к проектированию микросхем, ориентированных на обеспечение работоспособности при низковольтном питании (Еп=1,2÷1,5 В).

Таким образом, последние несколько лет источники питания с напряжением 5 В вытесняются более низковольтными. Требования к уменьшению рассеиваемой мощности и уменьшению числа батарей в таких приложениях, как беспроводные устройства связи и персональные компьютеры, привели к снижению напряжения питания в цифровых схемах до уровня 1,5 В. Эта тенденция, как отмечалось выше, реализована в современных SiGe транзисторах, которые сконструированы так, чтобы обеспечить максимальную частоту среза (f1) в компромиссе с напряжением пробоя

(Uпp). Для кремниевых транзисторов существует следующее фундаментальное ограничение: f1×Uпp≈const, т.е. малые размеры транзисторов, обеспечивающие высокие значения f1 (до 200 ГГц), привели к снижению напряжения питания микросхем до 1,2÷1,5 В.

Уменьшение напряжения питания (Еп) в биполярных схемах приводит к появлению новых проблем и некоторые из них становятся особенно важными при напряжении питания менее 2 В. Принципиальная сложность уменьшения напряжения Еп состоит в том, что биполярный транзистор имеет фиксированное напряжение база - эмиттер Uбэ, которое не уменьшается линейно с уменьшением технологических норм, так как

,

,

где φт=kT/q, Iк - ток коллектора и Is - обратный ток эмиттерного р-n-перехода. При этом параметры транзистора и уровни тока оказывают слабое влияние на напряжение Uбэ. На практике плотность тока в биполярном транзисторе (Iк/Is), изменяя свое значение, также слабо влияет на напряжение Uбэ. Если в используемой технологии Uбэ≈0,7 В, то использование 1,5 В источника питания приводит к тому, что между «землей» и шиной Еп не может быть включено больше, чем один р-n-переход.

Учитывая вышесказанное, а также численные значения напряжения Uбэ≈700 мВ, можно сделать вывод о том, что при напряжении питания 1,5 В запрещается использовать многоярусные дифференциальные пары или каскадные конфигурации (архитектуры) на однотипных транзисторах.

Таким образом, отсутствие возможности масштабирования напряжения на переходе база - эмиттер обостряет проблему дальнейшего масштабирования напряжения питания схем на биполярных транзисторах.

Известны схемы комплементарных дифференциальных усилителей (КДУ), реализованных на основе двух параллельно-включенных дифференциальных каскадов (ДК) с источниками опорного тока в эмиттерных цепях входных транзисторов (так называемые dual input stage) [1-20]. По такой архитектуре, на модификации которой выдано более 50 патентов различных стран, выполнены микросхемы ведущих микроэлектронных фирм (НА5190, НА2539 и др. [16, 18]). Все варианты построения дифференциальных усилителей «dual input stage» можно разбить на два больших класса. В усилителях первого класса передача сигнала от параллельно включенных по входу дифференциальных каскадов на выход осуществляется через сумматоры выходных токов, реализованные в виде двух токовых зеркал [1-13]. В усилителях второго класса сигнал от входных дифференциальных каскадов передается на выход дифференциального усилителя через сумматор выходных токов, реализованный в виде транзисторных каскадов по схеме с общей базой [14-20].

Ближайшим прототипом (фиг.1) заявляемого устройства является дифференциальный усилитель, описанный в патенте США №5.294.893, содержащий первый дифференциальный каскад на первом 1 и втором 2 входных n-р-n транзисторах, эмиттеры которых соединены с первым токовым входом 3 первого дифференциального каскада и первым 4 источником опорного тока, а коллекторы связаны с первым 5 и вторым 6 токовыми выходами первого дифференциального каскада, второй дифференциальный каскад на первом 7 и втором 8 р-n-р входных транзисторов, эмиттеры которых соединены со вторым токовым входом 9 второго дифференциального каскада и вторым 10 источником опорного тока, а коллекторы связаны с первым 11 и вторым 12 токовыми выходами второго дифференциального каскада, первый 13 и второй 14 входы дифференциального усилителя, соединенные с соответствующими базами первого 1 n-p-n и первого 7 р-n-р входных транзисторов и второго 2 n-р-n и второго 8 р-n-р входных транзисторов, сумматор выходных токов 15 с первым 16 и вторым 17 входами, согласованными с шиной положительного источника питания 18, а также с первым 19 и вторым 20 входами, согласованными с шиной отрицательного источника питания 21.

Существенный недостаток известного КДУ состоит в том, что он не имеет специального входа «У» для электронного управления коэффициентом усиления по напряжению. Это существенно сужает область его использования, не позволяет реализовывать на его основе адаптивные функциональные узлы систем на кристалле, например СВЧ-операционные усилители с парафазным выходом, у которых петлевое усиление изменяется по заданному алгоритму в зависимости от свойств источников сигнала и цепей обратных связей (см., например, патент РФ №2307393 «Способ управления коэффициентом передачи решающего усилителя с глубокой отрицательной обратной связью»).

Основная цель предлагаемого изобретения состоит в создании условий для электронного управления коэффициентом усиления по напряжению КДУ. Реализация этой цели позволяет выполнять на базе заявляемого устройства не только широкополосные ВЧ- и СВЧ-усилители с регулируемыми параметрами, но создавать на его основе более сложные функциональные узлы, например аналоговые перемножители сигналов.

Первая дополнительная цель - создание архитектуры КДУ с малым напряжением питания и электронным управлением его коэффициента усиления по напряжению, а также обеспечение возможности практической реализации устройств по технологии SG25H2 (Up=1,9 В; Uп=2,8 В).

Дополнительная цель - реализация на базе известного КДУ функции аналогового смесителя и/или аналогового перемножителя двух напряжений.

Поставленные цели достигаются тем, что в комплементарном дифференциальном усилителе, фиг.2, содержащем первый дифференциальный каскад на первом 1 и втором 2 входных n-р-n транзисторах, эмиттеры которых соединены с первым токовым входом 3 первого дифференциального каскада и первым 4 источником опорного тока, а коллекторы связаны с первым 5 и вторым 6 токовыми выходами первого дифференциального каскада, второй дифференциальный каскад на первом 7 и втором 8 р-n-р входных транзисторов, эмиттеры которых соединены со вторым токовым входом 9 второго дифференциального каскада и вторым 10 источником опорного тока, а коллекторы связаны с первым 11 и вторым 12 токовыми выходами второго дифференциального каскада, первый 13 и второй 14 входы дифференциального усилителя, соединенные с соответствующими базами первого 1 n-p-n и первого 7 р-n-р входных транзисторов и второго 2 n-р-n и второго 8 р-n-р входных транзисторов, сумматор выходных токов 15 с первым 16 и вторым 17 входами, согласованными с шиной положительного источника питания 18, а также с первым 19 и вторым 20 входами, согласованными с шиной отрицательного источника питания 21, предусмотрены новые элементы и связи - в схему введены первый 22 n-p-n и второй 23 р-n-р дополнительные транзисторы, базы которых соединены с цепью управления коэффициентом усиления 24, эмиттер первого 22 n-p-n дополнительного транзистора соединен с первым 25 дополнительным источником опорного тока и через первый 26 вспомогательный резистор связан с первым 3 токовым входом первого дифференциального каскада на n-p-n входных транзисторах, эмиттер второго 23 р-n-р дополнительного транзистора соединен со вторым 27 дополнительным источником опорного тока и через второй 28 вспомогательный резистор связан со вторым 9 токовым входом второго дифференциального каскада на р-n-р входных транзисторах, причем первый токовый выход 5 первого дифференциального каскада связан с первым входом 16 сумматора выходных токов 15, согласованного с шиной положительного источника питания 18, второй токовый выход 6 первого дифференциального каскада связан со вторым входом 17 сумматора выходных токов 15, согласованного с шиной положительного источника питания 18, первый токовый выход 11 второго дифференциального каскада связан со вторым входом 20 сумматора выходных токов 15, согласованного с шиной отрицательного источника питания 21, а второй токовый выход 12 второго дифференциального каскада связан с первым входом 19 сумматора, выходных токов 15, согласованного с шиной отрицательного источника питания 21.

Цепь управления коэффициентом усиления 24 в схеме, фиг.2, может иметь две модификации - дифференциальный или недифференциальный вход. При дифференциальном входе необходимо иметь два идентичных противофазных сигнала управления ±uy, а при недифференциальном - только одно напряжение uy, изменяющееся относительно общей шины.

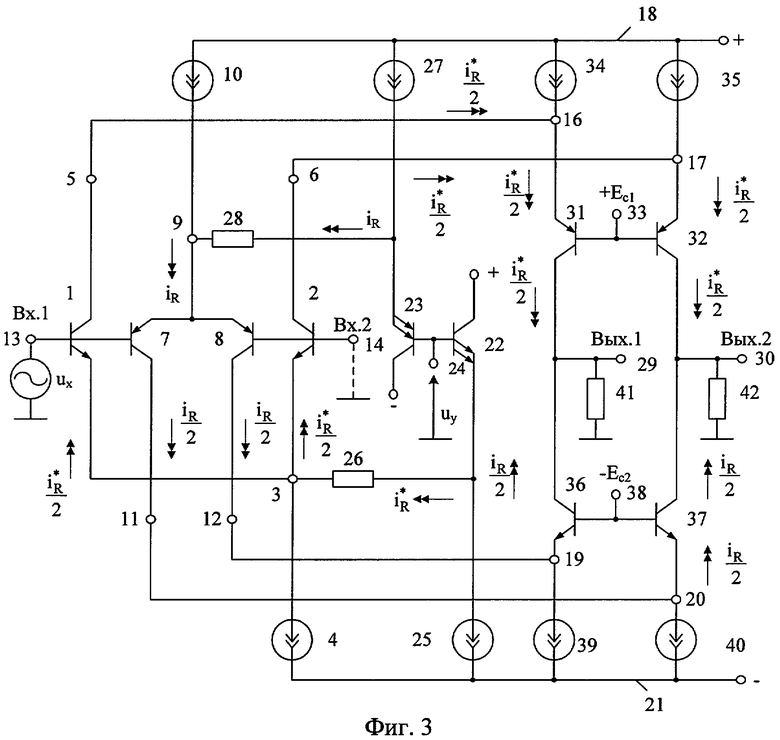

В частном случае сумматор выходных токов 15 реализован в КДУ, фиг.3, на вспомогательных р-n-р транзисторах 31 и 32, базы которых подключены к источнику напряжения смещения 33, а эмиттеры связаны с шиной положительного источника питания 18 через токостабилизирующие двухполюсники 34 и 35, и вспомогательных n-р-n транзисторах 36 и 37, базы которых подключены к источнику напряжения смещения 38, а эмиттеры через токостабилизирующие двухполюсники 39, 40 связаны с шиной 21 отрицательного источника питания. В частном случае к выходам 29 и 30 сумматора 15 могут подключаться масштабирующие резисторы нагрузки 41 и 42.

Выполнение заявляемого устройства в соответствии фиг.3 (п.2 формулы изобретения) позволяет реализовать на его основе аналоговый перемножитель двух напряжений «ux» «uy» с дифференциальным выходом (29, 30), «привязанным» к общей шине источников питания (элементы нагрузки 41 и 42). Данное свойство схемы, фиг.3, - одно из ее существенных достоинств. В схеме, фиг.3, для управления коэффициентом усиления используется синфазная цепь управления 24, обеспечивающая подачу на базы транзисторов 22 и 23 одинакового (синфазного) сигнала uy.

На фиг.4, соответствующей п.3 формулы изобретения, показана схема управляемого усилителя напряжения ux с дифференциальным выходом 29 и 30. В отличие от схемы, фиг.3, здесь используется другой вариант подключения выходов 5 и 6 (11 и 12) ко входам 16, 17 (19 и 20) сумматора выходных сигналов 15 (п.3). Кроме этого цепь управления коэффициентом усиления 24 реализована здесь по дифференциальной схеме, когда на входы «Bx.y1» и «Вх.у2» подаются одинаковые по амплитуде, но противофазные сигналы uy. В схеме, фиг.4, сумматор выходных токов 15 имеет первый 29 и второй 30 выходы, причем относительно первого выхода 29 его первый вход 16, согласованный с шиной положительного источника питания 18, и его второй вход 20, согласованный с шиной отрицательного источника питания 21 - синфазны, а относительно второго выхода 30 синфазны его второй вход 17, согласованный с шиной положительного источника питания 18, и его первый вход 19, согласованный с шиной отрицательного источника питания 21.

В частном случае сумматор выходных токов 15 реализован в схеме фиг.4 на транзисторах 43÷46, токостабилизирующих двухполюсниках 47÷50 и источниках напряжения смещения 51÷52 (+Ecl, -Ec2).

В схеме фиг.5, соответствующей п.4 формулы изобретения, сумматор выходных токов 15 имеет первый 29 выход, относительно которого его первый вход 16, согласованный с шиной положительного источника питания 18, и его первый вход 19, согласованный с шиной отрицательного источника питания 21, - синфазны, причем параллельно эмиттерно-базовому переходу первого 22 n-p-n и второго 23 р-n-р дополнительных транзисторов включены эмиттерно-базовые переходы первого 53 n-p-n и второго 54 р-n-р вспомогательных транзисторов, коллектор первого 53 n-p-n вспомогательного транзистора соединен с первым 16 входом сумматора выходных токов 15, а коллектор второго 54 р-n-р вспомогательного транзистора соединен с первым 19 входом сумматора выходных токов 15. При этом в схеме используется синфазная цепь управления коэффициентом усиления 24.

В частном случае сумматор выходных токов 15 реализован на фиг.5 на транзисторах 55 и 56, двухполюсниках 57 и 58, а также источниках напряжения смещения 59 (+Ec1) и 60 (-Еc2).

Реализация заявляемого устройства в соответствии с фиг.5 (п.4 формулы изобретения) позволяет выполнить на его основе смесители двух сигналов или перемножители напряжений ux и uy с одним выходом 29, «привязанным» к общей шине источников питания и синфазным построением цепи управления коэффициентом усиления 24.

Схема, фиг.6, соответствующая п.5 формулы изобретения, представляет собой управляемый усилитель сигнала ux с одним выходом 29, в котором используется дифференциальная цепь управления коэффициентом усиления 24, когда на базы транзисторов 22 и 23 подаются противофазные напряжения ±uy. В этой схеме сумматор выходных токов 15 имеет первый 29 выход, причем относительно первого выхода 29 его первый вход 16, согласованный с шиной положительного источника питания 18, и его второй вход 20, согласованный с шиной отрицательного источника питания 21, - синфазны. При этом в схеме используется дифференциальная цепь управления коэффициентом усиления 24.

В частном случае сумматор выходных токов 15 на фиг.6 выполнен на базе транзисторов 61 и 62, двухполюсников 63 и 64 и источников напряжения смещения 65 и 66.

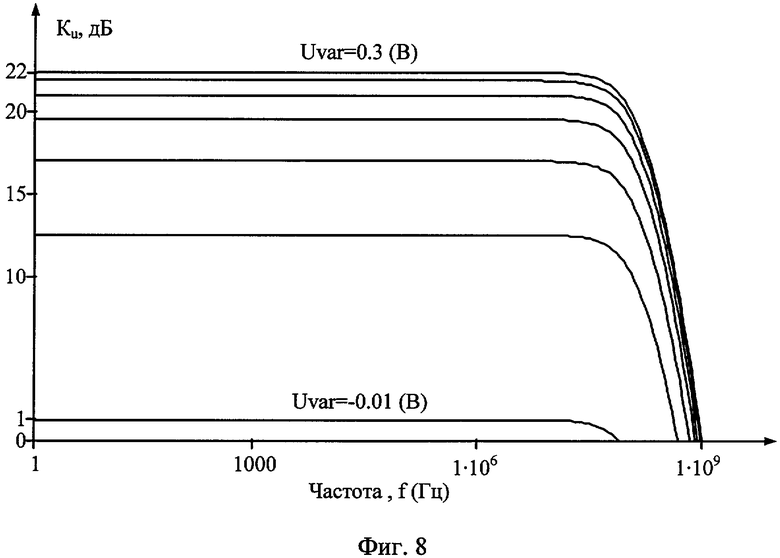

На фиг.7 показана схема КДУ, фиг.3, в среде компьютерного моделирования PSpice на транзисторах ФГУП «Пульсар».

На фиг.8 приведены результаты компьютерного моделирования схемы фиг.7 - зависимость коэффициента усиления по входу «X» (Ku) при управлении усилением по входу «У», а на фиг.9 - зависимость Ku схемы фиг.7 от напряжения управления uy=Uvar в логарифмическом масштабе.

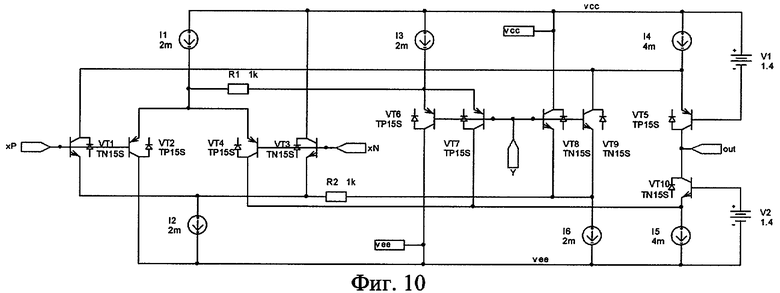

На фиг.10 показана схема перемножителя напряжений ux и uy, соответствующая фиг.5 в среде PSpice, а на фиг.11 - ее статические характеристики для входа «X» при управлении по входу «У».

Фиг.12 иллюстрирует статические характеристики КДУ, фиг.10, по входу «У» при управлении по входу «X».

Компьютерное моделирование предлагаемых схем фиг.11, фиг.12 подтверждает наличие в заявляемом устройстве эффекта перемножения двух напряжений при сравнительно низковольтном питании.

Зависимость коэффициента передачи по напряжению КДУ, фиг.10, по входу «X» и изменении управляющего напряжения по входу «У» (Uупр=-2В÷2В) приведена на фиг.13.

Рассмотрим вначале работу заявляемого устройства в режиме управляемого усилителя напряжения, подаваемого на вход «X» (ux) (фиг.4). В схеме фиг.4 используется синфазное соединение выходов 5 и 11, а также выходов 6 и 12 в сумматоре выходных токов на транзисторах 43-46.

В статическом режиме при uy=0 токи через резисторы 28 и 26 близки к нулю.

Коэффициент усиления по напряжению Ku для выхода 29 определяется формулой:

где R41 - сопротивление резистора нагрузки 41;

SΣ - суммарная крутизна преобразования ux в выходной ток iH.

Причем:

где φт≈26 мВ - температурный потенциал;

I4, I10 - токи двухполюсников 4 и 10 (I4=I10=I0);

rэi=φT/Iэi - сопротивление эмиттерного перехода i-го транзистора при токе эмиттера Iэi.

Таким образом, при uy=0 для схемы фиг.4:

Если управляющее напряжение на входе Bx.y1 получает положительное  , на входе Вх.у2 отрицательное

, на входе Вх.у2 отрицательное  приращение, то это приводит к изменению токов iR и

приращение, то это приводит к изменению токов iR и  чрез резисторы 28 и 26:

чрез резисторы 28 и 26:

Эти токи вызывают увеличение токов в общей эмиттерной цепи транзисторов 1 и 2, а также 7 и 8, что приводит к увеличению коэффициента усиления по напряжению со входа «X» на выход 29

где R=R26=R28.

При другой фазе напряжения uy коэффициент Ku уменьшается пропорционально Uy.

Замечательная особенность схемы фиг.4 - подавление передачи сигнала управления uy на выход 29 (30). Действительно, ток в нагрузке 41

Если выбрать R26=R28, то ток в нагрузке 41 не зависит от uy.

Рассмотрим далее работу перемножителя двух напряжений ux и uy с одним (недифференциальным) выходом 29 (фиг.5) на базе заявляемого устройства. В схеме фиг.5 используется противофазное соединение выходов 5 и 12.

В статическом режиме (uy=0) токи через резисторы 26 и 28 близки к нулю. На базы транзисторов 22 и 23 подается одинаковое напряжение управления uy. Если uy получает положительное приращение, то это создает в схеме токи iR,  , соответствующие формуле (4). Однако в отличие от схемы фиг.4 в схеме фиг.5 это приводит к уменьшению тока эмиттеров транзисторов 1 и 2 на величину

, соответствующие формуле (4). Однако в отличие от схемы фиг.4 в схеме фиг.5 это приводит к уменьшению тока эмиттеров транзисторов 1 и 2 на величину  и увеличению тока эмиттеров транзисторов 7 и 8 на величину

и увеличению тока эмиттеров транзисторов 7 и 8 на величину  . Вместе с противофазным включением выходов 5 и 12 относительно выхода АПМ 29 это является необходимым условием перемножения напряжений ux и uy (фиг.11, фиг.12). Для подавления в нагрузке 41 передачи сигнала управления в схеме фиг.5 используются транзисторы 53 и 54, которые «делят» токи

. Вместе с противофазным включением выходов 5 и 12 относительно выхода АПМ 29 это является необходимым условием перемножения напряжений ux и uy (фиг.11, фиг.12). Для подавления в нагрузке 41 передачи сигнала управления в схеме фиг.5 используются транзисторы 53 и 54, которые «делят» токи  и iR пополам и передают в противофазе соответствующие приращения на входы 16 и 19. В результате эмиттерные токи транзисторов 55 и 56 практически не зависят от сигнала управления uy:

и iR пополам и передают в противофазе соответствующие приращения на входы 16 и 19. В результате эмиттерные токи транзисторов 55 и 56 практически не зависят от сигнала управления uy:

Полученные выше аналитические соотношения подтверждаются результатами компьютерного моделирования предлагаемых схем КДУ (фиг.8, фиг.9, фиг.11, фиг.12, фиг.13).

Таким образом, заявляемый комплементарный дифференциальный усилитель имеет электронное управление коэффициентами усиления. Кроме этого, при использовании резисторов в качестве двухполюсников 4, 10, 25, 27, 47, 48, 49 и 50 схемы фиг.2 - фиг.6 могут иметь напряжение питания на уровне ±1,2÷1,5В, что позволяет рекомендовать их для использования в ВЧ и СВЧ интегральных микросхемах.

Источники информации

1. Патент США №5.291.149 (фиг.3)

2. А.св. СССР №611288, H03f 3/45

3. А.св. СССР №530425, H03f 3/45

4. Патент США №6.844.781

5. Патент США №3.968.451

6. Патент США №6.268.769 (фиг.3)

7. Патент США №5.515.005

8. Патент США №4.757.273

9. Патент США №4.636.743

10. Патент США №4.783.637

11. Патент США №3.974.455

12. Патент Франции №2.224.932

13. Патент Японии №53-25-232 (H03f, 3/26)

14. Патент США №5.291.149, фиг.1

15. Патент РФ №2.193.273, H03f 3/45

16. Справочник: операционные усилители и компараторы (Авербух В.Д.и др.). - М.: Изд-во «Додэка-XXI», 2001, С.122 (НА2539).

17. Патент США №4.600.893, фиг.3.

18. Матавкин В.В. Быстродействующие операционные усилители. - М.: Радио и связь, 1989, стр.103, рис.6. 11 (ОУ НА5190).

19. Патент США №4.837.522, фиг.1

20. Ежков Ю.С. Справочник по схемотехнике усилителей. - М., Радиософт, 2002, с.87, рис.5.21.

| название | год | авторы | номер документа |

|---|---|---|---|

| ДВУХТАКТНЫЙ КАСКОДНЫЙ ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ | 2006 |

|

RU2321161C1 |

| КОМПЛЕМЕНТАРНЫЙ ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ С УПРАВЛЯЕМЫМ УСИЛЕНИЕМ | 2008 |

|

RU2384938C1 |

| КОМПЛЕМЕНТАРНЫЙ КАСКОДНЫЙ ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ | 2009 |

|

RU2393629C1 |

| КАСКОДНЫЙ ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ | 2008 |

|

RU2374757C1 |

| КОМПЛЕМЕНТАРНЫЙ ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ | 2006 |

|

RU2320078C1 |

| ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ | 2005 |

|

RU2292632C1 |

| КАСКОДНЫЙ ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ | 2006 |

|

RU2319291C1 |

| ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ | 2005 |

|

RU2283533C1 |

| ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ | 2005 |

|

RU2292633C1 |

| КОМПЛЕМЕНТАРНЫЙ ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ | 2006 |

|

RU2319295C1 |

Изобретение относится к области радиотехники и связи и может быть использовано в устройствах автоматической регулировки усиления, фазовых детекторах и модуляторах, в системах фазовой автоподстройки и умножения частоты или в качестве усилителя, коэффициент передачи по напряжению которого зависит от уровня сигнала управления. Управляемый усилитель и аналоговый перемножитель являются базовыми узлами современных систем приема и обработки сигналов ВЧ и СВЧ-диапазонов, аналоговой вычислительной и измерительной техники. Технический результат: уменьшение напряжения питания и электронное управление коэффициентом усиления по напряжению. Комплементарный дифференциальный усилитель (КДУ) содержит первый дифференциальный каскад (ДК) с n-p-n транзисторами (1, 2), первым токовым входом (3), первым (4) источником опорного тока (ИОТ) и с первым (5) и вторым (6) токовыми выходами первого ДК, второй ДК на p-n-p Т (7, 8), с вторым токовым входом (9), вторым ИОТ (10), первым (11) и вторым (12) токовыми выходами второго ДК, первый (13) и второй (14) входы КДУ, соединены с соответствующими базами Т (1, 7) и базами Т (2, 8), сумматор выходных токов (15) с первым (16) и вторым (17) входами, согласованными с шиной положительного источника питания (ИП) (18), а также с первым (19) и вторым (20) входами, согласованными с шиной отрицательного ИП (21). В схему введены первый (22) n-p-n и второй (23) p-n-p дополнительные Т, базы которых соединены с цепью управления коэффициентом усиления (24), эмиттер Т (22) соединен с ИОТ (25) и через первый (26) вспомогательный резистор связан с токовым входом (3) первого ДК, эмиттер Т (23) соединен с ИОТ (27) и через второй (28) вспомогательный резистор связан с токовым входом (9) второго ДК, причем первый токовый выход (5) первого ДК связан с первым входом (16) сумматора выходных токов (15), второй токовый выход (6) первого ДК связан со вторым входом (17) сумматора выходных токов (15), первый токовый выход (11) второго ДК связан со вторым входом (20) сумматора выходных токов (15), а второй токовый выход (12) второго ДК связан с первым входом (19) сумматора выходных токов (15). 4 з.п. ф-лы, 13 ил.

1. Комплементарный дифференциальный усилитель с управляемым усилением, содержащий первый дифференциальный каскад на первом (1) и втором (2) входных n-p-n транзисторах, эмиттеры которых соединены с первым токовым входом (3) первого дифференциального каскада и первым (4) источником опорного тока, а коллекторы связаны с первым (5) и вторым (6) токовыми выходами первого дифференциального каскада, второй дифференциальный каскад на первом (7) и втором (8) p-n-p входных транзисторов, эмиттеры которых соединены со вторым токовым входом (9) второго дифференциального каскада и вторым (10) источником опорного тока, а коллекторы связаны с первым (11) и вторым (12) токовыми выходами второго дифференциального каскада, первый (13) и второй (14) входы дифференциального усилителя, соединенные с соответствующими базами первого (1) n-p-n и первого (7) p-n-p входных транзисторов и второго (2) n-p-n и второго (8) p-n-p входных транзисторов, сумматор выходных токов (15) с первым (16) и вторым (17) входами, согласованными с шиной положительного источника питания (18), а также с первым (19) и вторым (20) входами, согласованными с шиной отрицательного источника питания (21), отличающийся тем, что в схему введены первый (22) n-p-n и второй (23) p-n-p дополнительные транзисторы, базы которых соединены с цепью управления коэффициентом усиления (24), эмиттер первого (22) n-p-n дополнительного транзистора соединен с первым (25) дополнительным источником опорного тока и через первый (26) вспомогательный резистор связан с первым (3) токовым входом первого дифференциального каскада на n-p-n входных транзисторах, эмиттер второго (23) p-n-p дополнительного транзистора соединен со вторым (27) дополнительным источником опорного тока и через второй (28) вспомогательный резистор связан со вторым (9) токовым входом второго дифференциального каскада на p-n-p входных транзисторах, причем первый токовый выход (5) первого дифференциального каскада связан с первым входом (16) сумматора выходных токов (15), согласованного с шиной положительного источника питания (18), второй токовый выход (6) первого дифференциального каскада связан со вторым входом (17) сумматора выходных токов (15), согласованного с шиной положительного источника питания (18), первый токовый выход (11) второго дифференциального каскада связан со вторым входом (20) сумматора выходных токов (15), согласованного с шиной отрицательного источника питания (21), а второй токовый выход (12) второго дифференциального каскада связан с первым входом (19) сумматора выходных токов (15), согласованного с шиной отрицательного источника питания (21).

2. Устройство по п.1, отличающееся тем, что сумматор выходных токов (15) имеет первый (29) и второй (30) выходы, причем относительно первого выхода (29) его первый вход (16), согласованный с шиной положительного источника питания (18), и его первый вход (19), согласованный с шиной отрицательного источника питания (21) - синфазны, а относительно второго выхода (30) синфазны его второй вход (17), согласованный с шиной положительного источника питания (18), и его второй вход (20), согласованный с шиной отрицательного источника питания (21).

3. Устройство по п.1, отличающееся тем, что сумматор выходных токов (15) имеет первый (29) и второй (30) выходы, причем относительно первого выхода (29) его первый вход (16), согласованный с шиной положительного источника питания (18), и его второй вход (20), согласованный с шиной отрицательного источника питания (21) - синфазны, а относительно второго выхода (30) синфазны его второй вход (17), согласованный с шиной положительного источника питания (18), и его первый вход (19), согласованный с шиной отрицательного источника питания (21).

4. Устройство по п.1, отличающееся тем, что сумматор выходных токов (15) имеет первый (29) выход, относительно которого его первый вход (16), согласованный с шиной положительного источника питания (18), и его первый вход (19), согласованный с шиной отрицательного источника питания (21) - синфазны, причем параллельно эмиттерно-базовому переходу первого (22) n-p-n и второго (23) p-n-p дополнительных транзисторов включены эмиттерно-базовые переходы первого (53) n-p-n и второго (54) p-n-p вспомогательных транзисторов, коллектор первого (53) n-p-n вспомогательного транзистора соединен с первым (16) входом сумматора выходных токов (15), а коллектор второго (54) p-n-p вспомогательного транзистора соединен с первым (19) входом сумматора выходных токов (15), при этом в схеме используется синфазная цепь управления коэффициентом усиления (24).

5. Устройство по п.1, отличающееся тем, что сумматор выходных токов (15) имеет первый (29) выход, причем относительно первого выхода (29) его первый вход (16), согласованный с шиной положительного источника питания (18), и его второй вход (20), согласованный с шиной отрицательного источника питания (21) - синфазны, при этом в схеме используется дифференциальная цепь управления коэффициентом усиления (24).

| US 5294893 A, 15.03.1994 | |||

| US 4286226, 25.08.1981 | |||

| Дифференциальный усилитель с регулируемым коэффициентом усиления | 1990 |

|

SU1748227A1 |

| US 4621238 A, 04.11.1986 | |||

| ЛИНЕЙНЫЙ ЭЛЕКТРОДВИГАТЕЛЬ | 1995 |

|

RU2108651C1 |

Авторы

Даты

2010-03-20—Публикация

2008-08-12—Подача