Изобретение относится к импульсной технике и может быть использовано в телеметрии, системах автоматизированного управления, контроля, измерения и других устройствах различных отраслей техники.

Известна линия задержки, выбранная в качестве прототипа, содержащая D-триггер, управляемый посредством схем ИЛИ, ИЛИ-НЕ, а также генератор прямоугольных импульсов, двоичный счетчик импульсов и дешифратор (патент РФ №2103813 С1, МПК6 H03K 17/28).

Данное устройство позволяет сдвигать во времени выходной импульсный сигнал относительно входного и изменять после сдвига его длительность. Недостатком устройства являются ограниченные функциональные возможности, обусловленные недостаточной помехозащищенностью входного сигнала при использовании высокоскоростных микросхем (с малым временем переключения), фиксированным напряжением выходного сигнала, равным выходному напряжению выходов логических микросхем, и отсутствием возможности блокировки передачи импульсов с входа на выход.

Технический результат выражается в расширении функциональных возможностей устройства за счет обеспечения его помехозащищенности, возможности формирования выходного сигнала заданного напряжения, отличающегося от напряжения выходов логических микросхем, и возможности блокировки формирования выходных импульсов.

Для достижения технического результата формирователь импульсов, содержащий D-триггер, генератор прямоугольных импульсов, выход которого соединен с входом синхронизации двоичного счетчика импульсов, выходные разряды которого, кроме последнего, соединены с дешифратором, снабжен двумя сдвиговыми регистрами, двумя мажоритарными элементами, двумя D-триггерами, схемой управления транзисторными ключами, тремя транзисторными ключами и схемой И, причем выход генератора прямоугольных импульсов соединен с входами синхронизации первого и второго сдвиговых регистров, первого и третьего D-триггеров, а также с одним из входов схемы управления транзисторными ключами, первый информационный вход формирователя соединен с нулевым разрядом первого сдвигового регистра, выходы которого соединены с соответствующими входами первого мажоритарного элемента, выход которого подключен к входу первого D-триггера, выход которого соединен с входом синхронизации второго D-триггера, на другом входе которого установлен сигнал «1», выход второго D-триггера соединен с входом сброса двоичного счетчика, старший разряд двоичного счетчика соединен с входом сброса второго D-триггера, выход дешифратора соединен с первым входом схемы И, второй информационный вход формирователя соединен с нулевым разрядом второго сдвигового регистра, выходы которого соединены с соответствующими входами второго мажоритарного элемента, выход которого подключен к входу третьего D-триггера, инвертированный выход которого соединен со вторым входом схемы И, выход которой соединен со вторым входом схемы управления транзисторными ключами, первый выход которой соединен с первым выводом первого резистора, второй вывод которого соединен с базой первого транзистора, эмиттер которого соединен с общим проводом, а коллектор - с первым выводом второго резистора и базой второго транзистора, второй вывод второго резистора соединен с эмиттером второго транзистора и с плюсом опорного напряжения, второй выход схемы управления транзисторными ключами соединен с первым выводом третьего резистора, второй вывод которого соединен с базой третьего транзистора, эмиттер которого соединен с общим проводом, коллекторы второго и третьего транзисторов соединены между собой и с выходом формирователя.

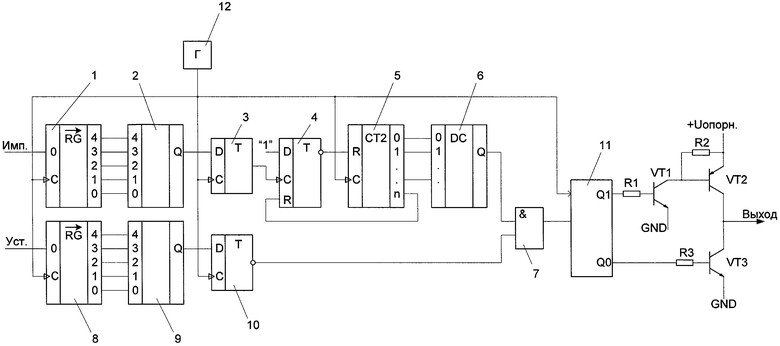

На чертеже представлена структурная схема формирователя импульсов.

Формирователь импульсов имеет два информационных входа: Имп. и Уст. Вход Имп. соединен с нулевым разрядом 5-разрядного сдвигового регистра 1. Сдвиг данных в этом регистре осуществляется от нулевого разряда к четвертому по фронту прямоугольных импульсов. Все пять разрядов сдвигового регистра 1 соединены с мажоритарным элементом 2. Элемент 2 передает на выход значение, соответствующее большинству входных данных. Выход мажоритарного элемента 2 соединен с входом D-триггера 3. Выход триггера 3 соединен с С-входом D-триггера 4, на входе которого присутствует постоянный единичный сигнал. Инвертированный выход триггера 4 соединен с входом сброса счетчика 5. Все разряды счетчика 5, за исключением старшего разряда, соединены с входами дешифратора 6. Старший разряд счетчика 5 соединен с входом сброса D-триггера 4. Выход дешифратора 6 соединен с первым входом схемы И 7.

Вход Уст. соединен с нулевым разрядом второго 5-и разрядного сдвигового регистра 8, аналогичного регистру 1. Все пять разрядов сдвигового регистра 8 соединены со вторым мажоритарным элементом 9. Выход мажоритарного элемента 9 соединен с входом D-триггера 10. Инвертирующий выход D-триггера 10 соединен со вторым входом схемы И 7. Выход схемы И 7 соединен с входом схемы управления транзисторными ключами 11, соединенной с генератором 12 импульсов. Прямоугольные импульсы с генератора 12 поступают на С-входы регистра 1, триггера 3, счетчика 5, регистра 8, триггера 10.

У схемы управления транзисторными ключами 11 два выхода: Q0 и Q1. Выход Q1 соединен с первым выводом резистора R1, второй вывод - с базой транзистора VT1. Эмиттер транзистора VT1 соединен с общим проводом, коллектор - первым выводом резистора R2 и базой транзистора VT2. Второй вывод резистора R2 соединен с эмиттером VT2 и плюсом источника опорного напряжения. Выход Q0 схемы управления транзисторными ключами 11 соединен с первым выводом резистора R3. Второй вывод резистора соединен с базой транзистора VT3. Эмиттер транзистора VT3 соединен с общим проводом. Коллекторы транзисторов VT2 и VT3 соединены между собой и с выходом формирователя.

Формирователь импульсов работает следующим образом.

В начальный момент времени триггеры 3, 4, 10 находятся в состоянии сброса. На выходе триггера 3 - «0», триггеров 4 и 10 - «1». Счетчик 5 - сброшен («обнулен»). Выходы Q0 и Q1 схемы управления транзисторными ключами 11 находятся в состоянии Q0=1, Q1=0. Транзисторы VT1 и VT2 заперты, VT3 - открыт, соединяя выход устройства с общим проводом.

Значение сигнала на входе Имп. непрерывно записывается в сдвиговый регистр 1 по фронту прямоугольных импульсов, поступающих на С-вход этого регистра 1 от генератора прямоугольных импульсов 12. Запись производится в 0-ой разряд, при этом значение из 0-го разряда записывается в 1-ый, из 1-го во 2-ой и т.д. (т.е. производится сдвиг значений разрядов). Пока на входе Имп. сигнал «0», все разряды сдвигового регистра 1 имеют значение «0», и на выходе мажоритарного элемента 2 тоже «0». При изменении сигнала на входе Имп. на «1», по фронту прямоугольного импульса от генератора 12 на входе С в 0-ой разряд будет записан «1». При длительности сигнала «1» на входе Имп. большей, чем три периода импульсов генератора 12, в сдвиговом регистре 1 минимум три разряда будут иметь значение, равное «1». Пока количество разрядов в сдвиговом регистре 1, имеющих значение «1», меньше или равно двум, на выходе Q мажоритарного элемента 2 состояние Q=0. Как только количество разрядов со значением «1» становится больше двух, состояние выхода изменяется на Q=1. Применение сдвиговых регистров 1 и 8, мажоритарных элементов 2 и 9 позволяет устройству игнорировать короткие импульсы помехи на информационном входе устройства, способные вызвать ложные срабатывания. Использование этих схем существенно повышает помехозащищенность формирователя. Сигнал «1» с выхода мажоритарного элемента 2 поступает на вход данных триггера 3, и по фронту прямоугольного импульса на С-входе этого триггера 3 сигнал «1» устанавливается на выходе триггера 1. Так как выход триггера 3 соединен с С-входом триггера 4, то при изменении сигнала на выходе триггера 3 с «0» на «1» сигнал на выходе триггера 4 устанавливается «0» (при обнуленном счетчике 5, все разряды которого при этом равны нулю, на вход сброса R триггера 4 поступает «0» с последнего разряда счетчика 5). Выход триггера 4 соединен с входом сброса R счетчика 5. После установления «0» на входе R счетчика 5 счетчик 5 начинает считать импульсы от генератора 12, приходящие на С-вход. Все разряды счетчика 5, за исключением старшего разряда, соединены с дешифратором 6. После формирования на входах дешифратора 6 двоичного кода, соответствующего первому заданному числу импульсов, на выходе дешифратора 6 устанавливается «1». После дешифрации числа импульсов, соответствующих второму числу, на выходе дешифратора 6 устанавливается «0». Далее счетчик 5 продолжает считать, пока на старшем разряде счетчика не установится «1». Этот сигнал со старшего разряда поступает на вход сброса R триггера 4. Триггер 4 сбрасывается, на его выходе устанавливается «1». Сигнал с выхода триггера 4 сбрасывает счетчик 5: все выходы счетчика обнуляются, сброс снимается с входа R триггера 4. Система приходит в состояние ожидания прихода следующего импульса на вход Имп. Сигнал с выхода дешифратора 6 поступает на первый вход схемы И 7, на второй вход которой поступает «1» с выхода триггера 10. Пока на втором входе схемы И 7 сигнал «1», сигнал на выходе схемы И соответствует сигналу на ее первом входе. Выход схемы И 7 соединен с входом схемы управления транзисторными ключами 11. Схема управления транзисторными ключами 11 предусмотрена для предотвращения одновременного открытия транзисторов VT2 и VT3 и короткого замыкания источника опорного напряжения на общий провод. Пока на входе схемы 11 сигнал «0», на выходах схемы Q1=0, Q0=1. После установки на входе схемы 11 сигнала «1» на выходе Q0 устанавливается Q0=0, а через интервал времени, равный одному периоду прямоугольных импульсов, поступающих в схему 11 от генератора 12, на выходе Q1 устанавливается Q1=1. При установке на входе схемы 11 снова значения «0» на выходе Q1 устанавливается Q1=0, а через интервал времени, равный одному периоду прямоугольных импульсов, на выходе Q0 устанавливается Q0=1. Интервал между установкой сигналов на выходах предусмотрен для выхода транзисторов из режима насыщения. Сигнал «1» с выхода Q1 схемы 11 через резистор R1 поступает на базу транзистора VT1, транзистор открывается, через переход эмиттер-коллектор начинает течь ток. При открытом транзисторе VT1 ток начинает течь через резистор R2. Напряжение на резисторе R2 открывает транзистор VT2, через переход эмиттер-коллектор которого +Uопорн. поступает на выход формирователя. Если на выходе Q1 схемы 11 «0», то транзисторы VT1 и VT2 закрыты, +Uопорн. на выход не поступает. Сигнал «1» с выхода Q0 схемы 11 через резистор R3 поступает на базу транзистора VT3, транзистор открывается, через переход эмиттер-коллектор выход устройства соединяется с общим проводом. Если на выходе Q0 схемы 11 «0, то транзистор VT3 закрыт, выход устройства с общим проводом не соединяется. Приведенная схема управления подачей напряжения на выход устройства позволяет использовать +Uопорн. любой заданной величины. Ограничение на величину напряжения накладывает тип транзисторов. Значение сигнала на входе Уст. непрерывно записывается в сдвиговый регистр 8 по фронту прямоугольных импульсов, поступающих на С-вход этого регистра (по типу, сдвиговый регистр 8 аналогичен сдвиговому регистру 1). Запись производится в 0-ой разряд, при этом значение из 0-го разряда сдвигается в 1-ый, из 1-го во 2-ой и т.д. При установке на входе Уст. сигнала «1» по фронту импульса на входе С в 0-ой разряд будет записан «1». При длительности сигнала, большей, чем три периода импульсов генератора 12, в сдвиговом регистре 8 минимум три разряда будут иметь значение, равное «1». Пока количество разрядов в сдвиговом регистре 8, имеющих значение «1» меньше или равно двум, на выходе Q мажоритарного элемента 9 состояние Q=0. Как только количество разрядов со значением «1» становится больше двух, состояние выхода изменяется на Q=1. Сигнал «1» с выхода мажоритарного элемента 9 поступает на вход данных триггера 10, и по фронту прямоугольного импульса на С-входе этого триггера на выходе триггера 10 устанавливается «0». Выход триггера 10 соединен со вторым входом схемы И 7, при подаче на этот вход сигнала «0» с триггера 10 на выходе схемы 7 устанавливается «0», блокируя изменение сигнала на выходе схемы И 7. Пока на входе Уст. удерживается «1», выход устройства соединен с общим проводом, импульсы на входе Имп. не влияют на состояние выхода устройства. Таким образом, установка сигнала «1» на входе Уст. позволяет блокировать формирование импульсов с входа Имп. на выход устройства.

Введение в состав формирователя импульсов сдвиговых регистров, триггеров, мажоритарных элементов, схемы И, а также транзисторных ключей на выходе устройства и схемы управления транзисторными ключами, соответствующим образом соединенных в единую электронную схему, повысило помехозащищенность формирователя, обеспечило возможность формирования выходного сигнала заданного напряжения, отличающегося от напряжения выходов логических микросхем, возможность блокировки формирования выходных импульсов и, как следствие, позволило расширить функциональные возможности формирователя импульсов.

Кроме того, D-триггеры, двоичный счетчик, дешифратор, сдвиговые регистры, мажоритарные элементы, схема И, схема управления транзисторными ключами могут быть реализованы на программируемой логической интегральной схеме ПЛИС типа ХС95144 или аналогичной, что позволит значительно уменьшить габариты устройства.

| название | год | авторы | номер документа |

|---|---|---|---|

| ИСТОЧНИК ПИТАНИЯ | 2011 |

|

RU2479100C1 |

| УСТРОЙСТВО ФОРМИРОВАНИЯ ИНТЕРВАЛОВ | 2011 |

|

RU2470458C1 |

| СИСТЕМА АВТОМАТИЧЕСКОГО УПРАВЛЕНИЯ | 2011 |

|

RU2494006C2 |

| Устройство для обработки информации датчиков | 1980 |

|

SU955093A1 |

| Импульсный стабилизатор постоянного напряжения | 1988 |

|

SU1571561A1 |

| МАГИСТРАЛЬНО-МОДУЛЬНАЯ ВЫЧИСЛИТЕЛЬНАЯ СИСТЕМА | 2013 |

|

RU2564626C2 |

| КОНТРОЛЛЕР ПЕРЕДАЧИ ДАННЫХ | 2013 |

|

RU2514135C1 |

| ВЫЧИСЛИТЕЛЬНАЯ СИСТЕМА | 2013 |

|

RU2536434C2 |

| МНОЖИТЕЛЬНО-ДЕЛИТЕЛЬНОЕ УСТРОЙСТВО | 2002 |

|

RU2210102C1 |

| СБОЕУСТОЙЧИВАЯ ВЫЧИСЛИТЕЛЬНАЯ СИСТЕМА | 2013 |

|

RU2541839C2 |

Изобретение относится к импульсной технике и может быть использовано в телеметрии, системах автоматизированного управления, контроля и измерения. Достигаемый технический результат - расширение функциональных возможностей формирователя импульсов за счет обеспечения его помехозащищенности, возможности формирования выходного сигнала заданного напряжения, возможности блокировки формирования выходных импульсов. Формирователь импульсов содержит D-триггеры, генератор прямоугольных импульсов, двоичный счетчик, дешифратор, сдвиговые регистры, мажоритарные элементы, схему И, а также транзисторные ключи на выходе устройства и схему управления транзисторными ключами, соответствующим образом соединенные в единую электронную схему. 1 ил.

Формирователь импульсов, содержащий D-триггер, генератор прямоугольных импульсов, выход которого соединен со входом синхронизации двоичного счетчика импульсов, выходные разряды которого, кроме последнего, соединены с дешифратором, отличающийся тем, что снабжен двумя сдвиговыми регистрами, двумя мажоритарными элементами, двумя D-триггерами, схемой управления транзисторными ключами, тремя транзисторными ключами и схемой И, причем выход генератора прямоугольных импульсов соединен со входами синхронизации первого и второго сдвиговых регистров, первого и третьего D-триггеров, а также с одним из входов схемы управления транзисторными ключами, первый информационный вход формирователя соединен с нулевым разрядом первого сдвигового регистра, выходы которого соединены с соответствующими входами первого мажоритарного элемента, выход которого подключен ко входу первого D-триггера, выход которого соединен со входом синхронизации второго D-триггера, на другом входе которого установлен сигнал «1», инвертированный выход второго D-триггера соединен с входом сброса двоичного счетчика, старший разряд двоичного счетчика соединен со входом сброса второго D-триггера, выход дешифратора соединен с первым входом схемы И, второй информационный вход формирователя соединен с нулевым разрядом второго сдвигового регистра, выходы которого соединены с соответствующими входами второго мажоритарного элемента, выход которого подключен ко входу третьего D-триггера, инвертированный выход которого соединен со вторым входом схемы И, выход которой соединен со вторым входом схемы управления транзисторными ключами, при этом в начальный момент времени на первом выходе схемы управления транзисторными ключами устанавливают сигнал логического нуля, а на втором выходе - сигнал логической единицы, после установки на втором входе схемы управления транзисторными ключами логической единицы, на ее втором выходе устанавливается логический ноль, а через интервал времени, равный одному периоду прямоугольных импульсов, поступающих от генератора прямоугольных импульсов на первый вход схемы управления транзисторными ключами, на ее первом выходе устанавливается логическая единица, при установке на втором входе схемы управления транзисторными ключами логического нуля, на ее первом выходе устанавливается логический ноль, а через интервал времени, равный одному периоду прямоугольных импульсов, на ее втором выходе устанавливается логическая единица, первый выход которой соединен с первым выводом первого резистора, второй вывод которого соединен с базой первого транзистора, эмиттер которого соединен с общим проводом, а коллектор - с первым выводом второго резистора и базой второго транзистора, второй вывод второго резистора соединен с эмиттером второго транзистора и с плюсом опорного напряжения, второй выход схемы управления транзисторными ключами соединен с первым выводом третьего резистора, второй вывод которого соединен с базой третьего транзистора, эмиттер которого соединен с общим проводом, коллекторы второго и третьего транзисторов соединены между собой и с выходом формирователя.

| ЛИНИЯ ЗАДЕРЖКИ | 1996 |

|

RU2103813C1 |

| RU 95104258 A1, 27.12.1996 | |||

| US 6466076 B2, 15.10.2002. | |||

Авторы

Даты

2011-06-27—Публикация

2009-08-04—Подача