Изобретение относится к вычислительной технике и может быть использовано при создании управляющих вычислительных машин (УВМ) или бортовых цифровых вычислительных систем (БЦВС), имеющих развитую сеть связей с периферийными подсистемами и работающих в составе систем автоматического управления (САУ) подвижными объектами и, в частности, объектами ракетно-космической техники, а также робототехническими комплексами, работающими в экстремальных условиях и в полях ионизирующего излучения, например, при ликвидации аварий типа Чернобыльской или тушении пожаров на объектах лесной, нефтяной и газодобывающих отраслей.

Пример БЦВС, входящей в состав таких САУ, может быть взят из патента RU №2450433 от 27.02. 2012, а пример периферийной подсистемы - из патента RU №2452125 от 27.05. 2012. Экстремальность условий обусловлена необходимостью работы в широком диапазоне изменения температуры окружающей среды (от -60 до +125 град по Цельсию) и механическими воздействиями в виде ударов и широкополосной вибрации.

Особенностью УВМ и БЦВС является необходимость обмена информацией (данными) как между модулями в самой системе, так и с большим количеством периферийных устройств и подсистем, в связи с чем в общем составе задач программно-математического обеспечения и потребляемых машинных ресурсов, программы обмена занимают значительную часть и стоит задача такой организации обменов, которая позволяет максимально высвободить машинные ресурсы (время процессоров и объемы памяти) для решения функциональных задач управления. Особенно остро эта задача стоит для БЦВС, входящих в состав САУ подвижными объектами, работающими в экстремальных условиях и полях электромагнитного и ионизирующих излучений космического пространства, атомных энергетических установок и загрязненной местности.

Менее остро задача оптимизации обмена стоит для электронных вычислительных машин общего назначения, в том числе ПЭВМ, работающих в нормальных условиях, но требования сокращения непроизводительных затрат процессорных ресурсов остаются актуальными и для них.

Известно «Устройство для сопряжения электронной вычислительной машины с терминалом» (См. AC №772408, G06F 13/00). Устройство содержит ряд согласующих элементов, обеспечивающих подключение процессора ЭВМ к терминалу. Обмен, т.е. ввод и вывод данных, производится по командам (операциям) обмена, выполняемым процессором. Для организации обмена в программу вводятся команды ввода и вывода, выполняемые в общей последовательности операций. Такое построение обмена упрощает программное обеспечение, облегчает отладку программ, но, к сожалению, потребляет значительные ресурсы машинного времени, так как в течение всего обмена процессор занят и не способен решать другие задачи, а время обмена, особенно при передаче данных последовательным кодом, может быть достаточно велико.

Известно решение, направленное на сокращение времени занятости процессора при обмене последовательным кодом (См. AC №490115 «Система для обмена данными управляющей вычислительной машины с периферийными устройствами»).

В этой известной системе дополнительно к процессору УВМ введен регистр обмена, подключенный выходом и входом соответственно к входу и выходу регистра периферийного устройства таким образом, что при сдвиге информации эти регистры образуют, по сути, единый сдвиговый регистр. В результате после выдачи (сдвига) информации из регистра обмена его содержимое оказывается в регистре периферийного устройства, а содержимое последнего вводится в регистр обмена УВМ. Кроме того, в состав системы входит блок микропрограммного управления (БМУ), обеспечивающий управление сдвигом информации синхронно в обоих регистрах, и блок выбора приоритета. Регистр обмена подключен к процессору шинами для передачи данных параллельным кодом.

После завершения сдвига по сигналу прерывания процессор считывает из регистра обмена принятое слово и записывает новое для следующего обмена.

Такое построение системы позволяет заметно сократить затраты машинного времени процессора, так как передача данных последовательным кодом производится без его участия. Кроме того, совмещение ввода с выводом позволят получить дополнительное сокращение времени обмена. Однако процессор занят обработкой прерываний, обменом с регистром обмена, что также расходует процессорное время, усложняет программы УВМ и затрудняет их отладку.

Кроме того, известная система не обеспечивает обмен большими массивами между модулями самой многомодульной или многомашинной БЦВС.

Наиболее полно задача освобождения процессора от непроизводительных затрат на прием и выдачу данных решена в известном устройстве для передачи данных (См. AC №64 2868, H04L 17/02, G06F 3/04 «Устройство для передачи данных»).

Это устройство может быть взято за ПРОТОТИП. Устройство содержит запоминающий блок (блок памяти), буферный накопитель (регистр), связанный с периферийным блоком, блок адреса, блок контроля и БМУ.

Важным достоинством устройства является наличие блока памяти, в который через буферный накопитель (буферный регистр) могут поступать данные от периферийного блока или, наоборот, данные из блока памяти через буферный накопитель (регистр) могут передаваться в периферийный блок. Такая организация обмена позволяет существенно освободить процессор от непроизводительных затрат на передачу данных. За процессором сохраняется задача выдачи команд в БМУ и кода адреса в блок задания адреса.

Однако в данном устройстве не обеспечивается возможность работы схем обмена непосредственно с блоком памяти процессора, а требуется опрос по программе процессором блока памяти, что требует соответствующих затрат процессорного времени, что ограничивает функциональные возможности УВМ. Кроме того, во всех известных решениях не обеспечивается сохранение работоспособности устройств при работе в экстремальных условиях в полях ионизирующего излучения.

Отсутствие возможности работы схем обмена непосредственно с блоком памяти процессора объясняется, видимо, сложностью обеспечения доступа к одному блоку двух устройств, а именно, процессора и схем обмена.

Целесообразно обеспечить работу с блоком памяти и процессору, и схемам обмена. Для рационального построения программ и повышения производительности процессор должен иметь возможность непрерывно работать с данными, размещенными в своем блоке памяти, а схемы обмена должны обеспечивать передачу данных между блоком памяти процессора и буферным накопителем (по сути, периферийным устройством), не влияя на выполнение функциональных программ процессором.

Решение задачи независимой работы с общим блоком памяти двух устройств не является тривиальным и требует совершенствования известного устройства для передачи данных. С целью расширения функциональных возможностей БЦВС и упрощения создания программно-математического обеспечения за счет обеспечения доступа схем обмена к блоку памяти, с которым работает процессор, а также для обеспечения работы системы в экстремальных условиях и, в том числе, при длительной работе в полях ионизирующего излучения предлагается КОНТРОЛЛЕР ПЕРЕДАЧИ ДАННЫХ. Далее по тексту просто контроллер.

Контроллер содержит буферный регистр и БМУ.

Дополнительно в контроллер введены таймер и перестраиваемый формирователь синхроимпульсов (ФСИ), обеспечивающий синхроимпульсами узлы и блоки контроллера и процессора.

Кроме того, в контроллер введен перестраиваемый источник вторичного электропитания (ИВЭП), также общий для узлов контроллера и процессора.

Установочный выход процессора подключен к установочным входам БМУ, ФСИ и ИВЭП.

Первой двунаправленной связью процессор соединен с запоминающим устройством, второй - с буферным регистром, третьей - с таймером.

БМУ содержит в своем составе запоминающее устройство микропрограмм (ЗУМП), регистр кода операции, регистр признаков, счетчик адреса и регистр смещения, установочный вход которых является установочным входом блока и подключен к установочному выходу процессора. Выходы признаков процессора подключены к одноименным входам БМУ (его регистра признаков), а вход регистра смещения подключен к адресному выходу ЗУМП. Выходы всех регистров и счетчика адреса образуют адресную шину, подключенную к адресному входу ЗУМП, выходы которого подключены к входам выходных триггеров. Выходы этих триггеров являются выходами микрокоманд блока.

ФСИ содержит три генератора импульсов, три соответствующих им блока фазирования и блок мажоритации. Выход каждого из генераторов первого, второго и третьего подключен соответственно к входу своего, соответственно первого, второго и третьего блоков фазирования, фазирующий выход каждого из которых подключен к фазирующим входам двух других блоков фазирования. Выходы блоков фазирования подключены к входам блока мажоритации, выходы которого являются выходом формирователя.

Генератор импульсов содержит последовательно соединенные инверторы, первый мультиплексор, первый счетчик кода частоты, первый счетчик частоты, первый регистр кода частоты и первую схему сравнения.

Выходы инверторов подключены к входам первого мультиплексора, выход которого является выходом генератора и соединен с входом первого инвертора и входом первого счетчика частоты, выходы которого подключены к первым входам первой схемы сравнения. Вторые входы этой схемы подключены к выходам первого регистра кода частоты. Инкрементный и декрементный выходы первой схемы сравнения подключены к одноименным входам первого счетчика кода частоты, выходы которого подключены к управляющим входам первого мультиплексора. При этом, установочные входы первого регистра кода частоты и первого счетчика кода частоты являются установочным входом генератора.

Блок фазирования ФСИ содержит логический элемент, динамический счетчик, сдвиговый регистр, дешифратор, триггер останова, триггер пуска, триггеры привязки, мажоритарный элемент, схему «И» и выходные формирователи.

Первый вход логического элемента является входом блока, а выход элемента подключен к входам сдвигового регистра и динамического счетчика, выход которого через дешифратор подключен к запускающему входу триггера останова, выход которого является фазирующим выходом блока и подключен ко второму входу логического элемента и первому входу мажоритарного элемента, выход которого подключен к первому вход схемы «И», второй вход которой является входом блока, а выход схемы подключен к входу триггера пуска, выход которого подключен к сбрасывающему входу триггера останова. Ко второму и к третьему входам мажоритарного элемента подключены выходы триггеров привязки, входы которых являются фазирующими входами блока. При этом выходы нечетных и четных разрядов сдвигового регистра подключены соответственно к запускающим и к сбрасывающим входам выходных формирователей, выходы которых являются синхронизирующими выходами блока.

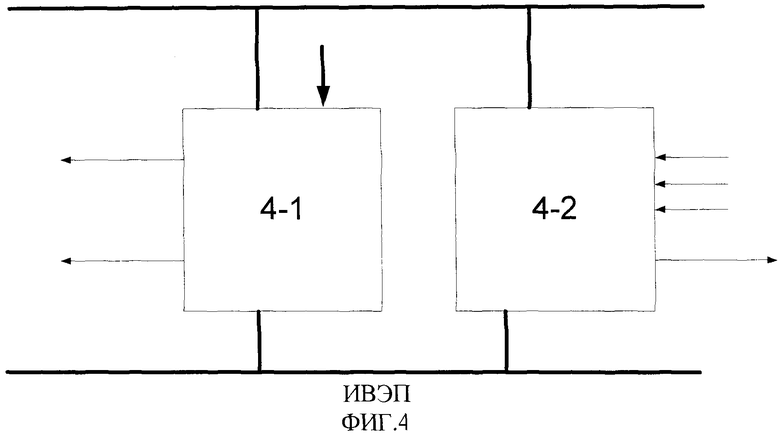

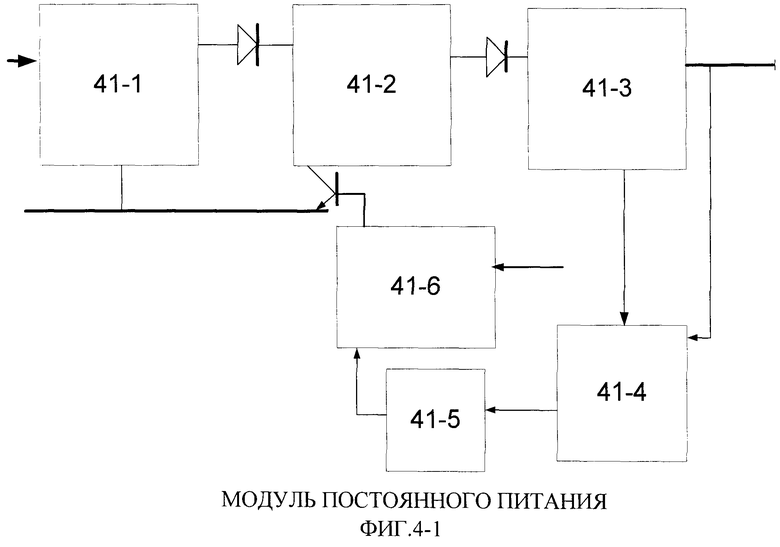

ИВЭП содержит модуль постоянного питания (МПП) и модуль импульсного питания (МИП).

МПП содержит последовательно включенные фильтр, вход которого является силовым входом модуля, защитный диод, трансформатор с включенным в первичную обмотку транзистором-прерывателем, выпрямительный диод и фильтр нижних частот, выход которого является выходом модуля и подключен к блоку преобразования напряжения в частоту, подключенному выходом через блок гальванической развязки к блоку управления, установочный вход которого является одноименным входом МПП и источника, подключенным к установочному выходу процессора, а выход блока управления подключен к базе транзистора прерывателя.

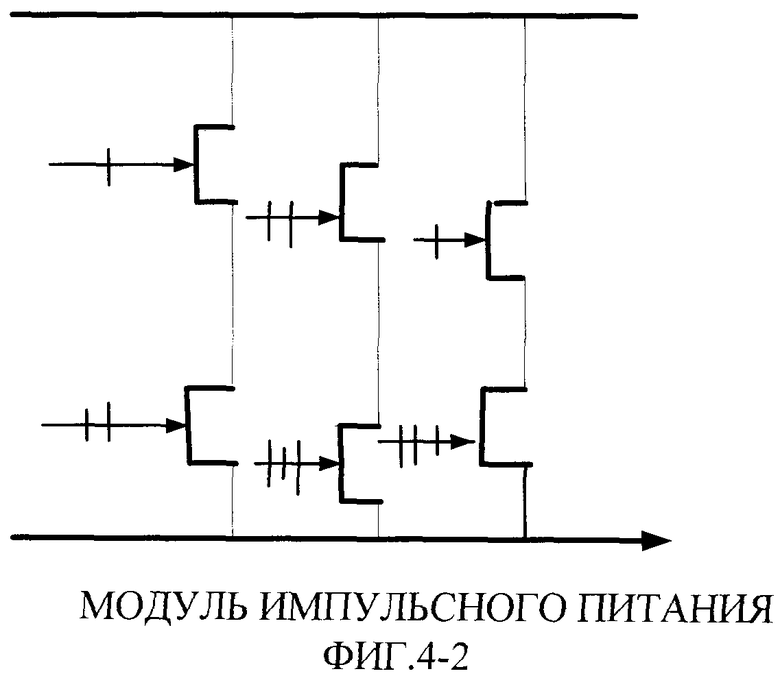

МИП содержит три идентичных цепи, каждая из которых содержит два последовательно включенных полевых транзистора. Цепи объединены с каждой стороны. Одна из сторон является силовым входом модуля, а вторая - выходом. При этом, три входных управляющих сигнала разведены таким образом, что каждый из них подключен к затворам двух транзисторов, установленных в разных цепях, образуя на транзисторах выборку «2 из 3».

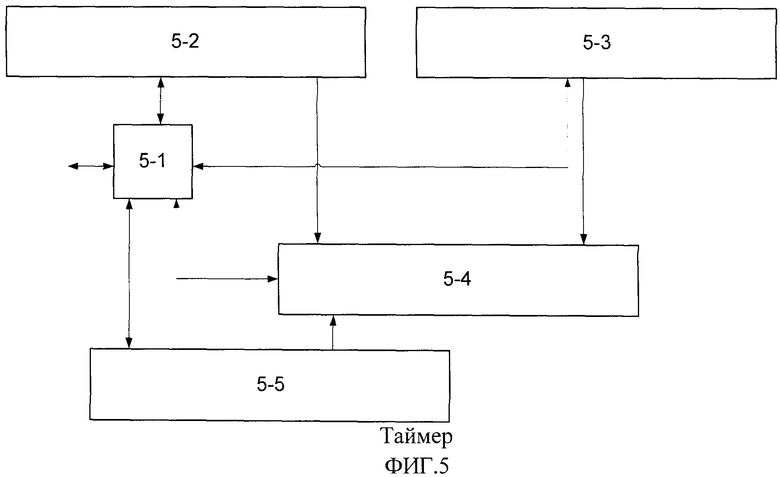

Таймер содержит два (первый и второй) точных счетчика и контрольный счетчик, подключенные через двунаправленную шину к блоку связи, а выходами подключенные к схеме контроля, которая, аналогично счетчикам, соединена через двунаправленную шину с блоком связи.

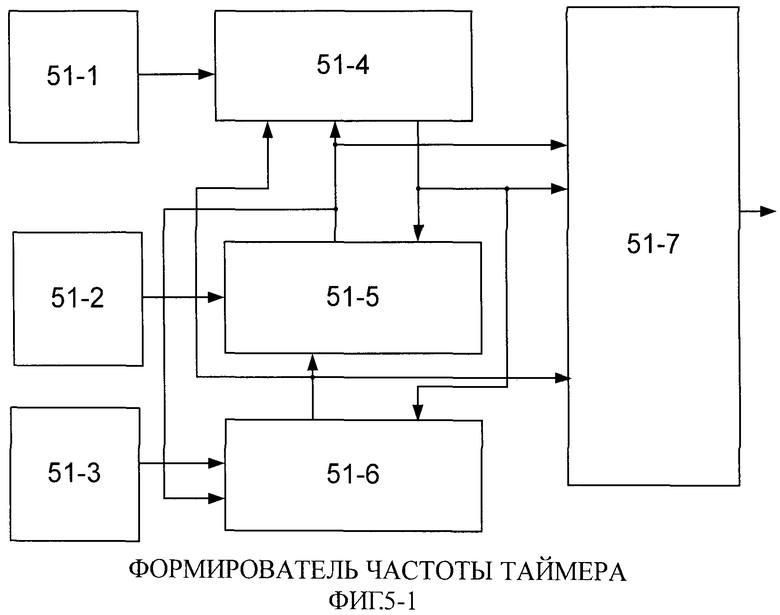

Формирователь частоты таймера содержит первый, второй и третий задающие генераторы, выходы которых подключены к входам первого, второго и третьего узлов фазирования соответственно. Фазирующий выход каждого из узлов фазирования подключен к фазирующим входам двух других узлов фазирования и к входам узла мажоритации, выход которого является выходом формирователя.

Блок управления МПП содержит m-последовательно соединенных инверторов, выходы которых подключены к входам второго мультиплексора, выход которого соединен с входом первого инвертора и является выходом блока, частотный вход которого является входом второго счетчика частоты, подключенного выходами к первым входам второй схемы сравнения, ко вторым входам которой подключены выходы второго регистра кода частоты. Высокостабильный генератор выходом подключен к входу второго счетчика, выходы которого через таймерный дешифратор подключены к стробирующему входу второй схемы сравнения, инкрементный и декрементный выходы которой подключены к одноименным входам второго счетчика кода частоты, выходы которого подключены к управляющим входам второго мультиплексора. Установочные входы второго регистра кода частоты и второго счетчика кода частоты являются установочным входом блока.

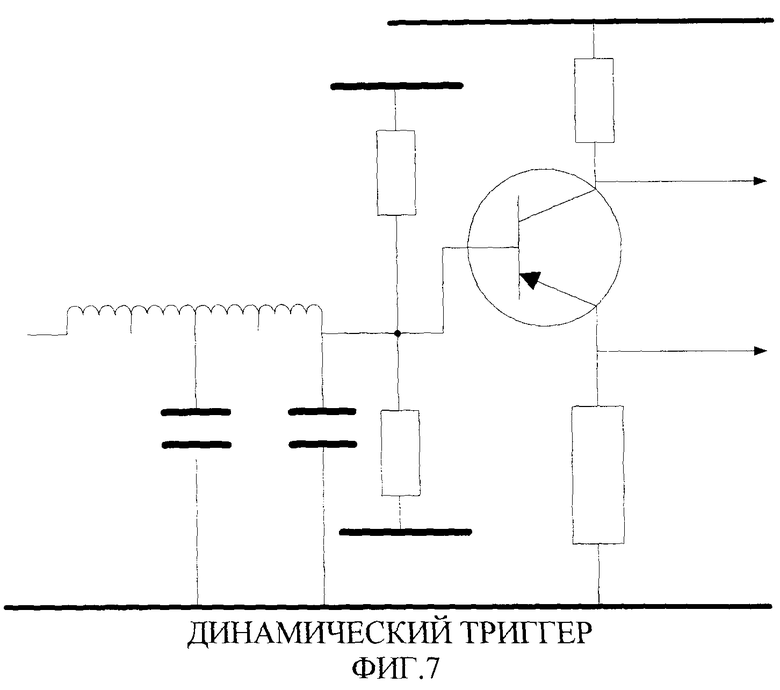

Динамический триггер выполнен как транзисторный усилитель, к базе транзистора которого, кроме резисторного делителя, в качестве элемента памяти, подключена LC - цепь, индуктивность которой содержит рабочую обмотку и намотанную поверх нее компенсационную, концы которой закорочены.

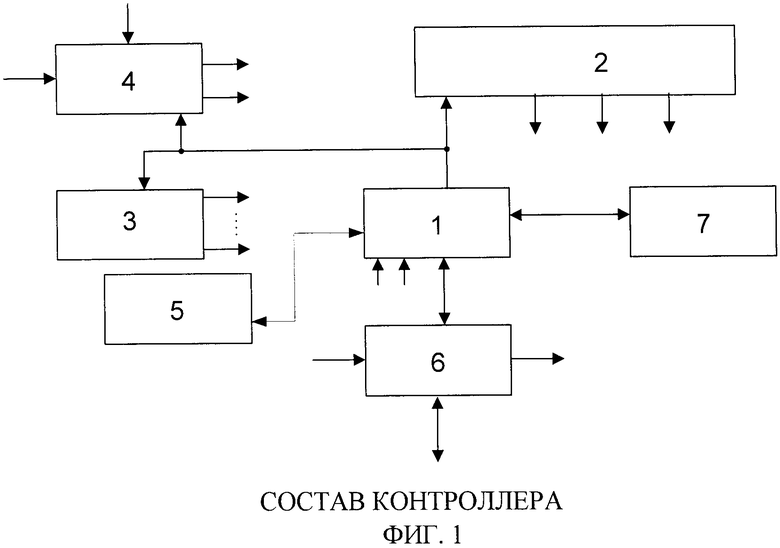

На чертежах (фигуры с 1 по 7) приведены состав контроллера, его блоков и узлов.

На фигуре 1 приведен состав контроллера, где цифрой 1 обозначен процессор, цифрой 2 - БМУ, цифрой 3 обозначен ФСИ, цифрой 4 - ИВЭП, цифрой 5 обозначен таймер, цифрой 6 - буферный регистр и цифрой 7 обозначено запоминающее устройство.

На фигуре 2 показан БМУ, где цифрой 2-0 обозначен ЗУМП, цифрой 2-1 - регистр кода операции, цифрой 2-2 обозначен регистр признаков, цифрой 2-3 - счетчик адреса, цифрой 2-4 обозначен регистр смещения и цифрами 2-5 и 2-n - выходные триггеры.

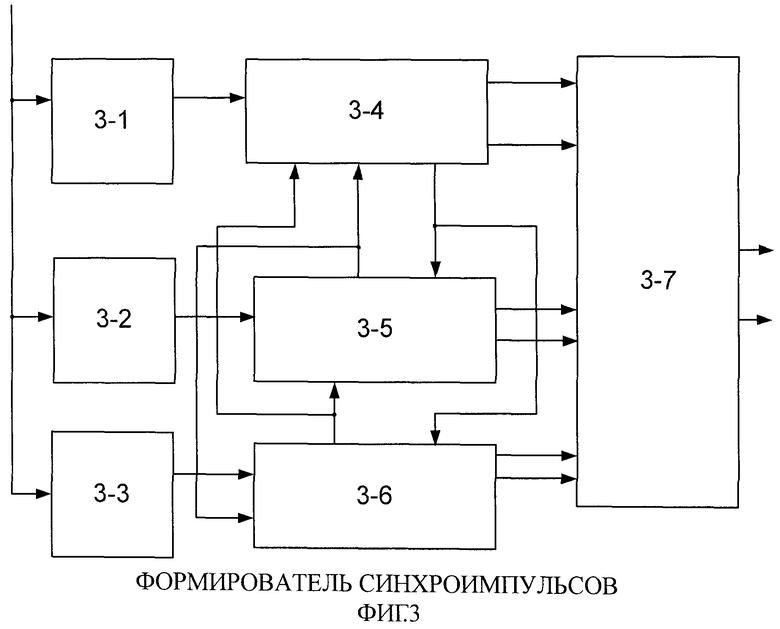

На фигуре 3 приведен ФСИ, где цифрами 3-1, 3-2 и 3-3 обозначены соответственно первый, второй и третий генераторы импульсов, цифрами 3-4, 3-5 и 3-6 обозначены соответственно первый, второй и третий блоки фазирования и цифрой 3-7 обозначен блок мажоритации.

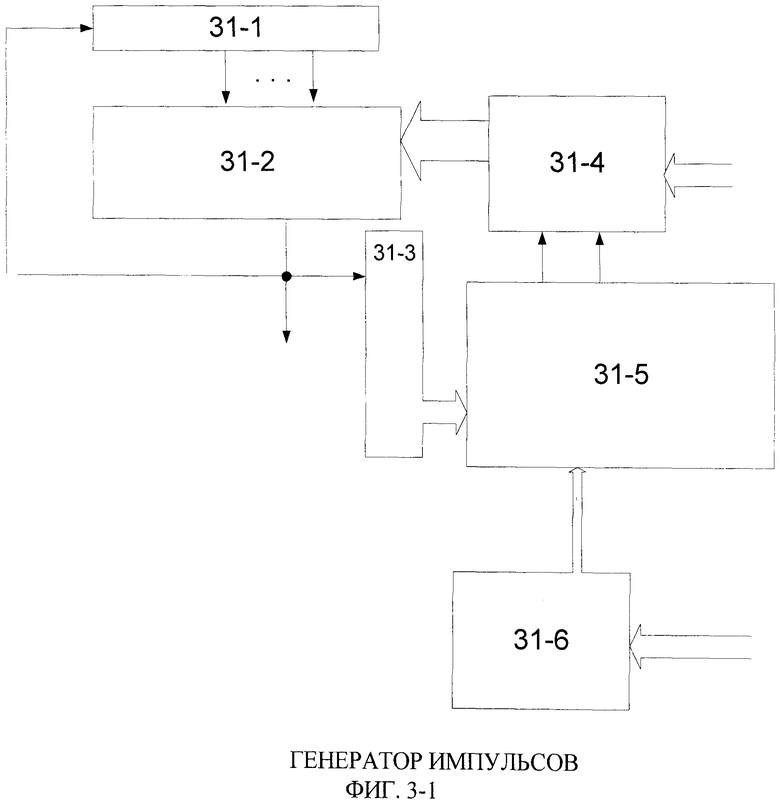

На фигуре 3-1 показан генератор импульсов, где цифрой 31-1 обозначены последовательно включенные инверторы, цифрой 31-2 - первый мультиплексор, цифрой 31-3 обозначен первый счетчик частоты. Цифрой 31-4 - первый счетчик кода частоты, цифрой 31-5 обозначена первая схема сравнения и цифрой 31-6 обозначен первый регистр кода частоты.

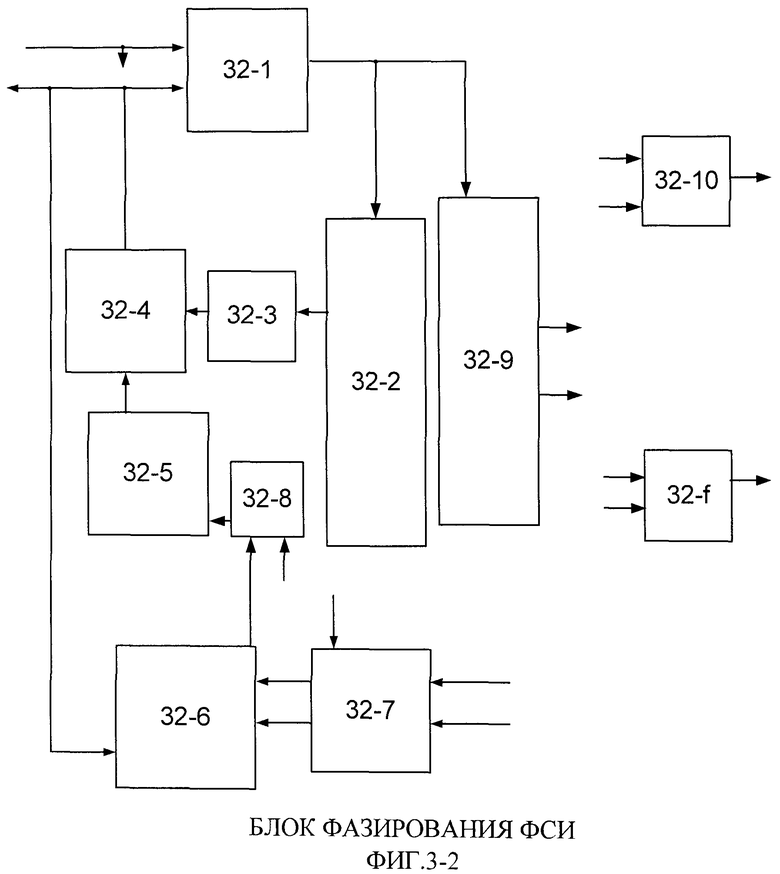

На фигуре 3-2 показан блок фазирования ФСИ, где цифрой 32-1 обозначен логический элемент, цифрой 32-2 - динамический счетчик, цифрой 32-3 - дешифратор. Цифрой 32-4 обозначен триггер останова, цифрой 32-5 обозначен триггер пуска, цифрой 32-6 - мажоритарный элемент. Цифрой 32-7 обозначены триггеры привязки, цифрой 32-8 обозначена схема «И», цифрой 32-9 обозначен сдвиговый регистр и цифрами от 32-10 до 32-f обозначены выходные формирователи.

На фигуре 4 изображен ИВЭП, где цифрой 4-1 обозначен модуль постоянного питания, а цифрой 4-2 - модуль импульсного питания.

На фигуре 4-1 показан МПП, где цифрой 41-1 обозначен фильтр, цифрой 41-2 обозначен трансформатор, цифрой 41-3 - фильтр нижних частот, цифрой 41-4 обозначен блок преобразования напряжения в частоту, цифрой 41-5 обозначен блок гальванической развязки и цифрой 41-6 обозначен блок управления.

На фигуре 4-2 изображен модуль импульсного питания.

На фигуре 5 изображен таймер, где цифрой 5-1 обозначен блок связи, цифрами с 5-2 по 5-3 обозначены первый и второй точные счетчики, цифрой 5-4 - схема контроля и цифрой 5-5 обозначен контрольный счетчик.

На фигуре 5-1 показан формирователь частоты таймера, где цифрами 51-1, 51-2, 51-3 показаны соответственно первый, второй и третий задающие генераторы, цифрами 51-4, 51-5, 51-6 обозначены соответственно первый, второй и третий узлы фазирования, цифрой 51-7 обозначен узел мажоритации.

На фигуре 6 показан блок управления МПП, где цифрой 6-0 обозначен высокостабильный генератор, цифрой 6-1 обозначены m-последовательно соединенных инверторов, цифрой 6-2 обозначен второй мультиплексор. Цифрой 6-3 обозначен второй счетчик кода частоты, цифрой 6-4 обозначен второй счетчик, цифрой 6-5 - таймерный дешифратор. Цифрой 6-6 обозначена вторая схема сравнения, цифрой 6-7 - второй регистр кода частоты и цифрой 6-8 обозначен второй счетчик частоты.

На фигуре 7 показан динамический триггер.

Контроллер может быть реализован следующим образом:

Для реализации процессора можно использовать БИС

микропроцессоров серии 1867, созданных и изготовленных в НИИЭТ г.Воронеж.

Для запоминающего устройства можно использовать микросхемы серии 1620, дополненные специализированными БИС на основе БМК серии 5516.

Формирователь синхроимпульсов может быть реализован на основе БИС 1825 ВБ2, дополненной БИС на основе указанных БМК.

Для реализации преобразователя напряжения в частоту можно использовать БИС ADFC32 фирмы Analog Devices, или ее аналог.

Для реализации гальванической развязки может быть использован оптрон 249ЛП5 или планарный трансформатор.

Контроллер работает следующим образом.

После включения питания по сигналу внутренней схемы сброса во всех регистрах и счетчиках устанавливаются коды, соответствующие номинальным значениям формируемых частот и начальному адресу микропрограмм.

Контроллер настроен на прием управляющих сигналов. По информации, выделенной из управляющих сигналов, контроллер выходит на соответствующую микропрограмму, содержащуюся в блоке ЗУМП. Последовательность считывания микропрограммных слов зависит от начальной установки регистров и счетчика команд и условий, формируемых процессором при выполнении программы и адресов, поступающих в регистр смещения БМУ с адресного выхода его запоминающего устройства. Переход к следующей команде может быть линейным по содержимому счетчика адреса БМУ, либо условным по содержимому его регистра признаков или безусловным по содержимому регистра смещения БМУ. После формирования начального адреса микропрограммы, контроллер переходит к выполнению микропрограммы принятой команды.

При принятии команды, где есть обмен с основным ЗУ, контроллер посылает в ФСИ сигнал приостанова на время, необходимое для обмена с ЗУ, что позволяет сохранить содержимое регистров процессора и продолжить работу после возобновления формирования синхроимпульсов без искажения обрабатываемых данных.

Предложенный контроллер без его аппаратурной переработки встраивается как в активное устройство, инициирующее обмен, так и в ведомое. Перестройкой быстродействия номиналов питания и частоты синхронизации он позволяет, с одной стороны, сохранить работоспособность при изменении быстродействия элементов из-за температурного дрейфа параметров полупроводников или дозовых факторов ионизирующего излучения, а с другой стороны, увеличить пропускную способность, если дрейф параметров полупроводников приводит к увеличению быстродействия элементов. Причем последнее встречается достаточно часто, так как при изготовлении большинства радиационно стойких БИС технологическими средствами (перелегированием) вызывают начальный сдвиг параметров полупроводников в сторону, противоположную их дрейфу от дозовых факторов ионизирующего излучения. Понижение температуры окружающей среды также может увеличивать быстродействие БИС, что отражено в соответствующих документах предприятий - изготовителей БИС и, в частности, в базовых технических условиях на БИС серий 1825 и 1620, выпускаемых АО «НПФ САПФИР» г.Москва.

Таким образом, предложенный контроллер свободен от недостатков известных устройств и имеет ряд принципиально новых свойств, обеспечивающих его эффективное применение в системах, работающих в экстремальных условиях, в которых известные устройства неработоспособны.

| название | год | авторы | номер документа |

|---|---|---|---|

| НЕЙРОВЫЧИСЛИТЕЛЬ | 2013 |

|

RU2553098C2 |

| ТЕХНОЛОГИЧЕСКАЯ УВМ | 2013 |

|

RU2563139C2 |

| ВЫЧИСЛИТЕЛЬНАЯ СИСТЕМА | 2013 |

|

RU2536434C2 |

| БЕСПЛАТФОРМЕННАЯ ИНЕРЦИАЛЬНАЯ НАВИГАЦИОННАЯ СИСТЕМА | 2013 |

|

RU2563333C2 |

| СБОЕУСТОЙЧИВАЯ ВЫЧИСЛИТЕЛЬНАЯ СИСТЕМА | 2013 |

|

RU2541839C2 |

| СИСТЕМА АВТОМАТИЧЕСКОГО УПРАВЛЕНИЯ | 2013 |

|

RU2534955C1 |

| МАГИСТРАЛЬНО-МОДУЛЬНАЯ ВЫЧИСЛИТЕЛЬНАЯ СИСТЕМА | 2013 |

|

RU2564626C2 |

| СИСТЕМА АСТРОНАВИГАЦИИ | 2013 |

|

RU2548927C1 |

| МОДЕЛИРУЮЩИЙ КОАП | 2013 |

|

RU2516703C1 |

| УПРАВЛЯЮЩАЯ ВЫЧИСЛИТЕЛЬНАЯ СИСТЕМА | 2011 |

|

RU2520350C2 |

Изобретение относится к вычислительной технике и может быть использовано при создании магистрально модульных управляющих вычислительных систем. Технический результат - повышение производительности контроллера. Контроллер передачи данных содержит буферный регистр, блок микропрограммного управления, перестраиваемый формирователь синхроимпульсов и управляемый источник вторичного электропитания, которые своими установочными входами подключены к процессору, к управляющим входам которого подключены выходы блока микропрограммного управления, а через первую, вторую и третью двунаправленные связи к нему подключены соответственно запоминающее устройство, буферный регистр и таймер. 8 з.п. ф-лы, 12 ил.

1 Контроллер передачи данных, содержащий буферный регистр и блок микропрограммного управления, отличающийся тем, что в его состав введены перестраиваемый формирователь синхроимпульсов и управляемый источник вторичного электропитания, которые своими установочными входами подключены к процессору, к управляющим входам которого подключены выходы блока микропрограммного управления, а через первую, вторую и третью двунаправленные связи к нему подключены соответственно запоминающее устройство, буферный регистр и таймер.

2. Контроллер по п.1, отличающийся тем, что формирователь синхроимпульсов содержит три генератора импульсов, выходы которых подключены к входам соответствующих им блоков фазирования, фазирующий выход каждого из которых подключен к фазирующим входам двух других блоков, и к входам блока мажоритации, выходы которого являются выходами формирователя.

3. Контроллер по п.1, отличающийся тем, что источник вторичного электропитания содержит модуль постоянного питания и модуль импульсного питания.

4. Контроллер по п.1, отличающийся тем, что таймер содержит два точных счетчика, схему контроля и контрольный счетчик, подключенных через двунаправленную связь к блоку связи.

5. Контроллер по п.2, отличающийся тем, что генератор импульсов содержит последовательно соединенные инверторы, выходы которых подключены к входам первого мультиплексора, выход которого подключен к входу первого инвертора и входу первого счетчика частоты, выходы которого подключены к первым входам первой схемы сравнения, ко вторым входам которой подключены выходы первого регистра кода частоты, а инкрементный и декрементный выходы первой схемы сравнения подключены к одноименным входам первого счетчика кода частоты, выходы которого подключены к управляющим входам первого мультиплексора, при этом установочные входы первого регистра кода частоты и первого счетчика кода частоты являются установочным входом генератора.

6. Контроллер по п.2, отличающийся тем, что блок фазирования содержит логический элемент, первый вход которого является входом блока, а выход подключен к входам сдвигового регистра и динамического счетчика, выход которого через дешифратор подключен к запускающему входу триггера останова, выход которого является фазирующим выходом блока и подключен ко второму входу логического элемента и первому входу мажоритарного элемента, выход которого через первый вход схемы «И» подключен к входу триггера пуска, второй вход которой является входом блока, выход которого подключен к сбрасывающему входу триггера останова, а ко второму и третьему входам мажоритарного элемента подключены выходы триггеров привязки, входы которых являются фазирующими входами блока, при этом выходы нечетных и четных разрядов сдвигового регистра подключены соответственно к запускающим и сбрасывающим входам формирователей, выходы которых являются синхронизирующими выходами блока.

7. Контроллер по п.3, отличающийся тем, что модуль постоянного питания содержит последовательно включенные фильтр, вход которого является силовым входом модуля, защитный диод, трансформатор с включенным в первичную обмотку транзистором-прерывателем, выпрямительный диод и фильтр нижних частот, выход которого является выходом модуля и подключен к блоку преобразования напряжения в частоту, подключенного через блок гальванической развязки к блоку управления, установочный вход которого является одноименным входом модуля, а выход подключен к базе транзистора прерывателя.

8. Контроллер по п.3, отличающийся тем, что блок управления МПП содержит m-последовательно соединенных инверторов, выходы которых подключены к входам второго мультиплексора, выход которого подключен к входу первого инвертора и является выходом блока, управляющий вход которого является входом второго счетчика кода частоты, подключенного выходами к первым входам второй схемы сравнения, ко вторым входам которой подключены выходы второго регистра кода частоты, а инкрементный и декрементный выходы этой схемы подключены к одноименным входам второго счетчика кода частоты, выходы которого подключены к управляющим входам второго мультиплексора, а установочные входы регистра кода и счетчика кода являются установочным входом блока.

9. Контроллер по п.6, отличающийся тем, что, динамический триггер выполнен как транзисторный усилитель, к базе транзистора которого кроме резисторного делителя в качестве элемента памяти подключена LC цепь, индуктивность которой содержит рабочую обмотку и намотанную поверх нее встречно компенсационную, концы которой закорочены.

| Устройство для передачи данных | 1976 |

|

SU642868A1 |

| СИСТЕМА УПРАВЛЕНИЯ СУДНОМ | 2010 |

|

RU2424944C1 |

| ФОРМИРОВАТЕЛЬ СИНХРОИМПУЛЬСОВ | 2011 |

|

RU2450433C1 |

| СИСТЕМА ОБРАБОТКИ ИЗОБРАЖЕНИЙ | 2011 |

|

RU2452125C1 |

| КОНТРОЛЛЕР ПЕРЕДАЧИ ДАННЫХ С ПСЕВДОСЛУЧАЙНОЙ ПЕРЕСТРОЙКОЙ РАБОЧЕЙ ЧАСТОТЫ | 2011 |

|

RU2446559C1 |

| Способ и приспособление для нагревания хлебопекарных камер | 1923 |

|

SU2003A1 |

| Пресс для выдавливания из деревянных дисков заготовок для ниточных катушек | 1923 |

|

SU2007A1 |

Авторы

Даты

2014-04-27—Публикация

2013-01-29—Подача