Изобретение относится к вычислительной технике и может быть использовано при построении устройств, обрабатывающих операнды, представленные в широтно-импульсной, частотной и кодовой формах. Техническим результатом является повышение быстродействия устройства.

Известно множительно-делительное устройство [1], которое осуществляет обработку время-импульсных сигналов, представленных в широтно-импульсной форме, и сигнала, представленного в виде кода по множительно-делительной зависимости с выдачей результата как в виде кода, так и в виде частоты.

Недостатком устройства [1] является низкое быстродействие вычислительного преобразователя, обусловленное необходимостью иметь дополнительную разрядность устройства для реализации оператора усреднения.

Из числа аналогов наиболее близким по технической сущности является множительно-делительное устройство [2], осуществляющее деление двух широтно-импульсных (ШИМ) сигналов пропорционально коду масштаба, которое и выбрано в качестве прототипа. Прототип отличается более высоким быстродействием по сравнению с устройством [1].

В состав прототипа входят регистр последовательного приближения, реверсивный счетчик, первый и второй элементы И, первый и второй умножители частоты на код, блок управления, причем у первого умножителя частоты на код установочные входы соединены соответственно с разрядами входной шины кода масштаба устройства, информационный вход - со входом первой опорной частоты устройства, а выход - с первым входом первого элемента И, второй вход которого соединен с первым информационным входом устройства, а выход - со входом сложения реверсивного счетчика, у второго умножителя частоты на код установочные входы соединены соответственно с разрядными выходами регистра и параллельного выхода устройства, информационный вход соединен со входом второй опорной частоты устройства, а выход - с последовательным выходом устройства и с первым входом второго элемента И, выход которого соединен со входом вычитания реверсивного счетчика, а вход установки в "0" этого счетчика соединен с выходом сброса блока управления, у которого установочный вход соединен с установочным входом устройства, причем информационные входы устройства соединены соответственно первый - со входом синхронизации блока управления, а второй - со вторым входом второго элемента И, при этом у блока управления вход сброса соединен с младшим дополнительным разрядом выхода регистра, вход управления информацией - с выходом знака разности реверсивного счетчика, а у блока управления выходы управляющего сигнала, управления информацией и синхронизации соединены соответственно с управляющим входом, информационным входом и входом синхронизации регистра последовательного приближения.

Блок управления содержит три триггера, элемент И, элемент ИЛИ, элемент задержки, вход которого соединен с установочным входом блока управления, а выход - со входом установки в "1" третьего триггера, выход второго триггера соединен с первым входом элемента И, выход третьего - с выходом управляющего сигнала, а выход элемента ИЛИ - с выходом синхронизации блока управления.

Кроме того, в состав блока управления входят второй элемент ИЛИ, элемент НЕ и два формирователя импульсов, причем вход синхронизации второго триггера соединен с выходом элемента НЕ, вход которого соединен с выходом второго формирователя импульсов, входом установки в "1" первого триггера, вторым входом элемента И и выходом сигнала сброса блока управления, установочный вход которого соединен с первыми входами первого и второго элементов ИЛИ, у третьего триггера вход установки в "0" соединен с выходом второго элемента ИЛИ, а выход - с информационным входом второго триггера, входы управления информацией, сброса и сигнала синхронизации блока управления соединены соответственно со входом установки в "0" первого триггера, входами первого и второго формирователей импульсов, а выход первого формирователя импульсов соединен со вторым входом второго элемента ИЛИ и со входом установки в "0" второго триггера, выход элемента И соединен со вторым входом первого элемента ИЛИ, а выход первого триггера - с выходом управления информацией блока управления.

Прототип [2] осуществляет обработку сигналов по множительно-делительной зависимости с выдачей результата как в виде кода

Nвых = N(Θ2/Θ1),

так и в виде частоты

Fвых = (F01/2n)Θ2N/Θ1,

где Θ1 = τ1/T и Θ2 = τ2/T - относительные длительности входных широтно-импульсных сигналов с длительностями τ1 и τ2 и периодом Т;

F01 - опорная частота устройства;

N - входной код, подаваемый на вход устройства;

n - разрядность умножителей частоты.

Недостатком прототипа [2] является низкое быстродействие устройства, поскольку длительность переходного процесса зависит от его разрядности, и окончательный результат формируется только в конце n+1 периода ШИМ сигнала.

Задачей, на решение которой направлено заявляемое изобретение, является создание множительно-делительного устройства, время срабатывания которого не зависит от его разрядности. Техническим результатом является повышение быстродействия множительно-делительного устройства.

Решение поставленной задачи состоит в том, что в множительно-делительное устройство, в состав которого входят регистр, реверсивный счетчик, первый и второй элементы И, первый и второй умножители частоты на код, блок управления, причем у первого умножителя частоты на код установочные входы соединены соответственно с разрядами входной шины кода масштаба устройства, информационный вход - со входом первой опорной частоты устройства, а выход - с первым входом первого элемента И, второй вход которого соединен с первым информационным входом устройства, а выход - со входом сложения реверсивного счетчика, у второго умножителя частоты на код установочные входы соединены соответственно с разрядными выходами регистра и параллельного выхода устройства, информационный вход соединен со входом второй опорной частоты устройства, а выход - с последовательным выходом устройства и с первым входом второго элемента И, выход которого соединен со входом вычитания реверсивного счетчика, а вход установки в "0" этого счетчика соединен с выходом сброса блока управления, у которого установочный вход соединен с установочным входом устройства, кроме того, в устройство введены комбинационный сумматор, второй регистр, второй реверсивный счетчик, третий и четвертый элементы И, причем выход сигнала сброса блока управления соединен со входом установки в "0" второго реверсивного счетчика, с первым входом третьего элемента И и с третьим входом первого элемента И, разрядные входы счетчика соединены с разрядными выходами комбинационного сумматора, разрядные входы слагаемых которого подключены соответственно к разрядным выходам регистра и реверсивного счетчика, последние также соединены с разрядными входами регистра, прямой динамический вход записи которого соединен со вторым информационным входом устройства, со вторым входом третьего элемента И и со входом управления информацией блока управления, в котором выход управляющего сигнала соединен со вторым входом второго элемента И, выход управления информацией - с прямым динамическим входом записи начального состояния реверсивного счетчика и со входом прямой динамической записи второго реверсивного счетчика, выход синхронизации - со вторым входом четвертого элемента И и прямым динамическим входом записи второго регистра, а вход сброса - с выходом флага обнуления второго реверсивного счетчика, а также с третьими инверсными входами второго и четвертого элементов И, входы второго реверсивного счетчика подсоединены соответственно вычитающий - к выходу четвертого элемента И, а суммирующий - к выходу третьего элемента И, третий вход которого подключен ко входу второй опорной частоты устройства и к первому входу четвертого элемента И, разрядные выходы второго реверсивного счетчика соединены с разрядными входами второго регистра, разрядные выходы которого соединены с разрядными входами второго реверсивного счетчика.

В блоке управления, содержащем три триггера, элемент И, элемент ИЛИ, элемент задержки, вход которого соединен с установочным входом блока управления, а выход - со входом установки в "1" третьего триггера, выход второго триггера соединен с первым входом элемента И, выход третьего - с выходом управляющего сигнала, а выход элемента ИЛИ - с выходом синхронизации блока управления, в котором триггеры объединены в циклический сдвиговый регистр, вход установки в "0" которого соединен с установочным входом, а вход сдвига - со входом управления информацией блока управления, вход сброса которого подключен ко второму входу элемента И, входы элемента ИЛИ подключены к выходам второго и третьего триггеров, а выходы блока управления соединены соответственно выход управления информацией - с выходом элемента И, а сброса - с выходом первого триггера сдвигового регистра.

Сущность предлагаемого изобретения состоит в создании множительно-делительного устройства с повышенным быстродействием за счет использования гиперболической запоминающей обратной связи, обеспечивающей дополняющую компенсацию, благодаря чему снимается зависимость длительности процесса вычисления от разрядности структуры.

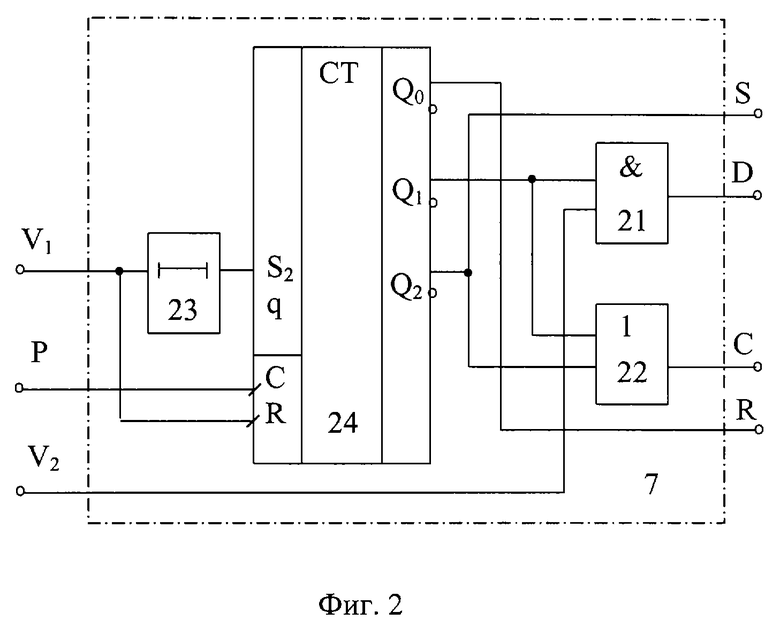

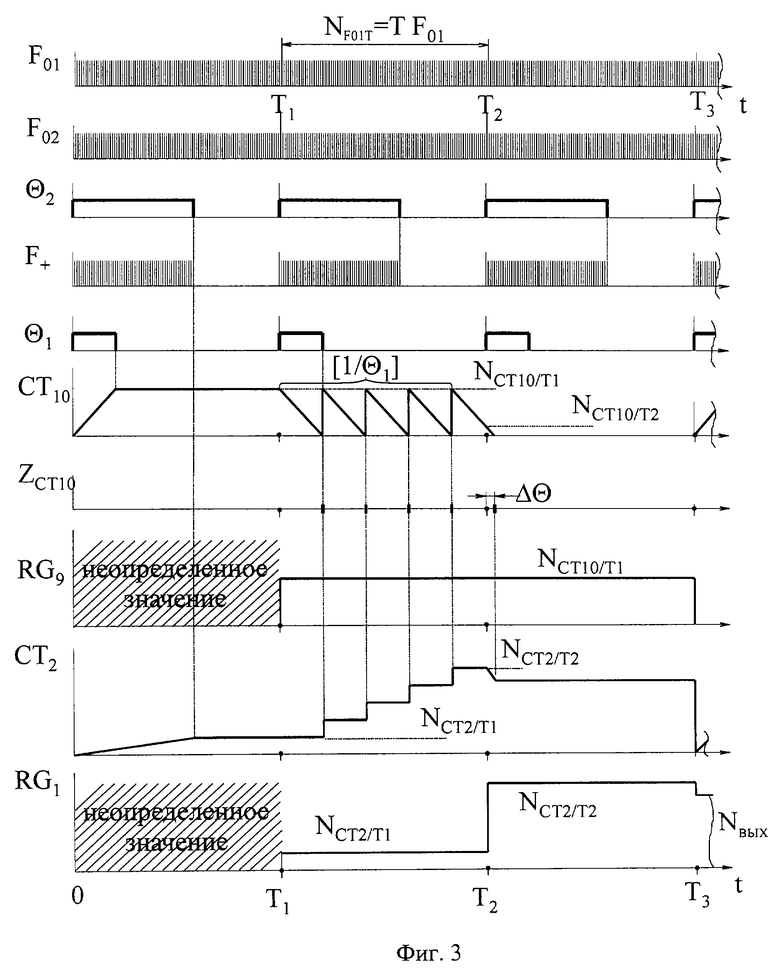

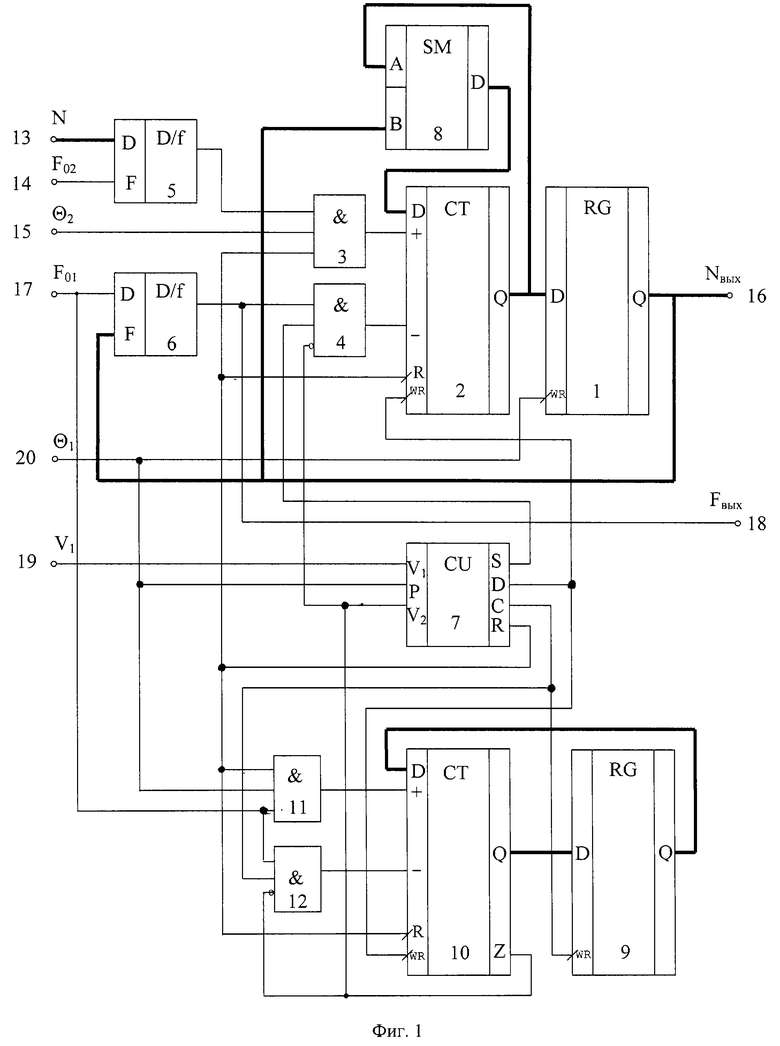

Сущность предлагаемого изобретения поясняется чертежами, где на фиг.1 изображена функциональная схема предлагаемого множительно-делительного устройства, на фиг.2 - функциональная схема блока управления, а на фиг.3 - временная диаграмма процессов, протекающих в устройстве.

Множительно-делительное устройство содержит регистр 1, реверсивный счетчик 2, первый и второй элементы И 3 и 4, первый и второй умножители частоты на код 5 и 6, блок управления 7, комбинационный сумматор 8, второй регистр 9, второй реверсивный счетчик 10, третий и четвертый элементы И 11 и 12, причем у первого умножителя частоты на код 5 установочные входы соединены соответственно с разрядами входной шины кода масштаба 13 устройства, информационный вход - со входом 14 первой опорной частоты устройства, а выход - с первым входом первого элемента И 3, второй вход которого соединен с первым информационным входом 15 устройства, а выход - со входом сложения реверсивного счетчика 2, у второго умножителя частоты на код 6 установочные входы соединены соответственно с разрядными выходами регистра 1 и параллельного выхода устройства 16, информационный вход соединен со входом 17 второй опорной частоты устройства, а выход - с последовательным выходом 18 устройства и с первым входом второго элемента И 4, выход которого соединен со входом вычитания реверсивного счетчика 2, а вход установки в "0" этого счетчика соединен с выходом сброса R блока управления 7, у которого установочный вход V1 соединен с установочным входом устройства 19, причем выход сигнала сброса R блока управления 7 соединен со входом установки в "0" второго реверсивного счетчика 10, с первым входом третьего элемента И 11 и с третьим входом первого элемента И 3, разрядные входы счетчика 2 соединены с разрядными выходами комбинационного сумматора 8, разрядные входы слагаемых которого подключены соответственно к разрядным выходам регистра 1 и реверсивного счетчика 2, последние также соединены с разрядными входами регистра 1, прямой динамический вход записи которого соединен со вторым информационным входом 20 устройства, со вторым входом третьего элемента И 11 и со входом управления информацией Р блока управления 7, в котором выход управляющего сигнала S соединен со вторым входом второго элемента И 4, выход управления информацией D - с прямым динамическим входом записи начального состояния реверсивного счетчика 2 и со входом прямой динамической записи второго реверсивного счетчика 10, выход синхронизации С - со вторым входом четвертого элемента И 12 и прямым динамическим входом записи второго регистра 9, а вход сброса V2 - с выходом флага обнуления второго реверсивного счетчика 10, а также с третьими инверсными входами второго и четвертого элементов И 4 и И 12, входы второго реверсивного счетчика 10 подсоединены соответственно вычитающий - к выходу четвертого элемента И 12, а суммирующий - к выходу третьего элемента И 11, третий вход которого подключен ко входу 17 второй опорной частоты устройства и к первому входу четвертого элемента И 12, разрядные выходы второго реверсивного счетчика 10 соединены с разрядными входами второго регистра 9, разрядные выходы которого соединены с разрядными входами второго реверсивного счетчика 10.

В блоке управления, содержащем три триггера, элемент И 21, элемент ИЛИ 22, элемент задержки 23, вход которого соединен с установочным входом V1 блока управления 7, а выход - со входом установки в "1" третьего триггера, выход второго триггера соединен с первым входом элемента И 21, выход третьего - с выходом управляющего сигнала S, а выход элемента ИЛИ 22 - с выходом синхронизации С блока управления 7, в котором триггеры объединены в циклический сдвиговый регистр 24, вход установки в "0" которого соединен с установочным входом V1, а вход сдвига - со входом управления информацией Р блока управления 7, вход сброса которого подключен ко второму входу элемента И 21, входы элемента ИЛИ 22 подключены к выходам второго и третьего триггеров, а выходы блока управления 7 соединены соответственно выход управления информацией D - с выходом элемента И 21, а сброса R - с выходом первого триггера сдвигового регистра 24.

Устройство работает следующим образом.

На вход 13 устройства подается входной двоичный код масштаба N, на информационные входы 20 и 15 - широтно-импульсные сигналы Θ1 и Θ2, на входы опорных частот устройства 17 и 14 - опорные импульсные последовательности F01 и F02. Сигнал запуска устройства, поступающий с установочного входа 19 устройства на установочный вход V1 блока управления 7, устанавливает в "0" сдвиговый регистр 24, который реализуется на трех триггерах, например, по схемам сдвиговых регистров ИР1 и ИР11 (серии 155, 555 и т.п.). Этот же сигнал запуска, пройдя через элемент задержки 23, обеспечивает запись единицы в старший разряд регистра 24, и на его выходе фиксируется код Q0=0, Q1=0, Q2=1.

В начале первого периода работы устройства по переднему фронту первого информационного сигнала Θ1 из счетчика 2 в регистр 1 переписывается значение, неопределенность которого не нарушает процесс вычисления. Кроме того, по переднему фронту сигнала Θ1, поступающего на вход управления информацией Р блока управления 7, в регистре 24 происходит циклический сдвиг кода, что приводит к фиксации единичного уровня на выходе Q0 и нулевых уровней на выходах Q1 и Q2. В результате на выходе сброса R блока управления 7 появляется сигнал сброса, положительный перепад которого обнуляет счетчики 2 и 10, а установившийся единичный уровень обеспечивает прохождение сигналов к суммирующим входам этих счетчиков через элементы И 3 и И 11 соответственно. Нулевые уровни на выходах Q1 и Q2 регистра 24 приводят к фиксации нулей на выходах S, D и С блока управления 7. Сигналы S и С, поступая на элементы И 4 и И 12 соответственно, блокируют работу цепей, подключенных к вычитающим входам счетчиков 2 и 10.

Единичный сигнал флага обнуления счетчика 10 формируется сразу после его сброса и поступает на блокированные другими сигналами элементы И 4, И 12, а также на вход сброса V2 блока управления 7. В блоке управления этот единичный сигнал поступает на второй вход элемента И 21, у которого на первом входе удерживается нулевой уровень с выхода Q1 регистра 24, и, следовательно, состояние выхода D блока управления не изменяется, то есть остается нулевым.

Под воздействием кода масштаба N на выходе умножителя частоты на код 5 начинают вырабатываться импульсы, которые в течение интервала времени отпирания элемента И 3 сигналом Θ2, поступающим с первого информационного входа 15, проходят через этот элемент на суммирующий вход реверсивного счетчика 2, изменяя его состояние.

Импульсы опорной частоты F01 в течение интервала времени отпирания элемента И 11 сигналом Θ1, поступающим со второго информационного входа 20, проходят через этот элемент на суммирующий вход реверсивного счетчика 10, изменяя его состояние.

В начале второго периода широтно-импульсных сигналов передним фронтом первого информационного сигнала Θ1 в регистр 1 переписывается текущее состояние счетчика 2. Этот же сигнал поступает на вход управления информацией Р блока управления 7, и в регистре 24 происходит циклический сдвиг кода, что приводит к фиксации единичного уровня на выходе Q1 и нулевых уровней на выходах Q0 и Q2.

В результате на первом входе элемента ИЛИ 22 появляется единичный сигнал, который проходит на выход синхронизации С блока управления 7. Передним фронтом этого сигнала в регистр 9 переписывается текущее состояние счетчика 10. Сдвиг кода, содержащегося в регистре 24, вызывает также появление нулевого сигнала на выходе сброса R и сохранение нулевого уровня на выходе управляющего сигнала S блока управления 7. Причем сигнал с выхода сброса R, поступая на элементы И 3 и И 11, блокирует работу цепей, подключенных к суммирующим входам счетчиков 2 и 10 соответственно. Сигнал с выхода управляющего сигнала S, поступая на элемент И 4, блокирует работу цепи, подключенной к вычитающему входу счетчика 2.

Нулевое значение сигнала флага обнуления счетчика 10, сигнализирующее о ненулевом значении кода в счетчике, поступает на вход сброса V2 блока управления 7. Здесь этот сигнал приходит на второй вход элемента И 21, благодаря чему обеспечивается нулевой уровень сигнала управления информацией D.

В течение второго периода выполняется циклическое увеличение содержимого счетчика 2 на значение, зафиксированное в начале периода в регистре 1. Это происходит следующим образом: через элемент И 12, который открыт в течение второго периода сигналом С блока управления, на вычитающий вход счетчика 10 поступают импульсы опорной частоты F01 и уменьшают его состояние. В момент обнуления счетчика 10 флаг обнуления устанавливается в единицу, то есть Z=1. Положительный перепад этого сигнала появляется на входе V2 блока управления 7.

Проходя на второй вход элемента И 21, этот сигнал обеспечивает формирование положительного перепада сигнала управления информацией D. Положительный перепад сигнала, поступающего с выхода D блока управления 7, инициирует запись в счетчик 2 кода, снимаемого с выхода сумматора 8, и обеспечивает перезапись содержимого регистра 9 в счетчик 10. После этого значение флага Z обнуления счетчика 10 вновь становится нулевым. На этом завершается первый цикл увеличения содержимого счетчика 2 и начинается следующий. Этот процесс продолжается до окончания второго периода.

В начале третьего периода широтно-импульсных сигналов передним фронтом первого информационного сигнала Θ1 в регистр 1 переписывается текущее состояние счетчика 2. Этот же сигнал поступает на вход управления информацией Р блока управления 7, и в регистре 24 происходит циклический сдвиг кода, что приводит к фиксации единичного уровня на выходе Q2 и нулевых уровней на выходах Q0 и Q1.

В результате единичный уровень на выходе Q2 приводит к появлению единичных сигналов на выходе управляющего сигнала S блока управления 7 и на втором входе элемента ИЛИ 22. При этом на выходе элемента ИЛИ 22 сохраняется единичный сигнал, который проходит на выход синхронизации С блока управления 7. Нулевой уровень с выхода Q0 регистра 24 проходит непосредственно на выход сброса R блока управления 7, а нулевой уровень с выхода Q1, поступая на первый вход элемента И 21, приводит к фиксации нулевого сигнала на выходе управления информацией D блока управления 7.

Нулевой сигнал сброса R, поступая на элементы И 3 и И 11, блокирует работу цепей, подключенных к суммирующим входам счетчиков 2 и 10 соответственно. Как и на предыдущем периоде ШИМ сигналов единичное значение на выходе сигнала синхронизации С отпирает элемент И 12. Этот элемент открыт также нулевым значением флага Z счетчика 10, поступающим на его инверсный вход, что обеспечивает декрементирование содержимого счетчика 10 импульсами опорной частоты F01. Сохранение единичного уровня на выходе С блока управления 7 не приводит к изменению содержимого регистра 9 на третьем периоде, так как процесс записи в регистр осуществляется по динамическому входу.

Единичное значение на выходе управляющего сигнала S блока управления 7 отпирает элемент И 4, открытый также нулевым значением флага Z счетчика 10, поступающим на его инверсный вход. Это обеспечивает пропускание на вычитающий вход счетчика 2 импульсов, которые вырабатываются на выходе умножителя частоты на код 6 под воздействием кода, зафиксированного в начале третьего периода в регистре 1. В момент обнуления счетчика 10 флаг обнуления устанавливается в единицу, то есть Z=1. Этот сигнал блокирует цепи, подключенные к вычитающим входам реверсивных счетчиков 2 и 10. До наступления следующего периода широтно-импульсных сигналов изменений в состоянии элементов схемы не происходит.

В начале следующего, четвертого, периода широтно-импульсных сигналов передним фронтом первого информационного сигнала Θ1 в регистр 1 переписывается текущее состояние счетчика 2, которое соответствует результату Nвыx выполненной множительно-делительной операции.

Кроме того, по переднему фронту сигнала Θ1, поступающего на вход управления информацией Р блока управления 7, в регистре 24 происходит циклический сдвиг кода, что приводит к фиксации единичного уровня на выходе Q0 и нулевых уровней на выходах Q1 и Q2. Далее процесс работы устройства повторяется по описанию работы с первого по третий период.

Принцип действия множительно-делительного устройства основан на широтной модуляции частотно-импульсных последовательностей с целью выработки временных шагов и кодовых весов для пошагового последовательного весового приближения к результату до его превышения и с последующей дополнительной частотно-импульсной компенсацией перевеса до получения результата.

В течение первого периода среднее значение частоты импульсной последовательности на суммирующем входе счетчика 2 (см. диаграмму F+, фиг.3), определяется как

За первый период в счетчике 2 накопится значение (см. диаграмму СТ2, фиг.3)

NСT2/Т1=TNΘ2F02/2n.

Принимая k2=TF02/2n, для счетчика 2 имеем

NСT2/Т1=NΘ2k2. (1)

По окончании первого периода в счетчике 10 содержится значение количества импульсов опорной частоты F01, которое соответствует длительности сигнала Θ1 (см. диаграмму СТ10, фиг.3)

NСT10/Т1=Θ1F01T или NСT10/Т1=Θ1k1, (2)

где k1=TF01.

В течение второго периода комбинационный сумматор 8 с регистром 1 и счетчиком 2 будут выполнять накапливающее суммирование по следующему правилу:

Nsm8i=NCT2/T2i+NRG1;

NCT2/T2i+1=NSM8i,

где i изменяется в диапазоне от 1 до целой части частного [1/Θ1], a NRG1=NCT2/T1, NCT2/T20=NCT2/T1 (см. диаграммы ZСТ10 и RG1 фиг.3).

К концу второго периода в счетчике 10 будет зафиксирован код

NСT10/Т2=([1/Θ1]+1)NСT10/Т1-NF01/Т, (3)

где NF01/Т - количество импульсов опорной частоты F01 за период Т, то есть

NF01/Т=F01T, (4)

а в счетчике 2 -

NСT2/Т2=NСT2/Т1+NСT2/Т1[1/Θ1]

или

NСT2/Т2=NСT2/Т1(1+[1/Θ1]). (5)

Из выражения (3) с учетом (2) и (4) получим

NСT10/Т2=([1/Θ1]+1)Θ1F01T-F01Т, (6)

а из выражения (5) с учетом (1) получим

NСT2/Т2=(1+[1/Θ1])NΘ2k2. (7)

В течение третьего периода значение в счетчике 10 будет преобразовано в ШИМ сигнал

ΔΘ=NСT10/Т2/NF01/T. (8)

Среднее значение частоты импульсной последовательности на вычитающем входе счетчика 1 в течение третьего периода определяется как

F_=МСТ2/Т2ΔΘF01/2n,

что обеспечит отрицательное приращение кода на счетчике 2

ΔN- = TNCT2/T2ΔΘF01/2n, (9)

со следующим значением в конце периода

NСT2/Т3=NCT2/T2ΔN_. (10)

С учетом (7), (9), (8) и (6) имеем

При установленном соотношении TF01=2n имеем

NCT2/T3 = NΘ2k2(1+[1/Θ1])(2-(1+[1/Θ1])Θ1).

Упрощая выражение с учетом замены целой части на разность частного и дробной части результата деления, то есть

[1/Θ1] = 1/Θ1-{1/Θ1},

получаем

При установленном соотношении TF02=2n имеем

NCT2/T3 = NΘ2/Θ1-NΘ2Θ1(1-{1/Θ1})2,

где первое слагаемое NΘ2/Θ1 = Nвых.идеал - функциональная характеристика по параллельному выходу устройства,

а второе слагаемое NΘ2Θ1(1-{1/Θ1})2 - абсолютная погрешность устройства.

Таким образом, в начале четвертого периода на выходе регистра 1 будет зафиксирован код Nвых=NСТ2/Т3.

Моделирование, проведенное при малых значениях входных данных (0<Θ1<0,2; 0<Θ2<0,2), когда обычно относительная погрешность велика, показало, что погрешность находится в диапазоне от 0 до 0,1% для восьмиразрядной структуры. При увеличении разрядности точность вычислений повышается соответственно.

Характеристика устройства по последовательному выходу будет иметь вид

Fвых = (F01/2n)NΘ2/Θ1.

Таким образом, характеристика устройства соответствует заданной, результат получен за три периода ШИМ сигналов и длительность переходного процесса не зависит от разрядности устройства. В то же время у прототипа длительность переходного процесса зависит от его разрядности, и окончательный результат формируется только в конце n+1 периода ШИМ сигнала. Следовательно, быстродействие заявляемого устройства при трехразрядных структурах эквивалентно быстродействию прототипа, а при четырех разрядах и более заявляемое устройство является более быстродействующим. Причем с увеличением разрядности эффект повышения быстродействия по сравнению с прототипом увеличивается. Эффект цифровой обработки ШИМ сигналов проявляется при работе с большими разрядностями, во всяком случае больше трех.

Источники информации

1. Авторское свидетельство СССР 788128. И.В. Герасимов, И.М. Сафьянников. Множительно-делительное устройство, кл. G 06 G 7/161, G 06 J 3/00, заявлено 1977, опубликовано 1980, бюллютень 46.

2. Авторское свидетельство СССР 1305677. А.В. Петров, Н.М. Сафьянников. Множительно-делительное устройство, кл. G 06 F 7/68, G 06 J 3/00, заявлено 1985, опубликовано 1987, бюллютень 15 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Множительно-делительное устройство | 1985 |

|

SU1305677A1 |

| МНОЖИТЕЛЬНО-ДЕЛИТЕЛЬНОЕ УСТРОЙСТВО | 2008 |

|

RU2389065C1 |

| ЦИФРОВОЙ ТЕРМОМЕТР | 2002 |

|

RU2207529C1 |

| МНОЖИТЕЛЬНО-ДЕЛИТЕЛЬНОЕ УСТРОЙСТВО | 2002 |

|

RU2222042C2 |

| МНОЖИТЕЛЬНО-ДЕЛИТЕЛЬНОЕ УСТРОЙСТВО | 1995 |

|

RU2097829C1 |

| УСТРОЙСТВО ДЛЯ ИЗМЕРЕНИЯ СРЕДНЕЙ ТЕМПЕРАТУРЫ | 2004 |

|

RU2260778C1 |

| Цифровое множительно-делительное устройство | 1990 |

|

SU1730623A1 |

| Функциональный широтно-импульсный преобразователь кода | 1987 |

|

SU1437882A1 |

| ШИРОТНО-ИМПУЛЬСНЫЙ МОДУЛЯТОР | 2000 |

|

RU2171011C1 |

| УСТРОЙСТВО АВТОМАТИЧЕСКОГО ПОИСКА КАНАЛОВ РАДИОСВЯЗИ | 2011 |

|

RU2450447C1 |

Изобретение относится к вычислительной технике и может использоваться в устройствах, обрабатывающих операнды, представленные в широтно-импульсной, частотной и кодовой формах. Технический результат заключается в повышении быстродействия множительно-делительного устройства. Для этого устройство содержит два регистра, два реверсивных счетчика, четыре элемента И, два умножителя частоты на код, блок управления и комбинационный сумматор. 3 ил.

Множительно-делительное устройство, содержащее регистр, реверсивный счетчик, первый и второй элементы И, первый и второй умножители частоты на код, блок управления, причем у первого умножителя частоты на код установочные входы соединены соответственно с разрядами входной шины кода масштаба устройства, информационный вход - со входом первой опорной частоты устройства, а выход - с первым входом первого элемента И, второй вход которого соединен с первым информационным входом устройства, а выход - со входом сложения реверсивного счетчика, у второго умножителя частоты на код установочные входы соединены соответственно с разрядными выходами регистра и параллельного выхода устройства, информационный вход соединен со входом второй опорной частоты устройства, а выход - с последовательным выходом устройства и с первым входом второго элемента И, выход которого соединен со входом вычитания реверсивного счетчика, а вход установки в "0" этого счетчика соединен с выходом сброса блока управления, у которого установочный вход соединен с установочным входом устройства, у которого блок управления содержит три триггера, элемент И, элемент ИЛИ, элемент задержки, вход которого соединен с установочным входом блока управления, а выход - со входом установки в "1" третьего триггера, выход второго триггера соединен с первым входом элемента И, выход третьего - с выходом управляющего сигнала, а выход элемента ИЛИ - с выходом синхронизации блока управления, отличающееся тем, что в устройство введены комбинационный сумматор, второй регистр, второй реверсивный счетчик, третий и четвертый элементы И, причем выход сигнала сброса блока управления соединен со входом установки в "0" второго реверсивного счетчика, с первым входом третьего элемента И и с третьим входом первого элемента И, разрядные входы счетчика соединены с разрядными выходами комбинационного сумматора, разрядные входы слагаемых которого подключены соответственно к разрядным выходам регистра и реверсивного счетчика, последние также соединены с разрядными входами регистра, прямой динамический вход записи которого соединен со вторым информационным входом устройства, со вторым входом третьего элемента И и со входом управления информацией блока управления, в котором выход управляющего сигнала соединен со вторым входом второго элемента И, выход управления информацией - с прямым динамическим входом записи начального состояния реверсивного счетчика и со входом прямой динамической записи второго реверсивного счетчика, выход синхронизации - со вторым входом четвертого элемента И и прямым динамическим входом записи второго регистра, а вход сброса - с выходом флага обнуления второго реверсивного счетчика, а также с третьими инверсными входами второго и четвертого элементов И, входы второго реверсивного счетчика подсоединены соответственно вычитающий - к выходу четвертого элемента И, а суммирующий - к выходу третьего элемента И, третий вход которого подключен ко входу второй опорной частоты устройства и к первому входу четвертого элемента И, разрядные выходы второго реверсивного счетчика соединены с разрядными входами второго регистра, разрядные выходы которого соединены с разрядными входами второго реверсивного счетчика, а в блоке управления триггеры объединены в циклический сдвиговый регистр, вход установки "0" которого соединен с установочным входом, а вход сдвига - со входом управления информацией блока управления, вход сброса которого подключен ко второму входу элемента И, входы элемента ИЛИ подключены к выходам второго и третьего триггеров, а выходы блока управления соединены соответственно выход управления информацией - с выходом элемента И, а сброса - с выходом первого триггера сдвигового регистра.

| Множительно-делительное устройство | 1985 |

|

SU1305677A1 |

| ЧАСТОТНО-ИМПУЛЬСНОЕ МНОЖИТЕЛЬНО-ДЕЛИТЕЛЬНОЕ УСТРОЙСТВО | 1992 |

|

RU2012040C1 |

| МНОЖИТЕЛЬНОЕ УСТРОЙСТВО | 1993 |

|

RU2082996C1 |

| Делительно-множительное устройство | 1979 |

|

SU857989A1 |

| Делительно-множительное устройство | 1984 |

|

SU1265768A1 |

Авторы

Даты

2003-08-10—Публикация

2002-02-14—Подача