Настоящее изобретение относится к интегральной электронной технике и может быть использовано в устройствах фазовой автоподстройки частоты (ФАПЧ) и, более конкретно, при реализации фильтра контура управления (ФКУ) с высокой скоростью перестройки управляющего напряжения и, в случае полностью интегральной реализации, малой площадью, занимаемой ФКУ на кристалле микросхемы.

Устройства импульсной ФАПЧ широко применяются в синтезаторах сетки частот (ССЧ), схемах генерации и распределения цифровых тактовых сигналов, схемах восстановления тактовой информации из потока данных. С появлением технологий, позволяющих создавать интегральные микросхемы высокой плотности, все более проявляется тенденция, заключающаяся в минимизации использования внешних по отношению к микросхеме компонентов. В полной мере эта тенденция коснулась проектирования интегральных устройств ФАПЧ, все элементы которых должны размещаться на кристалле микросхемы.

Типовая структурная схема системы импульсной ФАПЧ представлена на фиг.1. В ее состав входят: импульсный частотно-фазовый детектор 1 (ИЧФД), источник тока поддержания заряда 2 (ИТПЗ), фильтр контура управления 3 (ФКУ), фильтр низкой частоты 4 (ФНЧ), генератор, управляемый напряжением 5 (ГУН) и делитель частоты 6 (ДЧ). Синхронизм системы ФАПЧ обеспечивается устранением фазовой ошибки между фронтами импульсов сигналов опорной частоты Fоп и частоты обратной связи Fос. С этой целью ИЧФД вырабатывает соответствующие импульсные сигналы фазового рассогласования Up или Down. Под воздействием этих сигналов ИТПЗ либо отдает, либо принимает ток со схемы ФКУ, тем самым формируя управляющее напряжение Uупр для автоматической подстройки частоты и фазы ГУН. ФНЧ осуществляет подавление пульсаций в напряжении Uупр, вызванных импульсным характером управления. Умножение входной опорной частоты обеспечивается включением ДЧ в цепь обратной связи. Сигнал выходной частоты Fвых снимается с выхода ГУН.

Типовая структурная схема ФКУ состоит из конденсатора Сп, обеспечивающего точку полюса в передаточной функции системы и изодромного звена Rэкв, Сэкв, обеспечивающего точку нуля. Для обеспечения устойчивости и приемлемой колебательности процесса автоподстройки частоты точка нуля располагается перед точкой полюса. При этом система должна иметь достаточный запас по фазе. Для осуществления соответствующей частотной коррекции контура управления емкость конденсатора Сэкв обычно по крайней мере в десять раз больше, чем емкость конденсатора Сп. При заданном токе ИТПЗ минимальное значение Сп ограничивается требованиями уменьшения пульсаций управляющего напряжения Uупр уже на входе ФНЧ. Значение минимального тока ИТПЗ ограничивается уровнем помех от других блоков в подложке микросхемы. В результате, конденсатор Сэкв имеет большую емкость и, соответственно, занимает большую площадь на кристалле микросхемы, что является существенным недостатком данной структуры интегрального ФКУ.

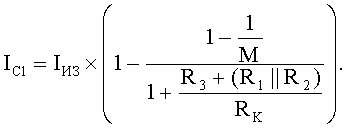

Известно описание изобретения к патенту США №7567133 «Phase-Locked Loop Filter Capacitance With A Drag Current», МПК H03L 7/00 [1]. Это изобретение относится к методам уменьшения значения конденсатора изодромного звена ФКУ и представляет схему, основанную на использовании операционного усилителя (ОУ). Эта схема выбрана в качестве аналога-прототипа заявляемого изобретения и изображена на фиг.2.

Схема ФКУ фиг.2 включает в себя: операционный усилитель ОУ1, конденсатор С1 и первый и второй резисторы R1 и R2; первый вывод резистора R1 и первый вывод резистора R2 соединены с линией управляющего напряжения Uупр; второй вывод резистора R1, первый вывод конденсатора С1 и неинвертирующий вход операционного усилителя ОУ1 соединены между собой; второй вывод резистора R2, инвертирующий вход операционного усилителя и выход операционного усилителя соединены между собой; второй вывод конденсатора С1 соединен с линией земли.

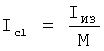

Примем допущение, что входное напряжение смещения и входные токи утечки операционного усилителя равны нулю. При этом напряжения на неинвертирующем входе и выходе ОУ1 равны и величины токов I1 и I2, протекающих через резисторы R1 и R2, обратно пропорциональны значениям их сопротивлений

.

.

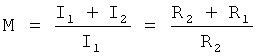

Соответствующим выбором отношения сопротивления резистора R1 к сопротивлению резистора R2, ток IC1, втекающий в конденсатор С1, по сравнению с током Iиз, втекающим в изодромное звено, может быть уменьшен с коэффициентом М

,

,

где  .

.

В результате, меньшее значение емкости конденсатора С1 может использоваться для замены большей эквивалентной емкости Сэкв фиг.1

СЭКВ=M×C1.

При этом Rэкв

RЭКВ=R1||R2.

Однако данная схема имеет недостатки. Первым недостатком является существенное увеличение суммарного значения RΣ сопротивлений резисторов R1 и R2 по сравнению с эквивалентным сопротивлением Rэкв заменяемого изодромного звена фиг.1. Причем чем с большим коэффициентом М значение С1 заменяет значение Сэкв, тем больше увеличивается RΣ

.

.

Вторым недостатком является невозможность осуществления быстрой перестройки напряжения на конденсаторе С1 для уменьшения времени переходного процесса автоподстройки частоты на этапе отработки контуром ФАПЧ больших фазовых рассогласований.

Техническим результатом настоящего изобретения является создание структуры интегрального ФКУ, занимающего меньшую площадь на кристалле микросхемы за счет уменьшения суммарного значения сопротивлений резисторов, и уменьшение времени переходного процесса в контуре ФАПЧ за счет увеличения скорости перестройки напряжения на конденсаторе изодромного звена ФКУ.

Указанный результат достигается тем, что в ФКУ, в состав которого входит: первый и второй резисторы, операционный усилитель и конденсатор; первый вывод первого резистора и первый вывод второго резистора соединены между собой; второй вывод первого резистора, первый вывод конденсатора и неинвертирующий вход операционного усилителя соединены между собой; второй вывод второго резистора, инвертирующий вход операционного усилителя и выход операционного усилителя соединены между собой; второй вывод конденсатора соединен с линией земли; предложено ввести третий резистор и управляемый элемент коммутации; первый вывод третьего резистора и первый вывод элемента коммутации соединены с линией управляющего напряжения; второй вывод третьего резистора соединен с первым выводом первого резистора; второй вывод элемента коммутации соединен со вторым выводом первого резистора; на вход управления элементом коммутации подается сигнал управления элементом коммутации.

В результате, за счет реализации части сопротивления Rэкв третьим резистором суммарное значение RΣ сопротивлений резисторов уменьшается по сравнению с RΣ изобретения [1]. Увеличение скорости перестройки напряжения на конденсаторе обеспечивается тем, что при замыкании элемента коммутации практически весь ток, втекающий в изодромное звено, втекает в данный конденсатор. В результате, скорость перезаряда конденсатора увеличивается почти в М раз по сравнению с изобретением [1]. При этом Сэкв уменьшается примерно до значения данного конденсатора, а Rэкв уменьшается примерно до значения сопротивления элемента коммутации в замкнутом состоянии.

Заявляемое изобретение иллюстрируется следующими графическими материалами:

Фиг.1 - типовая структурная схема системы импульсной ФАПЧ.

Фиг.2 - схема ФКУ, представленная в изобретении [1] и выбранная в качестве аналога-прототипа заявляемого изобретения.

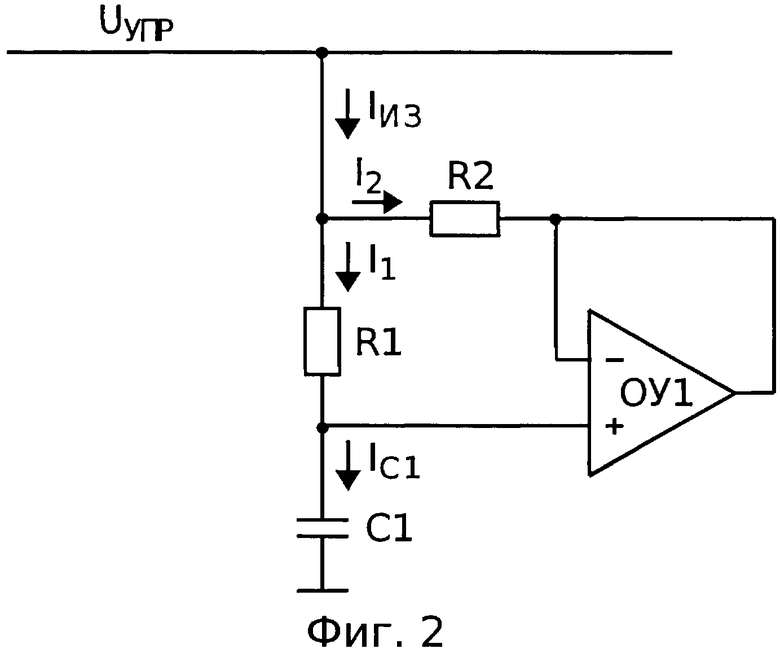

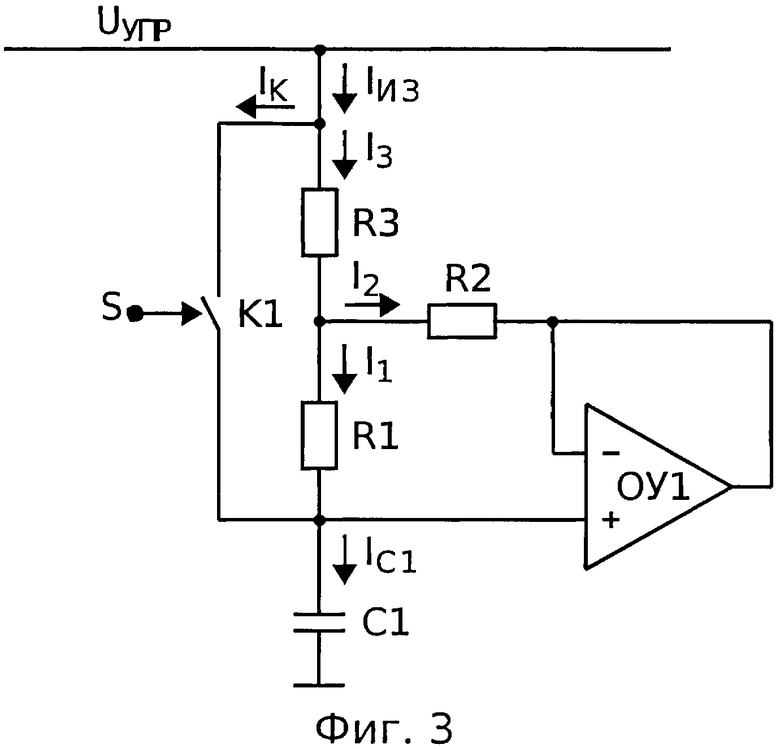

Фиг.3 - схема ФКУ, заявляемая в данном изобретении.

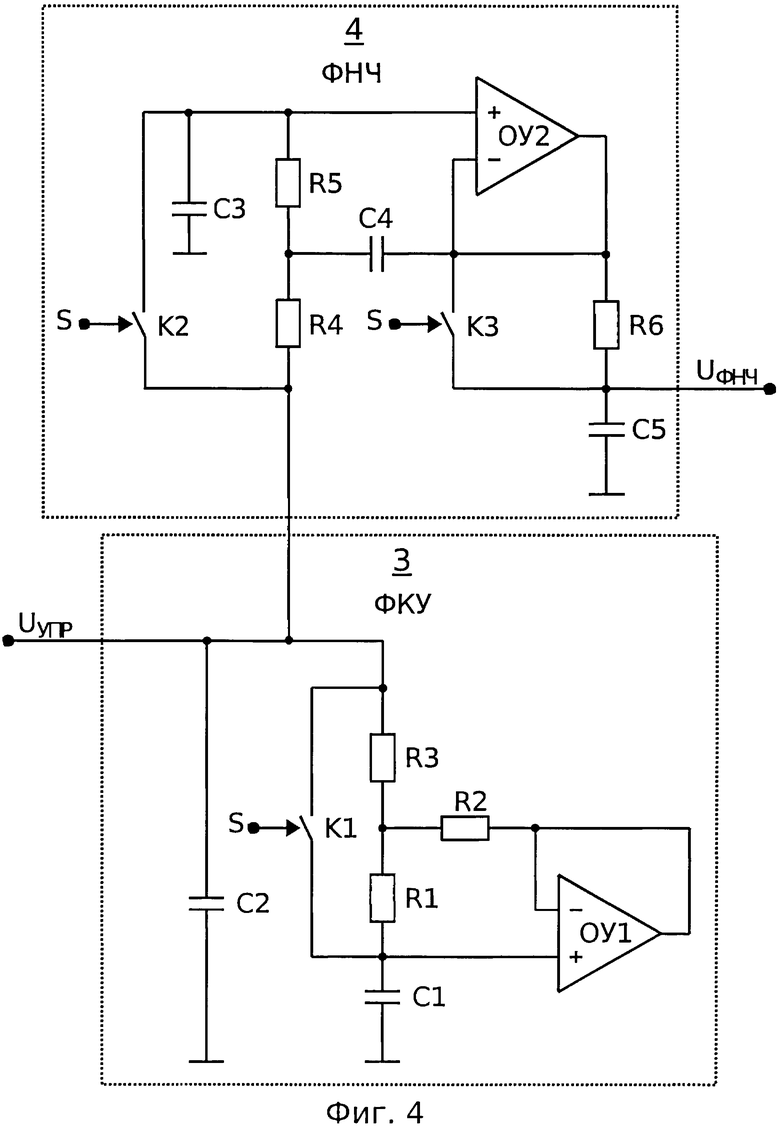

Фиг.4 - структурная схема практической интегральной реализации заявляемой схемы ФКУ и схемы ФНЧ.

Заявляемая в данном изобретении схема ФКУ представлена на фиг.3. В состав ФКУ входит: первый, второй и третий резисторы R1, R2, и R3, операционный усилитель ОУ1, конденсатор С1 и управляемый элемент коммутации К1; первый вывод первого резистора R1, первый вывод второго резистора R2 и второй вывод третьего резистора R3 соединены между собой; первый вывод элемента коммутации К1 и первый вывод третьего резистора R3 соединены с линией управляющего напряжения Uупр; второй вывод элемента коммутации К1, второй вывод первого резистора R1, первый вывод конденсатора С1 и неинвертирующий вход операционного усилителя ОУ1 соединены между собой; второй вывод второго резистора R2, инвертирующий вход операционного усилителя и выход операционного усилителя ОУ1 соединены между собой; второй вывод конденсатора С1 соединен с линией земли; на вход управления элементом коммутации К1 подается сигнал S управления элементом коммутации.

Элемент коммутации К1 может быть выполнен на N-канальном или P-канальном транзисторе или на комплементарной паре таких транзисторов, когда истоки Р и N-канальных транзисторов соединены и образуют 1-й вывод элемента коммутации, стоки Р и N-канальных транзисторов соединены и образуют 2-й вывод элемента коммутации, на затворы транзисторов подаются соответствующие сигналы управления.

Для схемы, представленной на фиг.3, формула расчета значения Сэкв совпадает с формулой расчета значения Сэкв фиг.2. При этом Rэкв

RЭКВ=RK||(R3+(R1||R2)),

где RK - значение сопротивления элемента коммутации К1. Если при разомкнутом состоянии элемента коммутации выполняется условие

RK>>R3+(R1||R2),

то RЭКВ= R3+(R1||R2).

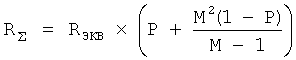

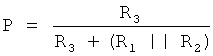

Технический результат заявляемого изобретения - уменьшение RΣ значения суммарного сопротивления резисторов R1, R2 и R3 обеспечивается пропорционально реализации части сопротивления Rэкв резистором R3

,

,

где  .

.

Таким образом, чем ближе коэффициент Р к единице, тем ближе RΣ к Rэкв. Значения резисторов R1, R2 и R3 выбираются такими, чтобы гарантировать требуемую точность установки Rэкв и коэффициента М с учетом технологических разбросов при производстве кристалла микросхемы.

Технический результат заявляемого изобретения - уменьшение времени переходного процесса в контуре ФАПЧ за счет увеличения скорости перестройки напряжения на конденсаторе С1 изодромного звена обеспечивается следующим образом. Ток IС1, протекающий через конденсатор С1, равен

,

,

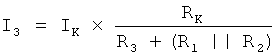

где I3 - ток через резистор R3, равный

,

,

где Iк - ток через элемент коммутации К1.

Отсюда

Для замкнутого состояния элемента коммутации не вызывает затруднений реализация следующего условия:

RK<0,1×(R3+(R1||R2)).

Таким образом, при замыкании элемента коммутации К1 практически весь ток Iиз, втекающий в изодромное звено, втекает в конденсатор С1. В результате, скорость перезаряда конденсатора С1 увеличивается почти в М раз по сравнению с изобретением [1]. При этом

СЭКВ≈С1,

RЭКВ≈RK.

На фиг.4 представлена структурная схема практической интегральной реализации заявляемой схемы 3 ФКУ и схемы 4 ФНЧ третьего порядка. Также как и в ФКУ, в данном ФНЧ используются элементы коммутации К2 и К3, управляемые тем же сигналом S, для быстрой перестройки управляющего напряжения Uфнч на выходе ФНЧ. Операционный усилитель ОУ1 и элементы С1, R1, R2 и R3 представляют собой изодромное звено, обеспечивающее точку нуля в передаточной функции системы. Конденсатор С2 обеспечивает точку полюса в передаточной функции системы. Операционный усилитель ОУ2 и элементы R4, R5, С3 и С4 представляют собой активный фильтр второго порядка, реализованный по схеме источника напряжения, управляемого напряжением. Пассивный фильтр первого порядка R6, С5 предназначен для уменьшения величины резонансного пика в полосе пропускания активного фильтра и усиления фильтрации в полосе подавления. Достижение высокой динамической точности контуром ФАПЧ во время переходного процесса автоподстройки частоты обеспечивается благодаря быстрой перестройке напряжения на конденсаторах ФКУ и ФНЧ. В установившемся режиме необходимое подавление помех, вызванных импульсным характером управления, обеспечивается характеристиками ФНЧ. В данном включении оба операционных усилителя используют однополярное питание, что является неотъемлемым требованием для большинства практических интегральных применений.

Однако область использования схемы ФКУ, представленной на фиг.3, не ограничивается только интегральными применениями. По принципу ее работы увеличение скорости перестройки напряжения на конденсаторе С1 изодромного звена осуществляется без увеличения выходного тока ИТПЗ, что является дополнительным преимуществом и делает эту схему удобной не только при полностью интегральной реализации устройства ФАПЧ, но также при реализации на отдельных компонентах.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство эквивалентного умножения емкости конденсатора петлевого фильтра контура ФАПЧ | 2015 |

|

RU2612573C1 |

| ИМПУЛЬСНЫЙ ЧАСТОТНО-ФАЗОВЫЙ ДЕТЕКТОР | 2012 |

|

RU2483434C1 |

| ИМПУЛЬСНЫЙ ЧАСТОТНО-ФАЗОВЫЙ ДЕТЕКТОР | 2013 |

|

RU2530248C1 |

| СИНТЕЗАТОР СЕТКИ ЧАСТОТ НА БАЗЕ КОНТУРА ФАПЧ С КОМПЕНСАЦИЕЙ ПОМЕХ ДРОБНОСТИ | 2012 |

|

RU2491713C1 |

| Устройство эквивалентного умножения емкости конденсатора петлевого фильтра контура ФАПЧ | 2022 |

|

RU2783664C1 |

| Синтезатор с коммутируемой полосой пропускания кольца фазовой автоподстройки частоты | 2023 |

|

RU2812098C1 |

| Синтезатор с коммутируемой полосой пропускания кольца фазовой автоподстройки частоты | 2024 |

|

RU2827940C1 |

| Устройство защиты радиоприема в условиях сложной электромагнитной обстановки корабля, судна | 2019 |

|

RU2723434C1 |

| УСТРОЙСТВО АВТОМАТИЧЕСКОГО КОНТРОЛЯ И ВЫРАВНИВАНИЯ СТЕПЕНИ ЗАРЯЖЕННОСТИ БЛОКА АККУМУЛЯТОРОВ КОМБИНИРОВАННОЙ ЭНЕРГЕТИЧЕСКОЙ УСТАНОВКИ | 2016 |

|

RU2626378C1 |

| УНИВЕРСАЛЬНЫЙ МОДУЛЬ ЧАСТОТНОГО ИНТЕГРИРУЮЩЕГО РАЗВЁРТЫВАЮЩЕГО ПРЕОБРАЗОВАТЕЛЯ ДЛЯ ДАТЧИКОВ ФИЗИЧЕСКИХ ВЕЛИЧИН | 2016 |

|

RU2631494C1 |

Изобретение относится к радиоэлектронике, а именно к фильтру контура управления (ФКУ), предназначенного для использования в составе устройства фазовой автоподстройки частоты (ФАПЧ). Технический результат - уменьшение времени переходного процесса в контуре ФАПЧ за счет быстрой перестройки напряжения на ФКУ и, в случае полностью интегральной реализации, уменьшение площади, занимаемой ФКУ на кристалле микросхемы. Достигается тем, что в схему ФКУ, содержащую операционный усилитель ОУ (1), конденсатор (С1) и резисторы (R1) и (R2), введены резистор (R3) и управляемый элемент коммутации (К1). При замыкании элемента коммутации (К1) происходит многократное увеличение тока перезаряда, текущего через конденсатор (С1), и тем самым обеспечивается увеличение скорости перестройки напряжения на ФКУ. За счет переноса на R3 части сопротивления (R1) и (R2) пропорционально уменьшается суммарное значение резисторов и, соответственно, площадь ФКУ, занимаемая на кристалле микросхемы. 4 ил.

Фильтр контура управления (ФКУ) для устройства фазовой автоподстройки частоты (ФАПЧ), содержащий: первый и второй резисторы, операционный усилитель и конденсатор; первый вывод первого резистора и первый вывод второго резистора соединены между собой; второй вывод первого резистора, первый вывод конденсатора и неинвертирующий вход операционного усилителя соединены между собой; второй вывод второго резистора, инвертирующий вход операционного усилителя и выход операционного усилителя соединены между собой; второй вывод конденсатора соединен с линией земли, отличающийся тем, что введены третий резистор и управляемый элемент коммутации; первый вывод третьего резистора и первый вывод элемента коммутации соединены с линией управляющего напряжения; второй вывод третьего резистора соединен с первым выводом первого резистора; второй вывод элемента коммутации соединен со вторым выводом первого резистора; на вход управления элементом коммутации подается сигнал управления элементом коммутации.

| Пресс для выдавливания из деревянных дисков заготовок для ниточных катушек | 1923 |

|

SU2007A1 |

| СИНТЕЗАТОР ЧАСТОТ С ПЕРЕМЕННЫМИ УСИЛЕНИЕМ И ПОЛОСОЙ ПРОПУСКАНИЯ КОЛЬЦА ФАЗОВОЙ АВТОПОДСТРОЙКИ | 2003 |

|

RU2267860C2 |

| US 6437615 B1, 20.08.2002 | |||

| EP 1487109 A1, 15.12.2004. | |||

Авторы

Даты

2011-06-27—Публикация

2010-02-09—Подача