Изобретение относится к радиоэлектронике, а именно к импульсному частотно-фазовому детектору (ИЧФД), предназначенному для использования в составе контура импульсной фазовой автоподстройки частоты (ФАПЧ).

При проектировании синтезаторов сетки частот (ССЧ) наибольшее распространение получили устройства на базе генератора, управляемого напряжением, частота и фаза выходного сигнала которого стабилизируются с помощью контура импульсной ФАПЧ. Контур ФАПЧ основан на синхронизации сигнала частоты, обратной связи к сигналу опорной частоты. Во множестве применений к ССЧ импульсной ФАПЧ предъявляются требования чрезвычайно высокого быстродействия. С этой целью при большом рассогласовании сигналов сравниваемых частот управление контуром ФАПЧ осуществляется только исходя из условия обеспечения предельного быстродействия, а затем, когда рассогласование снижено до достаточно малой величины управление изменяется в соответствии с требованиями к приемлемому окончанию переходных процессов.

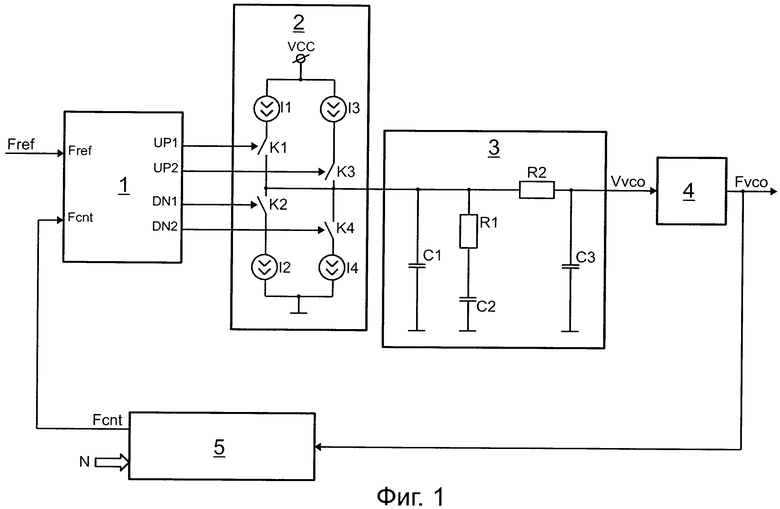

На фиг.1 представлена типовая структурная схема быстродействующего ССЧ на базе импульсной ФАПЧ с аналоговым фильтром в контуре управления, в которой реализуется частотно-фазовое регулирование по пропорционально-интегральному закону. Пропорциональная составляющая изменяется со скоростью изменения величины мгновенной ошибки, а интегральной составляющей (накопленному рассогласованию) свойственна задержка во времени.

В состав ССЧ входят следующие блоки:

1 - Импульсный частотно-фазовый детектор (ИЧФД).

2 - Блок управляемых источников тока накачки заряда (ИТНЗ), состоящий из собственно источников тока (ИТ) II - 14 и ключей К1 - К4 для подключения ИТ к выходу блока.

3 - Аналоговый фильтр контура управления (ФКУ), состоящий из накапливающего конденсатора С1, изодромного звена R1, C2 и фильтра низкой частоты (ФНЧ) R2, С3.

4 - Генератор, управляемый напряжением (ГУН).

5 - Делитель частоты (ДЧ) с коэффициентом деления N, устанавливаемым управляющим устройством.

Установка выходных сигналов ИЧФД UP1, UP2 или DN1, DN2 определяется знаком, а длительность - разностью фаз между фронтами сигналов сравниваемых частот Fref и Fcnt. Под управлением выходных сигналов ИЧФД источники тока противоположной направленности блока ИТПЗ либо отдают, либо принимают ток с конденсаторов схемы ФКУ, формируя на них соответствующий потенциал напряжения Vvco. Таким образом, осуществляется преобразование интервалов времени рассогласования сигналов Fref и Fcnt в изменения сигнала управляющего напряжения ГУН. Управление производится таким образом, чтобы устранить фазовую ошибку между фронтами импульсов Fref и Fcnt, и, тем самым, ввести контур ФАПЧ в синхронизм. Умножение входной опорной частоты Fref до значения выходной частоты Fvco обеспечивается делением частоты Fvco на соответствующий коэффициент N (сигнал Fcnt). В установившемся режиме длительность импульсов на выходе ИЧФД, а значит, и импульсов тока ИТНЗ, приближается к нулю. При этом конденсаторы ФКУ работают как элементы запоминания, сохраняя напряжение Vvco, поддерживающее требуемую частоту и фазу ГУН.

Параметры элементов изодромного звена ФКУ R1, C2 задают точку нуля передаточной функции контура управления ФАПЧ, тем самым осуществляя его частотную коррекцию с целью обеспечения устойчивости, приемлемой длительности и колебательности переходных процессов автоматической подстройки частоты и фазы ГУН. ФНЧ осуществляет подавление шумов, вызванных импульсным характером управления в контуре, но при этом вносит в него дополнительную инерционность. Параметры элементов ФНЧ R2, С3 и накапливающего конденсатора С1 задают точку полюса передаточной функции контура ФАПЧ.

С целью сокращения длительности переходных процессов, в контуре ФАПЧ, в зависимости от величины фазового рассогласования сигналов сравниваемых частот Fref и Fcnt, используются режимы фазового и частотного регулирования. При рассогласовании менее ±2π радиан ИЧФД осуществляет фазовое детектирование, а при рассогласовании более ±2π радиан - частотное детектирование. Режим частотного регулирования позволяет устранить биения в управлении (циклы проскальзывания) при больших рассогласованиях между сигналами сравниваемых частот. Переход в частотный режим происходит после прихода подряд второго импульса Fref или Fcnt. Дополнительно, в частотном режиме работы величина тока на выходе блока ИТНЗ формируется параллельным включением двух ИТ по сигналам UP1 и UP2 или DN1 и DN2. В результате значение тока по модулю становится больше, чем при фазовом регулировании. Это ведет к ускорению перезаряда конденсаторов ФКУ и сокращению длительности переходных процессов.

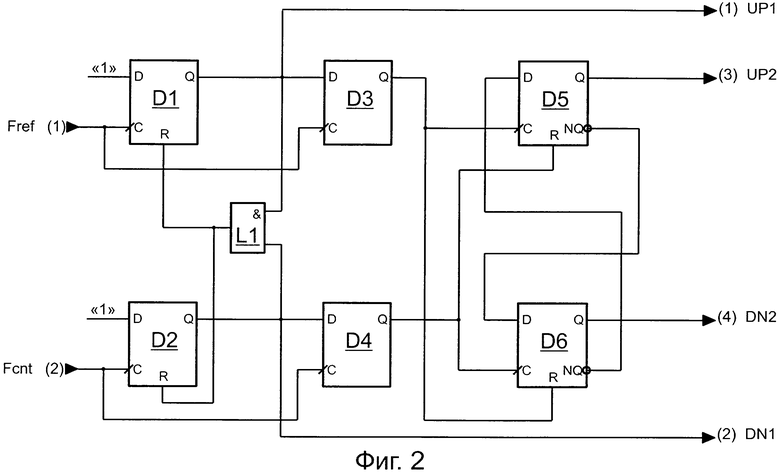

Наиболее близким техническим решением к заявляемому изобретению является схема ИЧФД, описанная в патенте Российской Федерации №2012992 (С1) «Импульсный Частотно-Фазовый Детектор», МПК H03D 13/00 [1]. Эта схема выбрана в качестве прототипа заявляемого изобретения и изображена на фиг.2.

Общим признаком с заявляемым изобретением является то, что при превышении разности фаз входных сравниваемых сигналов значения ±2π радиан, схема изобретения [1] вырабатывает сигналы для включения дополнительных ИТ.

Схема ИЧФД изобретения [1] имеет: первый (Fref) и второй (Fcnt) входы; первый (UP1), второй (DN1), третий (UP2) и четвертый (DN2) выходы; первый (D1), второй (D2), третий (D3), четвертый (D4) пятый (D5) и шестой (D6) запоминающие элементы и логический элемент (L1). Запоминающие элементы имеют входы и выходы, обозначенные как: информационный вход - «D», информационный выход - «Q», инвертированный информационный выход - «NQ», тактовый вход - «С», установочный вход - «R».

Информационные входы элементов D1 и D2 подключены к уровню «лог.1». Тактовые входы элементов D1 и D3 соединены между собой и подключены к входу Fref устройства. Тактовые входы элементов D2 и D4 соединены между собой и подключены к входу Fcnt устройства. Информационный выход элемента D1 и информационный вход элемента D3 соединены между собой и подключены к выходу UP1 устройства. Информационный выход элемента D2 и информационный вход элемента D4 соединены между собой и подключены к выходу DN1 устройства. Информационный выход элемента D5 подключен к выходу UP2 устройства. Информационный выход элемента D6 подключен к выходу DN2 устройства. Установочные входы элементов D1 и D2 соединены между собой и подключены к выходу элемента L1. Входы элемента L1 соединены с информационными выходами элементов D1 и D2. Тактовый вход элемента D5 и установочный вход элемента D6 соединены между собой и подключены к информационному выходу элемента D3. Тактовый вход элемента D6 и установочный вход элемента D5 соединены между собой и подключены к информационному выходу элемента D4. Информационный вход элемента D5 соединен с инвертированным информационным выходом элемента D6. Информационный вход элемента D6 соединен с инвертированным информационным выходом элемента D5.

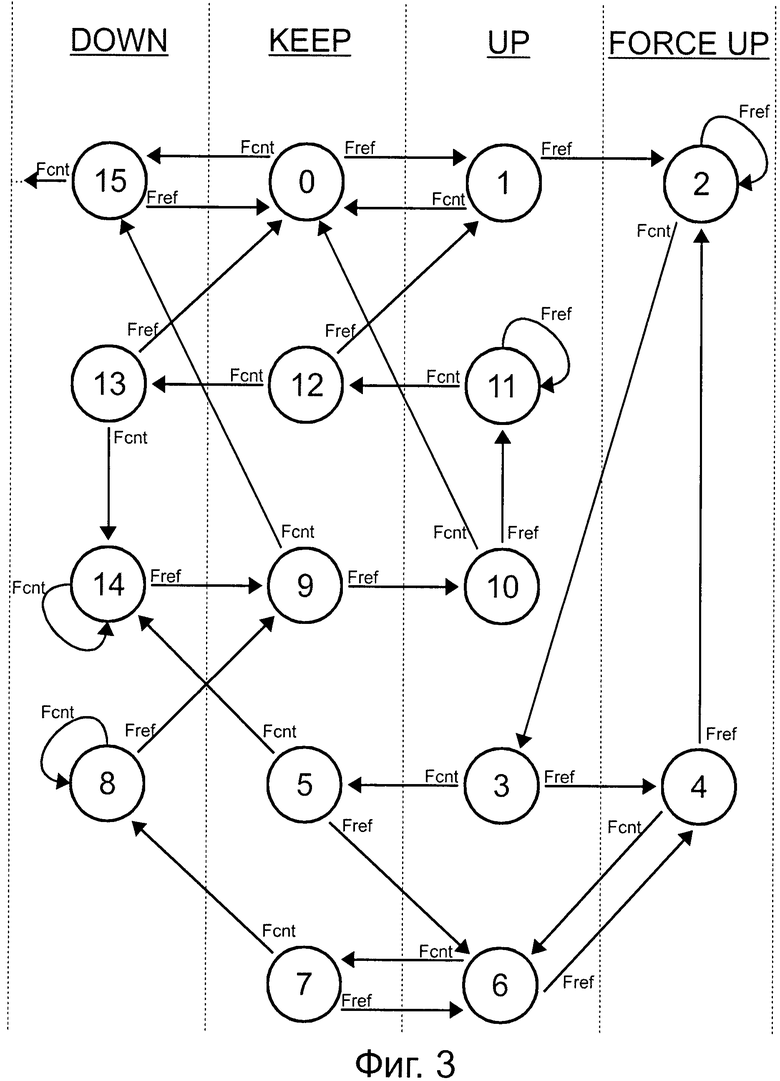

На фиг.3 представлен алгоритм работы схемы ИЧФД изобретения [1] в форме направленного графа, по которому можно проследить закономерности переходов его состояний. Группа состояний соответствующая режиму хранения заряда в ФКУ обозначена как «KEEP». Заряд и разряд конденсаторов ФКУ в режиме фазового регулирования осуществляется в соответствующих состояниях обозначенных как «UP» и «DOWN». Ускоренный заряд и разряд конденсаторов ФКУ увеличенным значением тока в режиме частотного регулирования осуществляется в состояниях обозначенных как «FORCE UP» и «FORCE DOWN». Для упрощения, детально показана только правая часть графа переходов. Так как схема ИЧФД симметричная, то для левой части будут соответственно симметричные состояния и условия переходов.

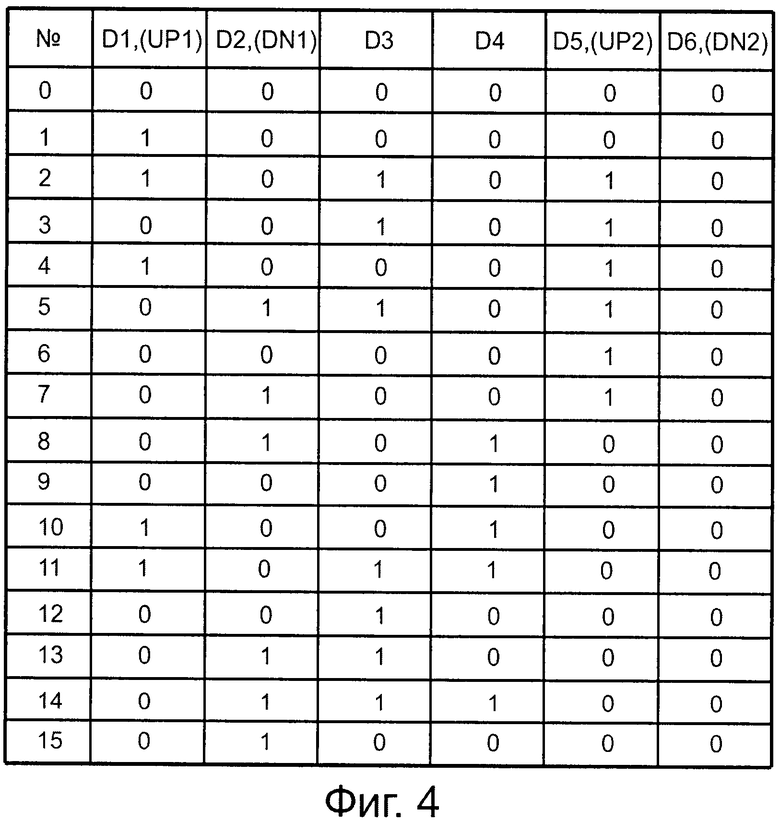

На фиг.4 представлена таблица состояний схемы ИЧФД изобретения [1] для соответствующих состояний графа переходов фиг.3. В состояниях 2 и 4 (FORCE UP) осуществляется частотный режим регулирования контуром ФАПЧ, при котором одновременно вырабатываются сигналы UP1 и UP2. При этом происходит ускоренный заряд конденсаторов ФКУ суммарным током ИТ одной направленности I1 и I3.

Схема ИЧФД изобретения [1] имеет следующие недостатки.

Первым недостатком является то, что в режиме хранения заряда в ФКУ схема ИЧФД имеет состояния (5 и 7), в которых одновременно вырабатываются сигналы DN1 и UP2, включающие ИТ с разной направленностью тока (12 и 13). Для сохранения значения заряда в ФКУ это потребует абсолютного согласования ИТ, что является проблемой при практической реализации. Невозможность абсолютного согласования ИТ делает невозможным сохранение заряда в ФКУ, что будет изменять частоту ГУН, т.е. это неустойчивые состояния хранения. Противодействуя этому изменению, контур ФАПЧ будет возвращать частоту ГУН обратно к требуемому значению постоянной выработкой соответствующих импульсов тока ИТНЗ, что приведет к увеличению фазового шума в выходной частоте ГУН. Кроме того, требование равенства токов I2 и I3 (по модулю) ограничивает возможности ускоренного перезаряда конденсаторов ФКУ в режиме частотного регулирования.

Вторым недостатком является то, что схема ИЧФД имеет состояния (8, 11 и 14), в которых повторение входного сигнала (т.е. дальнейшее увеличение фазового рассогласования) не приводит к включению дополнительного ИТ. Так в состоянии 8 и 14 повторение Fcnt не приводит к выработке сигнала DN2 и включению I4, а в состоянии 11 повторение Fref не приводит к выработке сигнала UP2 и включению I3. Наличие состояний не включения дополнительных ИТ при больших фазовых рассогласованиях приводят к затягиванию переходных процессов в контуре ФАПЧ.

Третьим недостатком является то, что схема ИЧФД имеет не оптимальный, с точки зрения сокращения длительности переходных процессов, алгоритм перевода контура ФАПЧ из состояний с двумя включенными ИТ (частотного регулирования) в состояния хранения заряда в ФКУ. Переход осуществляется только через состояния с одним включенным ИТ (фазового регулирования). В результате, на все время перехода сохраняется воздействие тока блока ИТНЗ на конденсаторы ФКУ. Например, если схема перешла в состояния 2 или 4, то только пришедшие подряд два импульса сигнала Fcnt вернут ее в состояния хранения заряда 5 или 7, являющиеся, к тому же, неустойчивыми состояниями. Учитывая, что сигналы Fref и Fcnt еще не синхронизированы, при наихудшем сочетании их фаз, частоты этих сигналов могут стать отличными друг от друга в два раза. Следствием такой «инерционности» графа переходов ИЧФД будут большое перерегулирование и соответственно длительность переходных процессов в контуре ФАПЧ.

В связи с тем, что граф состояний схемы ИЧФД изобретения [1] симметричный, те же самые недостатки будут и для левой его части (не показанной на фиг.3).

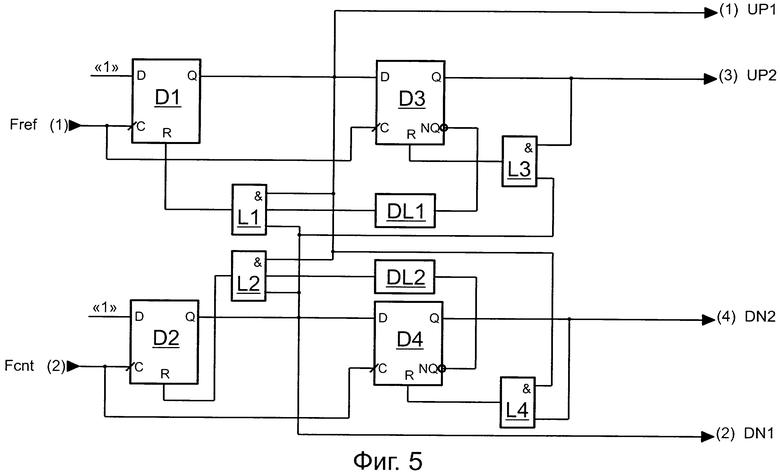

Также известна схема ИЧФД, описанная в патенте США №6617884 (В2) «Fast Locking Phase Frequency Detector», МПК H03D 13/00 [2], представленная на фиг.5.

Общим признаком с заявляемым изобретением является то, что при превышении разности фаз входных сравниваемых сигналов значения ±2π радиан, схема изобретения [2] вырабатывает сигналы для включения дополнительных ИТ.

Схема имеет: первый (Fref) и второй (Fcnt) входы; первый (UP1), второй (DN1), третий (UP2) и четвертый (DN2) выходы; первый (D1), второй (D2), третий (D3) и четвертый (D4) запоминающие элементы; первый (L1), второй (L2), третий (L3) и четвертый (L4) логические элементы; первый (DL1) и второй (DL2) элементы задержки. Запоминающие элементы имеют входы и выходы обозначенные как: информационный вход - «D», информационный выход - «Q», инвертированный информационный выход - «NQ», тактовый вход - «С», установочный вход - «R».

Информационные входы элементов D1 и D2 подключены к уровню «лог.1. Тактовые входы элементов D1 и D3 соединены между собой и подключены к входу Fref устройства. Тактовые входы элементов D2 и D4 соединены между собой и подключены к входу Fcnt устройства. Информационный выход элемента D1 и информационный вход элемента D3 соединены между собой и подключены к выходу UP1 устройства. Информационный выход элемента D2 и информационный вход элемента D4 соединены между собой и подключены к выходу DN1 устройства. Информационный выход элемента D3 подключен к выходу UP2 устройства. Информационный выход элемента D4 подключен к выходу DN2 устройства. Выход элемента L1 соединен с установочным входом элемента D1, а входы элемента L1 соединены с информационными выходами элементов D1, D2 и с выходом элемента DL1. Выход элемента L2 соединен с установочным входом элемента D2, а входы элемента L2 соединены с информационными выходами элементов D1, D2 и с выходом элемента DL2. Входы элементов DL1 и DL2 соединены с инвертированными информационными выходами элементов D3 и D4 соответственно. Выход элемента L3 соединен с установочным входом элемента D3, а входы элемента L3 соединены с информационными выходами элементов D2 и D3. Выход элемента L4 соединен с установочным входом элемента D4, а входы элемента L4 соединены с информационными выходами элементов D1 и D4.

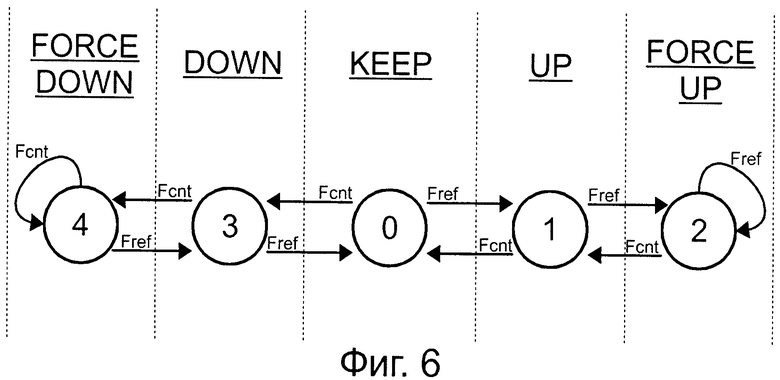

На фиг.6 представлен алгоритм работы схемы ИЧФД изобретения [2] в форме направленного графа, по которому можно проследить закономерности переходов его состояний.

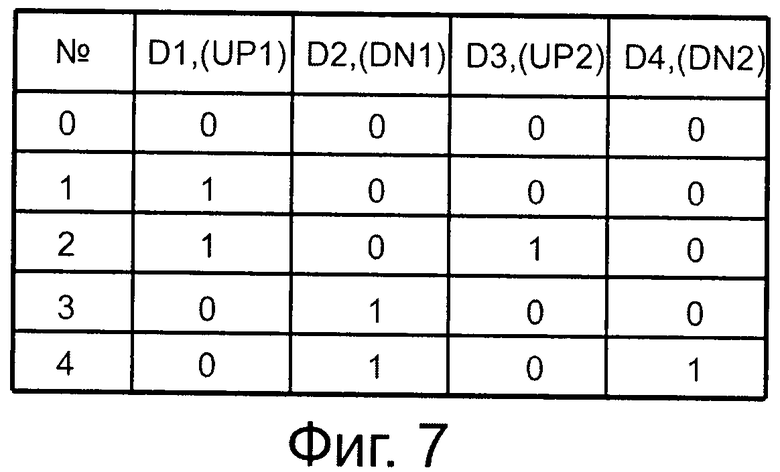

На фиг.7 представлена таблица состояний схемы ИЧФД изобретения [2] для соответствующих состояний графа переходов фиг.6.

Схема ИЧФД изобретения [2] не имеет первых двух недостатков схемы изобретения [1], но сохраняется недостаток, заключающийся в не оптимальности («инерционности») при переводе контура ФАПЧ из состояний с двумя включенными ИТ (частотного регулирования) в состояния хранения заряда в ФКУ происходящем только через состояния с одним включенным ИТ (фазового регулирования). Например, если ИЧФД находится в состоянии 2, то только пришедшие подряд два импульса сигнала Fcnt вернут схему в состояние 0. Если ИЧФД находится в состоянии 4, то только пришедшие подряд два импульса сигнала Fref вернут схему в состояние 0. Так же как и в изобретении [1], при наихудшем сочетании фаз сигналов Fref и Fcnt их частоты могут стать отличными друг от друга в два раза, что приводит к большому перерегулированию и длительности переходных процессов в контуре ФАПЧ.

Техническим результатом настоящего изобретения является уменьшение времени переходных процессов в ССЧ на базе контура импульсной ФАПЧ за счет оптимизации алгоритма формирования управляющих сигналов схемой ИЧФД.

Указанный технический результат достигается за счет того, что в схеме ИЧФД, описанной в изобретении [1], имеющей первый и второй входы; первый, второй, третий и четвертый выходы; первый, второй, третий, четвертый, пятый и шестой запоминающие элементы и первый логический элемент; тактовые входы первого и третьего запоминающих элементов соединены между собой и подключены к первому входу устройства; тактовые входы второго и четвертого запоминающих элементов соединены между собой и подключены ко второму входу устройства; информационный выход первого и информационный вход третьего запоминающих элементов и первый вход первого логического элемента соединены между собой и подключены к первому выходу устройства; информационный выход второго и информационный вход четвертого запоминающих элементов и второй вход первого логического элемента соединены между собой и подключены к второму выходу устройства; установочные входы первого и второго запоминающих элементов соединены между собой и подключены к выходу первого логического элемента; информационный вход второго запоминающего элемента подключен к уровню логической единицы, предложено ввести второй логический элемент; тактовые входы пятого и шестого запоминающих элементов соединить между собой и подключить к первому входу устройства; информационный выход третьего запоминающего элемента подключить к третьему выходу устройства; выход второго логического элемента подключить к четвертому выходу устройства; информационный вход первого и установочный вход пятого запоминающих элементов соединить между собой и подключить к инвертированному информационному выходу четвертого запоминающего элемента; установочные входы третьего и шестого запоминающих элементов соединить между собой и подключить к выходу первого логического элемента; установочный вход четвертого и информационный выход пятого запоминающих элементов соединить между собой; первый вход второго логического элемента и информационный вход шестого запоминающего элемента соединить между собой и подключить к информационному выходу четвертого запоминающего элемента; второй вход второго логического элемента и информационный выход шестого запоминающего элемента соединить между собой; информационный вход пятого запоминающего элемента подключить к уровню логической единицы.

В результате заявляемая схема ИЧФД осуществляет выработку сигналов управления переводящих контур ФАПЧ из состояний с двумя включенными ИТ (частотного регулирования) в состояния хранения заряда в ФКУ, минуя состояния с одним включенным ИТ (фазового регулирования), т.е. без инерции сохранения воздействия на ФКУ тока ИТНЗ. В случае последующего ввода контура ФАПЧ в режим фазового регулирования, управление начнется с наиболее благоприятных, с точки зрения быстрого окончания переходного процесса, траекторий фазового пространства.

Заявляемое изобретение иллюстрируется следующими графическими материалами:

Фиг.1. Типовая структурная схема быстродействующего ССЧ на базе контура импульсной ФАПЧ с аналоговым фильтром в контуре управления.

Фиг.2. Схема ИЧФД, представленная в изобретении [1] и выбранная в качестве аналога-прототипа заявляемого изобретения.

Фиг.3. Алгоритм работы схемы ИЧФД изобретения [1] в форме направленного графа.

Фиг.4. Таблица состояний схемы ИЧФД изобретения [1] для соответствующих состояний графа переходов фиг.3.

Фиг.5. Схема ИЧФД, представленная в изобретении [2].

Фиг.6. Алгоритм работы схемы ИЧФД изобретения [2] в форме направленного графа.

Фиг.7. Таблица состояний схемы ИЧФД изобретения [2] для соответствующих состояний графа переходов фиг.6.

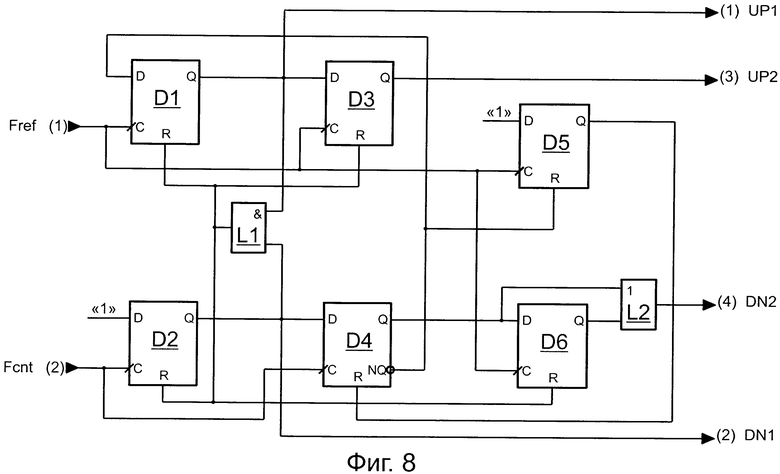

Фиг.8. Схема ИЧФД, заявляемая в данном изобретении.

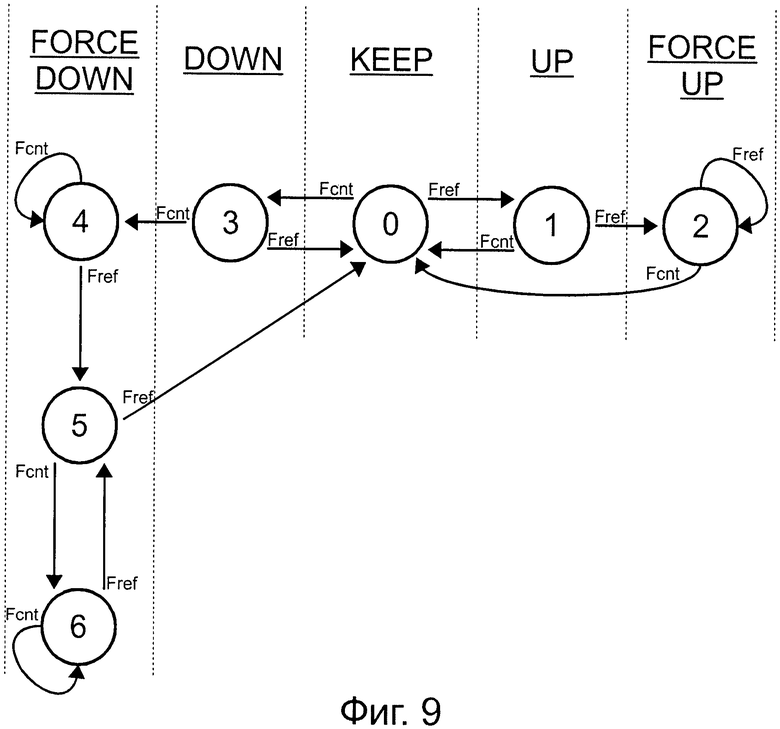

Фиг.9. Алгоритм работы схемы ИЧФД, заявляемой в данном изобретении, в форме направленного графа.

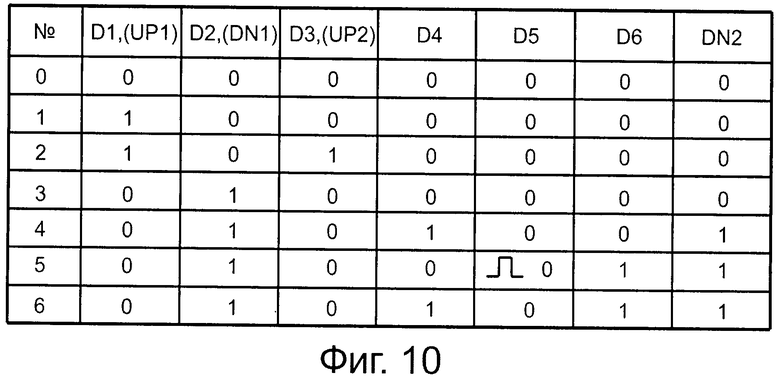

Фиг.10. Таблица состояний схемы ИЧФД, заявляемой в данном изобретении, для соответствующих состояний графа переходов фиг.9.

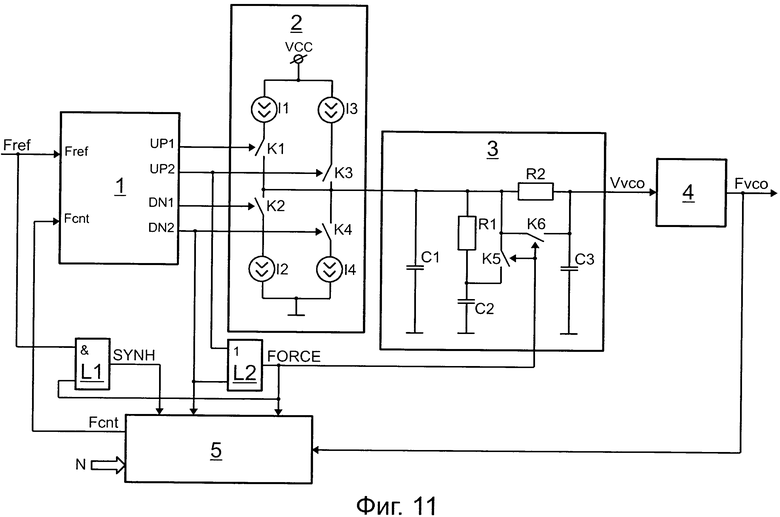

Фиг.11. Структурная схема быстродействующего ССЧ на базе контура импульсной ФАПЧ с аналоговым фильтром в контуре управления и с использованием схемы ИЧФД, заявляемой в данном изобретении.

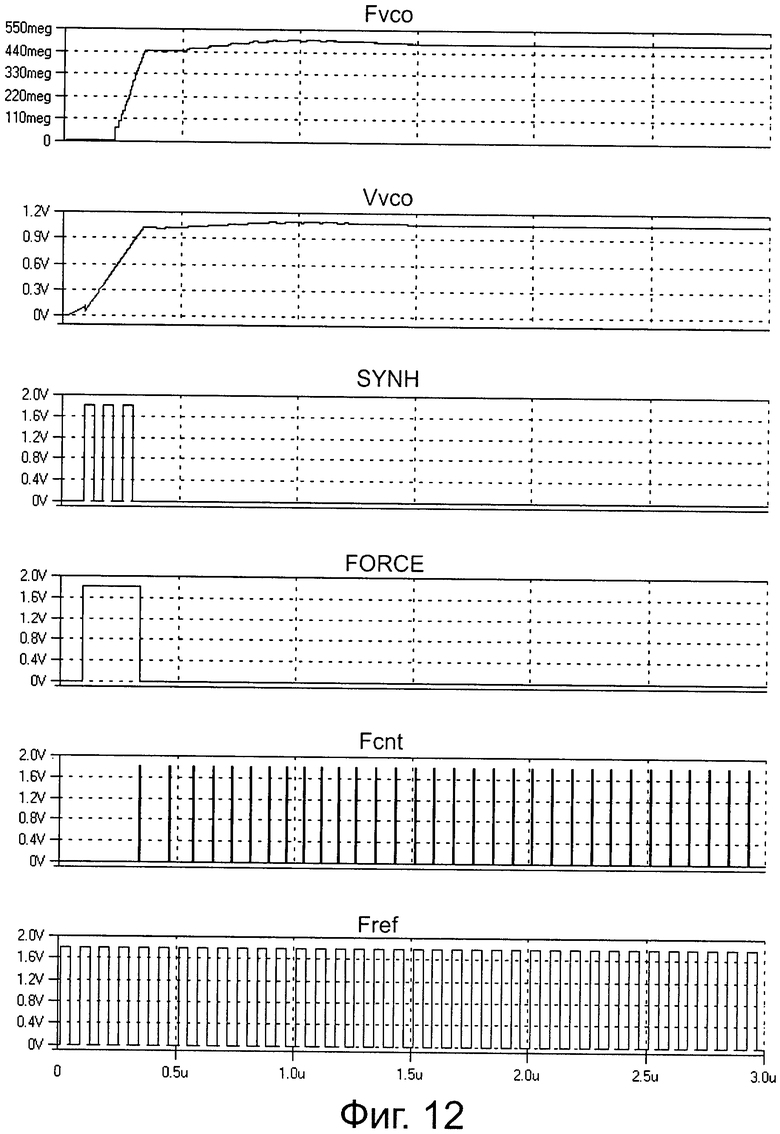

Фиг.12. Результаты математического моделирования работы ССЧ во время переходного процесса по включению питания.

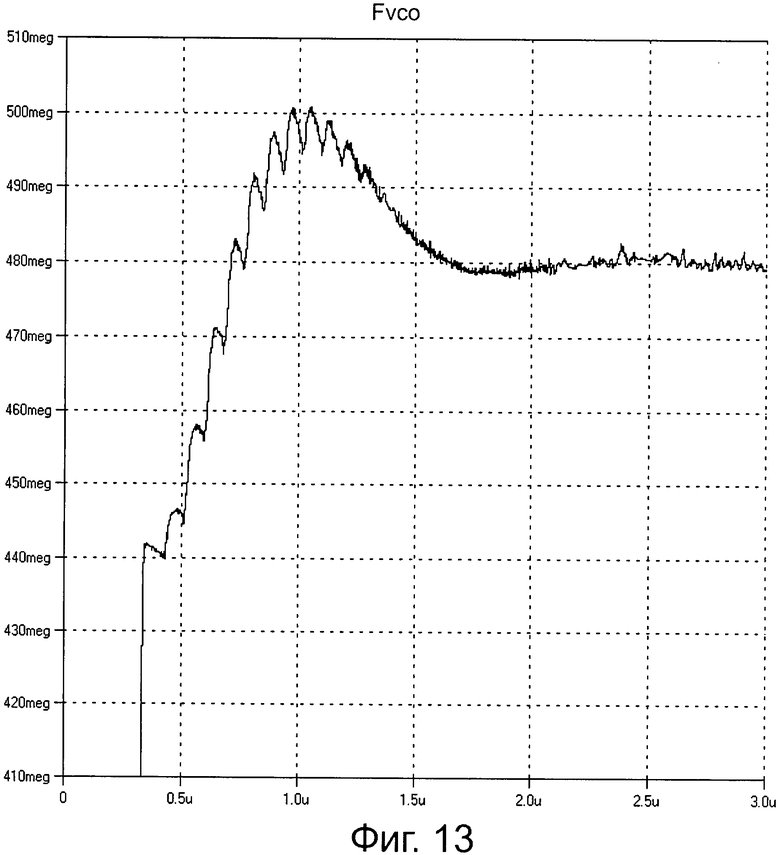

Фиг.13. Увеличенный масштаб окончания переходного процесса установления выходной частоты ССЧ.

Заявляемая в данном изобретении схема ИЧФД представлена на фиг.8. Схема ИЧФД имеет: первый (Fref) и второй (Fcnt) входы; первый (UP1), второй (DN1), третий (UP2) и четвертый (DN2) выходы; первый (D1), второй (D2), третий (D3), четвертый (D4) пятый (D5) и шестой (D6) запоминающие элементы; первый (L1) и второй (L2) логические элементы. Запоминающие элементы имеют входы и выходы, обозначенные как: информационный вход - «D», информационный выход - «Q», инвертированный информационный выход - «NQ», тактовый вход - «С», установочный вход - «R».

Тактовые входы элементов D1, D3, D5 и D6 соединены между собой и подключены к входу Fref устройства. Тактовые входы элементов D2 и D4 соединены между собой и подключены к входу Fcnt устройства. Информационный выход элемента D1, информационный вход элемента D3 и первый вход элемента L1 соединены между собой и подключены к выходу UP1 устройства. Информационный выход элемента D2, информационный вход элемента D4 и второй вход элемента L1 соединены между собой и подключены к выходу DN1 устройства. Информационный выход элемента D3 подключен к выходу UP2 устройства. Выход элемента L2 подключен к выходу DN2 устройства. Информационный вход элемента D1, инвертированный информационный выход элемента D4 и установочный вход элемента D5 соединены между собой. Установочные входы элементов D1, D2, D3 и D6 и выход элемента L1 соединены между собой. Установочный вход элемента D4 и информационный выход элемента D5 соединены между собой. Первый вход элемента L2, информационный выход элемента D4 и информационный вход элемента D6 соединены между собой. Второй вход элемента L2 и информационный выход элемента D6 соединены между собой. Информационные входы элементов D2 и D5 подключены к уровню «лог.1».

На фиг.9 представлен алгоритм работы в форме направленного графа схемы ИЧФД, заявляемой в данном изобретении.

На фиг.10 представлена таблица состояний схемы ИЧФД, заявляемой в данном изобретении, для соответствующих состояний графа переходов фиг.9.

Алгоритм формирования управляющих сигналов ИЧФД, осуществляющих перевод контура импульсной ФАПЧ из состояний с двумя включенными ИТ (частотного регулирования) в состояния хранения заряда, минуя состояния с одним включенным ИТ (фазового регулирования), реализуется следующим образом.

Состояния элементов D1 и D2 находятся в логической взаимосвязи через элемент L1, исключающий одновременное нахождение элементов D1 и D2 в состоянии «лог.1». В случае нахождения схемы ИЧФД в состоянии 2 (усиленный заряд конденсаторов ФКУ) приход фронта сигнала Fcnt переведет элементы схемы ИЧФД в состояние 0 (хранение заряда в ФКУ). Состояния элементов D4 и D5 находятся в логической взаимосвязи. Нахождение элемента D4 в состоянии «лог.0» (все состояния графа переходов, кроме 4 и 6) блокирует установку в «лог.1» элемента D5. Если элемент D4 находится, состоянии «лог.1», то по переднему фронту сигнала Fref элемент D5 устанавливается в состояние «лог.1», тем самым устанавливая элемент D4 в состояние «лог.0». После этого инвертированный информационный выход элемента D4 устанавливает элемент D5 обратно в состояние «лог.О», что, в свою очередь, разрешает работу элемента D4. При выполнении усиленного разряда конденсаторов ФКУ, если ИЧФД находится в состояниях 4 или 6, то с инвертированного информационного выхода элемента D4 на информационный вход элемента D1 подан уровень «лог.0», что блокирует установку элемента D1 в состояние «лог.1» по фронту сигнала Fref и переход схемы ИЧФД в состояние 0. Приход переднего фронта сигнала Fref установит элемент D6 в состояние «лог.1», схема ИЧФД перейдет в состояние 5. При этом сигналы DN1 и DN2 останутся активными, а элемент D4 сбросится в состояние «лог.0», тем самым разрешая работу элемента D1. Если выходная частота ГУН снизилась так, что раньше сигнала Fcnt опять приходит сигнал Fref, то ИЧФД перейдет в состояние 0. Если же в состоянии 5 опять придет сигнал Fcnt, то ИЧФД перейдет в состояние 6, функционально аналогичное состоянию 4. Таким образом, состояние 5 необходимо для сохранения величины выходного тока ИТНЗ, равного I2+I4 для усиленного разряда конденсаторов ФКУ (до прихода следующего фронта Fref).

При входе графа состояний ИЧФД в режим частотного регулирования и при нахождении в этом режиме по импульсам сигнала Fref в контуре ФАПЧ осуществляется подсинхронизация ДЧ, описанная ниже в примере практического применения.

На фиг.11 представлена структурная схема быстродействующего ССЧ на базе контура импульсной ФАПЧ с аналоговым фильтром в контуре управления и с использованием схемы ИЧФД, заявляемой в данном изобретении.

В представленном ССЧ для сокращения величины перерегулирования и длительности переходных процессов, при нахождении контура ФАПЧ в режиме частотного регулирования дополнительно к увеличению выходного тока блока ИТНЗ используются:

- коммутация цепей в ФКУ для безынерционной установки потенциалов напряжения на входящих в состав ФКУ конденсаторах;

- упреждение вывода контура ФАПЧ из режима частотного регулирования;

- подсинхронизация ДЧ.

В случае установки в активное состояние выходных сигналов ИЧФД UP2 или DN2 логический элемент L2 схемы ССЧ вырабатывает сигнал режима частотного регулирования (FORCE). По сигналу FORCE ключи K5 и K6 коммутацией соответствующих цепей шунтируют резисторы R1 и R2 ФКУ. Вместе с увеличением значения выходного тока блока ИТНЗ это обеспечивает быстрое изменение потенциалов напряжения Vvco на конденсаторах ФКУ, вследствие чего ГУН быстро входит в область выходных частот, близких к требуемым.

В связи с тем, что наличие делителя частоты в цепи обратной связи вносит дополнительную инерционность в контур ФАПЧ, необходимо сдвинуть в сторону опережения момент вывода контура из частотного режима регулирования. Реализуется опережение делением выходной частоты ГУН на значение, отличное от значения N в установившемся режиме, но обеспечивающее необходимое упреждение. Соответствующая коммутация в ДЧ осуществляется по сигналу FORCE. В зависимости от того, в какой области частотного регулирования (UP или DOWN) находится контур, деление осуществляется на коэффициент упреждения соответственно меньше или больше требуемого N. Введение упреждения по характеру действия аналогично введению дифференциальной составляющей в пропорционально-интегральное управление.

Для улучшения условий захвата фазы, осуществляегся подсинхронизация ДЧ по импульсам сигнала опорной частоты Fref (SYNH). Благодаря такому автофазированию перевод контура ФАПЧ в режим фазового регулирования произойдет сразу, как только частота Fcnt превысит частоту Fref (при перестройке ССЧ по частоте вверх) или как только Fcnt станет ниже Fref (при перестройке по частоте вниз).

В качестве примера на фиг.12 представлены результаты математического моделирования переходного процесса в ССЧ при синтезе сигнала частотой 480 МГц при значении опорной частоты 12 МГц. По диаграммам можно сделать выводы о качестве управления, оценить значения перерегулирования и длительности переходного процесса.

При превышении значения фазового рассогласования на величину 2π радиан (по второму такту сигнала опорной частоты Fref) контур переходит в частотный режим регулирования с установкой сигнала FORCE и включением второго ИТ (состояние 2 графа переходов фиг.9). При этом управляющее напряжение Vvco, а следовательно, и значение выходной частоты Fvco, начинают быстро увеличиваться. По фронту сигнала SYNH происходит подсинхронизация ДЧ. Момент приближения выходной частоты ГУН к значениям, близким к требуемым, определяется переполнением ДЧ, осуществляющим подсчет импульсов частоты Fvco до значения упреждения. В результате, значение частоты Fvco увеличивается настолько, что подсинхронизированный ДЧ вырабатывает сигнал переполнения Fcnt до прихода импульса Fref. Происходит переход контура в режим хранения заряда в ФКУ. Далее, до окончания переходного процесса, контур будет переключаться между состояниями фазового регулирования. Задержка начала переходного процесса у диаграммы, показывающей значение частоты Fvco, объясняется необходимостью заряда конденсаторов ФКУ до уровня рабочего диапазона входного управляющего напряжения ГУН.

На фиг.13 представлено окончание переходного процесса установления выходной частоты Fvco в увеличенном масштабе. Пререгулирование не превысило 4,4%. Длительность переходного процесса до установления синтезируемой частоты с точностью ±0,5% составила 20 тактов опорной частоты Fref.

Представленные диаграммы подтверждают возможность получения высокого быстродействия в ССЧ на базе контура импульсной ФАПЧ с использованием заявляемой схемы ИЧФД. В начале переходного процесса контур ФАПЧ ведет себя как оптимальная по быстродействию релейная система, замкнутая по частоте, с использованием подсинхронизации контура обратной связи, упреждения и быстрой установкой потенциалов напряжения в ФКУ. Такое управление позволяет приблизиться к управлению, оптимальному по быстродействию, и предложенная схема ИЧФД с «безынерционным» алгоритмом перехода из состояний частотного регулирования в состояние хранения может быть рекомендована к внедрению при разработке ССЧ с требованиями высокой скорости перестройки значений синтезируемых частот.

Описанная схема ИЧФД может иметь различные варианты своей реализации в зависимости от используемого схемотехнического базиса запоминающих и логических элементов, с сохранением заданной функциональности схемы в целом. Также в описанной схеме возможны изменения, не имеющие принципиального влияния на алгоритм ее работы. Например, информационный вход элемента D5 может быть подключен не к уровню «лог.1», а к информационному выходу элемента D4. Кроме того, в схеме ССЧ фиг.11 возможны различные реализации схем изодромного звена и ФНЧ (например, активные схемы на операционных усилителях), важно, чтобы под воздействием управляющего сигнала (FORCE) они имели возможность быстрой предустановки потенциалов контролируемого напряжения.

Изобретение относится к радиоэлектронике, а именно к импульсному частотно-фазовому детектору. Техническим результатом является уменьшение времени переходных процессов в контуре фазовой автоподстройки частоты за счет оптимизации алгоритма формирования выходных управляющих сигналов импульсного частотно-фазового детектора. Схема импульсного частотно-фазового детектора содержит первый, второй, третий, четвертый, пятый и шестой запоминающие элементы, первый и второй логические элементы, а переход контура фазовой автоподстройки частоты из состояний частотного регулирования в состояния ожидания происходит, минуя состояния фазового регулирования, т.е. без инерции сохранения корректирующего воздействия. 13 ил.

Частотно-фазовый детектор, имеющий первый и второй входы; первый, второй, третий и четвертый выходы; первый, второй, третий, четвертый, пятый и шестой запоминающие элементы и первый логический элемент; тактовые входы первого и третьего запоминающих элементов соединены между собой и подключены к первому входу устройства; тактовые входы второго и четвертого запоминающих элементов соединены между собой и подключены к второму входу устройства; информационный выход первого и информационный вход третьего запоминающих элементов и первый вход первого логического элемента соединены между собой и подключены к первому выходу устройства; информационный выход второго и информационный вход четвертого запоминающих элементов и второй вход первого логического элемента соединены между собой и подключены к второму выходу устройства; установочные входы первого и второго запоминающих элементов соединены между собой и подключены к выходу первого логического элемента; информационный вход второго запоминающего элемента подключен к уровню логической единицы, отличающийся тем, что введен второй логический элемент; тактовые входы пятого и шестого запоминающих элементов соединены между собой и подключены к первому входу устройства; информационный выход третьего запоминающего элемента подключен к третьему выходу устройства; выход второго логического элемента подключен к четвертому выходу устройства; информационный вход первого и установочный вход пятого запоминающих элементов соединены между собой и подключены к инвертированному информационному выходу четвертого запоминающего элемента; установочные входы третьего и шестого запоминающих элементов соединены между собой и подключены к выходу первого логического элемента; установочный вход четвертого и информационный выход пятого запоминающих элементов соединены между собой; первый вход второго логического элемента и информационный вход шестого запоминающего элемента соединены между собой и подключены к информационному выходу четвертого запоминающего элемента; второй вход второго логического элемента и информационный выход шестого запоминающего элемента соединены между собой; информационный вход пятого запоминающего элемента подключен к уровню логической единицы.

| ИМПУЛЬСНЫЙ ЧАСТОТНО-ФАЗОВЫЙ ДЕТЕКТОР | 1991 |

|

RU2012992C1 |

| ЧАСТОТНО-ФАЗОВЫЙ ДЕТЕКТОР | 2006 |

|

RU2300170C1 |

| Частотно-фазовый детектор | 1977 |

|

SU661769A1 |

| Детектор сигналов с угловой модуляцией | 1980 |

|

SU1059660A1 |

| US 20060057996 А1, 16.03.2006 | |||

| US 7834708 В1, 16.11.2010. | |||

Авторы

Даты

2013-05-27—Публикация

2012-03-28—Подача