Изобретение относится к радиоэлектронике, а именно к импульсному частотно-фазовому детектору, предназначенному для использования в составе быстродействующих синтезаторов сетки частот (ССЧ) на базе контура импульсной фазовой автоподстройки частоты (ФАПЧ).

Быстродействующие ССЧ на базе контура импульсной ФАПЧ - важные элементы таких приложений, как системы связи с «прыгающей» частотой, комплексы радиомониторинга, высокопроизводительные микропроцессоры с поддержкой функции динамического масштабирования напряжения питания и частоты, высокоскоростные цифровые интерфейсы. Требование улучшения характеристик этих систем определяет повышение требований к качественным показателям ССЧ ФАПЧ и, в первую очередь, к повышению быстродействия переходных процессов (ПП) автоподстройки при переключении частот. Одним из направлений путей повышения быстродействия контура ФАПЧ является оптимизация алгоритма формирования выходных управляющих сигналов импульсного частотно-фазового детектора во время ПП.

На фиг.1 представлена типовая структурная схема быстродействующего ССЧ на базе контура импульсной ФАПЧ с аналоговым фильтром в контуре управления.

В состав ССЧ входят следующие блоки:

1 - импульсный частотно-фазовый детектор (ИЧФД);

2 - блок управляемых источников тока накачки заряда (ИТНЗ);

3 - аналоговый фильтр контура управления (ФКУ), состоящий из конденсатора C1, изодромного звена R2, C2, фильтра низкой частоты (ФНЧ) R3, C3 и элемента коммутации Sw;

4 - генератор, управляемый напряжением (ГУН);

5 - делитель частоты (ДЧ) с коэффициентами деления N, Nup и Ndn, устанавливаемыми управляющим устройством;

6 - блок синхронизации делителя частоты (СДЧ).

Блок ИЧФД, сравнивая фазы сигналов опорной частоты Fref и частоты обратной связи Fcnt, вырабатывает сигналы Up и Dn, установка которых определяется знаком, а длительность - величиной обнаруженной разности. В соответствии с сигналами Up и Dn блок ИТНЗ вырабатывает импульсы тока I0 требуемой полярности. Под воздействием импульсов тока на элементах ФКУ формируется напряжение Vvco. В соответствии с напряжением Vvco, на выходе ГУН формируется сигнал выходной частоты Fvco, поступающий на схему ДЧ для формирования сигнала Fcnt. Изменение напряжения Vvco осуществляется таким образом, чтобы устранить фазовую ошибку между сравниваемыми сигналами Fref и Fcnt и тем самым ввести контур ФАПЧ в синхронизм. В установившемся режиме длительность импульсов выходных сигналов ИЧФД, а значит, и импульсов выходного тока ИТНЗ, практически приближается к нулю. При этом конденсаторы ФКУ работают как элементы запоминания, сохраняя напряжение Vvco. Умножение контуром ФАПЧ входной опорной частоты Fref до значения выходной частоты Fvco обеспечивается делением частоты Fvco на соответствующий коэффициент. Амплитуда выходного тока ИТНЗ и характеристики ФКУ определяют полосу пропускания контура ФАПЧ.

Для повышения быстродействия контура ФАПЧ в переходном режиме при сохранении заданных фильтрующих свойств в установившемся режиме, используются режимы раздельного управления в зависимости от величины фазового рассогласования сигналов сравниваемых частот Fref и Fcnt. При фазовой разности сравниваемых сигналов Fref и Fcnt менее ±2π радиан осуществляется управление, линейно зависящее от величины фазовой разности. При превышении фазовой разности сигналов Fref и Fcnt более чем на ±2π радиан (а также по факту переключения на новую синтезируемую частоту) осуществляется перевод контура в режим релейного управления с регулированием по частоте, расширением полосы пропускания контура и использованием благоприятных фазовых соотношений за счет синхронизации ДЧ по импульсам сигнала опорной частоты. В релейном режиме частотного регулирования управляющее воздействие вырабатывается непрерывно, а его величина не зависит от величины фазовой разности, что позволяет устранить биения в управлении (циклы проскальзывания) и ускорить отработку контуром большой фазовой разности.

Учитывая, что наличие ДЧ в цепи обратной связи вносит в контур дополнительную инерционность, для предотвращения значительного перерегулирования момент вывода контура из релейного режима частотного управления сдвигается в сторону опережения. С этой целью осуществляется деление выходной частоты ГУН на значение, отличное от требуемого в установившемся режиме, но обеспечивающее необходимое упреждение. Выбор соответствующего коэффициента деления Nup или Ndn осуществляется по состоянию сигналов Relay, Up и Dn.

В режиме релейного частотного управления осуществляется синхронизация (сброс в начальное состояние) ДЧ по импульсам сигнала опорной частоты Fref. Соответствующие импульсы сигнала Sync вырабатываются блоком СДЧ, типовая структурная схема которого представлена на фиг.2. Длительность импульсов сигнала Sync определяется задержками переключений инверторов L61 и L62.

Благодаря синхронизации ДЧ, возвращение контура в режим линейного фазового регулирования происходит сразу, как только будет достигнута частота упреждения (условием является изменение знака разности периодов сравниваемых частот). Таким образом, в контуре создаются предпосылки для установки фазовых соотношений, благоприятных с точки зрения быстрого окончания ПП.

Расширение полосы пропускания контура реализуется увеличением амплитуды тока ИТНЗ с одновременным соответствующим шунтированием сопротивления резистора R2 изодромного звена элементом коммутации Sw с малым остаточным сопротивлением. После возвращения контура в режим линейного фазового регулирования, полоса пропускания восстанавливается до исходного значения.

Переход контура в релейный режим частотного управления может также осуществляться внутри интервала фазовой разности ±2π радиан.

Решающее влияние на динамику ПП контура ФАПЧ оказывает алгоритм формирования выходных управляющих сигналов ИЧФД, выбор момента вывода контура из релейного режима частотного управления и, особенно, начальные условия при возвращении ИЧФД в линейный режим фазового управления.

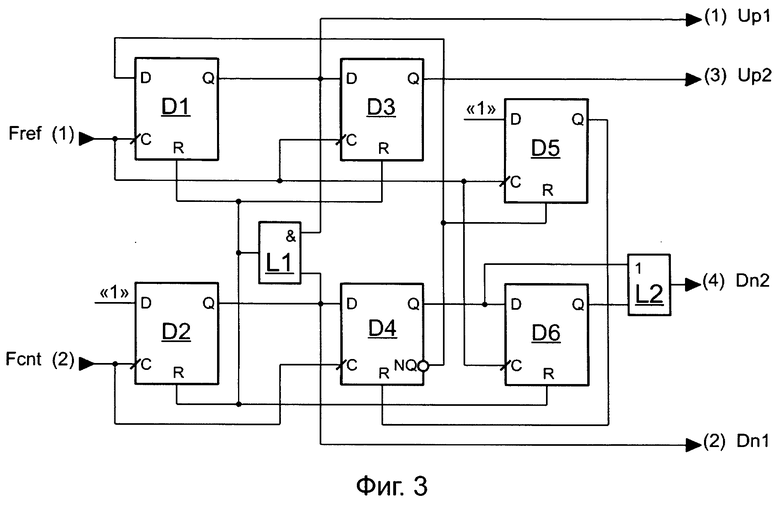

Наиболее близким техническим решением к заявляемому изобретению является схема ИЧФД, описанная в патенте Российской Федерации №2483434 (С1) «Импульсный Частотно-Фазовый Детектор», МПК H03D 13/00 [1]. Эта схема выбрана в качестве прототипа заявляемого изобретения и изображена на фиг.3.

Первым общим признаком с заявляемым изобретением является то, что при превышении разности фаз входных сигналов сравниваемых частот значения ±2π радиан, схема изобретения [1] осуществляет выработку сигналов управления, переводящих контур ФАПЧ из линейного режима фазового управления в релейный режим частотного управления. Вторым общим признаком с заявляемым изобретением является то, что при нахождении в релейном режиме частотного управления в случае изменения знака разности сравниваемых частот, схема изобретения [1] осуществляет выработку сигналов управления, переводящих контур ФАПЧ непосредственно в исходное состояние хранения заряда в ФКУ, т.е. минуя промежуточные состояния линейного режима фазового управления.

Схема ИЧФД изобретения [1] имеет: первый (Fref) и второй (Fcnt) входы; первый (Up1), второй (Dn1), третий (Up2) и четвертый (Dn2) выходы; первый (D1), второй (D2), третий (D3), четвертый (D4), пятый (D5) и шестой (D6) запоминающие элементы; первый (L1) и второй (L2) логические элементы. Запоминающие элементы имеют входы и выходы, обозначенные как: информационный вход - «D», информационный выход - «Q», инвертированный информационный выход - «NQ», тактовый вход - «C», установочный вход - «R».

Тактовые входы элементов D1, D3, D5 и D6 соединены между собой и подключены к входу Fref устройства. Тактовые входы элементов D2 и D4 соединены между собой и подключены к входу Fcnt устройства. Информационный выход элемента D1, информационный вход элемента D3 и первый вход элемента L1 соединены между собой и подключены к выходу Up1 устройства. Информационный выход элемента D2, информационный вход элемента D4 и второй вход элемента L1 соединены между собой и подключены к выходу Dn1 устройства. Информационный выход элемента D3 подключен к выходу Up2 устройства. Выход элемента L2 подключен к выходу Dn2 устройства. Информационный вход элемента D1, инвертированный информационный выход элемента D4 и установочный вход элемента D5 соединены между собой. Установочные входы элементов D1, D2, D3 и D6 и выход элемента L1 соединены между собой. Установочный вход элемента D4 и информационный выход элемента D5 соединены между собой. Первый вход элемента L2, информационный выход элемента D4 и информационный вход элемента D6 соединены между собой. Второй вход элемента L2 и информационный выход элемента D6 соединены между собой. Информационные входы элементов D2 и D5 подключены к уровню «лог.1».

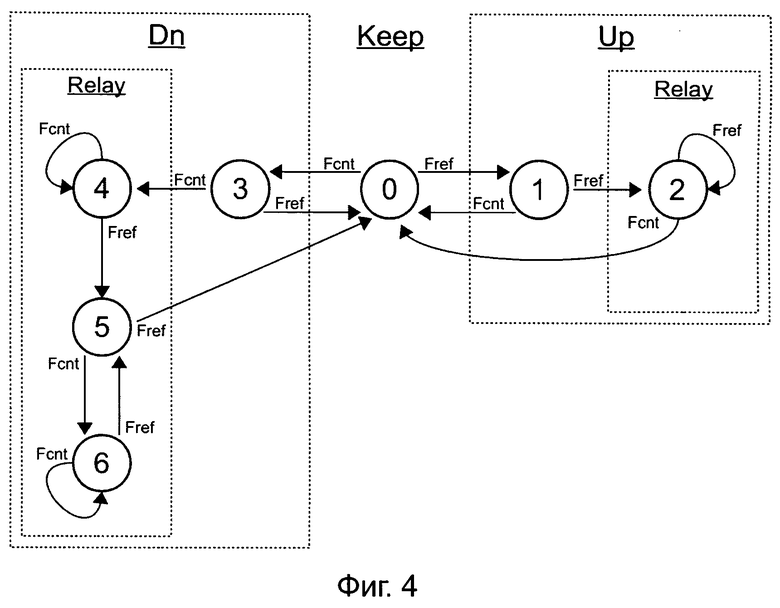

На фиг.4 в форме направленного графа представлен алгоритм переходов состояний и формирования выходных управляющих сигналов схемы ИЧФД изобретения [1]. Группа состояний, соответствующая режиму хранения заряда в ФКУ, обозначена как «Keep». Перезаряд конденсаторов ФКУ осуществляется в соответствующих состояниях, обозначенных как «Up» и «Dn», а ускоренный перезаряд увеличенным значением тока ИТНЗ осуществляется в состояниях релейного режима частотного управления, обозначенных как «Relay».

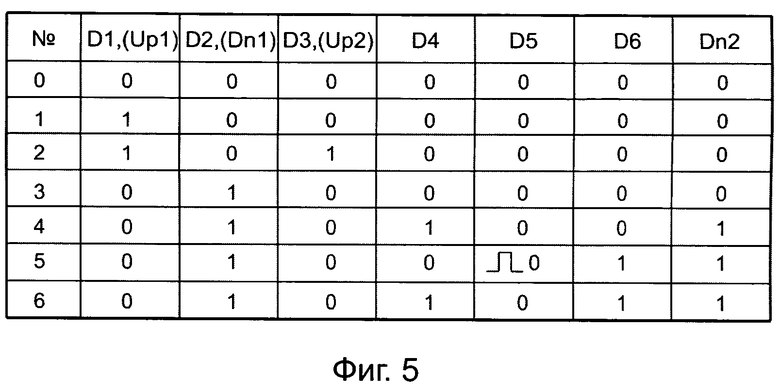

На фиг.5 представлена таблица состояний схемы ИЧФД изобретения [1] для соответствующих состояний графа переходов фиг.4. В состояниях 2 и 4 осуществляется релейный режим частотного управления. Для выработки сигнала Relay выходные сигналы схемы ИЧФД Up2 и Dn2 комбинируются по функции «лог. ИЛИ».

Схема ИЧФД изобретения [1] имеет следующий недостаток. После выхода ИЧФД из состояния 2 релейного режима управления в исходное состояние хранения линейного режима фазового управления, фаза сигнала Fref опорной частоты и начало счета в ДЧ не синхронизированы, что увеличивает исходную фазовую разность в первый такт сравнения линейном режиме и, соответственно, увеличивает длительность ПП, необходимого для отработки этой разности.

Техническим результатом заявляемого изобретения является минимизация длительности ПП контура импульсной ФАПЧ за счет того, что при выходе ИЧФД из релейного режима частотного управления в состояние хранения линейного режима фазового управления, периоды сигналов сравниваемых частот Fref и Fcnt имеют нулевую исходную фазовую разность.

Указанный технический результат достигается тем, что перед возвращением в исходное состояние хранения линейного режима фазового управления схема ИЧФД заявляемого изобретения имеет дополнительное состояние хранения, в котором осуществляется синхронизация начала периодов сравниваемых частот Fref и Fcnt с одновременной блокировкой выработки выходных управляющих сигналов Up и Dn.

Для обеспечения данной функциональности схемы ИЧФД заявляемого изобретения, в схему ИЧФД изобретения [1], имеющую первый и второй входы; первый, второй и третий выходы; первый, второй, третий, четвертый, пятый и шестой запоминающие элементы; первый и второй логические элементы; тактовые входы первого, третьего и шестого запоминающих элементов соединены между собой и подключены к первому входу устройства; тактовые входы второго и четвертого запоминающих элементов соединены между собой и подключены к второму входу устройства; информационный выход первого и информационный вход третьего запоминающих элементов и первый вход первого логического элемента соединены между собой и подключены к первому выходу устройства; установочные входы первого и третьего запоминающих элементов соединены между собой; информационный вход второго запоминающего элемента подключен к уровню логической единицы; информационный выход второго запоминающего элемента и второй вход первого логического элемента соединены между собой; установочный вход второго запоминающего элемента и выход первого логического элемента соединены между собой; информационный вход шестого запоминающего элемента и первый вход второго логического элемента соединены между собой; информационный выход шестого запоминающего элемента и второй вход второго логического элемента соединены между собой, предложено ввести третий, четвертый, пятый, шестой и седьмой логические элементы; выход третьего логического элемента подключить к второму выходу устройства; выход четвертого логического элемента подключить к третьему выходу устройства; информационный вход первого запоминающего элемента подключить к уровню логической единицы; инвертированный информационный выход первого запоминающего элемента и первый вход пятого логического элемента соединить между собой; установочный вход первого запоминающего элемента и выход шестого логического элемента соединить между собой; первые входы третьего и седьмого логических элементов соединить между собой и подключить к информационному выходу второго запоминающего элемента; информационный выход третьего и информационный вход пятого запоминающих элементов и первый вход четвертого логического элемента соединить между собой; информационный вход четвертого запоминающего элемента и выход седьмого логического элемента соединить между собой; информационный выход четвертого запоминающего элемента и вторые входы третьего, четвертого и седьмого логических элементов соединить между собой; инвертированный информационный выход четвертого запоминающего элемента и второй вход пятого логического элемента соединить между собой; установочный вход четвертого запоминающего элемента, выход пятого и первый вход шестого логических элементов соединить между собой; третий вход пятого и второй вход шестого логических элементов соединить между собой и подключить к выходу первого логического элемента; информационный выход пятого запоминающего элемента, первый вход второго и третьи входы четвертого и шестого логических элементов соединить между собой; установочные входы пятого и шестого запоминающих элементов и выход второго логического элемента соединить между собой; тактовый вход пятого запоминающего элемента подключить к второму входу устройства.

В результате заявляемая схема ИЧФД при выходе из релейного режима частотного управления, перед возвращением в исходное состояние хранения линейного режима фазового управления имеет дополнительное состояние хранения, в котором осуществляется синхронизация начала периодов сигналов сравниваемых частот Fref и Font с одновременной блокировкой выработки выходных управляющих сигналов Up и Dn, что обеспечивает нулевую исходную фазовую разность периодов сравниваемых частот Fref и Fcnt и, соответственно, способствует быстрому окончанию ПП.

Заявляемое изобретение иллюстрируется следующими графическими материалами.

Фиг.1. Типовая структурная схема быстродействующего ССЧ на базе контура импульсной ФАПЧ с аналоговым фильтром в контуре управления.

Фиг.2. Типовая структурная схема СДЧ.

Фиг.3. Схема ИЧФД, представленная в изобретении [1] и выбранная в качестве аналога-прототипа заявляемого изобретения.

Фиг.4. Алгоритм работы схемы ИЧФД изобретения [1] в форме направленного графа.

Фиг.5. Таблица состояний схемы ИЧФД изобретения [1] для соответствующих состояний графа переходов фиг.4.

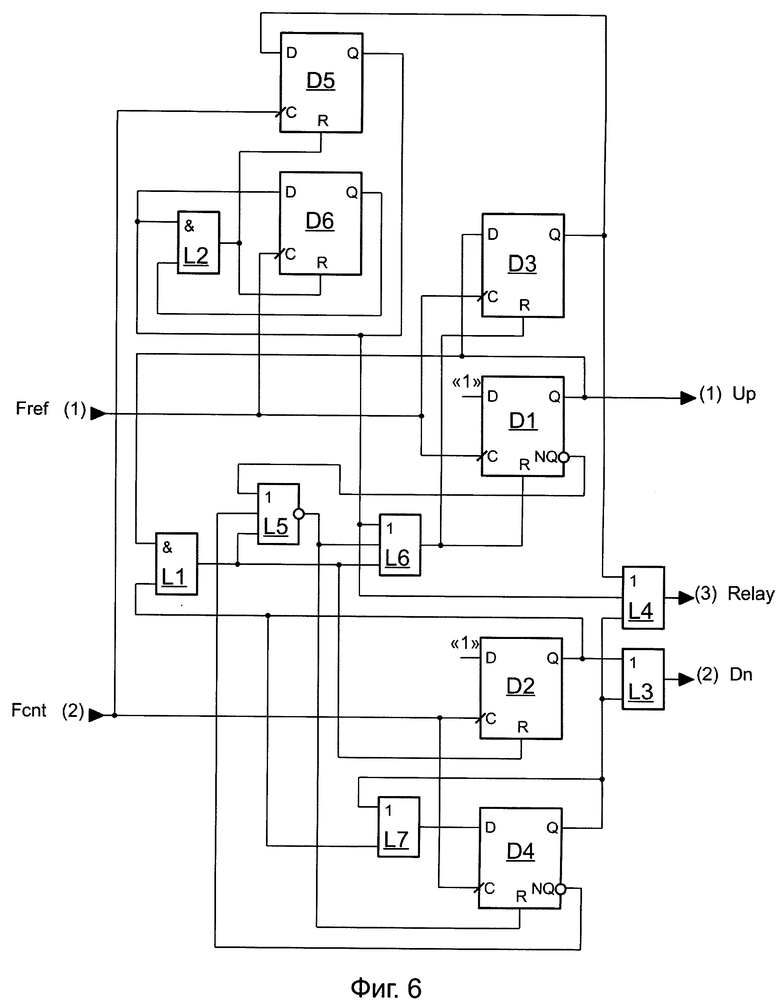

Фиг.6. Схема ИЧФД, заявляемая в данном изобретении.

Фиг.7. Алгоритм работы схемы ИЧФД, заявляемой в данном изобретении, в форме направленного графа.

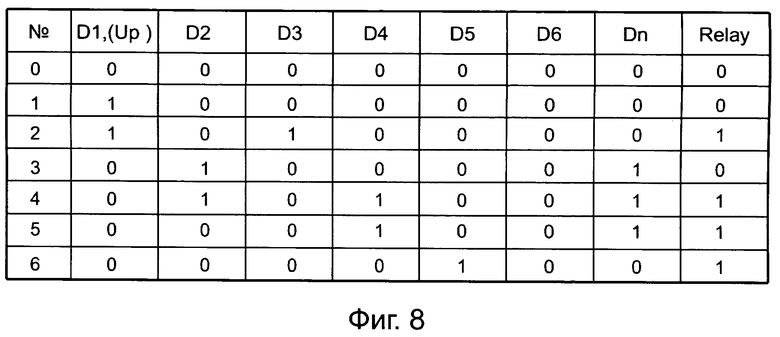

Фиг.8. Таблица состояний схемы ИЧФД, заявляемой в данном изобретении, для соответствующих состояний графа переходов фиг.7.

Фиг.9. Диаграммы состояний и формирование выходных управляющих сигналов схемы ИЧФД во время ПП автоподстройки частоты Fvco при перестройке по частоте вверх.

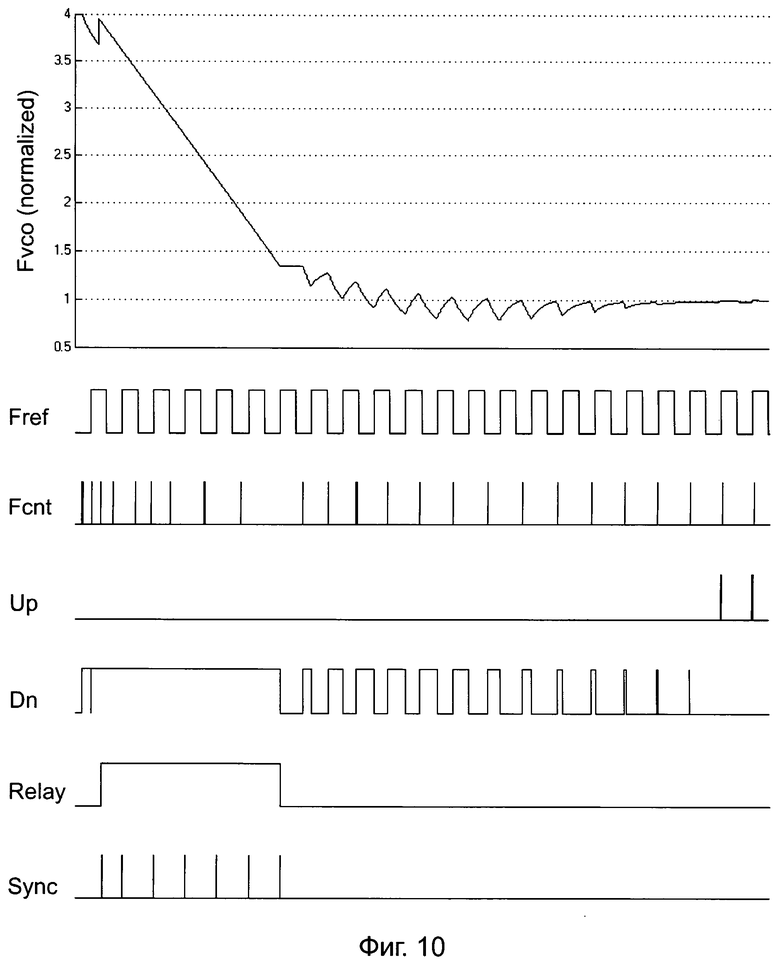

Фиг.10. Диаграммы состояний и формирование выходных управляющих сигналов схемы ИЧФД во время ПП автоподстройки частоты Fvco при перестройке по частоте вниз.

Заявляемая в данном изобретении схема ИЧФД представлена на фиг.6.

Схема ИЧФД имеет: первый (Fief) и второй (Fcnt) входы; первый (Up), второй (Dn) и третий (Relay) выходы; первый (D1), второй (D2), третий (D3), четвертый (D4), пятый (D5) и шестой (D6) запоминающие элементы; первый (L1), второй (L2), третий (L3), четвертый (L4), пятый (L5), шестой (L6) и седьмой (L7) логические элементы. Запоминающие элементы имеют входы и выходы, обозначенные как: информационный вход - «D», информационный выход - «Q», инвертированный информационный выход - «NQ», тактовый вход - «C», установочный вход - «R».

Тактовые входы элементов D1, D3 и D6 соединены между собой и подключены к входу Fref устройства. Тактовые входы элементов D2, D4 и D5 соединены между собой и подключены к входу Fcnt устройства. Информационные входы элементов D1 и D2 подключены к уровню «лог.1». Информационный выход элемента D1, информационный вход элемента D3 и первый вход элемента L1 соединены между собой и подключены к выходу Up устройства. Инвертированный информационный выход элемента D1 и первый вход элемента L5 соединены между собой. Информационный выход элемента D2, второй вход элемента L1, первые входы элементов L3 и L7 соединены между собой. Установочные входы элементов D1 и D3 и выход элемента L6 соединены между собой. Информационный выход элемента D3, информационный вход элемента D5 и первый вход элемента L4 соединены между собой. Информационный вход элемента D4 и выход элемента L7 соединены между собой. Информационный выход элемента D4 и вторые входы элементов L3, L4 и L7 соединены между собой. Инвертированный информационный выход элемента D4 и второй вход элемента L5 соединены между собой. Установочный вход элемента D4, выход элемента L5 и первый вход элемента L6 соединены между собой. Установочный вход элемента D2, выход элемента L1, третий вход элемента L5 и второй вход элемента L6 соединены между собой. Информационный выход элемента D5, информационный вход элемента D6, первый вход элемента L2, третьи входы элементов L4 и L6 соединены между собой. Установочные входы элементов D5 и D6 и выход элемента L2 соединены между собой. Информационный выход элемента D6 и второй вход элемента L2 соединены между собой. Выход элемента L3 подключен к выходу Dn устройства. Выход элемента L4 подключен к выходу Relay устройства.

На фиг.7 представлен алгоритм работы схемы ИЧФД, заявляемой в данном изобретении, в форме направленного графа.

На фиг.8 представлена таблица состояний схемы ИЧФД, заявляемой в данном изобретении, для соответствующих состояний графа переходов фиг.7. Состояния с 0 по 4 таблицы фиг.8 совпадают с соответствующими состояниями таблицы фиг.5 для изобретения [1].

При увеличении во время ПП фазовой разности более -2π радиан схема ИЧФД переходит в состояние 4 алгоритма. По сигналу Fref схема ИЧФД переходит в состояние 5 алгоритма. Состояния 4 и 5 алгоритма являются состояниями релейного управления, в которых по сигналу Fref осуществляется синхронизация ДЧ. Далее происходит переключение схемы ИЧФД между состояниями 4 и 5 алгоритма до тех пор, пока не изменится знак разности сравниваемых частот, что переведет ИЧФД в исходное состояние 0 алгоритма. Причем в момент входа ИЧФД в исходное состояние 0 алгоритма, начала периодов частот сравниваемых сигналов Fref и Fcnt будут синхронизированы, как и в изобретении [1].

Алгоритм переходов состояний схемы ИЧФД заявляемого изобретения, в результате которого перед возвращением ИЧФД из релейного режима частотного управления в исходное состояние хранения линейного режима фазового управления осуществляется синхронизация начала периодов сравниваемых частот с одновременной блокировкой выработки выходных управляющих сигналов, реализуется следующим образом.

При увеличении во время ПП фазовой разности сигналов сравниваемых частот более +2π радиан, схема ИЧФД переходит в состояние 2 алгоритма, в котором элементы D1 и D3 находятся в состоянии «лог.1». При поступлении сигнала Fref это состояние сохраняется и осуществляется синхронизация ДЧ. Благодаря синхронизации ДЧ, выработка сигнала Fcnt (и последующий переход в состояние 6 алгоритма) произойдет только при смене знака разности сфазированных периодов сравниваемых частот, т.е. после достижения требуемой частоты упреждения.

При поступлении сигнала Fcnt элементы D2 и D5 устанавливаются в состояние «лог.1», что через элементы L1 и L7 асинхронно сбросит элементы D1, D2 и D3 в состояние «лог.0». В отличие от изобретения [1], схема ИЧФД заявляемого изобретения перейдет в состояние 6 алгоритма, являющееся дополнительным состоянием хранения заряда в ФК, в котором выходной сигнал Relay сохраняет состояние «лог.1», что необходимо для выработки схемой СДЧ сигнала Sync для синхронизации ДЧ по сигналу Fref. При этом состояние «лог.1» элемента D5 асинхронно удерживает в состоянии «лог.0» элемент D1.

По сигналу Fref элемент D6 устанавливается в состояние «лог.1», что через элемент L2 асинхронно сбросит элементы D5 и D6 в состояние «лог.0». В результате осуществляется блокировка на один такт сигнала Fref установки в состояние «лог.1» элемента D1 (и, соответственно, выходного сигнала Up), схема ИЧФД перейдет в исходное состояние 0 алгоритма. Следующие пришедшие импульсы сигналов Fref и Fcnt дадут разность двух сфазированных сравниваемых периодов для исходного состояния 0 алгоритма, что уменьшает начальную фазовую разность в первый такт сравнения в линейном режиме фазового управления.

В случае если в состоянии 6 алгоритма поступит сигнал Fcnt, то элемент D2 установится в состояние «лог.1», а элемент D5 установится в состояние «лог.0» и схема ИЧФД перейдет в состояние 3 алгоритма.

Таким образом, переход схемы ИЧФД из релейного режима частотного управления (состояние 2 алгоритма) в дополнительное состояние хранения заряда в ФКУ (состояние 6 алгоритма), при переходе из которого в исходное состояние 0 алгоритма осуществляется синхронизация ДЧ по сигналу опорной частоты Fref, является необходимым и достаточным условием для синхронизации периодов сигналов сравниваемых частот при возвращении схемы ИЧФД в линейный режим фазового управления.

В качестве примера на фиг.9 и фиг.10 представлены диаграммы результатов моделирования ПП в ССЧ контура импульсной ФАПЧ с использованием схемы ИЧФД заявляемого изобретения. По диаграммам можно видеть переходы состояний и формирование выходных управляющих сигналов ИЧФД, сделать выводы о качестве управления, оценить значения перерегулирования и длительности ПП. Значение выходной синтезируемой частоты Fvco представлено в нормированном виде.

На фиг.9 представлены диаграммы состояний и формирование выходных управляющих сигналов схемы ИЧФД во время ПП автоподстройки частоты Fvco при перестройке по частоте вверх, а на фиг.10 при перестройке по частоте вниз.

Как следует из представленных диаграмм, отработка остаточной фазовой разности после возвращения схемы ИЧФД в линейный режим фазового управления начинается с наиболее благоприятных, с точки зрения быстрого окончания ПП, траекторий фазового пространства, что подтверждает возможность получения высокого быстродействия в ССЧ на базе контура импульсной ФАПЧ с использованием заявляемой схемы ИЧФД.

В начальной стадии ПП контур ФАПЧ ведет себя как оптимальная по быстродействию релейная система, замкнутая по частоте, с использованием упреждения и быстрой установкой напряжения на конденсаторах ФКУ.

Непрерывный контроль в релейном режиме разности частот Fref и Fcnt (с помощью синхронизации ДЧ) обеспечивает переход в линейную область фазового управления, как только ГУН перейдет границу частоты упреждения.

При этом синхронизация периодов сравниваемых частот перед возвращением в исходное состояние линейного режима фазового управления обеспечивает нулевую исходную фазовую разность, что способствует быстрому окончанию ПП.

Описанная схема ИЧФД может иметь различные альтернативные варианты своей реализации в зависимости от используемого схемотехнического базиса запоминающих и логических элементов с сохранением заданной функциональности и алгоритма формирования выходных управляющих сигналов.

Изобретение относится к радиоэлектронике, а именно к импульсному частотно-фазовому детектору. Технический результат заключается в уменьшении времени переходных процессов в контуре фазовой автоподстройки частоты за счет оптимизации алгоритма формирования выходных управляющих сигналов импульсного частотно-фазового детектора. При выходе детектора из релейного режима частотного управления в состояние хранения линейного режима фазового управления периоды сигналов сравниваемых частот имеют нулевую исходную фазовую разность. 10 ил.

Частотно-фазовый детектор, имеющий первый и второй входы; первый, второй и третий выходы; первый, второй, третий, четвертый, пятый и шестой запоминающие элементы; первый и второй логические элементы; тактовые входы первого, третьего и шестого запоминающих элементов соединены между собой и подключены к первому входу устройства; тактовые входы второго и четвертого запоминающих элементов соединены между собой и подключены к второму входу устройства; информационный выход первого и информационный вход третьего запоминающих элементов и первый вход первого логического элемента соединены между собой и подключены к первому выходу устройства; установочные входы первого и третьего запоминающих элементов соединены между собой; информационный вход второго запоминающего элемента подключен к уровню логической единицы; информационный выход второго запоминающего элемента и второй вход первого логического элемента соединены между собой; установочный вход второго запоминающего элемента и выход первого логического элемента соединены между собой; информационный вход шестого запоминающего элемента и первый вход второго логического элемента соединены между собой; информационный выход шестого запоминающего элемента и второй вход второго логического элемента соединены между собой, отличающийся тем, что введены третий, четвертый, пятый, шестой и седьмой логические элементы; выход третьего логического элемента подключен к второму выходу устройства; выход четвертого логического элемента подключен к третьему выходу устройства; информационный вход первого запоминающего элемента подключен к уровню логической единицы; инвертированный информационный выход первого запоминающего элемента и первый вход пятого логического элемента соединены между собой; установочный вход первого запоминающего элемента и выход шестого логического элемента соединены между собой; первые входы третьего и седьмого логических элементов соединены между собой и подключены к информационному выходу второго запоминающего элемента; информационный выход третьего и информационный вход пятого запоминающих элементов и первый вход четвертого логического элемента соединены между собой; информационный вход четвертого запоминающего элемента и выход седьмого логического элемента соединены между собой; вторые входы третьего, четвертого и седьмого логических элементов и информационный выход четвертого запоминающего элемента соединены между собой; инвертированный информационный выход четвертого запоминающего элемента и второй вход пятого логического элемента соединены между собой; установочный вход четвертого запоминающего элемента, выход пятого и первый вход шестого логических элементов соединены между собой; третий вход пятого и второй вход шестого логических элементов соединены между собой и подключены к выходу первого логического элемента; информационный выход пятого запоминающего элемента, первый вход второго, третьи входы четвертого и шестого логических элементов соединены между собой; установочные входы пятого и шестого запоминающих элементов и выход второго логического элемента соединены между собой; тактовый вход пятого запоминающего элемента подключен к второму входу устройства.

| ИМПУЛЬСНЫЙ ЧАСТОТНО-ФАЗОВЫЙ ДЕТЕКТОР | 2012 |

|

RU2483434C1 |

| ЧАСТОТНО-ФАЗОВЫЙ ДЕТЕКТОР | 2006 |

|

RU2300170C1 |

| Пломбировальные щипцы | 1923 |

|

SU2006A1 |

| Колосоуборка | 1923 |

|

SU2009A1 |

Авторы

Даты

2014-10-10—Публикация

2013-10-07—Подача