Изобретение относится к системам обработки цифровых сигналов и предназначено для ввода однополярных и дифференциальных цифровых сигналов различных стандартов в устройства обработки цифровых сигналов, в том числе в компьютеры.

При обработке информации на компьютерах часто возникает задача ввода множества симметричных дифференциальных цифровых сигналов (по стандарту LVDS) и несимметричных однополярных сигналов (LVTTL).

Обычно для ввода подобных сигналов используются так называемые линейные приемники, которые преобразуют входной сигнал допустимого уровня в стандартный логический выходной сигнал.

Если стандарт вводимого сигнала заранее не определен или может оперативно изменяться, предусматривают входные соединители как для симметричных, так и для несимметричных сигналов. При многоканальных системах ввода это приводит к существенному увеличению количества требуемых входных соединителей аппаратуры, что приводит к увеличению габаритов и усложнению коммутации аппаратуры. Например, при восьмиканальном вводе (с учетом тактового сигнала) требуется 18 разъемов для симметричных сигналов и еще 9 для несимметричных сигналов, причем при практическом подключении одна из групп разъемов остается незадействованной.

Этот недостаток может быть устранен при совмещенном использовании симметричных и несимметричных входов, т.е. при подключении несимметричных сигналов ко входам для прямых (либо для инверсных) симметричных сигналов.

Известен способ совмещения симметричных и несимметричных входов в аппаратуре, использующей программируемые логические интегральные схемы (ПЛИС), который может быть реализован путем их переконфигурирования. Например, такой способ совмещения может быть реализован на ПЛИС семейства Virtex4 фирмы Xilinx [1], в которых предусмотрены наборы симметричных и несимметричных входов. Однако такое решение не позволяет обеспечить автоматический выбор симметричных и несимметричных входов и, кроме того, должен быть заранее известен стандарт подключаемого сигнала.

В качестве аналога можно привести запатентованное устройство [2], которое предназначено для обнаружения наличия цифрового тактового сигнала на цифровом видеовходе в телевизионных системах.

Для ввода однополярных сигналов с помощью дифференциального приемника можно использовать простое схемотехническое решение [3], в котором однополярный сигнал подается на прямой вход симметричного входного устройства (при необходимости через аттенюатор), а на его инверсный вход подается опорное напряжение, соответствующее среднему значению входного однополярного сигнала. Недостатком этого решения является отсутствие возможности ввода симметричного сигнала и, тем более, автоматического переключения входного устройства в зависимости от типа входного сигнала. Именно это устройство выбрано в качестве прототипа.

Техническим результатом настоящего изобретения является обеспечение ввода как однополярных (LVTTL), так и дифференциальных (LVDS) цифровых сигналов с автоматическим определением типа входного сигнала и установлением соответствующих режимов ввода.

Предлагается универсальное устройство ввода однополярных и дифференциальных цифровых сигналов, которое включает в себя дифференциальный приемник, состоящий из двух усилителей-ограничителей для приема прямого и инверсного входных сигналов и формирователя выходного логического сигнала. При приеме дифференциального сигнала на прямой и инверсный входы дифференциального приемника подаются соответственно прямой и инверсный входные сигналы. Устройство отличается тем, что в него введены триггер, элемент задержки, резисторный делитель, управляемый ключ и два компаратора для формирования логических сигналов из прямого входного дифференциального сигнала и соответственно из однополярного входного сигнала, причем входы обоих компараторов соединены с прямым входом дифференциального приемника, вход тактового сигнала триггера соединен с выходом первого компаратора через элемент задержки, вход данных триггера соединен с выходом второго компаратора, вход резисторного делителя соединен с прямым выходом триггера, выход резисторного делителя соединен с входом управляемого ключа, выход управляемого ключа соединен с инверсным входом дифференциального приемника, а вход управления управляемого ключа соединен с инверсным выходом триггера.

Дальнейшее описание поясняется с помощью следующих чертежей.

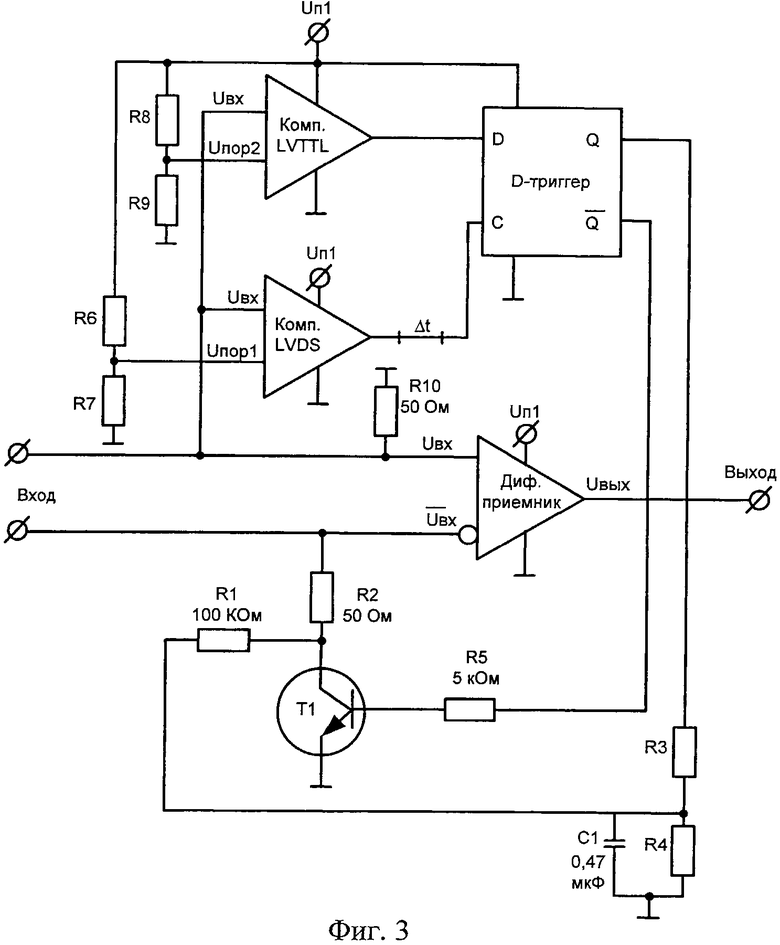

Фиг.1 - структурная схема предлагаемого устройства.

фиг.2 - сигналы, подаваемые на вход предлагаемого устройства.

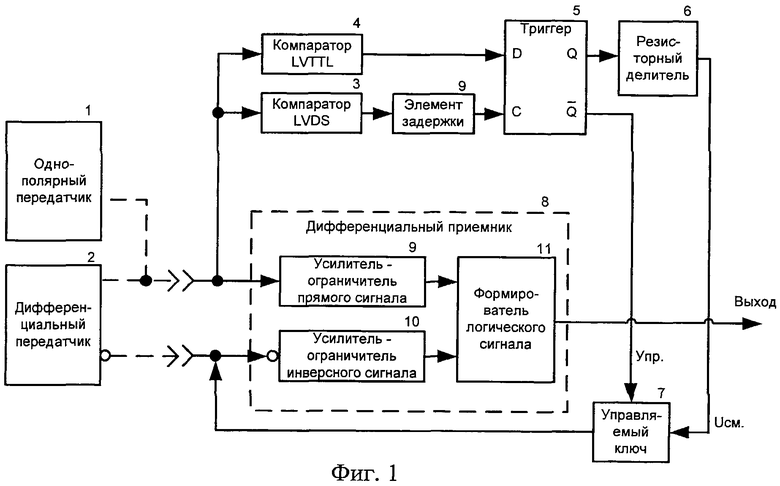

Фиг.3 - пример электрической схемы предлагаемого устройства.

В устройстве-прототипе используется дифференциальный приемник с прямым и инверсным входами, источник опорного напряжения, содержащий резисторный делитель напряжения. Сигнал на вход устройства-прототипа поступает от однополярного передатчика. Между выходом передатчика и входом прямого сигнала дифференциального приемника может быть включен резисторный аттенюатор сигнала, который при необходимости используется для ослабления однополярного сигнала. Для обеспечения нормальной работы приемника при приеме однополярного сигнала на инверсном входе должно быть установлено постоянное напряжение, равное среднему значению входного однополярного сигнала, которое получается с помощью упомянутого резисторного делителя напряжения.

На фиг.1 представлена структурная схема предлагаемого устройства для ввода однополярных и дифференциальных цифровых сигналов.

На входы устройства можно подавать однополярный сигнал от однополярного передатчика 1 или дифференциальный сигнал от дифференциального передатчика 2. При подаче дифференциального сигнала устройство автоматически переводится в режим приема дифференциального сигнала. При подаче логической "1" на вход однополярного сигнала устройство автоматически переводится в режим приема однополярного сигнала. Сводка возможных состояний устройства приводится в таблице 1.

Устройство обеспечивает ввод однополярных сигналов по стандартам LVTTL, TTL (с уровнем логической "1" не менее 2,4 В) и ввод дифференциальных сигналов по стандартам LVDS (с номинальным размахом логического сигнала от 1 до 1,4 В относительно среднего постоянного напряжения 1,2 В).

На выходе предлагаемого устройства образуется логический сигнал, пригодный для подачи на устройства обработки цифровых сигналов.

В случае приема однополярного сигнала при подаче на прямой вход дифференциального приемника логической "1" на входе компараторов 3 и 4 образуется смещение выше их порогового уровня и, следовательно, на их выходах устанавливаются уровни логической "1", что приводит к срабатыванию триггера 5 и установке на его прямом выходе Q логической "1", а на инверсном  логического "0". При этом резисторный делитель 6 формирует напряжение смещения Uсм, управляемый ключ 7 обеспечивает подачу требуемого Uсм на инверсный вход дифференциального приемника 8, состоящего из двух усилителей-ограничителей 9 и 10 для приема прямого и инверсного входных сигналов соответственно, и формирователя 11 выходного логического сигнала. При последующем попадании на прямой вход приемника 8 логических "0" и "1" состояние триггера 5 не изменяется.

логического "0". При этом резисторный делитель 6 формирует напряжение смещения Uсм, управляемый ключ 7 обеспечивает подачу требуемого Uсм на инверсный вход дифференциального приемника 8, состоящего из двух усилителей-ограничителей 9 и 10 для приема прямого и инверсного входных сигналов соответственно, и формирователя 11 выходного логического сигнала. При последующем попадании на прямой вход приемника 8 логических "0" и "1" состояние триггера 5 не изменяется.

В случае приема дифференциального сигнала на входы компараторов 3 (LVDS) и 4 (LVTTL) поступает сигнал, который превышает пороговое напряжение компаратора 3 и не превышает пороговое напряжение компаратора 4. При этом на выходе компаратора 3 устанавливается напряжение логической "1", а на выходе компаратора 4 - логического "0". Это приводит к срабатыванию триггера 5 и установке на его прямом выходе Q логического "0", а на инверсном  логической "1". При этом резисторный делитель 6 формирует нулевое напряжение, и управляемый ключ 7 не обеспечивает подачу Uсм на инверсный вход дифференциального приемника 8.

логической "1". При этом резисторный делитель 6 формирует нулевое напряжение, и управляемый ключ 7 не обеспечивает подачу Uсм на инверсный вход дифференциального приемника 8.

При выборе порогов компараторов 3 и 4 необходимо учитывать следующие условия.

1. Компаратор 4 должен срабатывать только от "1" в сигнале LVTTL и не должен срабатывать от "0" и "1" сигнала LVDS.

2. Компаратор 3 должен срабатывать как от "1" в сигнале LVTTL, так и от сигнала LVDS. При этом, как следует из стандартов LVDS [4], возможно два варианта установки порога. При установке напряжения около 0,5 В переход устройства в режим приема сигнала LVDS будет происходить независимо от логических значений сигнала ("0" или "1"). При установке напряжения около 1,2 В переход устройства в режим приема сигнала LVDS будет происходить при появлении на входе логической "1".

Для того чтобы обеспечить надежное срабатывание триггера 5 (перенос данных со входа D на выход Q) в цепь его тактового входа С введен элемент задержки 12, который обеспечивает необходимую задержку фронта тактового сигнала относительно данных.

Таким образом, при подаче однополярного сигнала осуществляется его ввод посредством установки Uсм на инверсном входе дифференциального приемника 1, а при подаче дифференциального сигнала осуществляется его непосредственный ввод дифференциальным приемником 8, при этом на его инверсном входе не формируется напряжение смещения Uсм.

На фиг.2 показаны примеры стандартизованных входных (тактовых) сигналов LVTTL и LVDS и пороги срабатывания компараторов 3 и 4.

Для однополярного сигнала стандарта LVTTL номинальное напряжение "0" составляет менее 0,4 В, номинальное напряжение "1" составляет не менее 2,4 В. Для дифференциального сигнала LVDS номинальное напряжение "0" прямой составляющей составляет 1,05 В, номинальное напряжение "1" составляет 1,35 В.

Пример электрической схемы для реализации предлагаемого устройства представлен на фиг.3. Напряжение питания Uп1 элементов схемы подается от внешнего источника. В качестве триггера 5 выбран D-триггер. Управляемый ключ 7 реализован на насыщаемом транзисторе Т1, а делитель 6 - на резисторах R3 и R4. Делители на резисторах R6, R7 и R8, R9 предназначены соответственно для установки пороговых напряжений Uпор1 и Uпор2 для компараторов 3 и 4. Резисторы R2 и R10 предназначены для согласования входной линии передачи с номинальной нагрузкой 50 Ом. Элемент задержки 12 обозначен на схеме как Δt и может быть реализован с помощью логической ячейки, либо с помощью линейной LC или RC цепи задержки.

Управляемый ключ 7 реализован на транзисторе Т1. Он входит в режим насыщения при токе базы 0,3-0,7 мА, который образуется при наличии напряжения Uсм и определяется резистором R5; при этом ключ замкнут, и его проходное сопротивление составляет 0,3-1,0 Ом. При нулевом входном напряжении ток базы отсутствует, и при этом ключ разомкнут, и его проходное сопротивление превышает 1 МОм.

Предлагаемое устройство может также быть использовано при многоканальном вводе сигналов, когда, например, по первому каналу идут тактовые сигналы, а по остальным каналам - сигналы данных. В этом случае в каждый из каналов данных должны быть введены управляемые ключи, которые управляются параллельно с ключом первого канала. Смещение Uсм может также подаваться из первого канала.

Таким образом, предлагаемое устройство решает поставленную задачу - обеспечить ввод как однополярных, так и дифференциальных сигналов с помощью единого приемника, чем при многоканальном вводе обеспечивается существенное (на 1/3) сокращение необходимого числа входных каналов и соответствующих схемных элементов.

Литература

1. Virtex-4 User Guide / Chapter 6: «Select 10 Resources» // Xilinx Inc. 10.08.2007.

2. Pat. USA №5343301 «Input clock presence detector for a digital video input». Int. Cl H04 5/04 / Ampex Systems Corp., Jan S. Wesolowski. Заявл. 05.11.1992, выд. 30.08.1994.

3. LVDS Application and Data Handbook // Texas Instruments. 11.2002., стр.3-1,3-2.

4. LVDS Application and Data Handbook // Texas Instruments. 11.2002., стр.3-3.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство межмодульного обмена по магистрали LVDS-M с канальным резервированием и прямым доступом в память | 2016 |

|

RU2648574C2 |

| ИЗМЕРИТЕЛЬНОЕ УСТРОЙСТВО | 2011 |

|

RU2469341C1 |

| Цифровой измеритель временных характеристик электрического сигнала | 1985 |

|

SU1291897A1 |

| Ультразвуковой дефектоскоп | 1990 |

|

SU1744636A1 |

| УСТРОЙСТВО ОХРАННОЙ СИГНАЛИЗАЦИИ | 1991 |

|

RU2031445C1 |

| ПРЕОБРАЗОВАТЕЛЬ ИНЕРЦИАЛЬНОЙ ИНФОРМАЦИИ | 2006 |

|

RU2325620C2 |

| ПРЕОБРАЗОВАТЕЛЬ НАПРЯЖЕНИЯ РАЗБАЛАНСА МОСТОВОЙ СХЕМЫ В ЧАСТОТУ ИЛИ СКВАЖНОСТЬ | 2018 |

|

RU2699303C1 |

| СПОСОБ КОРРЕКЦИИ РЕЗУЛЬТАТОВ ИЗМЕРЕНИЯ ТЕНЗОМЕТРИЧЕСКИМ МОСТОВЫМ ДАТЧИКОМ С ИНСТРУМЕНТАЛЬНЫМ УСИЛИТЕЛЕМ | 2011 |

|

RU2469340C1 |

| АЭРОЛОГИЧЕСКИЙ РАДИОЗОНД | 1999 |

|

RU2162239C1 |

| ДЕКОДЕР ДИФФЕРЕНЦИАЛЬНОГО СИГНАЛА КОДА RZ | 2005 |

|

RU2291560C1 |

Изобретение относится к системам обработки цифровых сигналов и предназначено для ввода однополярных и дифференциальных цифровых сигналов в устройства обработки цифровых сигналов. Техническим результатом настоящего изобретения является обеспечение ввода как однополярных, так и дифференциальных цифровых сигналов с автоматическим определением типа входного сигнала и установлением соответствующих режимов ввода. Универсальное устройство ввода однополярных и дифференциальных цифровых сигналов содержит дифференциальный приемник, состоящий из двух усилителей-ограничителей для приема прямого и инверсного входных сигналов и формирователя выходного логического сигнала, причем в устройство введены триггер, элемент задержки, резисторный делитель, управляемый ключ и два компаратора для формирования логических сигналов из прямого входного дифференциального сигнала и соответственно из однополярного входного сигнала, причем входы обоих компараторов соединены с прямым входом дифференциального приемника, вход тактового сигнала триггера соединен с выходом первого компаратора через элемент задержки, вход данных триггера соединен с выходом второго компаратора, вход резисторного делителя соединен с прямым выходом триггера, выход резисторного делителя соединен с входом управляемого ключа, выход управляемого ключа соединен с инверсным входом дифференциального приемника, а вход управления управляемого ключа соединен с инверсным выходом триггера. 3 ил.

Универсальное устройство ввода однополярных и дифференциальных цифровых сигналов, содержащее дифференциальный приемник, состоящий из двух усилителей-ограничителей для приема прямого и инверсного входных сигналов и формирователя выходного логического сигнала, причем при приеме дифференциального сигнала на прямой и инверсный входы дифференциального приемника подаются соответственно прямой и инверсный входные сигналы, отличающееся тем, что в него введены триггер, элемент задержки, резисторный делитель, управляемый ключ и два компаратора для формирования логических сигналов из прямого входного дифференциального сигнала и соответственно из однополярного входного сигнала, причем входы обоих компараторов соединены с прямым входом дифференциального приемника, вход тактового сигнала триггера соединен с выходом первого компаратора через элемент задержки, вход данных триггера соединен с выходом второго компаратора, вход резисторного делителя соединен с прямым выходом триггера, выход резисторного делителя соединен с входом управляемого ключа, выход управляемого ключа соединен с инверсным входом дифференциального приемника, а вход управления управляемого ключа соединен с инверсным выходом триггера.

| US 5343301 А, 30.08.1994 | |||

| US 6243776 В1, 05.06.2001 | |||

| US 6812736 B2, 02.11.2004 | |||

| US 6218858 B1, 17.04.2001 | |||

| Режущий аппарат для косилок, жаток и других уборочных машин | 1945 |

|

SU66644A1 |

Авторы

Даты

2012-01-20—Публикация

2010-07-05—Подача