Изобретение относится к области радиотехники и связи сможет быть использовано в качестве устройства усиления аналоговых сигналов, в структуре аналоговых микросхем различного функционального назначения (например, в компараторах и решающих усилителях с малыми значениями э.д.с. смещения нуля).

В современной радиоэлектронной аппаратуре находят применение дифференциальные операционные усилители (ОУ) с существенными различными параметрами. Особое место занимают ОУ с двухканальной активной нагрузкой, обеспечивающей непосредственное управление двухтактным буферным усилителем: [1÷10]. Такие ОУ имеют двухканальную передачу сигнала через управляемую активную нагрузку и характеризуются более высоким диапазоном рабочих частот благодаря наличию каскадной структуры.

Предлагаемое изобретение относится также к классу ОУ на базе несимметричных входных каскадов [1-10], которые до сих пор находили применение только в устройствах с низкими требованиями к стабильности нулевого уровня.

Наиболее близким по технической сущности к заявляемому схемотехническому решению является классическая схема ОУ фиг.1, представленная в патенте RU 2193273, fig.2, которая также присутствует в большом числе других патентов и монографий, например [1÷10], имеющих в качестве цепи нагрузки входных транзисторов двухканальные токовые зеркала с несимметричным включением (по отношению к входному каскаду). Это одна из перспективных архитектур ОУ, так как она обеспечивает (при минимально возможной сложности) получение двуполярных амплитуд выходного напряжения, близких к напряжениям питания.

Существенный недостаток известного ОУ фиг.1 состоит в том, что он имеет повышенное значение систематической составляющей напряжения смещения нуля (Uсм), связанной с несимметрией его архитектуры.

Основная задача предлагаемого изобретения состоит в уменьшении абсолютного значения Uсм, а также его температурного и радиационного дрейфа.

Поставленная задача решается тем, что в прецизионном операционном усилителе фиг.1, содержащем входной дифференциальный каскад 1 с первым 2 и вторым 3 токовыми выходами, общая эмиттерная цепь которого соединена с первой 4 шиной источника питания, первый 5 выходной транзистор, база которого соединена с первым 2 токовым выходом входного дифференциального каскада 1, эмиттер подключен ко второму 3 токовому выходу входного дифференциального каскада 1, а коллектор соединен со входом буферного усилителя 6, второй 7 выходной транзистор, эмиттер которого соединен со второй 8 шиной источника питания и связан с базой через два параллельно соединенных р-n-перехода (9, 10), первый 11 источник опорного тока, предусмотрены новые элементы и связи, - эмиттер первого 5 выходного транзистора соединен с базой второго 7 выходного транзистора, база первого 5 выходного транзистора соединена с коллектором второго 7 выходного транзистора, коллектор первого 5 выходного транзистора связан с коллектором дополнительного транзистора 12, эмиттер дополнительного транзистора 12 соединен с первой 4 шиной источника питания через первый 11 источник опорного тока, причем база дополнительного транзистора 12 подключена к выходу буферного усилителя 6.

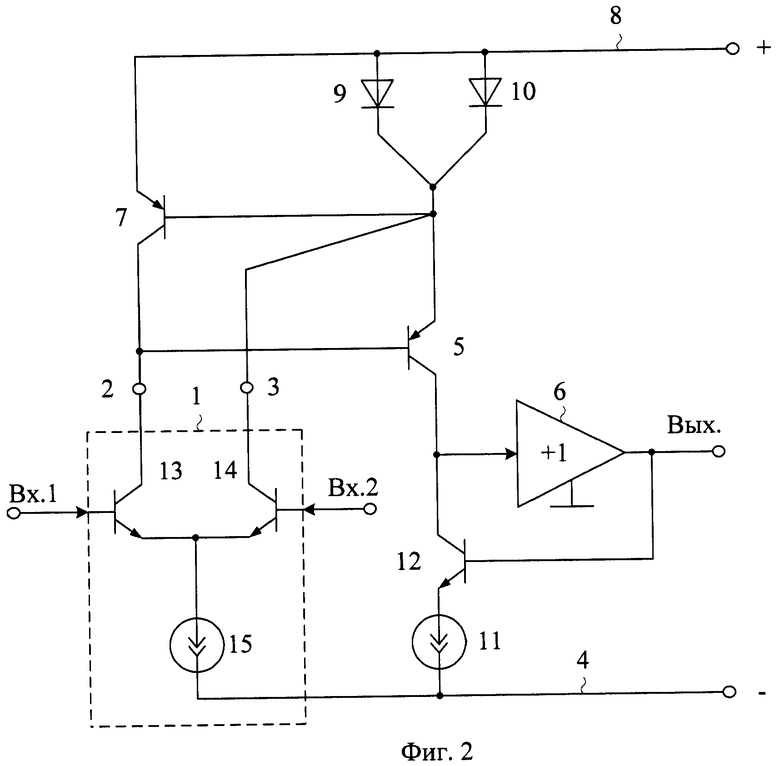

Схема усилителя-прототипа показана на фиг.1. На фиг.2 представлена схема заявляемого устройства в соответствии с п.1 формулы изобретения.

На фиг.3 показана схема ОУ фиг.2 с конкретным выполнением буферного усилителя 6, который реализован здесь на составном транзисторе Дарлингтона 16, 17 и источнике тока 18. Кроме этого на фиг.3, также как и на фиг.2, входной дифференциальный каскад 1 реализован на транзисторах 13, 14 и двухполюснике 15 по традиционной схеме.

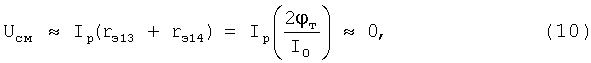

Схема фиг.4 соответствует п.2 формулы изобретения. В ней база первого 5 выходного транзистора соединена с коллектором второго 7 выходного транзистора через первый 19 дополнительный p-n переход, а эмиттер первого 5 выходного транзистора подключен ко второму 3 токовому выходу входного дифференциального каскада 1 через второй 20 прямосмещенный p-n-переход. Кроме этого здесь буферный усилитель 6 (также как и в схеме фиг.3) выполнен на элементах 16, 17, 18, причем источник тока 18 выполнен здесь на транзисторе 24 и резисторе 28, первый источник опорного тока 11 содержит транзистор 23 и резистор 27, а двухполюсник 15 (фиг.3) реализован на транзисторах 21, 22 и резисторах 25 и 26. На базы транзисторов 21, 22, 23, 24 подается вспомогательное напряжение Ес.

На фиг.5 и фиг.6 показаны схемы дифференциального ОУ-прототипа (фиг.5) и заявляемого ОУ (фиг.6) в среде компьютерного моделирования PSpice на моделях интегральных транзисторов ФГУП НПП «Пульсар».

На фиг.7 приведена схема фиг.3 в среде PSpice для случая, когда буферный усилитель 6 реализован на составном транзисторе Дарлингтона.

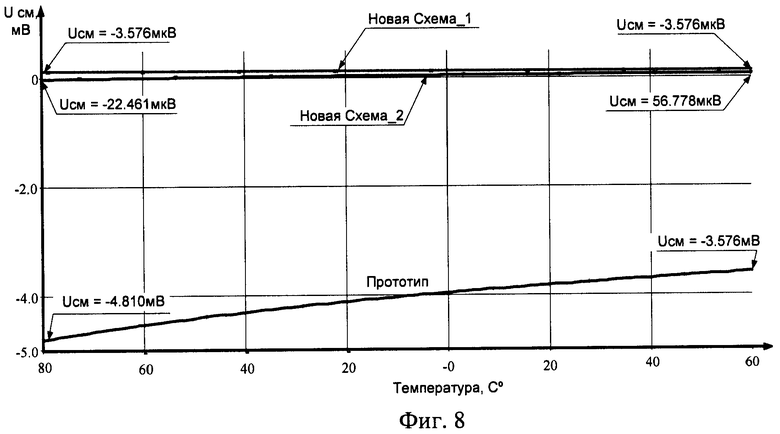

На фиг.8 приведены результаты компьютерного моделирования напряжения смещения нуля Uсм в диапазоне температур схемы 1 (фиг.7), схемы 2 (фиг.6) и схемы-прототипа (фиг.5). Данные графики показывают, что напряжение смещения нуля Uсм схемы фиг.7 на несколько порядков меньше, чем в ОУ-прототипе, и оно оказывается более стабильным.

Прецизионный операционный усилитель фиг.2 содержит входной дифференциальный каскад 1 с первым 2 и вторым 3 токовыми выходами, общая эмиттерная цепь которого соединена с первой 4 шиной источника питания, первый 5 выходной транзистор, база которого соединена с первым 2 токовым выходом входного дифференциального каскада 1, эмиттер подключен ко второму 3 токовому выходу входного дифференциального каскада 1, а коллектор соединен со входом буферного усилителя 6, второй 7 выходной транзистор, эмиттер которого соединен со второй 8 шиной источника питания и связан с базой через два параллельно соединенных p-n-перехода (9, 10), первый 11 источник опорного тока. Эмиттер первого 5 выходного транзистора соединен с базой второго 7 выходного транзистора, база первого 5 выходного транзистора соединена с коллектором второго 7 выходного транзистора, коллектор первого 5 выходного транзистора связан с коллектором дополнительного транзистора 12, эмиттер дополнительного транзистора 12 соединен с первой 4 шиной источника питания через первый 11 источник опорного тока, причем база дополнительного транзистора 12 подключена к выходу буферного усилителя 6.

Рассмотрим факторы, определяющие систематическую составляющую напряжения смещения нуля (Uсм) в схеме фиг.3, т.е. зависящие от схемотехники ОУ.

Если ток двухполюсника 15 равен величине 2I0, а двухполюсников 11 и 18 - величине I0, то токи эмиттеров (Iэi) и коллекторов (Iкi) транзисторов схемы, а также токи p-n-переходов 9 (I9) и 10 (I10):

где Iбi=Iэi/βi - ток базы n-p-n (Iбр) или p-n-p (Iбn) транзисторов при эмиттерном токе Iэi=I0;

βi - коэффициент усиления по току базы i-го транзистора.

Поэтому разность токов в узле «А» при его коротком замыкании на эквипотенциальную общую шину

где IБУ<<Iбр - ток базы транзистора 17.

Таким образом, в заявляемом устройстве при выполнении условия (8) уменьшается систематическая составляющая Uсм, обусловленная конечной величиной β транзисторов и его радиационной (или температурной) зависимостью. Как следствие, это уменьшает Uсм ОУ, так как разностный ток Iр в узле «А» создает Uсм, зависящее от крутизны (S) преобразования входного дифференциального напряжения ОУ (uвх) в выходной ток узла «А»:

где rэ13=rэ14 - сопротивления эмиттерных переходов входных транзисторов 13 и 14 входного дифференциального каскада 1.

Поэтому для схемы фиг.2

где φт=26 мВ - температурный потенциал.

В ОУ-прототипе фиг.1 Ip≠0, поэтому здесь систематическая составляющая Ucм получается как минимум на порядок больше, чем в заявляемой схеме.

Введение p-n-переходов 19 и 20 обеспечивает дальнейшее уменьшение температурного дрейфа Uсм за счет симметрирования статического режима по напряжению транзистора 7 и p-n перехода 9, а также транзисторов 13 и 14.

Компьютерное моделирование схем фиг.5, фиг.6, фиг.7 подтверждает (фиг.8) данные теоретические выводы. Несмотря на изменение β транзисторов вследствие внешних воздействий предлагаемый ОУ имеет меньшее напряжение смещения нуля, чем ОУ-прототип.

Таким образом, заявляемое устройство обладает существенными преимуществами в сравнении с прототипом до величины статической ошибки усиления сигналов постоянного тока и может использоваться в качестве IP-модулей прецизионных интерфейсов.

БИБЛИОГРАФИЧЕСКИЙ СПИСОК

1. Патент RU №2193293, fig.2, АООТ завод «Микрон» г.Зеленоград.

2. Патент США №4.250.460.

3. Патент США №3.843.935, fig.2.

4. Патент США №4.366.442.

5. Патент США №3,569.848, fig.7 (А2-В2).

6. Патент Японии JP 52-149946.

7. Полонников, Д.Е. Операционные усилители: Принципы построения, теория, схемотехника [Текст]. / Д.Е.Полонников. - М., 1983. - стр.141, рис.4.14.

8. Операционные усилители и компараторы. - М.: Издательский дом «Додэка-ХХI», 2001, стр.259 (микросхема 1450УД1, ТАА 2761).

9. Журнал «Схемотехника» №3, 2001, стр.3.

10. Справочник «Electronics information series: Linear integrated circuit D.A.T.A, bock», Edition 21, 1979, Condura Company, US, New Jersey, P212, fig.A358, HA1-4625, HA1-4605.

| название | год | авторы | номер документа |

|---|---|---|---|

| ПРЕЦИЗИОННЫЙ ОПЕРАЦИОННЫЙ УСИЛИТЕЛЬ | 2011 |

|

RU2449466C1 |

| ДИФФЕРЕНЦИАЛЬНЫЙ ОПЕРАЦИОННЫЙ УСИЛИТЕЛЬ | 2009 |

|

RU2412532C1 |

| ОПЕРАЦИОННЫЙ УСИЛИТЕЛЬ С МАЛЫМ НАПРЯЖЕНИЕМ СМЕЩЕНИЯ НУЛЯ | 2011 |

|

RU2462812C1 |

| ПРЕЦИЗИОННЫЙ ОПЕРАЦИОННЫЙ УСИЛИТЕЛЬ | 2011 |

|

RU2449465C1 |

| ДИФФЕРЕНЦИАЛЬНЫЙ ОПЕРАЦИОННЫЙ УСИЛИТЕЛЬ | 2009 |

|

RU2412538C1 |

| КАСКОДНЫЙ ОПЕРАЦИОННЫЙ УСИЛИТЕЛЬ С МАЛЫМ НАПРЯЖЕНИЕМ СМЕЩЕНИЯ НУЛЯ | 2009 |

|

RU2402157C1 |

| ПРЕЦИЗИОННЫЙ ОПЕРАЦИОННЫЙ УСИЛИТЕЛЬ | 2011 |

|

RU2455757C1 |

| ДИФФЕРЕНЦИАЛЬНЫЙ ОПЕРАЦИОННЫЙ УСИЛИТЕЛЬ | 2009 |

|

RU2412533C1 |

| ДИФФЕРЕНЦИАЛЬНЫЙ ОПЕРАЦИОННЫЙ УСИЛИТЕЛЬ С МАЛЫМ НАПРЯЖЕНИЕМ СМЕЩЕНИЯ НУЛЯ | 2009 |

|

RU2402156C1 |

| ПРЕЦИЗИОННЫЙ ОПЕРАЦИОННЫЙ УСИЛИТЕЛЬ | 2011 |

|

RU2450424C1 |

Изобретение относится к области радиотехники и связи и может быть использовано в качестве устройства усиления аналоговых сигналов, в структуре аналоговых микросхем различного функционального назначения (например, в компараторах и решающих усилителях с малыми значениями э.д.с. смещения нуля). Технический результат заключается в уменьшении абсолютного значения Uсм, а также его температурного и радиационного дрейфа. Прецизионный операционный усилитель содержит входной дифференциальный каскад, первый и второй выходные транзисторы, дополнительный транзистор, источник опорного тока, два р-n-перехода, буферный усилитель. 1 з.п. ф-лы, 8 ил.

1. Прецизионный операционный усилитель, содержащий входной дифференциальный каскад (1) с первым (2) и вторым (3) токовыми выходами, общая эмиттерная цепь которого соединена с первой (4) шиной источника питания, первый (5) выходной транзистор, база которого соединена с первым (2) токовым выходом входного дифференциального каскада (1), эмиттер подключен ко второму (3) токовому выходу входного дифференциального каскада (1), а коллектор соединен со входом буферного усилителя (6), второй (7) выходной транзистор, эмиттер которого соединен со второй (8) шиной источника питания и связан с базой через два параллельно соединенных р-n-перехода (9), (10), первый (11) источник опорного тока, отличающийся тем, что эмиттер первого (5) выходного транзистора соединен с базой второго (7) выходного транзистора, база первого (5) выходного транзистора соединена с коллектором второго (7) выходного транзистора, коллектор первого (5) выходного транзистора связан с коллектором дополнительного транзистора (12), эмиттер дополнительного транзистора (12) соединен с первой (4) шиной источника питания через первый (11) источник опорного тока, причем база дополнительного транзистора (12) подключена к выходу буферного усилителя (6).

2. Прецизионный операционный усилитель по п.1, отличающийся тем, что база первого (5) выходного транзистора соединена с коллектором второго (7) выходного транзистора через первый (19) дополнительный р-n-переход, эмиттер первого (5) выходного транзистора подключен ко второму (3) токовому выходу входного дифференциального каскада (1) через второй (20) прямосмещенный р-n- переход.

| ДВУХТАКТНЫЙ ОПЕРАЦИОННЫЙ УСИЛИТЕЛЬ | 2000 |

|

RU2193273C2 |

| ПРЕЦИЗИОННЫЙ ОПЕРАЦИОННЫЙ УСИЛИТЕЛЬ С МАЛЫМ НАПРЯЖЕНИЕМ СМЕЩЕНИЯ НУЛЯ | 2009 |

|

RU2411637C1 |

| US 4250460 A, 10.02.1981 | |||

| US 3843935 A, 22.10.1974. | |||

Авторы

Даты

2012-02-27—Публикация

2011-03-11—Подача