Изобретение относится к области радиотехники и связи и может быть использовано в качестве устройства усиления аналоговых сигналов, в структуре аналоговых микросхем различного функционального назначения (например, в прецизионных интегральных и решающих усилителях, компараторах и т.п.).

Известны схемы операционных усилителей (ОУ) на основе трех токовых зеркал [1-5]. ОУ с такой архитектурой стали основой построения многих современных аналоговых микросхем [1-22], в т.ч. ОУ с опцией rail-to-rail, имеющих максимальную амплитуду выходного напряжения, близкую к напряжениям питания.

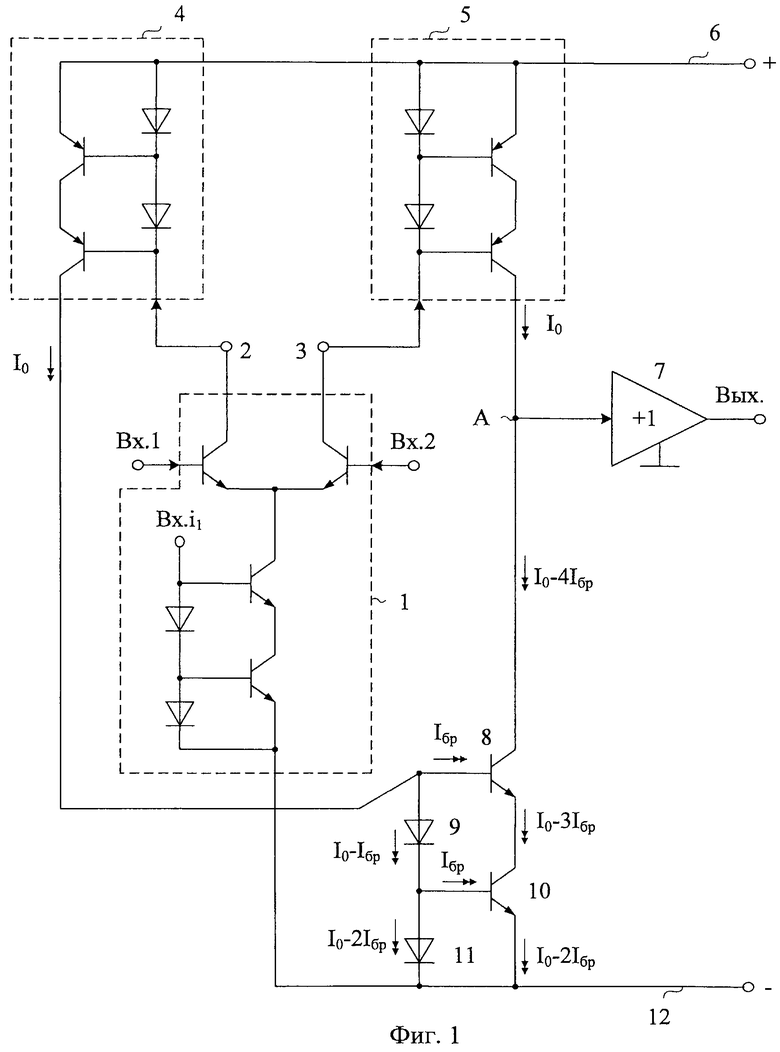

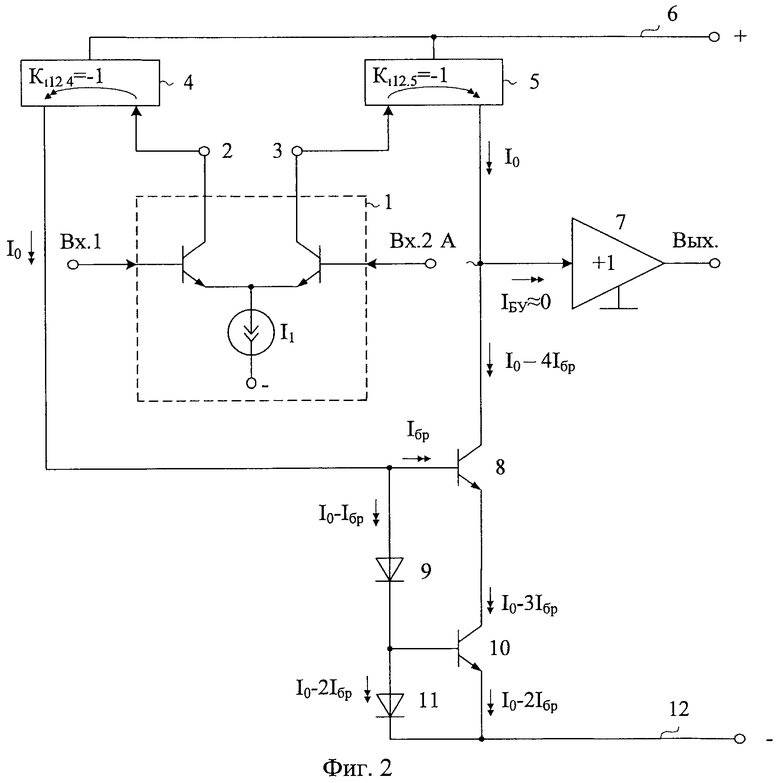

Ближайшим прототипом (фиг.1) заявляемого устройства является операционный усилитель, описанный в патенте US №4241315, fig.4. Его существенная особенность - применение каскодных токовых зеркал, обладающих высоким выходным сопротивлением (влияющим на коэффициент усиления ОУ по напряжению), а также характеризующихся повышенным диапазоном рабочих частот в сравнении с другими вариантами токовых зеркал. Архитектура ОУ-прототипа также используется во многих патентах ведущих микроэлектронных фирм [5-22]. ОУ фиг.1 содержит входной дифференциальный каскад 1 с первым 2 и вторым 3 токовыми выходами, связанными со входами соответствующих первого 4 и второго 5 токовых зеркал, согласованными с первой 6 шиной источника питания, буферный усилитель 7, вход которого соединен с выходом второго 5 токового зеркала и коллектором первого 8 выходного транзистора третьего токового зеркала, первый 9 p-n переход третьего токового зеркала, включенный между базой первого 8 выходного транзистора третьего токового зеркала, подключенной к выходу первого 4 токового зеркала и базой второго 10 выходного транзистора третьего токового зеркала, второй 11 p-n переход третьего токового зеркала, включенный параллельно эмиттерно-базовому переходу второго 10 выходного транзистора третьего токового зеркала, вторую 12 шину источника питания, связанную с эмиттером второго 10 выходного транзистора третьего токового зеркала, причем коллектор второго 10 выходного транзистора третьего токового зеркала связан с эмиттером первого 8 выходного транзистора третьего токового зеркала.

Существенный недостаток известного ОУ фиг.1 состоит в том, что он имеет повышенное значение систематической составляющей напряжения смещения нуля (Uсм), в том числе при температурных и радиационных воздействиях.

Основная задача предлагаемого изобретения состоит в уменьшении абсолютного значения Uсм, его температурного и радиационного дрейфа.

Поставленная задача решается тем, что в операционном усилителе (фиг.1), содержащем входной дифференциальный каскад 1 с первым 2 и вторым 3 токовыми выходами, связанными со входами соответствующих первого 4 и второго 5 токовых зеркал, согласованными с первой 6 шиной источника питания, буферный усилитель 7, вход которого соединен с выходом второго 5 токового зеркала и коллектором первого 8 выходного транзистора третьего токового зеркала, первый 9 p-n переход третьего токового зеркала, включенный между базой первого 8 выходного транзистора третьего токового зеркала, подключенной к выходу первого 4 токового зеркала и базой второго 10 выходного транзистора третьего токового зеркала, второй 11 p-n переход третьего токового зеркала, включенный параллельно эмиттерно-базовому переходу второго 10 выходного транзистора третьего токового зеркала, вторую 12 шину источника питания, связанную с эмиттером второго 10 выходного транзистора третьего токового зеркала, причем коллектор второго 10 выходного транзистора третьего токового зеркала связан с эмиттером первого 8 выходного транзистора третьего токового зеркала, предусмотрены новые элементы и связи - в схему введен дополнительный составной транзистор 13, содержащий N параллельно включенных биполярных транзисторов (13.1, 13.2, …13.N), база которого соединена с эмиттером первого 8 выходного транзистора третьего токового зеркала, эмиттер подключен ко второй 12 шине источника питания, а коллектор соединен с дополнительным 14 источником питания.

Схема операционного усилителя-прототипа представлена на фиг.1, а на фиг.2 приведена схема ОУ фиг.1, в которой подсхемы 4 и 5 могут иметь идентичное, в том числе каскодное построение.

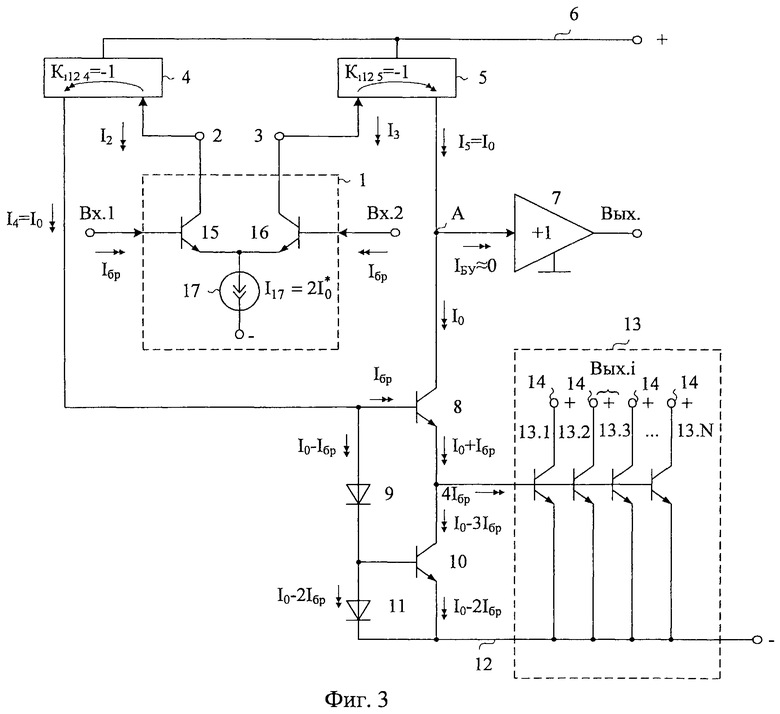

На фиг.3 показана схема заявляемого ОУ в соответствии с п.1 формулы изобретения.

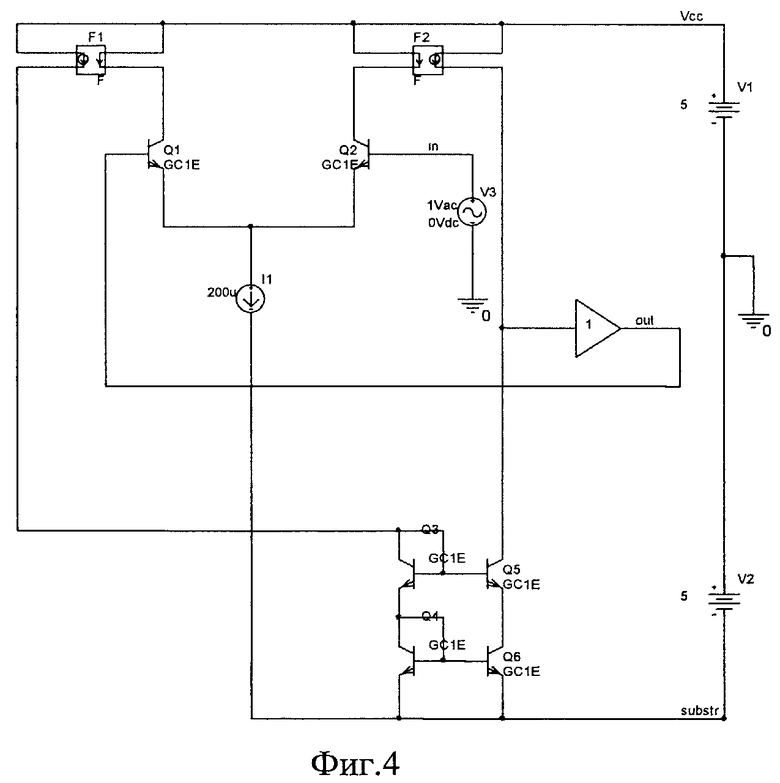

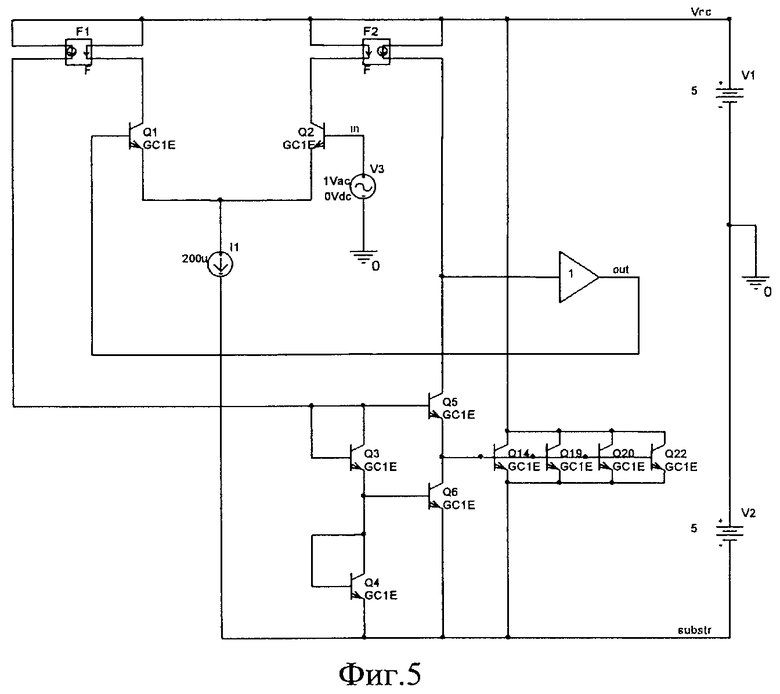

На фиг.4 и 5 показаны схемы усилителя-прототипа (фиг.4) и заявляемого ОУ (фиг.5) в среде компьютерного моделирования PSpice на моделях интегральных транзисторов АВМК_1_3 (г.Минск) с идеальным буферным каскадом.

На фиг.6 приведены температурные зависимости напряжения смещения нуля Uсм сравниваемых схем ОУ фиг.4 и фиг.5.

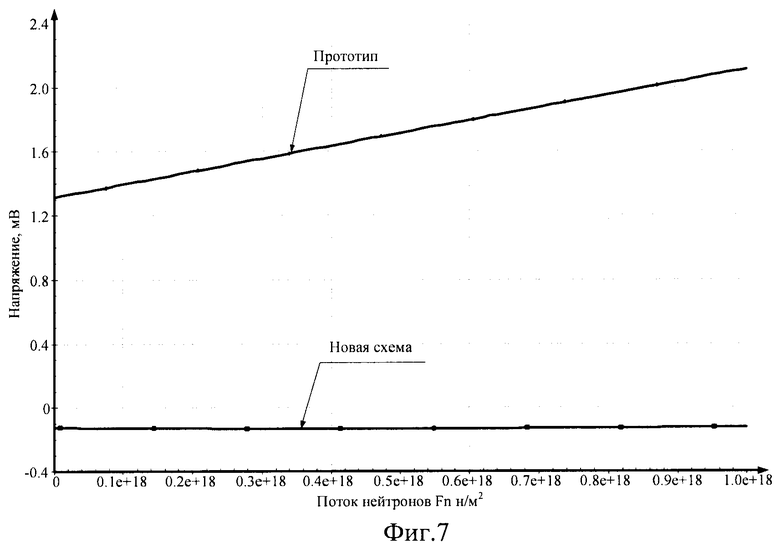

На фиг.7 приведена зависимость напряжения смещения нуля Uсм сравниваемых схем ОУ фиг.4 и 5 от потока нейтронов.

Операционный усилитель с малым напряжением смещения нуля фиг.2 содержит входной дифференциальный каскад 1 с первым 2 и вторым 3 токовыми выходами, связанными со входами соответствующих первого 4 и второго 5 токовых зеркал, согласованными с первой 6 шиной источника питания, буферный усилитель 7, вход которого соединен с выходом второго 5 токового зеркала и коллектором первого 8 выходного транзистора третьего токового зеркала, первый 9 p-n переход третьего токового зеркала, включенный между базой первого 8 выходного транзистора третьего токового зеркала, подключенной к выходу первого 4 токового зеркала и базой второго 10 выходного транзистора третьего токового зеркала, второй 11 p-n переход третьего токового зеркала, включенный параллельно эмиттерно-базовому переходу второго 10 выходного транзистора третьего токового зеркала, вторую 12 шину источника питания, связанную с эмиттером второго 10 выходного транзистора третьего токового зеркала, причем коллектор второго 10 выходного транзистора третьего токового зеркала связан с эмиттером первого 8 выходного транзистора третьего токового зеркала. В схему введен дополнительный составной транзистор 13, содержащий N параллельно включенных биполярных транзисторов (13.1, 13.2, …13.N), база которого соединена с эмиттером первого 8 выходного транзистора третьего токового зеркала, эмиттер подключен ко второй 12 шине источника питания, а коллектор соединен с дополнительным 14 источником питания.

В соответствии с п.2 формулы изобретения число параллельно включенных биполярных транзисторов в структуре дополнительного составного транзистора 13 равно четырем (N=4) (13.1, 13.2, 13.3, 13.4), а в качестве первого 4 и второго 5 токовых зеркал используются схемы идентичных токовых зеркал, реализуемых, например, по схеме Вильсона и ее многочисленным модификациям.

В соответствии с п.3 формулы изобретения в качестве дополнительного 14 источника питания используется общая шина положительного 6 и отрицательного 12 источников питания.

Буферный усилитель 7 с малым входным током может быть реализован как на полевых, так и на биполярных транзисторах по классическим схемам Дарлингтона. Входной дифференциальный каскад 1 в схеме фиг.3 реализован на входных транзисторах 15, 16 и источнике тока 17.

Рассмотрим факторы, определяющие систематическую составляющую напряжения смещения нуля (Uсм) в схеме фиг.3, в которой буферный усилитель 7 имеет малые входные токи (IБУ≈0).

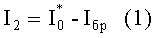

Если учесть, что выходные токи для узлов 2 и 3 входного дифференциального каскада 1 удовлетворяют условиям

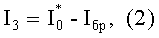

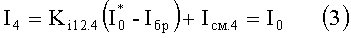

то можно найти выходные токи токовых зеркал 4 и 5, в качестве которых рекомендуется использовать как классические токовые зеркала Вильсона с Ki12=-1, так и каскодные токовые зеркала (см. US 4.241.315)

где Iсм.4=Iсм.5 - токи смещения нуля идентичных токовых зеркал 4 и 5;

Iбр=Iэ/βi - токи базы входных n-p-n транзисторов 15 и 16 схемы ОУ фиг.3 при их эмиттерном токе  ;

;

βi - коэффициент усиления по току базы n-p-n транзисторов схемы;

Ki12.4=Ki12.5=1 - коэффициент передачи по току идентичных токовых зеркала 4 и 5.

Таким образом, при идентичных токовых зеркалах 4 и 5 на вход третьего каскадного токового зеркала на транзисторах 8 и 10 поступает ток I4=I0=I5.

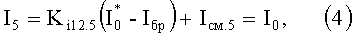

Введение в схему ОУ составного транзистора 13 при N=4 обеспечивает следующие эмиттерный (Iэ) и коллекторный (Iк) токи транзистора 8

где

Таким образом, в схеме фиг.2 в высокоимпедансном узле «А» обеспечивается полная взаимная компенсация токов I5 и Iк8, обусловленных неидентичностью транзисторов 8 и 10 третьего токового зеркала. Поэтому систематическая составляющая напряжения смещения нуля в схеме фиг.3 близка к нулю (Uсм≈0).

В частном случае коллекторы биполярных транзисторов 13.1…13.N могут использоваться как источники тока, устанавливающие статический режим транзисторов буферного усилителя 7, или подключаться к общей шине источника питания.

Результаты компьютерного моделирования известной (фиг.4) и предлагаемой (фиг.5) схем ОУ, представленные на фиг.6 и 7 показывают, что схема фиг.5 имеет более чем на порядок меньшее значение Uсм, его температурный (фиг.6), а также радиационный дрейф (фиг.7).

Таким образом, заявляемое устройство обладает существенными преимуществами в сравнении с прототипом по величине статической ошибки усиления сигналов постоянного тока.

БИБЛИОГРАФИЧЕСКИЙ СПИСОК

1. Операционные усилители и компараторы [Текст]. - М.: Издательский дом «Додэка-ХХI», 2001, стр.225.

2. Полонников Д.Е. Операционные усилители: принципы построения, теория, схемотехника [Текст] / Д.Е.Полонников. - М., 1983, с.203.

3. Операционные усилители и компараторы. - М.: Издательский дом «Додэка-XXI», 2001, стр.106 (ОУ СА3078).

4. Матавкин В.В. Быстродействующие операционные усилители [Текст] / В.В.Матавкин. - М.: Радио и связь, 1989. - Рис.2.12.

5. Шкритек П. Справочное руководство по звуковой схемотехнике [Текст]: Пер. с нем. / П.Шкритек - М.: Мир, 1991. - С.96, рис.8.2.1.

6. Патент США №4783602.

7. Патент США №4176323.

8. Патент США №5371476.

9. Патент США RE 30.587.

10. Патент США №4241315.

11. Патент США №4267519.

12. Патент США №4361815.

13. Патент США №3439542.

14. Патент США №5880639.

15. A.св. СССР №361605.

16. Патент ФРГ №2551068.

17. Патент ФРГ №2620999.

18. Патент США №5936568.

19. Патент США №5497124.

20. Патент США №3979689.

21. Патент США №5399991.

22. Патент США №4618832.

| название | год | авторы | номер документа |

|---|---|---|---|

| БИПОЛЯРНО-ПОЛЕВОЙ ОПЕРАЦИОННЫЙ УСИЛИТЕЛЬ | 2015 |

|

RU2595926C1 |

| ПРЕЦИЗИОННЫЙ ОПЕРАЦИОННЫЙ УСИЛИТЕЛЬ | 2010 |

|

RU2419198C1 |

| ПРЕЦИЗИОННЫЙ ОПЕРАЦИОННЫЙ УСИЛИТЕЛЬ НА ОСНОВЕ РАДИАЦИОННО СТОЙКОГО БИПОЛЯРНО-ПОЛЕВОГО ТЕХНОЛОГИЧЕСКОГО ПРОЦЕССА | 2014 |

|

RU2568384C1 |

| Безрезистивный арсенид-галлиевый операционный усилитель с малым уровнем систематической составляющей напряжения смещения нуля | 2023 |

|

RU2814681C1 |

| ПРЕЦИЗИОННЫЙ ДВУХКАСКАДНЫЙ ДИФФЕРЕНЦИАЛЬНЫЙ ОПЕРАЦИОННЫЙ УСИЛИТЕЛЬ | 2015 |

|

RU2615070C1 |

| ПРЕЦИЗИОННЫЙ ОПЕРАЦИОННЫЙ УСИЛИТЕЛЬ | 2011 |

|

RU2455757C1 |

| РАДИАЦИОННО-СТОЙКИЙ МУЛЬТИДИФФЕРЕНЦИАЛЬНЫЙ ОПЕРАЦИОННЫЙ УСИЛИТЕЛЬ ДЛЯ РАБОТЫ ПРИ НИЗКИХ ТЕМПЕРАТУРАХ | 2016 |

|

RU2628131C1 |

| ПРЕЦИЗИОННЫЙ ОПЕРАЦИОННЫЙ УСИЛИТЕЛЬ ДЛЯ РАДИАЦИОННО-СТОЙКОГО БИПОЛЯРНО-ПОЛЕВОГО ТЕХПРОЦЕССА | 2014 |

|

RU2571579C1 |

| ОПЕРАЦИОННЫЙ УСИЛИТЕЛЬ С МАЛЫМ НАПРЯЖЕНИЕМ СМЕЩЕНИЯ НУЛЯ | 2010 |

|

RU2414808C1 |

| ПРЕЦИЗИОННЫЙ ОПЕРАЦИОННЫЙ УСИЛИТЕЛЬ | 2011 |

|

RU2450425C1 |

Изобретение относится к области радиотехники и связи и может быть использовано в качестве устройства усиления аналоговых сигналов, в структуре аналоговых микросхем различного функционального назначения (например, в прецизионных интегральных и решающих усилителях, компараторах и т.п.). Технический результат заключается в уменьшении абсолютного значения напряжения смещения нуля, его температурного и радиационного дрейфа. Операционный усилитель с малым напряжением смещения нуля содержит входной дифференциальный каскад, первое и второе токовые зеркала, буферный усилитель, первый и второй выходные транзисторы третьего токового зеркала, первый и второй р-n переходы третьего токового зеркала, составной транзистор, содержащий N параллельно включенных биполярных транзисторов. 2 з.п. ф-лы, 7 ил.

1. Операционный усилитель с малым напряжением смещения нуля, содержащий входной дифференциальный каскад (1) с первым (2) и вторым (3) токовыми выходами, связанными со входами соответствующих первого (4) и второго (5) токовых зеркал, согласованными с первой (6) шиной источника питания, буферный усилитель (7), вход которого соединен с выходом второго (5) токового зеркала и коллектором первого (8) выходного транзистора третьего токового зеркала, первый (9) р-n переход третьего токового зеркала, включенный между базой первого (8) выходного транзистора третьего токового зеркала, подключенной к выходу первого (4) токового зеркала и базой второго (10) выходного транзистора третьего токового зеркала, второй (11) р-n переход третьего токового зеркала, включенный параллельно эмиттерно-базовому переходу второго (10) выходного транзистора третьего токового зеркала, вторую (12) шину источника питания, связанную с эмиттером второго (10) выходного транзистора третьего токового зеркала, причем коллектор второго (10) выходного транзистора третьего токового зеркала связан с эмиттером первого (8) выходного транзистора третьего токового зеркала, отличающийся тем, что в схему введен дополнительный составной транзистор (13), содержащий N параллельно включенных биполярных транзисторов (13.1, 13.2,… 13.N), база которого соединена с эмиттером первого (8) выходного транзистора третьего токового зеркала, эмиттер подключен ко второй (12) шине источника питания, а коллектор соединен с дополнительным (14) источником питания.

2. Операционный усилитель с малым напряжением смещения нуля по п.1, отличающийся тем, что в качестве первого (4) и второго (5) токовых зеркал используются идентичные токовые зеркала, а число параллельно включенных биполярных транзисторов в структуре дополнительного составного транзистора (13) равно N=4 (13.1, 13.2, 13.3, 13.4).

3. Операционный усилитель с малым напряжением смещения нуля по п.1, отличающийся тем, в качестве дополнительного (14) источника питания используется общая шина источников питания.

| US 4241315 А, 23.12.1980 | |||

| ЕР 1863171 A1, 05.12.2007 | |||

| ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ С ПОВЫШЕННЫМ ОСЛАБЛЕНИЕМ СИНФАЗНОГО СИГНАЛА | 2005 |

|

RU2292636C1 |

| ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ С МАЛЫМ НАПРЯЖЕНИЕМ СМЕЩЕНИЯ НУЛЯ | 2007 |

|

RU2331975C1 |

Авторы

Даты

2012-09-27—Публикация

2011-08-10—Подача