Изобретение относится к построению коммутируемых локальных сетей для обмена данными между вычислительными модулями параллельных вычислительных систем или распределенных вычислительных комплексов.

Известен модульный масштабируемый коммутатор и способ распределения кадров в сети быстрого ETHERNET [1], выполненный в виде множества индивидуально программируемых однопортовых модулей связи для доступа к общей распределительной шине, при этом каждый однопортовый модуль связи содержит программируемый микроконтроллер, выполненный как блок управления доступом к передающей среде Ethernet (MAC), содержащий процессор с сокращенным набором команд (RISC CPU), и логическое устройство распределения кадров данных, предусматривающее обработку в реальном времени и передачу, на адресуемые порты назначения кадров данных Ethernet, поступающих на указанный однопортовый модуль связи, процесс передачи является последовательным и осуществляется в режиме «сохранить и переслать».

Недостатком данного модульного масштабируемого коммутатора является то, что он не может коммутировать данные, представленные в параллельном коде.

Локальные сети, являясь пакетными сетями, используют принцип временного мультиплексирования, то есть распределяют передающую среду во времени, поэтому кадры обрабатываются последовательно.

Известен организатор поля заголовка в сети системы обработки (Selective header field dispatch in a network processing system) [2], в типичных сетях которого используются коммутаторы для продвижения пакетизированных данных от одной точки соединения к другой, точки соединения сети типа коммутаторов используются в узлах организации сети, чтобы достичь наибольшей гибкости и больших функциональных возможностей, ячейка коммутатора, состоящая из входного порта, узла извлечения поля заголовка выходных данных, первой памяти данных, устройства потока входных данных, кадра преобразования входных данных, выходного интерфейса коммутатора, первого процессора сети, второго процессора сети, входного интерфейса коммутатора, узла извлечения поля заголовка входных данных, второй памяти данных, устройства потока выходных данных, кадра преобразования выходных данных, выходной порт, соединенный с первым выходом коммутатора, первый вход которого соединен со входом входного порта, выход которого соединен с первым входом устройства потока входных данных, первый выход которого соединен со входом первого процессора сети, выход которого соединен со вторым входом устройства потока входных данных, второй выход которого соединен со входом выходного интерфейса коммутатора, выход которого является вторым выходом ячейки коммутатора, второй вход которого соединен со входом входного интерфейса коммутатора, выход которого соединен со входом устройства потока выходных данных, выход которого соединен со входом выходного порта.

Недостатком данного организатора поля заголовка в сети системы обработки является то, что он не может коммутировать данные, представленные в параллельном коде. Локальные сети, являясь пакетными сетями, используют принцип временного мультиплексирования, то есть распределяют передающую среду во времени, поэтому кадры отрабатываются последовательно.

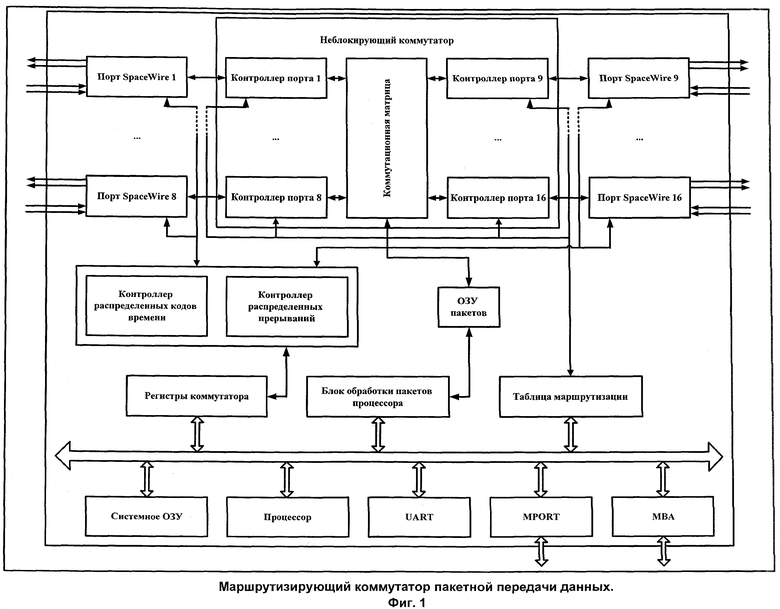

Известен маршрутизирующий коммутатор пакетной передачи данных (МСК-01) [3], состоящий из встроенного процессора, позволяющего организовать детальную обработку ошибочных ситуаций, динамический подбор скоростей передачи, мониторинг и администрирование работы, шестнадцати портов Space Wire, шестнадцати контроллеров портов, коммутационной матрицы, контроллера распределенных кодов времени, контроллера распределенных прерываний, ОЗУ пакетов, регистров коммутатора, блока обработки пакетов процессора, таблицы маршрутизации, системного ОЗУ, каналов прямого доступа М PORT контроллера, внешний 32-разрядный параллельный порт (МВА), предназначенный для подключения к МСК-01 внешнего процессора, соединенный с внутренней магистралью, соединенной с системным ОЗУ, с процессором, с каналами прямого доступа (М PORT), с регистрами коммутатора, с блоком обработки пакетов процессора, с таблицей маршрутизации, входы-выходы которой соединены с первыми входами-выходами шестнадцати контроллеров порта, вторые входы-выходы которых соединены с первыми входами-выходами шестнадцати портов Space Wire, группы выходов которых являются шестнадцатью группами выходов коммутатора, шестнадцать групп входов которого соединены с группами входов шестнадцати портов Space Wire, вторые входы-выходы которых соединены между собой и соединены с первыми входами-выходами контроллера распределенных кодов времени и контроллера распределенных прерываний, вторые входы-выходы контроллеров соединены с регистрами коммутатора, причем вход-выход блока обработки пакетов процессора соединен с первым входом-выходом ОЗУ пакетов, второй вход-выход которого соединен с первым входом-выходом коммутационной матрицы, второй, третий, четвертый, пятый, шестой, седьмой, восьмой, девятый, десятый, одиннадцатый, двенадцатый, тринадцатый, четырнадцатый, пятнадцатый, шестнадцатый, семнадцатый входы-выходы которой соединены с третьими входами-выходами шестнадцати контроллеров портов, причем группа входов-выходов канала прямого доступа (М PORT) является первой группой входов-выходов маршрутизирующего коммутатора, вторая группа входов-выходов которого соединена с внешним 32-х разрядным параллельным портом. Описанное устройство как наиболее близкое к предлагаемому принято за прототип и представлено на фиг.1.

Данный коммутатор не может коммутировать данные представленные в виде байтов.

Недостатком данного коммутатора является то, что он не может обеспечить множественность путей доставки сообщений при логическом способе адресации, для его работы необходимы внешние микросхемы ОЗУ и ПЗУ, у него нет механизма проверки времени жизни сообщений.

Задачей изобретения является коммутация данных, представленных в виде байтов, обеспечение множественности путей доставки сообщений, исключение зацикливания сообщений, введение механизма таймаутов для исключения блокировки сообщений.

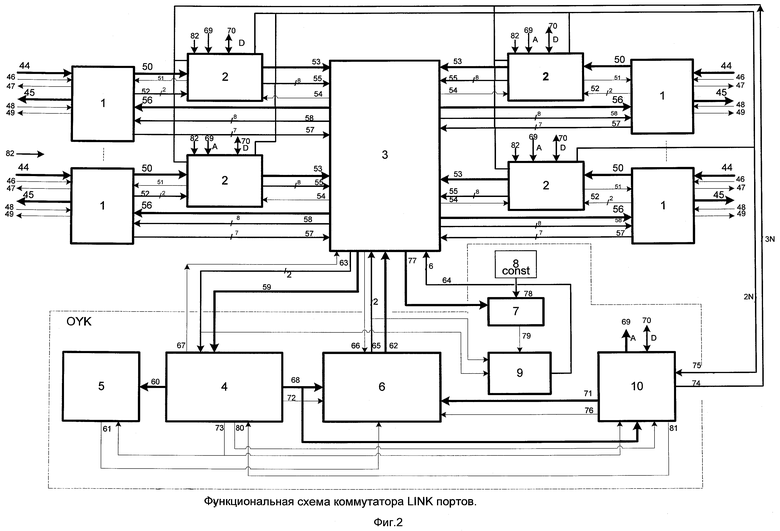

Сущность заявляемого изобретения, возможность его осуществления и промышленного использования поясняются чертежами, представленными на фиг.2 - фиг.28, где:

- на фиг.2 представлена функциональная схема коммутатора LINK-портов;

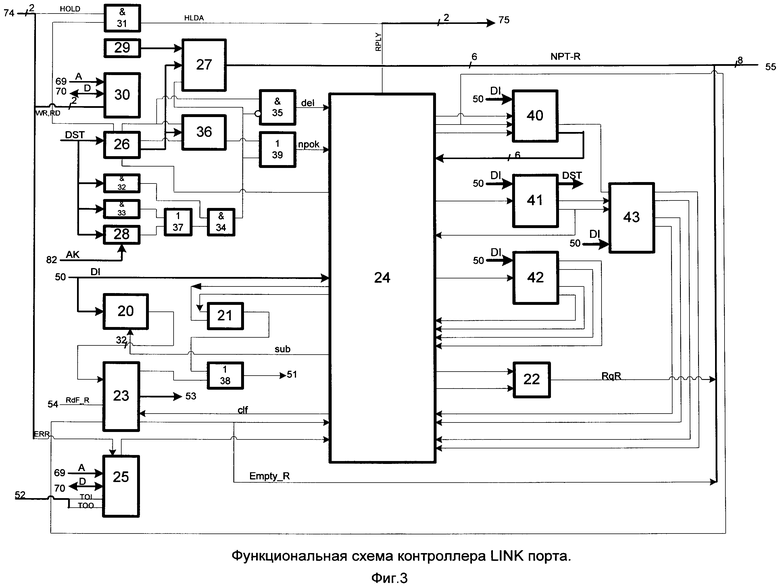

- на фиг.3 представлена функциональная схема контроллера LINK-порта;

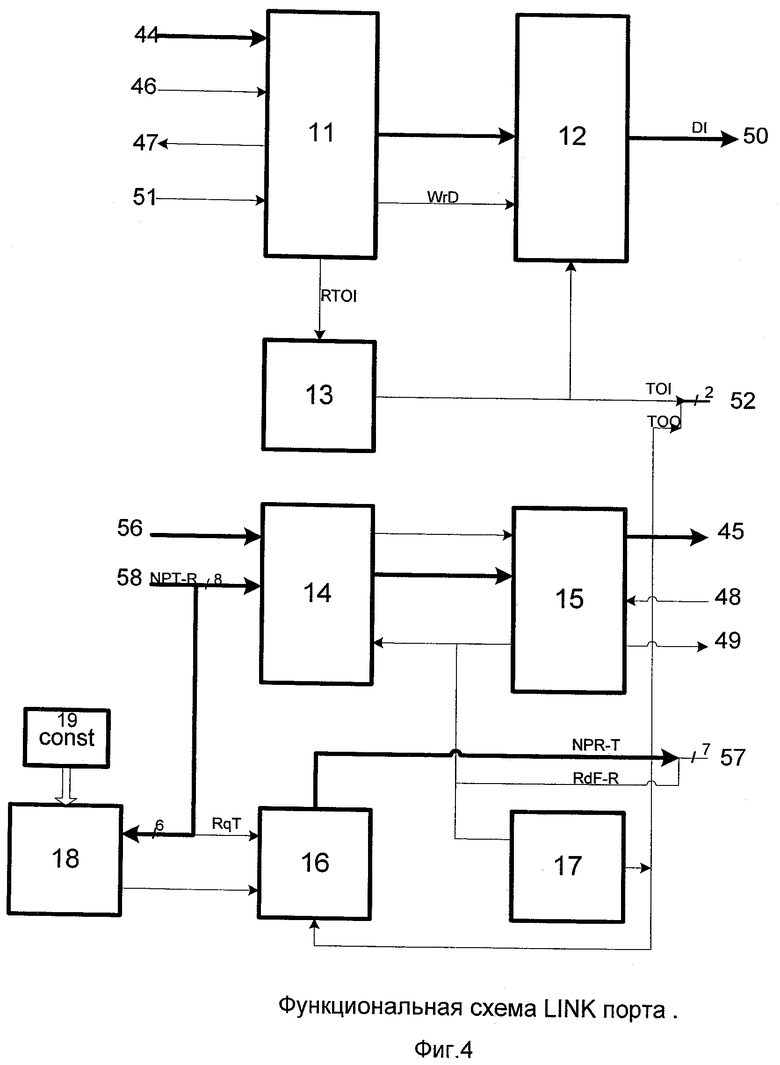

- на фиг.4 представлена функциональная схема LINK-порта;

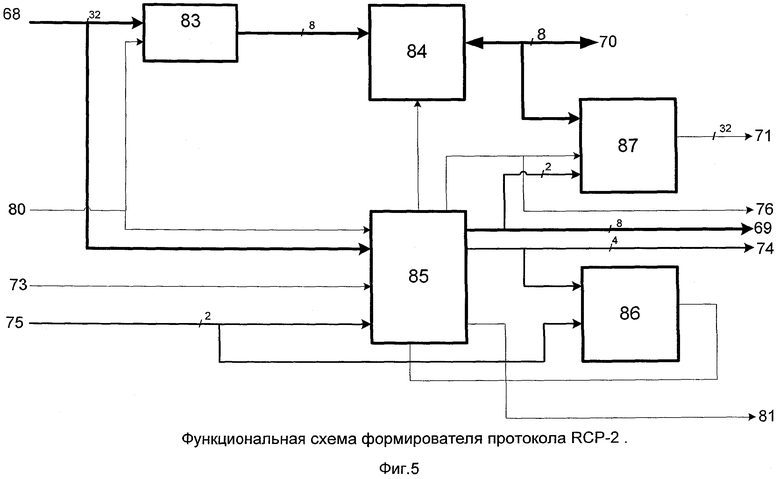

- на фиг.5 представлена функциональная схема формирователя протокола RCP-2;

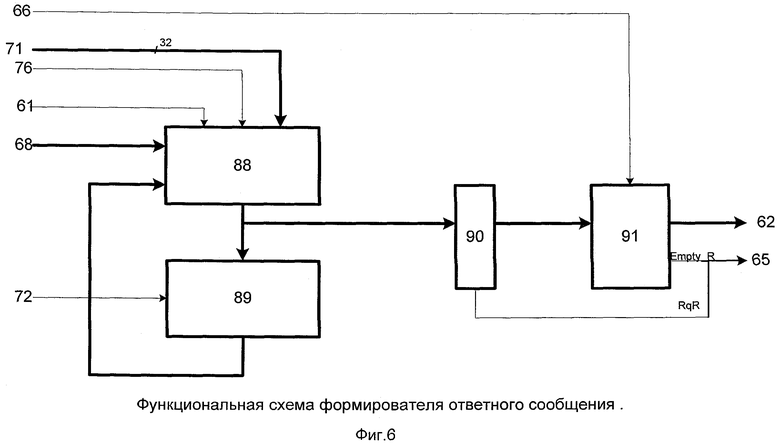

- на фиг.6 представлена функциональная схема формирователя ответного сообщения;

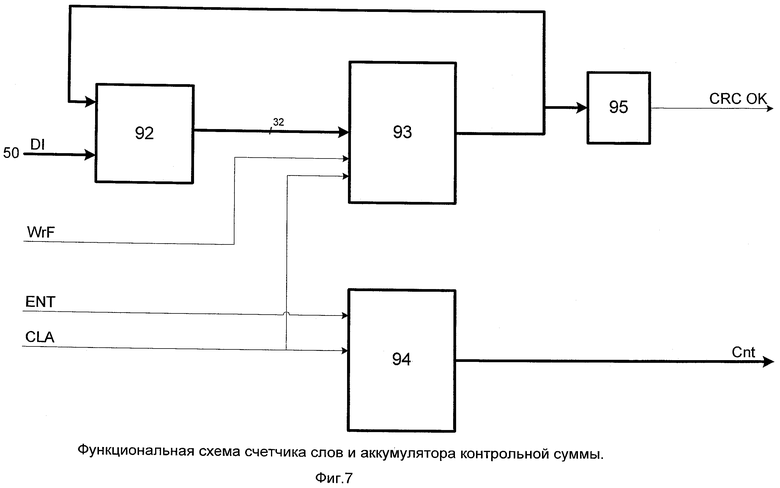

- на фиг.7 представлена функциональная схема счетчика слов и аккумулятора контрольной суммы;

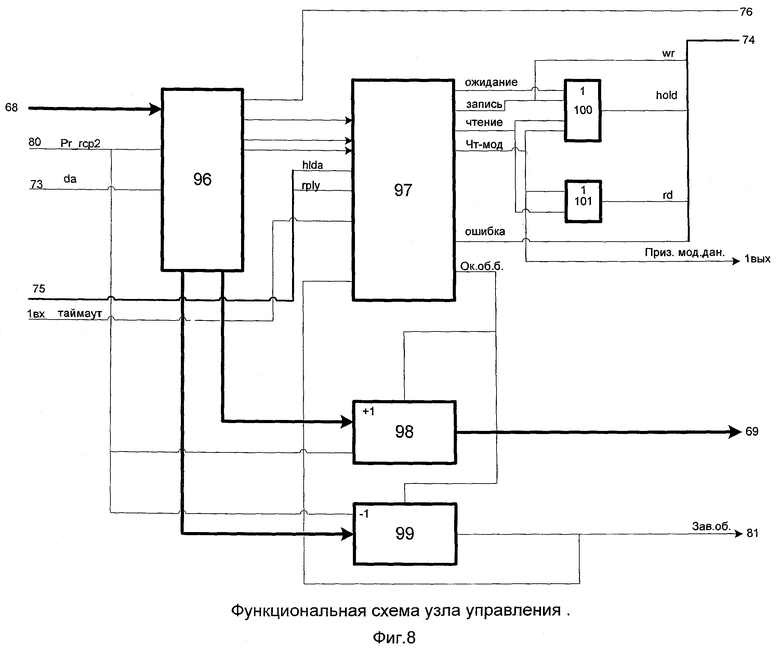

- на фиг.8 представлена функциональная схема узла управления;

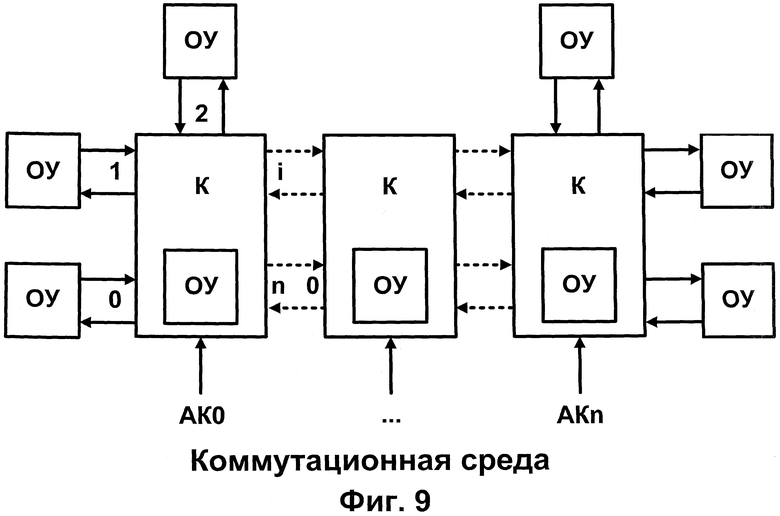

- на фиг.9 представлена коммутационная среда;

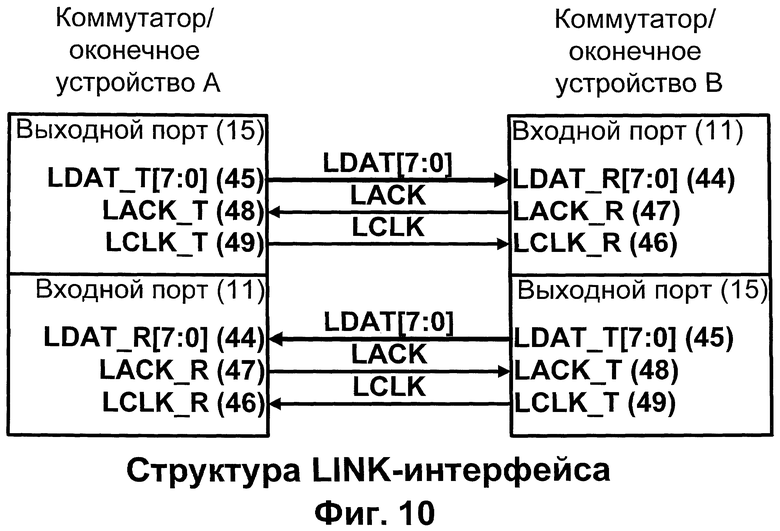

- на фиг.10 представлена структура LINK-интерфейса;

- на фиг.11 представлена таблица 1;

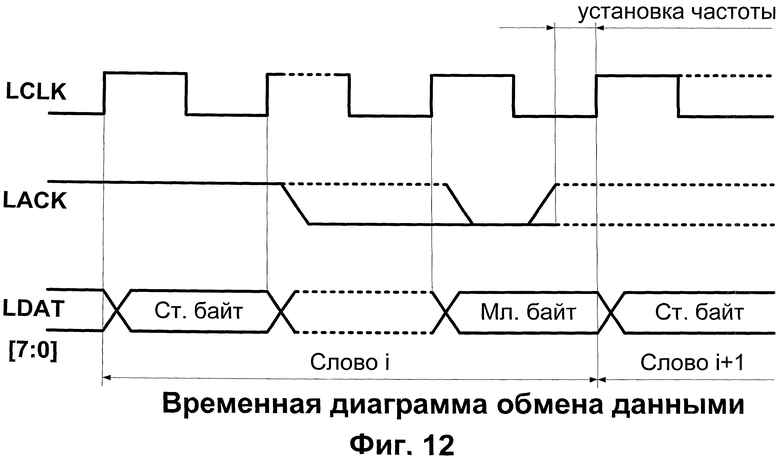

- на фиг.12 представлена временная диаграмма обмена данными;

- на фиг.13 представлен формат заголовка сообщения;

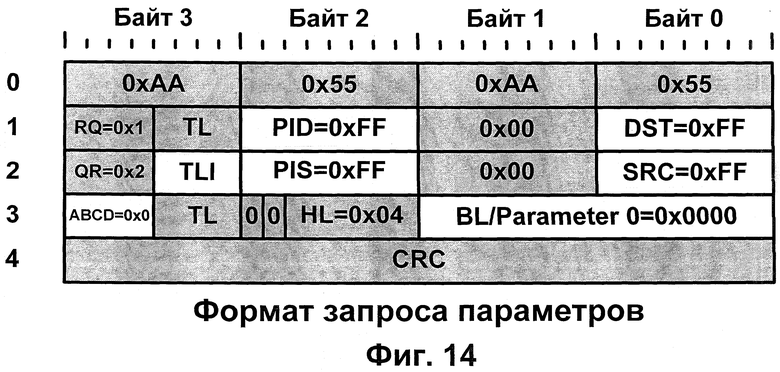

- на фиг.14 представлен формат запроса параметров;

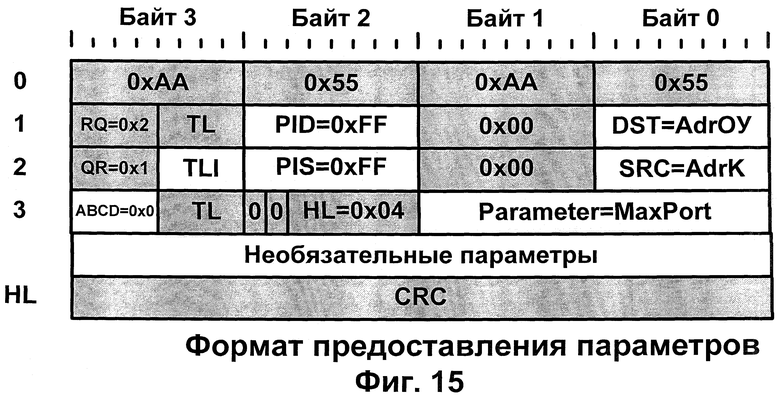

- на фиг.15 представлен формат предоставления параметров;

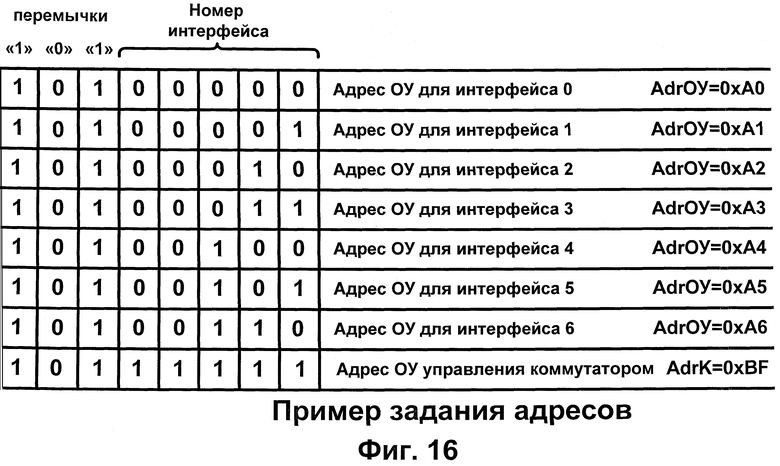

- на фиг.16 представлен пример задания адресов;

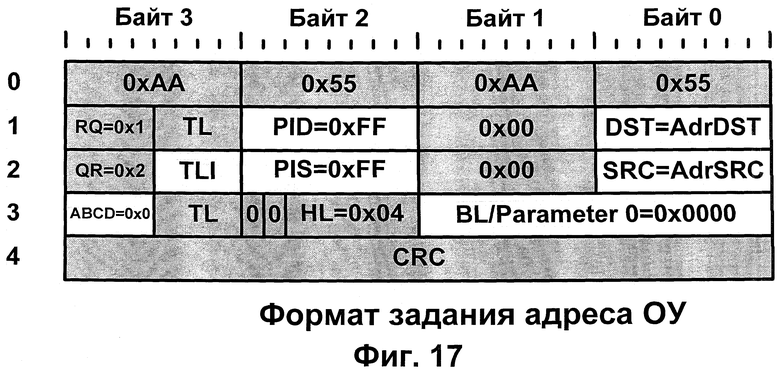

- на фиг.17 представлен формат задания адреса ОУ;

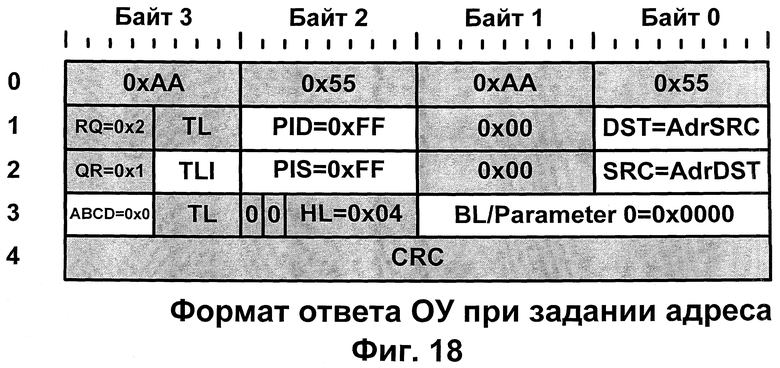

- на фиг.18 представлен формат ответа ОУ при задании адреса;

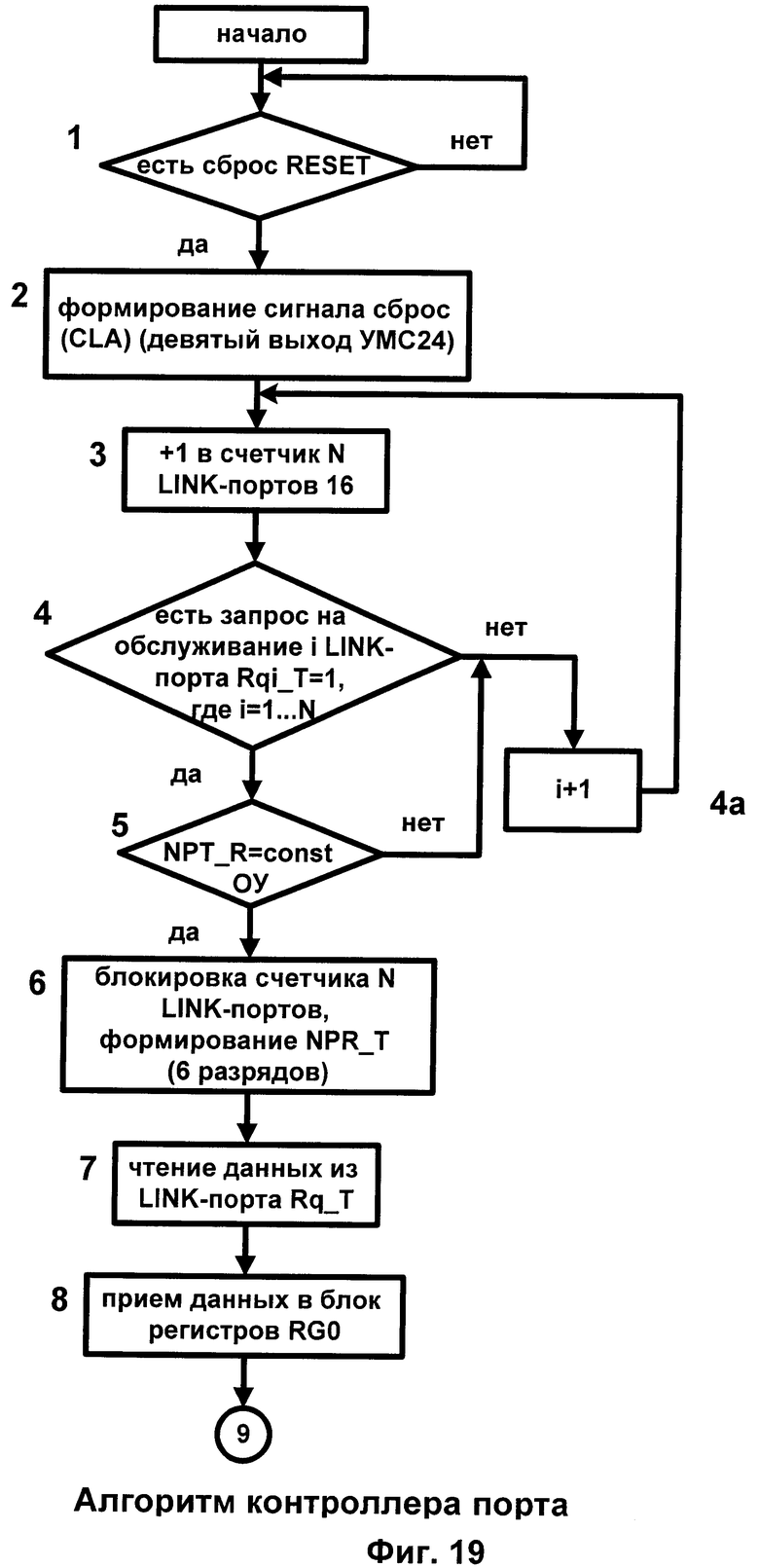

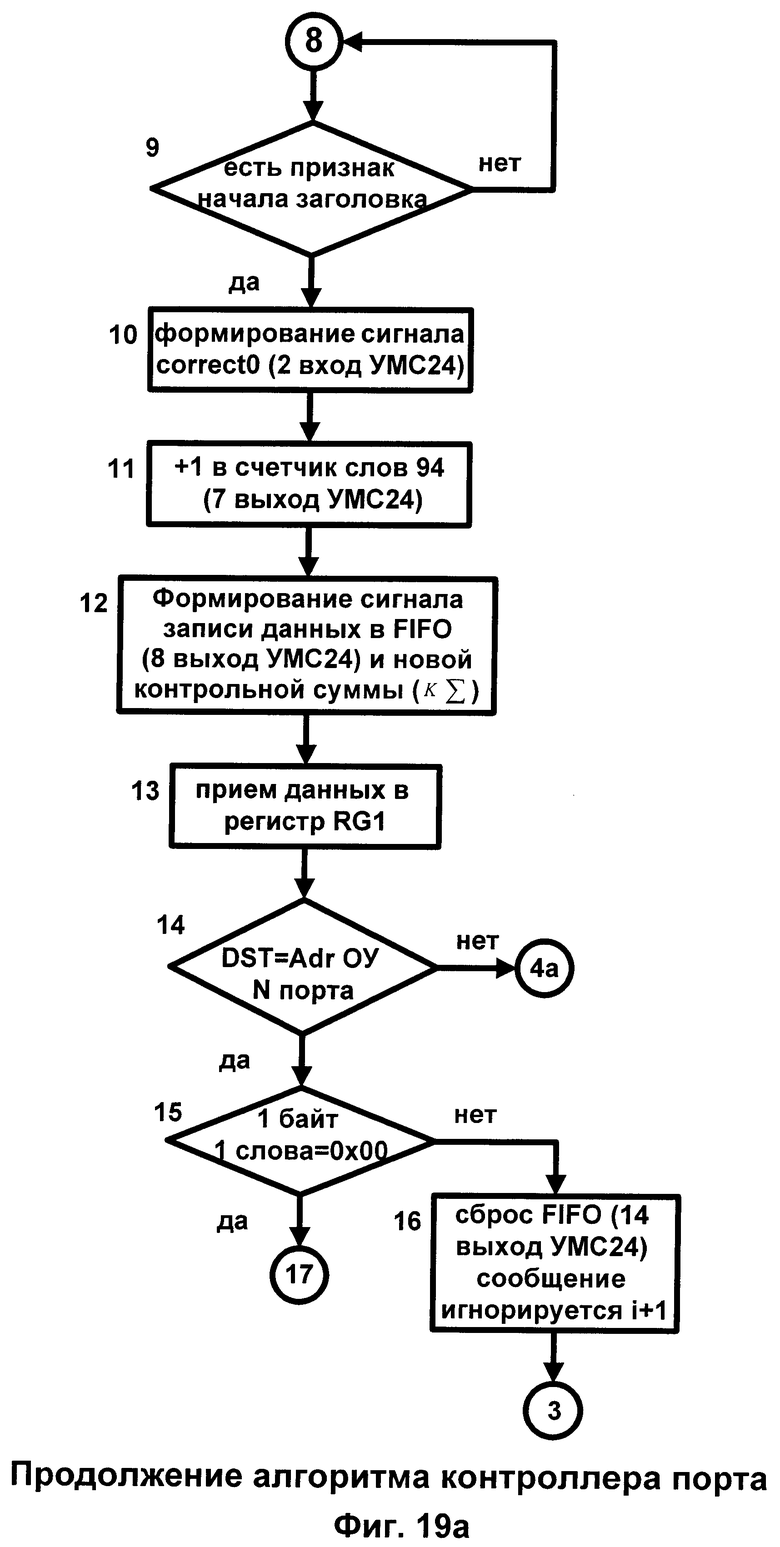

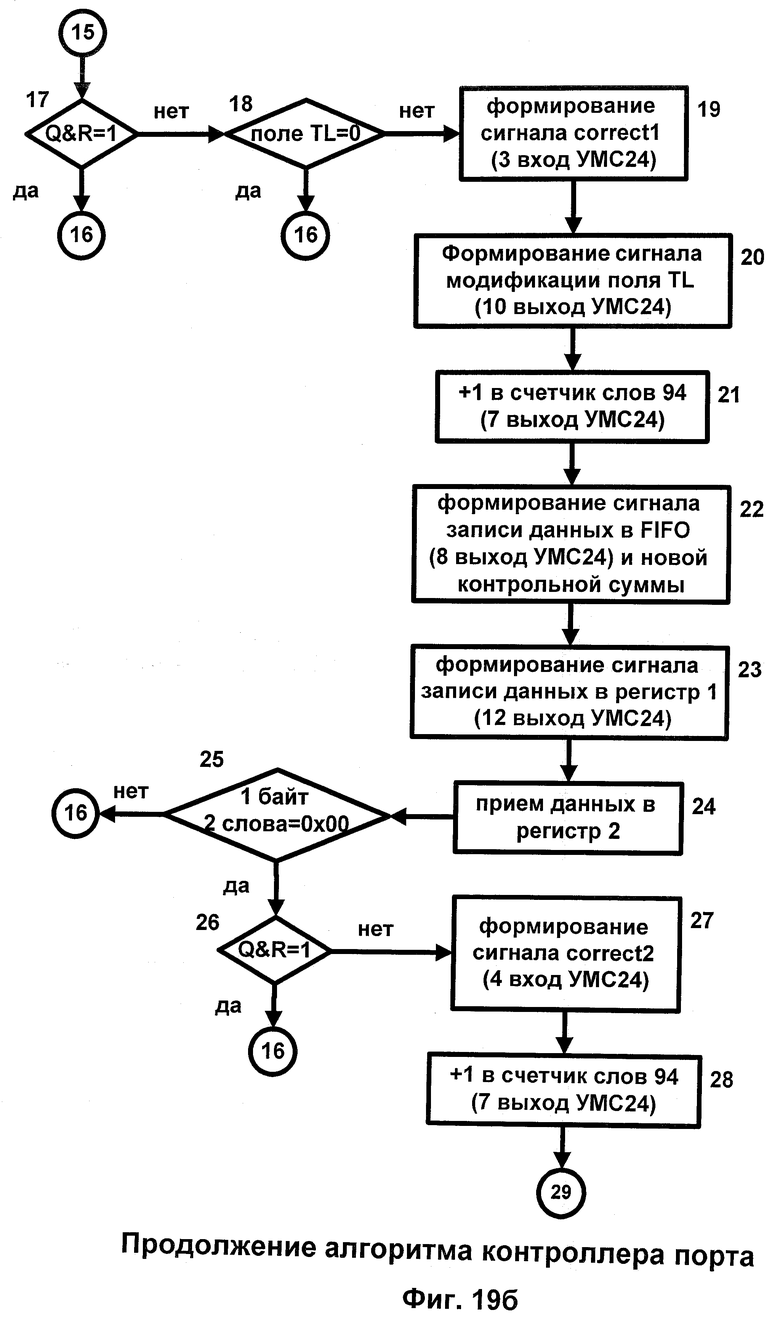

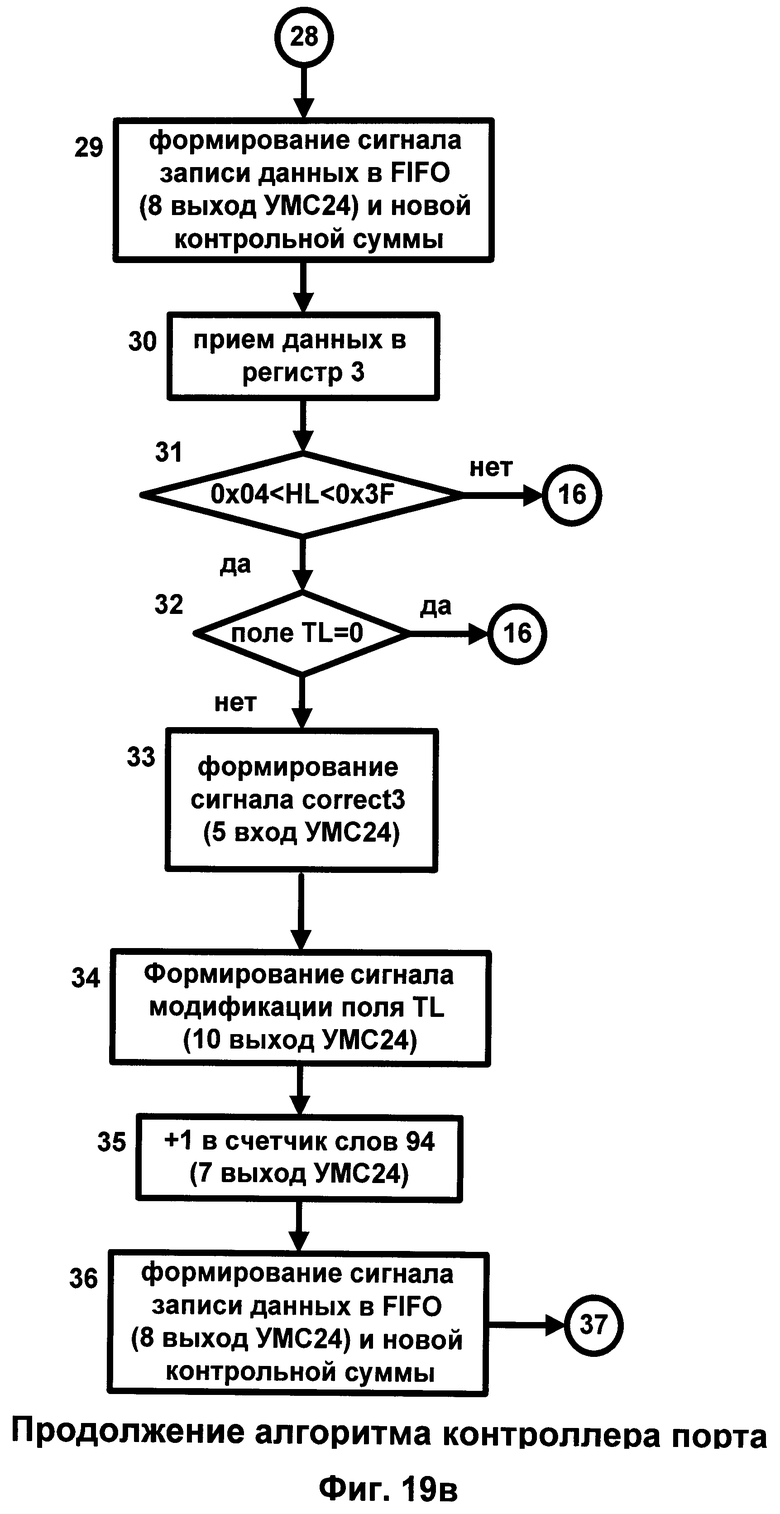

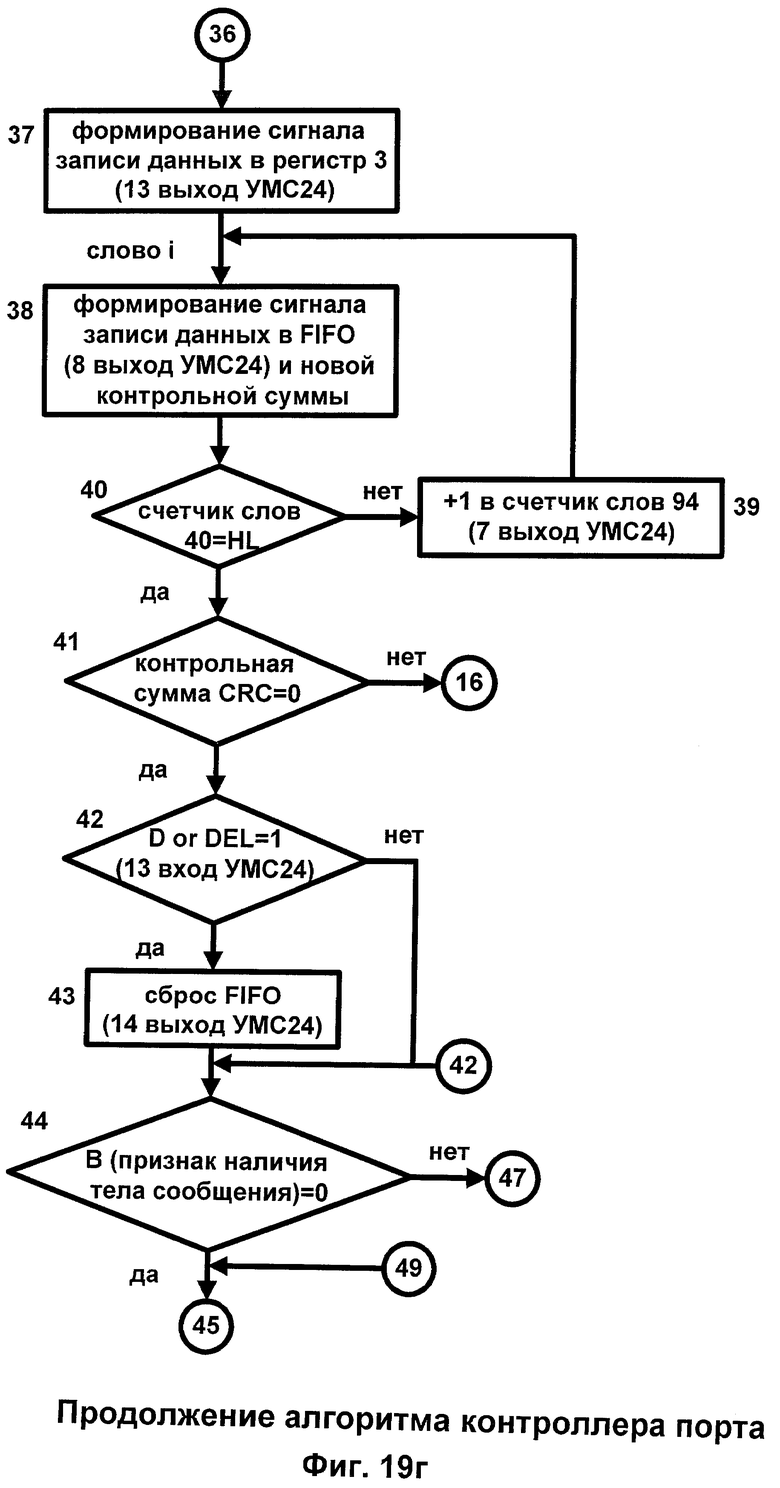

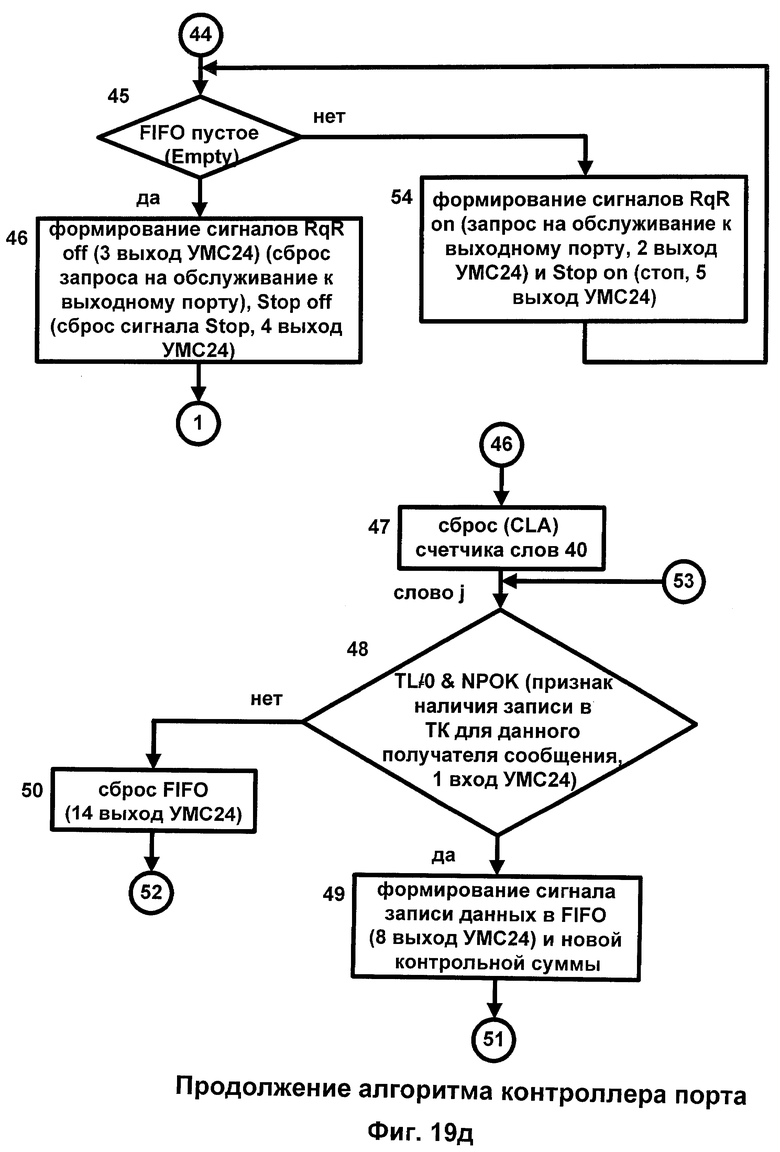

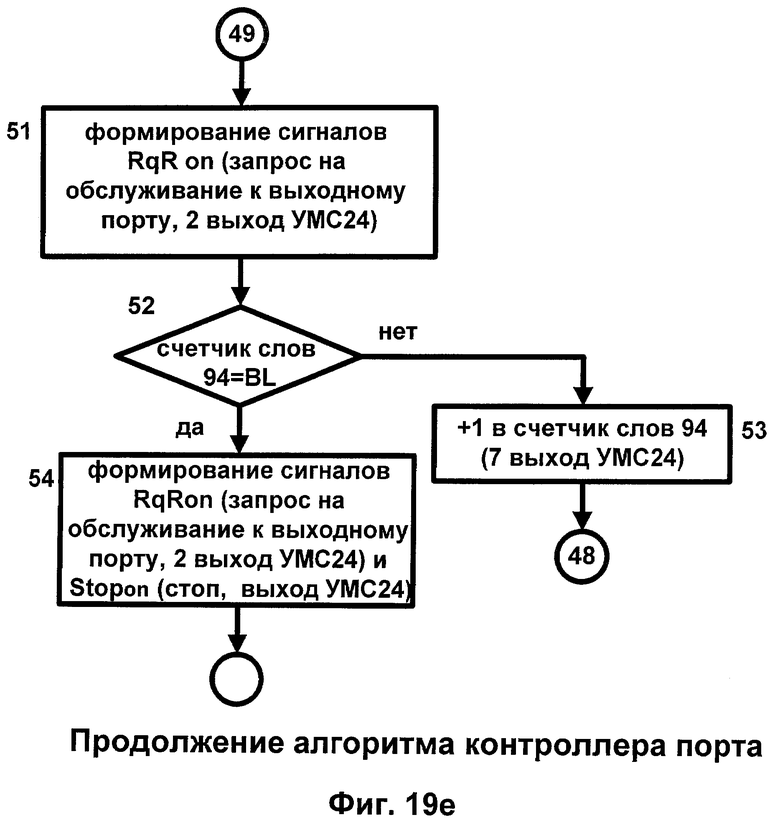

- на фиг.19, 19а, 19б, 19в, 19г, 19д, 19е представлен алгоритм работы контроллера LINK-порта;

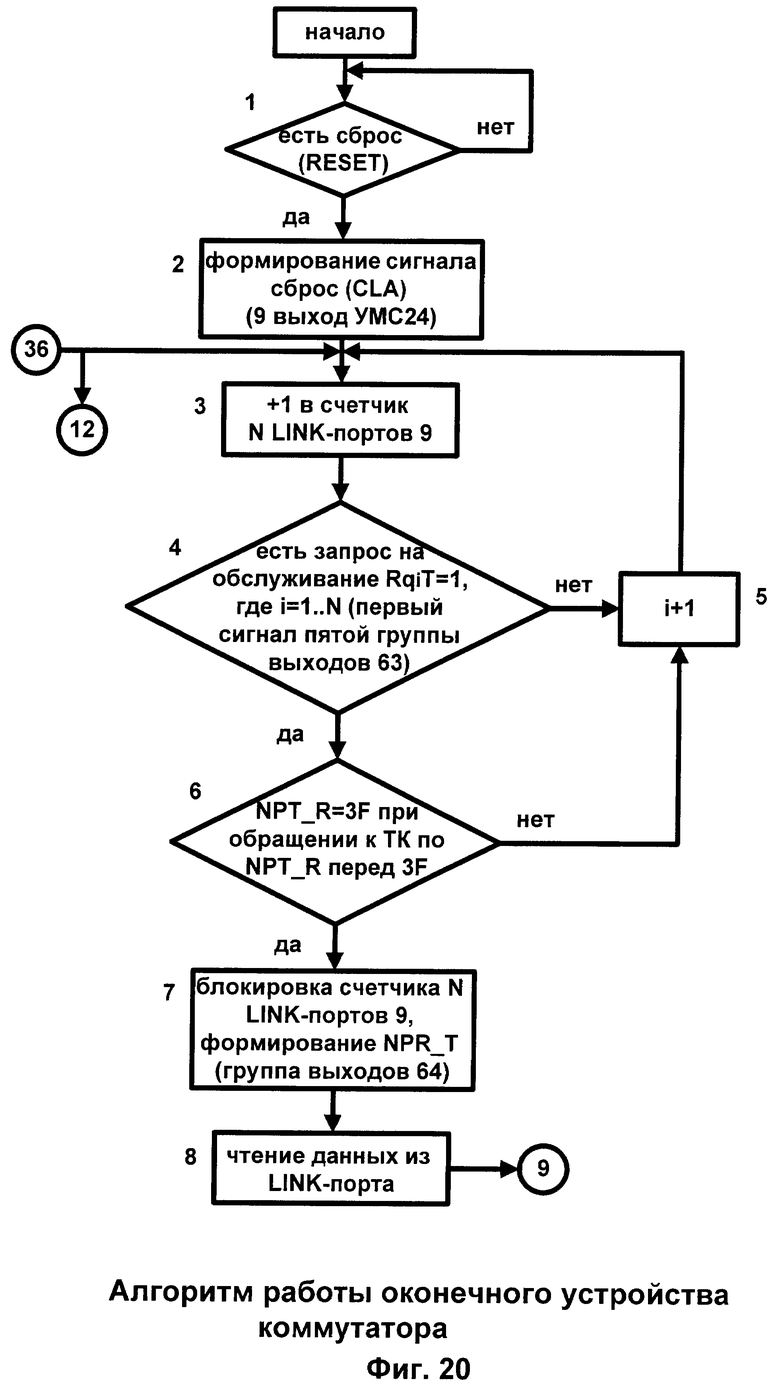

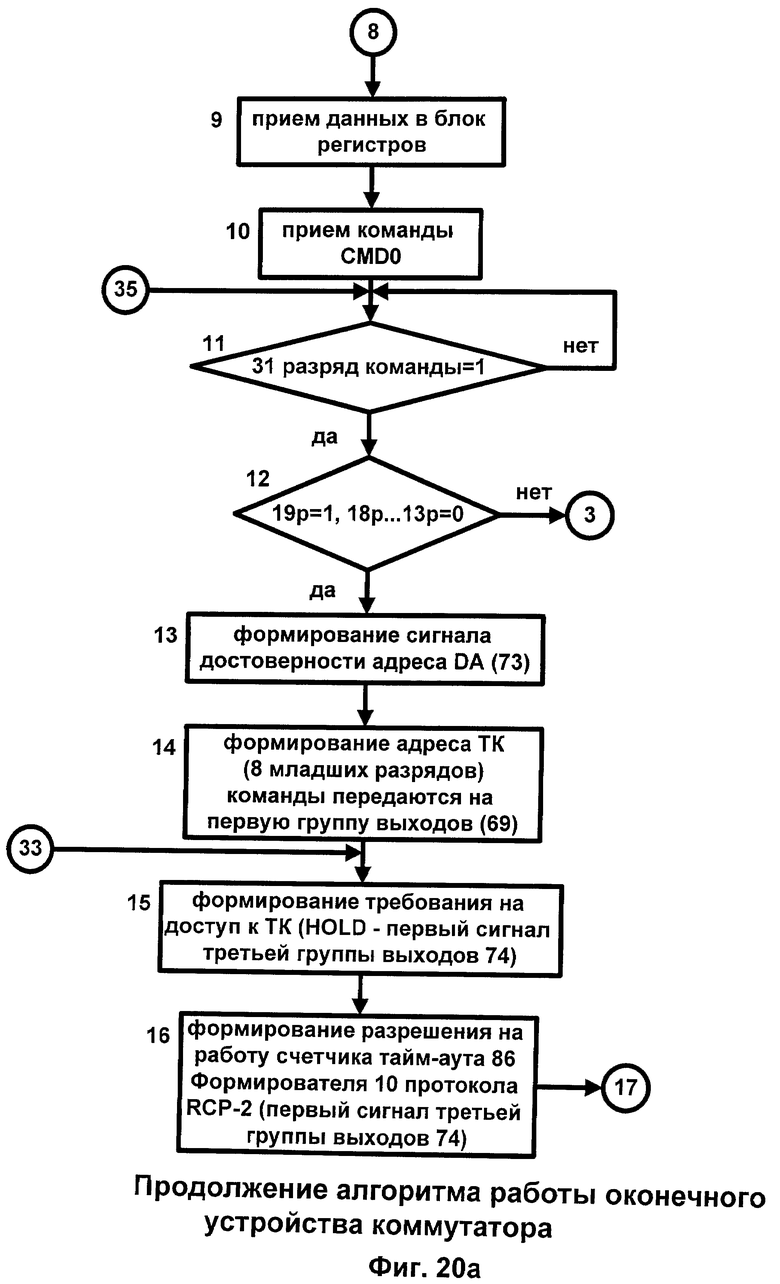

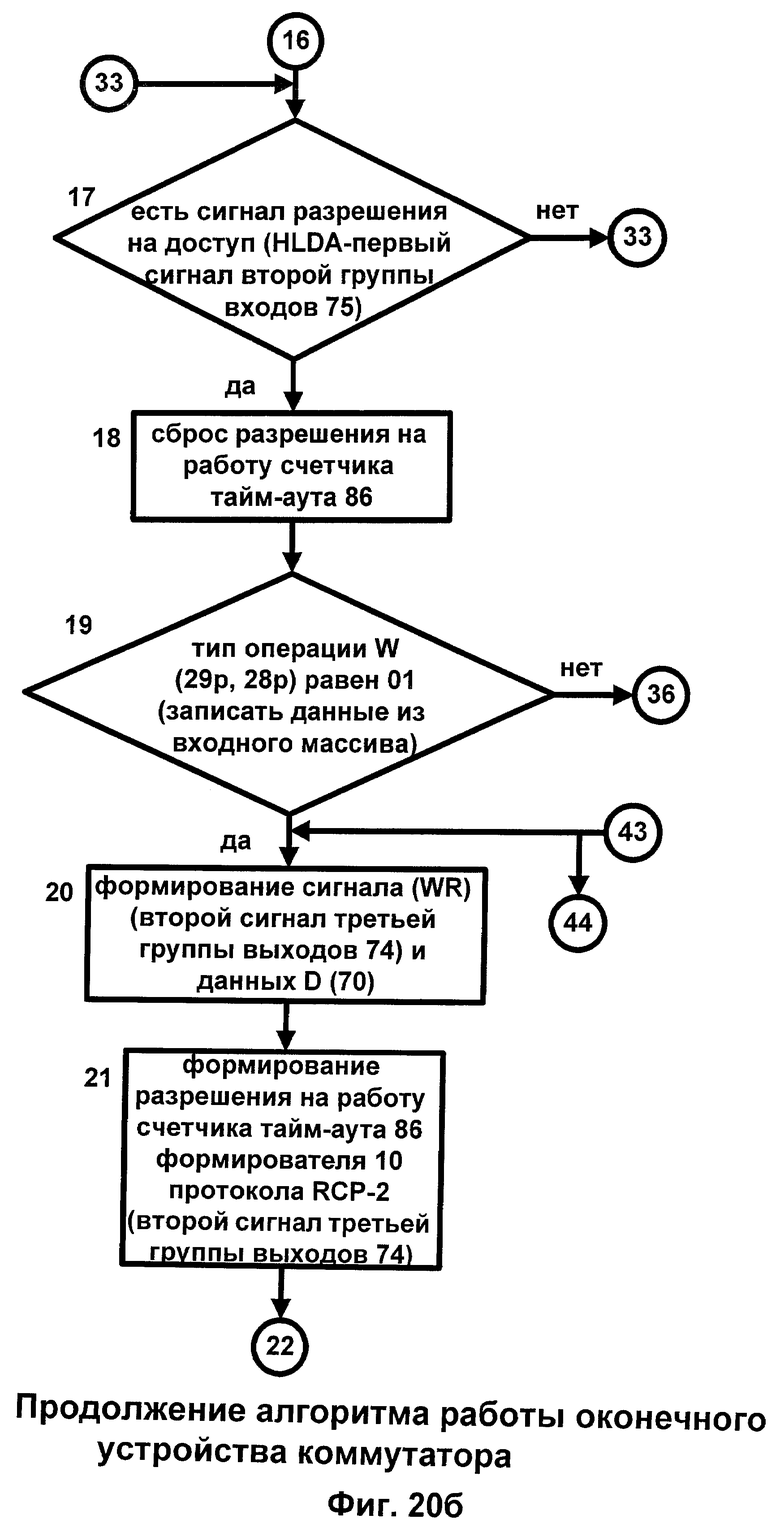

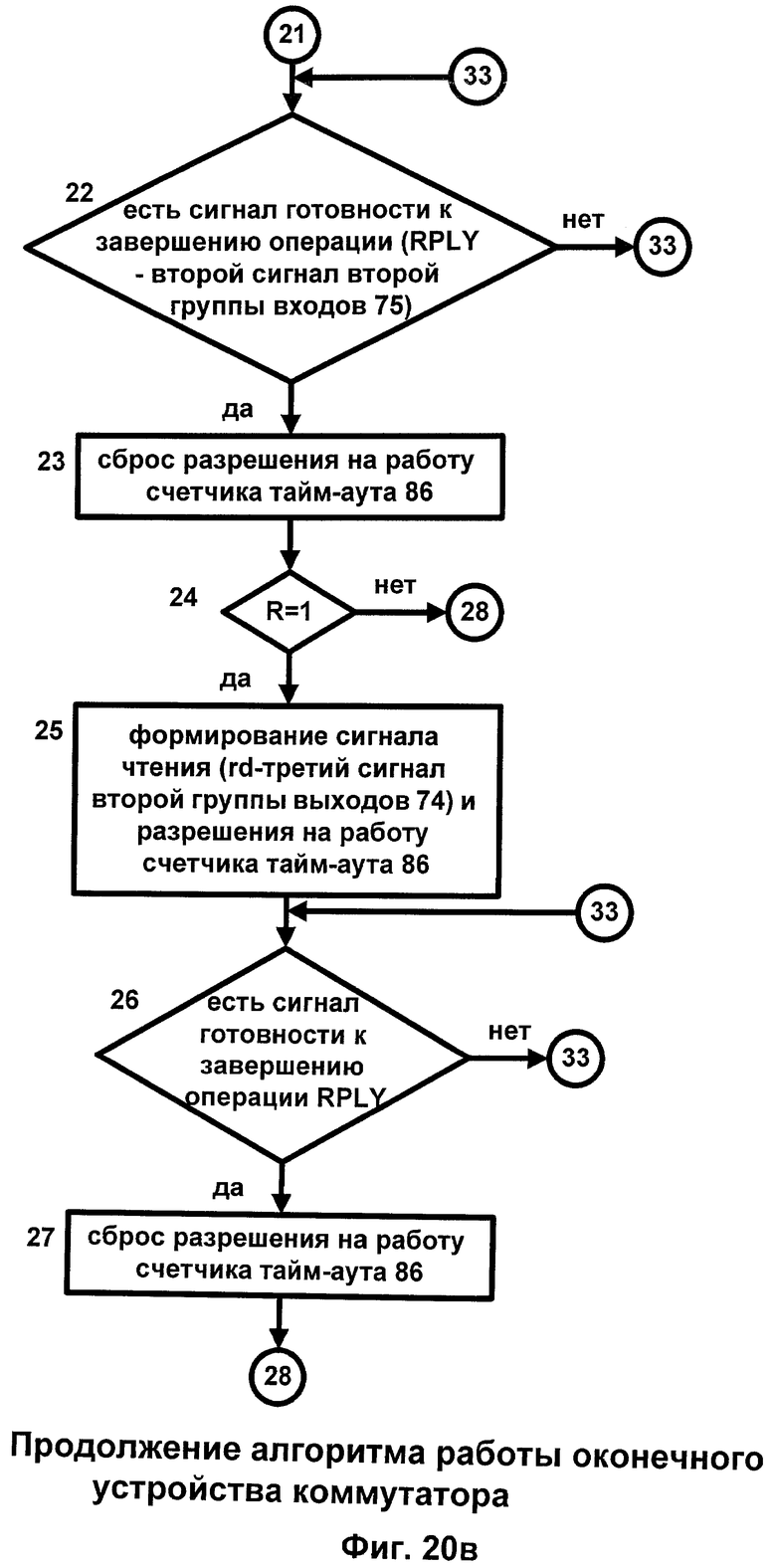

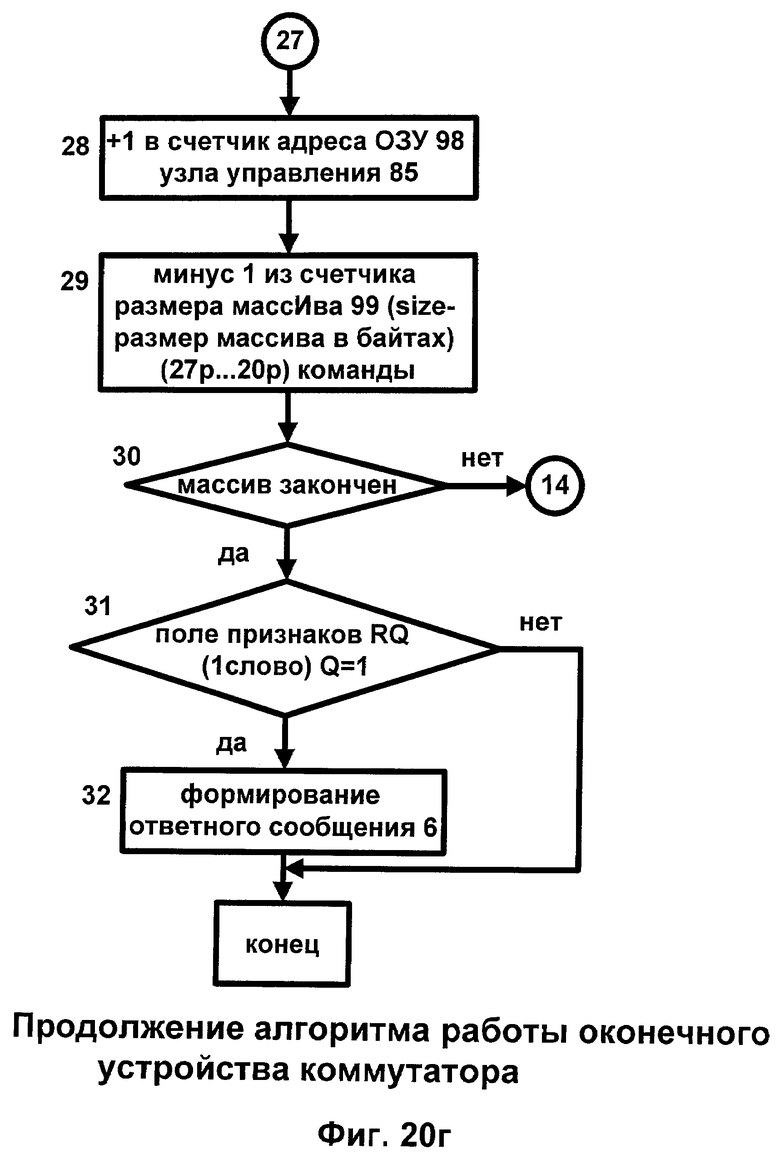

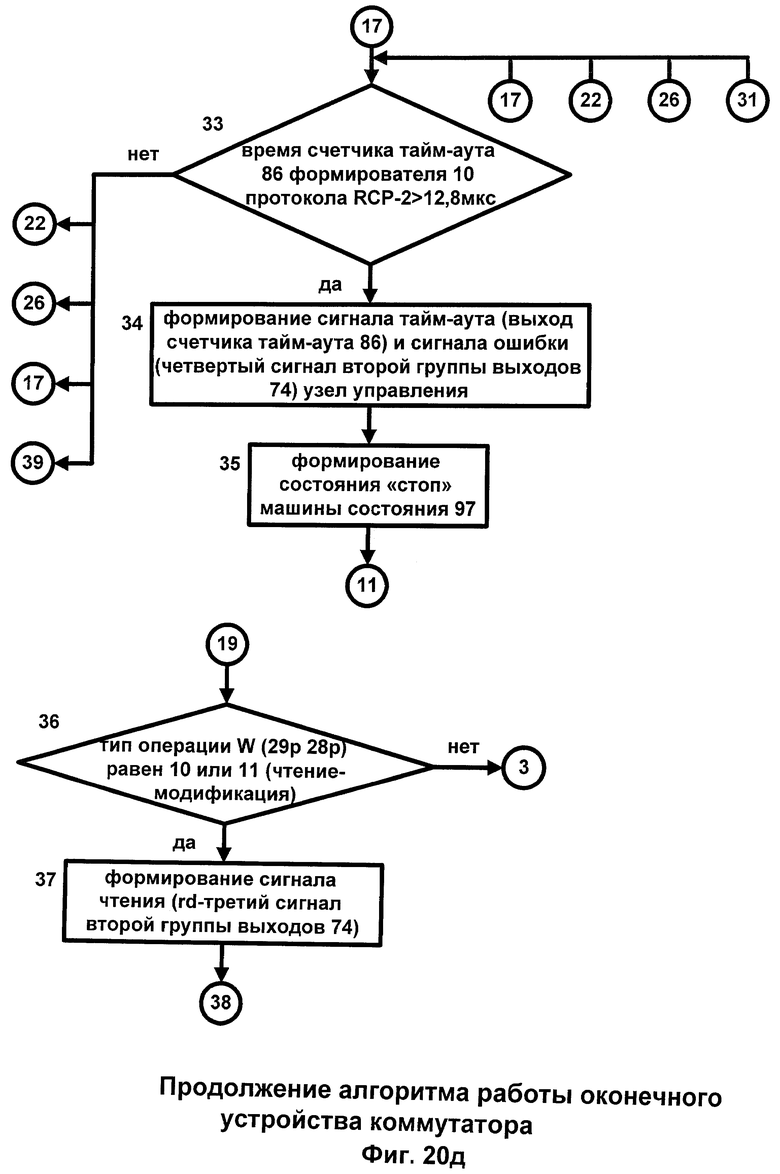

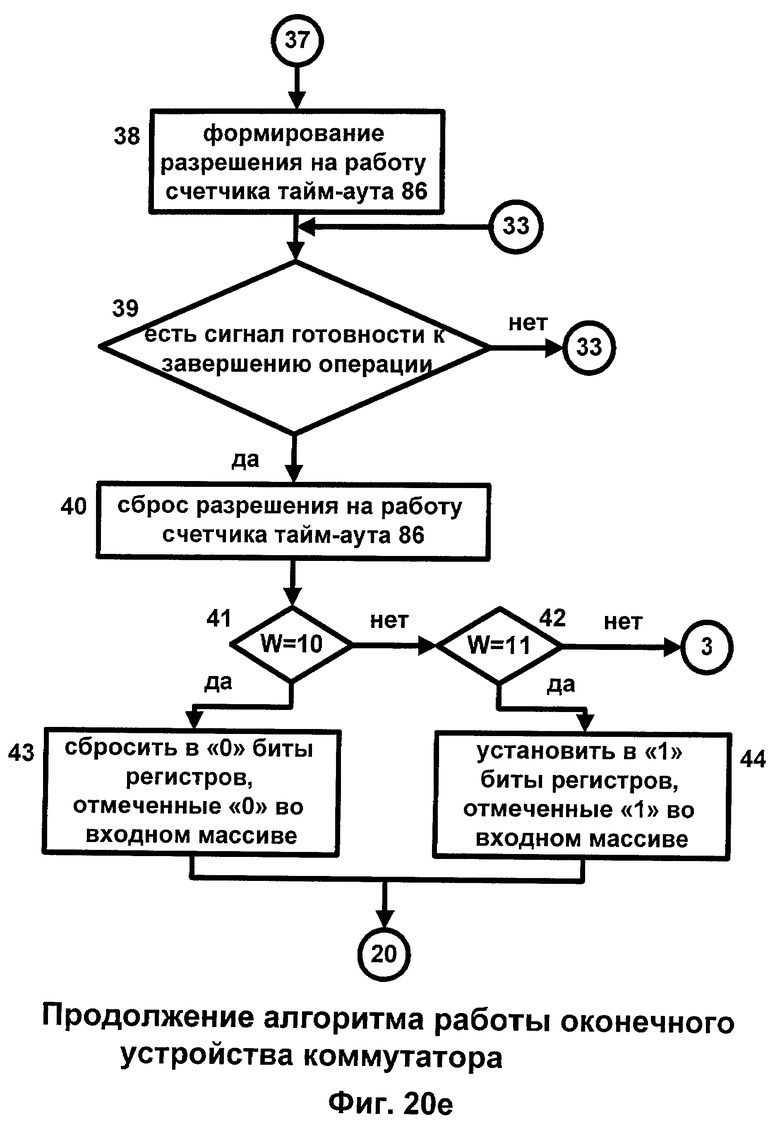

- на фиг.20, 20а, 206, 20в, 20г, 20д, 20е представлен алгоритм работы управляющей машины состояний (УМС);

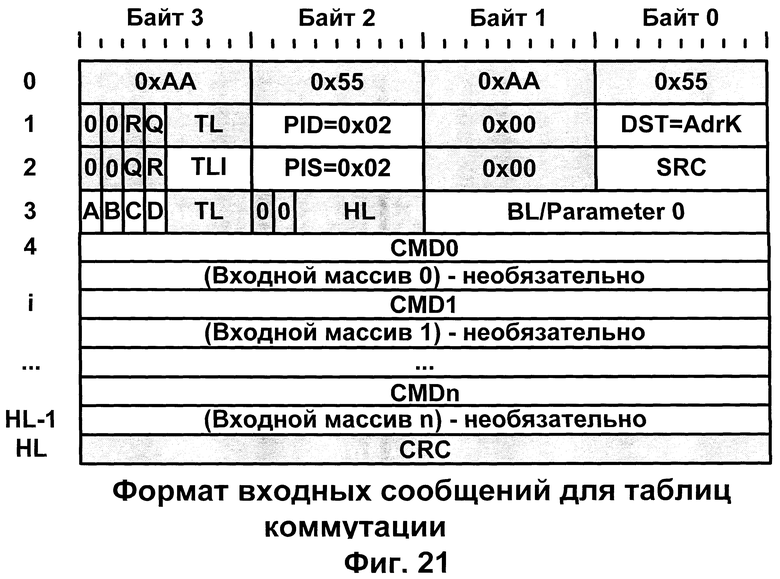

- на фиг.21 представлен формат входных сообщений для таблиц коммутации;

- на фиг.22 представлен формат команд СМД;

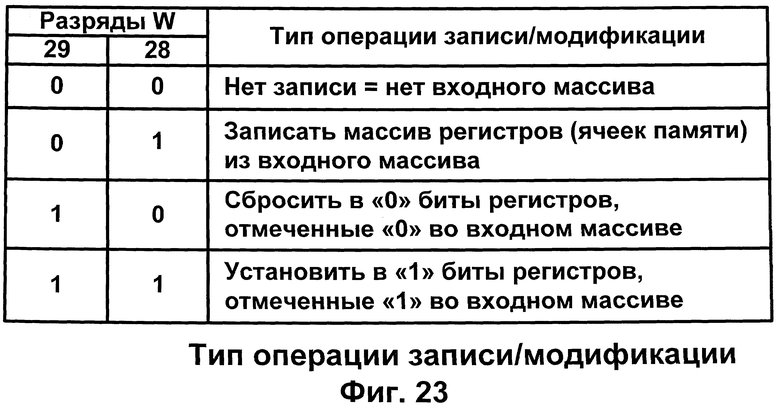

- на фиг.23 представлен тип операции записи/модификации;

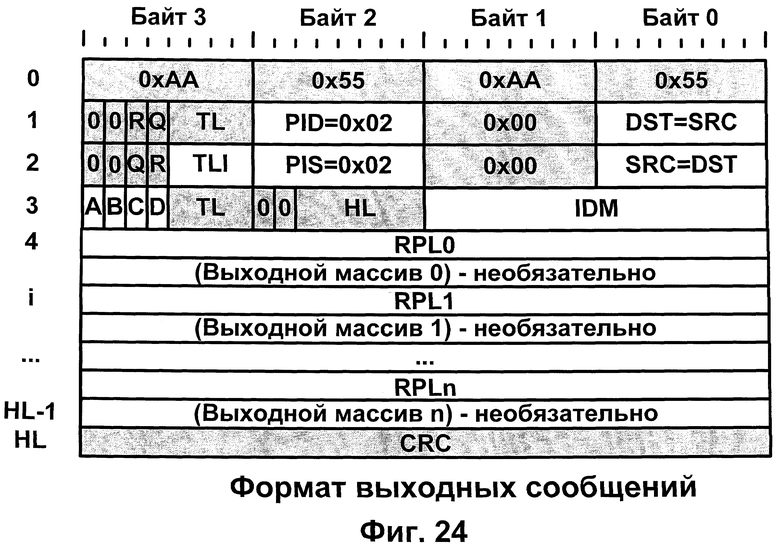

- на фиг.24 представлен формат выходных сообщений;

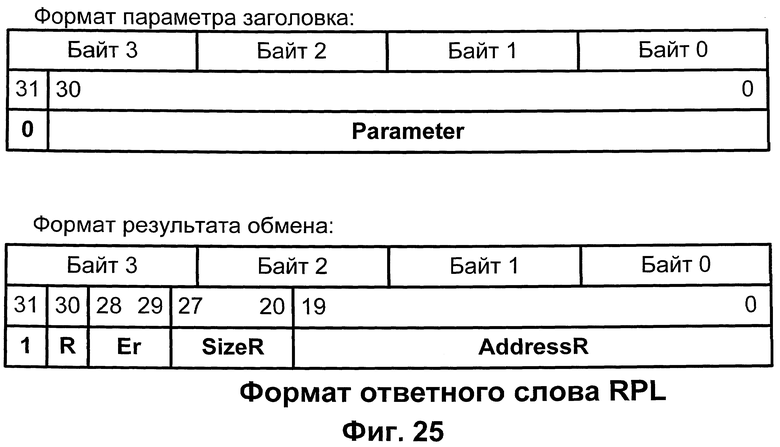

- на фиг.25 представлен формат ответного слова RPL;

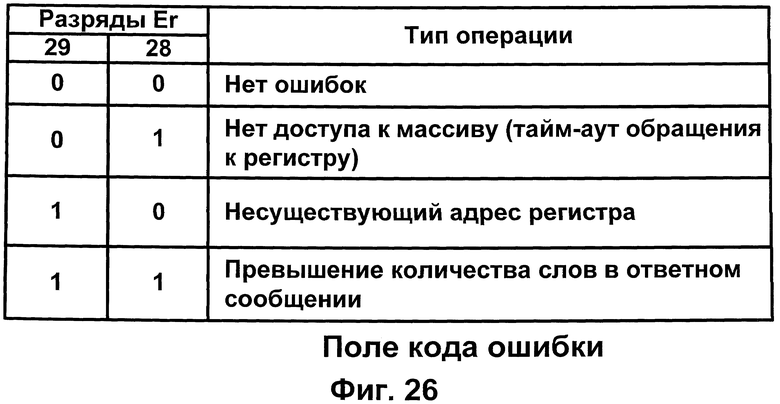

- на фиг.26 представлено поле кода ошибки;

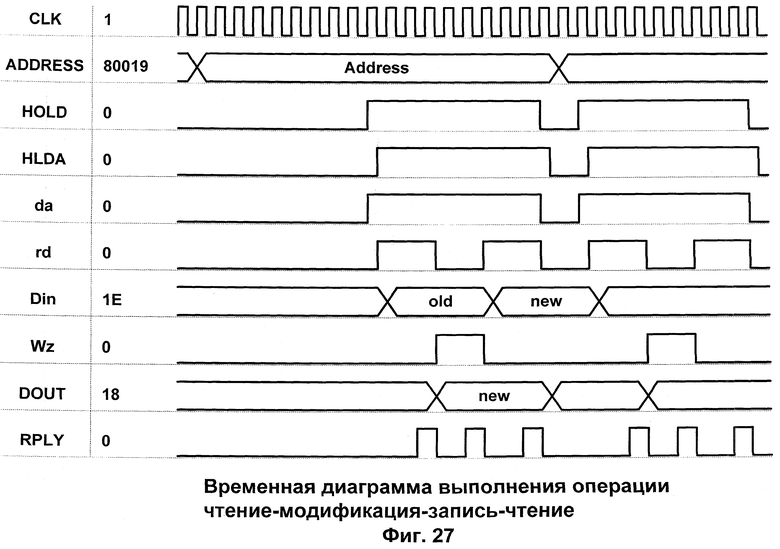

- на фиг.27 представлена временная диаграмма выполнения операции чтение - модификация - запись - чтение;

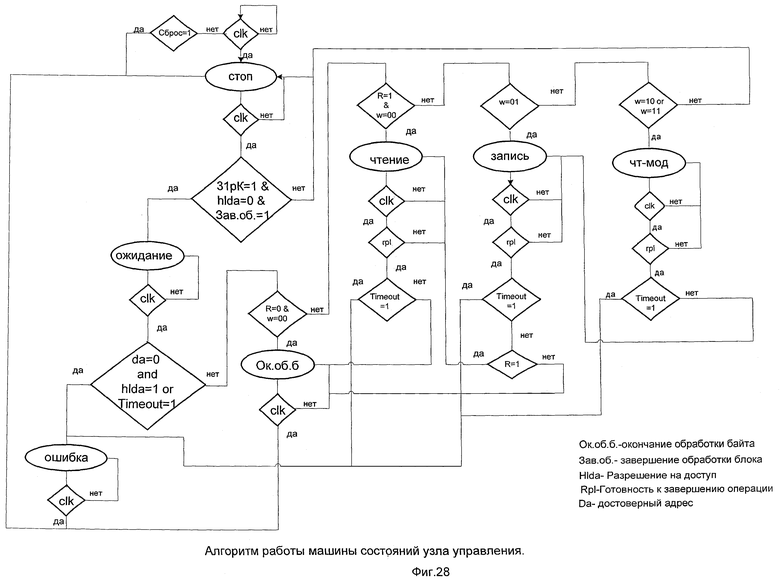

- на фиг.28 представлен алгоритм работы машины состояний узла управления.

Указанные преимущества заявляемого коммутатора LINK-портов перед прототипом достигаются за счет того, что в коммутатор LINK-портов, содержащий N LINK-портов 1, N контроллеров LINK-портов 2, коммутационную матрицу 3, блок регистров 4, дополнительно введены дешифратор протокола выдачи адреса 5, формирователь ответного сообщения 6, схема сравнения 7, константа 8, счетчик номера LINK-портов 9, формирователь 10 протокола RCP-2, в каждый LINK-порт 1 дополнительно введены входной LINK-порт 11, входной буферный регистр 12, счетчик тайм-аута приема 13, выходной буферный регистр 14, выходной LINK-порт 15, счетчик выбора входного порта 16, счетчик тайм-аута выдачи 17, схема сравнения 18, константа 19, в каждый контроллер LINK-порта 2 дополнительно введены узел модификации поля TL 20, первый JK-триггер 21, второй JK-триггер 22, буферная память FIFO 23, управляющая машина состояний 24, регистр состояния 25, ОЗУ1 таблицы коммутации 26, мультиплексор 27, схема сравнения 28, константа 29, ОЗУ2 30, первый 31 элемент И, второй 32 элемент И, третий 33 элемент И, четвертый 34 элемент И, пятый 35 элемент И, узел контроля на нечет 36, первый 37 элемент ИЛИ, второй 38 элемент ИЛИ, третий 39 элемент ИЛИ, счетчик слов и аккумулятор контрольной суммы 40, регистр первого слова заголовка 41, регистр третьего слова заголовка 42, узел проверки слов заголовка 43, причем N первые 44 группы входов коммутатора LINK-портов соединены с N первыми группами входов N LINK-портов 1, N первые группы выходов которых являются N группами выходов 45 коммутатора LINK-портов, N первые 46 входы которого соединены с N первыми входами N LINK-портов 1, N первые 47 выходы которых являются N первыми выходами коммутатора LINK-портов, N вторые 48 входы которого соединены с N вторыми входами N LINK-портов 1, N вторые выходы которых являются N вторыми 49 выходами коммутатора LINK-портов, причем N вторые 50 группы выходов N LINK-портов 1 соединены с N группами входов N контроллеров LINK-портов 2, выходы 51 которых соединены с третьими входами N LINK-портов 1, третья 52 группа выходов которых соединена со вторыми группами входов N контроллеров LINK-портов 2, первые 53 группы выходов которых соединены с N первыми группами входов коммутационной матрицы 3, N выходы 54 которой соединены с первыми входами N контроллеров LINK-портов 2, вторые 55 группы выходов которых соединены с N вторыми группами входов коммутационной матрицы 3, N первые 56 группы выходов которой соединены со вторыми группами входов N LINK-портов 1, четвертые 57 группы выходов которых соединены с N третьими группами входов коммутационной матрицы 3, N вторые 58 группы выходов которой соединены с третьими группами входов N LINK-портов 1, причем четвертая 59 группа выходов коммутационной матрицы 3 соединена с группой входов блока регистров 4, первая 60 группа выходов которого соединена с группой входов дешифратора протокола выдачи адреса 5, выход 61 которого соединен с первым входом формирователя ответного сообщения 6, первая 62 группа выходов которого соединена с четвертой группой входов коммутационной матрицы 3, пятая 63 группа выходов которой соединена со второй группой входов блока регистров 4 и первым входом счетчика номера LINK-портов 9, группа выходов 64 которого соединена с пятой группой входов коммутационной матрицы 3, шестая 65 группа входов которой соединена со вторым входом счетчика номера LINK-портов 9 и второй группой выходов формирователя ответного сообщения 6, второй 66 вход которого соединен с первым выходом коммутационной матрицы 3, первый 67 вход которой соединен с первым выходом блока регистров 4, вторая 68 группа выходов которого соединена с первыми группами входов формирователя ответного сообщения 6 и формирователя 10 протокола RCP-2, первая 69 группа выходов которого соединена с третьими группами входов N контроллеров LINK-портов 2, группы входов-выходов 70 которых соединены с группой входов-выходов формирователя протокола RCP-2 10, вторая 71 группа выходов которого соединена со второй группой входов формирователя ответного сообщения 6, третий 72 вход которого соединен с первым выходом блока регистров 4, второй 73 выход которого соединен с дешифратором протокола выдачи адреса 5 и с первым входом формирователя протокола RCP-2 10, третья 74 группа выходов которого соединена с четвертыми группами входов N контроллеров LINK-портов 2, третьи 75 группы выходов которых соединены со второй группой входов формирователя протокола RCP-2 10, первый 76 выход которого соединен с четвертым входом формирователя ответного сообщения 6, причем шестая 77 группа выходов коммутационной матрицы 3 соединена с первой группой входов схемы сравнения 7, вторая 78 группа входов которой соединена с константой 8, а выход 79 - с третьим входом счетчика номера LINK-портов 9, причем третий 80 выход блока регистров 4 соединен со вторым входом формирователя 10 протокола RCP-2, второй 81 выход которого соединен со входом блока регистров 4, N вторые 82 группы входов коммутатора LINK-портов соединены с пятыми группами входов N контроллеров LINK-портов 2.

Каждый LINK-порт 1 содержит входной LINK-порт 11, входной буферный регистр 12, счетчик тайм-аута приема 13, выходной буферный регистр 14, выходной LINK-порт 15, счетчик выбора входного порта 16, счетчик тайм-аута выдачи 17, схему сравнения 18, константу 19, группа выходов которой соединена с первой группой входов схемы сравнения 18, вторая группа входов которой соединена с первой группой входов выходного буферного регистра 14 и является третьей 58 группой входов LINK-порта, вторая 56 группа входов которого соединена со второй группой входов выходного буферного регистра 14, группа выходов которого соединена с группой входов выходного LINK-порта 15, группа выходов которого является первой 45 группой выходов LINK-порта, вторая 50 группа выходов которого является выходами входного буферного регистра 12, группа входов которого соединена с группой выходов входного LINK-порта 11, группа входов которого является первой 44 группой входов LINK-порта 1, первый вход которого является первым 46 входом входного LINK-порта 11, первый выход которого соединен со входом входного буферного регистра 12, второй вход которого соединен с выходом счетчика тайм-аута приема и является первым сигналом третьей 52 группы выходов LINK-порта 1, второй сигнал которой соединен с первым входом счетчика выбора входного порта 16 и выходом счетчика тайм-аута выдачи 17, вход счетчика тайм-аута приема 13 соединен со вторым выходом входного LINK-порта 11, третий выход которого является первым 47 выходом LINK-порта 1, второй 51 вход которого соединен со вторым входом входного LINK-порта 11, причем восьмой сигнал третьей 58 группы входов LINK-порта 1 соединен со вторым входом счетчика выбора входного порта 16, группа выходов которого является шестью сигналами четвертой 57 группы выходов LINK-порта 1, седьмой сигнал которой соединен со входами счетчика тайм-аута выдачи 17 и выходного буферного регистра 14 и первым выходом выходного LINK-порта 15, второй выход которого является вторым выходом 49 LINK-порта 1, третий вход которого соединен со вторым входом выходного LINK-порта 15, причем выход схемы сравнения 18 соединен с третьим входом счетчика выбора входного порта 16.

Каждый контроллер LINK-порта 2 содержит узел модификации поля TL 20, первый JK-триггер 21, второй JK-триггер 22, буферную память FIFO 23, управляющую машину состояний 24, регистр состояния 25, ОЗУ1 таблицы коммутации 26, ОЗУ2 30, мультиплексор 27, узел контроля на нечет 36, счетчик слов и аккумулятор контрольной суммы 40, регистр первого слова заголовка 41, регистр третьего слова заголовка 42, узел проверки слов заголовка 43, схему сравнения 28, константу 29, первый 31 элемент И, второй 32 элемент И, третий 33 элемент И, четвертый 34 элемент И, пятый 35 элемент И, первый 37 элемент ИЛИ, второй 38 элемент ИЛИ, третий 39 элемент ИЛИ, выход которого соединен с первым входом управляющей машины состояний 24, первый выход которой соединен со входом ОЗУ1 таблицы коммутации 26, группа выходов которого соединена с первыми группами входов мультиплексора 27 и узла контроля на нечет 36, выход которого соединен с первым входом третьего 39 элемента ИЛИ, второй вход которого соединен со входом мультиплексора 27, с инверсным входом пятого 35 элемента И, с выходом четвертого 34 элемента И, первый вход которого соединен с выходом второго 32 элемента И, группа входов DST которого соединена с группами входов DST ОЗУ1 таблицы коммутации 26, третьего 33 элемента И, схемы сравнения 28 и выходом регистра первого слова заголовка 41, группа входов DI которого соединена с группами входов DI управляющей машины состояний 24, узла модификации TL 20, счетчика слов и аккумулятора контрольной суммы 40, регистра третьего слова заголовка 42, узла проверки слов заголовка 43 и является первой 50 группой входов контроллера LINK-порта 2, первая 53 группа выходов которого является группой выходов буферной памяти FIFO 23, первый выход которой соединен с первым входом второго 38 элемента ИЛИ, выход которого является первым 51 выходом контроллера LINK-порта 2, вторая 55 группа выходов которого соединена с группой выходов NPT_R мультиплексора 27, со вторым выходом буферной памяти FIFO 23 и с выходом второго 22 JK-триггера, первый и второй входы которого соединены со вторым и третьим выходами управляющей машины состояний 24, четвертый и пятый выходы которой соединены с первым и вторым входами первого 21 JK-триггера, выход которого соединен со вторым входом второго 38 элемента ИЛИ, причем третья 75 группа выходов контроллера LINK-порта 2 состоит из первого сигнала с выхода первого 31 элемента И и второго сигнала с шестого выхода управляющей машины состояний 24, седьмой, восьмой и девятый выходы которой соединены с первым, вторым и третьим входами счетчика слов и аккумулятора контрольной суммы 40, первый выход которого соединен с первым входом узла проверки слов заголовка 43, первый, второй, третий, четвертый выходы которого соединены со вторым, третьим, четвертым, пятым входами управляющей машины состояний 24 соответственно, десятый выход которой соединен со входом узла модификации TL 20, группа выходов которого соединена с группой входов буферной памяти FIFO 23, второй выход которой соединен с шестым входом управляющей машины состояний 24, восьмой выход которой соединен с первым входом буферной памяти FIFO 23, второй вход которой является первым 54 входом контроллера LINK-порта 2, вторая 52 группа входов которого соединена с первым и вторым входами регистра состояния 25, группа входов-выходов которого соединена с группой входов-выходов ОЗУ2 30 и является группой входов-выходов 70 контроллера LINK-порта 2, третья 69 группа входов которого соединена с первыми группами входов ОЗУ2 30 и регистра состояния 25, выход которого соединен с седьмым входом управляющей машиной состояний 24, одиннадцатый выход которой соединен со входом регистра первого слова заголовка 41, первый выход которого соединен со вторым входом узла проверки слов заголовка 43, третий вход которого соединен со вторым выходом регистра первого слова заголовка 41 и с восьмым входом управляющей машины состояний 24, двенадцатый выход которого соединен с входом регистра третьего слова заголовка 42, первый, второй, третий, четвертый выходы которого соединены с девятым, десятым, одиннадцатым, двенадцатым входами управляющей машины состояний 24 соответственно, тринадцатый вход которой соединен с выходом пятого 35 элемента И, первый вход которого соединен с первым входом узла контроля на нечет 36 и первым выходом ОЗУ1 таблицы коммутации 26, второй выход которого соединен с первым входом первого 31 элемента И, второй вход которого является первым сигналом четвертой 74 группы входов, второй и третий сигналы которой соединены со второй группой входов ОЗУ2 30, а четвертый сигнал соединен с третьим входом регистра состояния, причем константа 29 соединена со второй группой входов мультиплексора 27, пятая 82. группа входов контроллера LINK-порта 2 соединена с группой входов схемы сравнения 28, выход которой соединен с первым входом первого 37 элемента ИЛИ, второй вход которого соединен с выходом третьего 33 элемента И, третий выход ОЗУ1 таблицы коммутации 26 соединен со вторым входом узла контроля на нечет 36, вторая группа входов управляющей машины состояний 24 соединена с группой выходов счетчика слов и аккумулятора контрольной суммы 40, причем тринадцатый выход управляющей машины состояний 24 соединен с третьим входом буферной памяти FIFO 23.

Формирователь 10 протокола RCP-2 содержит преобразователь данных 83, узел выполнения команд 84, узел управления 85, счетчик тайм-аута 86, формирователь ответного массива 87, группа выходов которого является второй 71 группой выходов формирователя 10 протокола RCP-2, первая 69 группа выходов которого соединена с первой группой выходов узла управления 85, вторая группа выходов которого соединена с первой группой входов счетчика тайм-аута 86 и является третьей 74 группой выходов формирователя 10 протокола RCP-2, группа входов-выходов 70 которого соединена с первой группой входов формирователя ответного массива 87 и группой входов-выходов узла выполнения команд 84, группа входов которого соединена с группой выходов преобразователя данных 83, группа входов которого соединена с группой входов узла управления 85 и является первой 68 группой входов формирователя 10 протокола RCP-2, вторая 75 группа входов которого соединена со вторыми группами входов узла управления 85 и счетчика тайм-аута 86, выход которого соединен с первым входом узла управления 85, первый выход которого соединен с первым входом узла выполнения команд 84, причем второй выход узла управления 85 соединен с первым входом формирователя ответного массива 87 и является первым 76 выходом формирователя 10 протокола RCP-2, первый 73 вход которого соединен со вторым входом узла управления 85, третий выход которого является вторым 81 выходом формирователя 10 протокола RCP-2, второй вход которого соединен со входом преобразователя данных 83 и третьим входом узла управления 85, причем два младших сигнала первой группы выходов узла управления 85 соединены со второй группой входов формирователя ответного массива.

Формирователь ответного сообщения 6 содержит мультиплексор 88, аккумулятор контрольной суммы (KΣ) 89, буферный регистр 90, ОЗУ 91, первая группа выходов которого является первой 62 группой выходов формирователя ответного сообщения 6, вторая 65 группа выходов которого является выходом буферного регистра 90 и выходом ОЗУ 91, группа входов которого соединена с группой выходов буферного регистра 90, группа входов которого соединена с группой входов аккумулятора KΣ 89 и группой выходов мультиплексора 88, первая группа входов которого является первой 68 группой входов формирователя ответного сообщения 6, вторая 71 группа входов которого соединена со второй группой входов мультиплексора 88, первый и второй входы которого являются первым 61 и четвертым 76 входами соответственно формирователя ответного сообщения 6, третья группа входов мультиплексора 88 соединена с группой выходов аккумулятора KΣ 89, первый вход которого является третьим 72 входом формирователя ответного сообщения 6, второй 66 вход которого соединен со входом ОЗУ 91.

Счетчик слов и аккумулятор KΣ 40 содержит сумматор 92 по mod 2, регистр 93, счетчик 94 и узел 95 анализа на «0», выход которого является первым выходом счетчика слов и аккумулятора KΣ 40, группа выходов которого соединена с группой выходов счетчика 94, первый вход которого является первым входом счетчика слов и аккумулятора KΣ 40, второй вход которого соединен с первым входом регистра 93, второй вход которого соединен со вторым входом счетчика 94 и является третьим входом счетчика слов и аккумулятора KΣ 40, группа входов 50 которого соединена с первой группой входов сумматора 92 по mod 2, вторая группа входов которого соединена с группой входов узла 95 анализа на «0» и группой выходов регистра 93, группа входов которого соединена с группой выходов сумматора 92 по mod 2.

Узел управления 85 содержит регистр 96, машину состояний 97, счетчик адреса 98, счетчик обмена 99, первый 100 элемент ИЛИ, второй 101 элемент ИЛИ, выход которого является третьим сигналом второй группы выходов 74 узла управления 85, первый сигнал которой соединен с выходом первого 100 элемента ИЛИ, первый вход которого соединен с первым выходом машины состояний 97, второй выход которой соединен со вторым входом первого 100 элемента ИЛИ и является вторым сигналом второй группы выходов 74 узла управления 85, четвертый сигнал которой соединен с третьим выходом машины состояний 97, четвертый выход которой соединен с первым входом второго 101 элемента ИЛИ и третьим входом первого 100 элемента ИЛИ, четвертый вход которого соединен с пятым выходом машины состояний 97, вторым входом второго 101 элемента ИЛИ и является первым выходом узла управления 85, первая 69 группа выходов которого соединена с группой выходов счетчика адреса 98, первый вход которого соединен с первым входом счетчика обмена 99 и является шестым выходом машины состояний 97, первый, второй, третий входы которой соединены с первым, вторым, третьим выходами регистра 96 соответственно, четвертый выход которого является вторым 76 выходом узла управления 85, третий 81 выход которого соединен с выходом счетчика обмена 99 и четвертым входом машины состояний 97, пятый и шестой входы которой являются первым и вторым сигналами второй 75 группы входов узла управления 85, первая 68 группа входов которого соединена с группой входов регистра 96, первая группа выходов которого соединена с группой входов счетчика обмена 99, второй вход которого соединен со вторым входом счетчика адреса 98, первым входом регистра 96 и является третьим 80 входом узла управления 85, второй 73 вход которого соединен со вторым входом регистра 96, вторая группа выходов которого соединена с группой входов счетчика адреса 98, причем первый вход узла управления 85 соединен с седьмым входом машины состояний 97.

Коммутатор LINK-портов работает следующим образом.

Коммутатор LINK-портов предназначен для создания коммутационной среды обмена пакетными сообщениями по LINK-интерфейсам в программно-аппаратных комплексах на основе процессоров ряда «Мультикор». [4]

Среда передачи информации состоит из набора оконечных устройств (ОУ), соединенных между собой через коммутаторы (К) LINK-портов. Коммутационная среда представлена на фиг.9.

Каждое оконечное устройство имеет свой уникальный адрес ОУ, по которому осуществляется его идентификация. В качестве ОУ могут выступать LINK-интерфейсы, входящие в состав процессоров, контроллеров памяти, контроллеров устройств ввода-вывода. Если какое-либо устройство имеет несколько LINK-интерфейсов (так процессор МС-24 [4] имеет 4 LINK-порта и, соответственно, 2 LINK-интерфейса), то каждый из интерфейсов является отдельным ОУ и имеет свой адрес. LINK-интерфейс состоит из двух LINK-портов, соответствующих описанию процессорного ряда «Мультикор».

В паре LINK-портов, составляющих интерфейс, один порт предназначен для выдачи информации (выходной порт 15), другой - для приема информации (входной порт 11). Направление работы порта жестко задается аппаратно или программно при инициализации системы и в процессоре работы не изменяется.

Информация через LINK-порты передается 32-х разрядными словами побайтно, начиная со старшего байта слова.

Структура интерфейса представлена на фиг.10. Состав интерфейсных сигналов и их назначение приведены в таблице 1, представленной на фиг.11. Временная диаграмма обмена данными приведена на фиг.12.

Данные передаются из выходного порта 15 во входной 32-х разрядными словами побайтно (по 4 байта начиная со старшего). Передача выходным портом 15 нового байта осуществляется по переднему фронту тактовой частоты LCLK 49. Задний фронт частоты LCLK 46 используется входным портом 11 для приема байта данных.

Входной порт 11 устанавливает сигнал LACK 47 при наличии готовности к приему следующего слова. Выходной порт 15 стробирует сигнал LACK 48 в момент выдачи нового слова. Если сигнал LACK 48 снят, то выходной порт 15 приостанавливает выдачу нового слова. Сигнал LCLK 49 при этом продолжает выдаваться высоким уровнем, а на линиях LDAT [7:0] 45 продолжается выдача старшего байта. По установке входным портом 11 сигнала LACK 47 выходной порт 15 вырабатывает спадающий фронт сигнала LCLK и продолжает выдачу слова.

В этом случае, если буфер выдачи выходного порта 15 пуст, то сигнал LCLK 49 после выдачи последнего слова остается снятым независимо от состояния сигнала LACK 48.

Адреса ОУ задаются любым образом, обеспечивающим однозначность и уникальность адреса в системе. Как вариант, ОУ могут получать свои адреса от коммутатора LINK-портов, к которому они подключены. В этом случае адрес ОУ состоит из адреса коммутатора LINK-порта и номера интерфейса коммутатора LINK-порта, к которому подключен ОУ.

Все ОУ в системе равноправны и могут по своей инициативе посылать сообщения другим ОУ. В то же время в системе могут присутствовать ОУ, которые посылают сообщения только в ответ на поступившее к ним сообщение - запрос. Как правило, это ОУ, входящее в состав контроллеров памяти и контроллеров ввода-вывода.

Коммутаторы LINK-портов предназначены для маршрутизации сообщений от ОУ - источника до ОУ - приемника сообщения. Для управления маршрутизацией в коммутаторах LINK-портов имеются таблицы маршрутизации. Каждому интерфейсу коммутатора LINK-портов соответствует своя таблица, в которой указывается, на какой выходной порт коммутатора LINK-порта выдавать сообщение для указанного в сообщении адреса ОУ получателя.

Сообщение - логически завершенная и неразрывная порция информации. Сообщение состоит из заголовка сообщения и необязательного тела сообщения. Заголовок сообщения содержит от 5 до 64-х слов. Тело сообщения содержит от 0 до 65536 слов. Заголовок полностью буферизуется в коммутаторе, проверяется на достоверность и допустимость, после чего все сообщение начинает передаваться на выходной порт.

Коммутатор LINK-портов должен проверять достоверность заголовка путем проверки полей, выделенных на фиг.13 серым фоном. Если хотя бы в одном из выделенных полей зафиксировано нарушение формата, то заголовок игнорируется и во входном потоке данных, идущем после слова, в котором зафиксировано нарушение формата, ищется новый заголовок. Если заголовок признан достоверным, то проверяются на допустимость поля, DST и TL. Если зафиксирована недопустимость одного из этих полей, то игнорируется сообщение целиком, т.е. и заголовок и тело сообщения, после чего во входном потоке данных, идущем после сообщения, ищется новый заголовок. Формат заголовка сообщения представлен на фиг.13.

Заголовок содержит:

Слово 0 - Признак начала заголовка

Должен содержать 0xАА55АА55, предназначен для первоначального выделения заголовка из поступающего на входной порт потока информации. Окончательное выделение заголовка из потока информации считается завершенным после проверки коммутатором достоверности заголовка путем проверки других полей заголовка.

Слово 1 - Описатель получателя сообщения

- байт 0: DST - адрес ОУ - получателя сообщения. Используется коммутаторами для определения номера выходного порта на который необходимо передать сообщение. Если указанный номер не содержится в таблице маршрутизации входного порта коммутатора, сообщение игнорируется;

- байт 1: зарезервирован, должен содержать 0x00, нарушение этого условия считается нарушением формата заголовка и приводит к его игнорированию;

- байт 2: PID - описатель вложенного протокола для ОУ - получателя сообщения (определяется соглашениями для конкретных ОУ);

- байт 3 имеет следующие поля:

- TL - текущее время жизни сообщения, определяет количество коммутаторов через которое может пройти сообщение. В каждом коммутаторе из содержимого данного поля вычитается единица. Если на коммутатор поступило сообщение с нулевым полем TL, то сообщение игнорируется.

Поле TL используется для ограничения распространения сообщений в тех случаях, когда из-за неправильной настройки таблиц коммутации в коммутационной среде образуются замкнутые петли, по которым сообщение могло бы передаваться бесконечно.

Поле TL это единственное поле заголовка, которое изменяется при прохождении через коммутатор. Для того, чтобы избежать пересчета контрольной суммы в коммутаторе (которая рассчитывается как поразрядное сложение по mod 2 всех слов заголовка) данное поле дублируется в слове 3 заголовка. При одновременном изменении двух идентичных полей контрольная сумма не изменяется.

- 00RQ - поле признаков, где

Q - reQuest - данный признак должен быть установлен, если на данное сообщение ОУ - приемником сообщения должно быть выдано ответное сообщение в адрес ОУ - источника сообщения;

R - Reply - признак ответного сообщения.

В поле признаков может быть установлен только один из признаков Q или R (или ни одного), старшие два разряда поля признаков должны быть нулевыми. Нарушение данного условия считается нарушением формата заголовка и приводит к его игнорированию.

Слово 2 - Описатель источника сообщения

- байт 0: SRC - адрес ОУ - источника сообщения, используется ОУ - получателем для формирования ответного сообщения;

- байт 1: зарезервирован, должен содержать 0х00, нарушение этого условия считается нарушением формата заголовка и приводит к его игнорированию;

- байт 2: PIS - описатель протокола для ОУ - источника сообщения. Как правило, указанный в данном поле протокол должен быть использован для выдачи ответного сообщения и совпадает с PID;

- байт 3 имеет следующие поля:

- TLI - исходное время жизни сообщения - как правило, определяет через какое количество коммутаторов может пройти ответное сообщение. Данное поле в коммутаторе не изменяется и используется ОУ - получателем для формирования ответного сообщения. ОУ - получатель в поле TL ответного сообщения записывает значение из поля TLI исходного сообщения, а в поле TLI ответного сообщения - значение из поля TL исходного сообщения;

- 00QR - поле признаков

Содержимое данного поля должно соответствовать признакам, установленным в описателе получателя сообщения. Нарушение данного условия считается нарушением формата заголовка и приводит к его игнорированию.

В целом формат описателя источника сообщения полностью соответствует формату описателя приемника сообщения, с тем чтобы использовать его в качестве такового при выдаче ОУ - получателем ответного сообщения, для чего достаточно поменять слова 1 и 2 местами.

Слово 3 - описатель сообщения

- байты 0 и 1: BL/Parameter 0 - Длина тела сообщения/Параметр.

Поле BL содержит длину тела сообщения в словах минус 1, если разряд В поля признаков установлен, и произвольный параметр, если разряд В сброшен. Максимальное количество слов в теле сообщения равно 65536 (BL=0×FFFF).

В качестве параметра при сброшенном разряде В рекомендуется использовать информацию о требуемой длине тела в ответном сообщении.

- байт 2: HL - длина заголовка

Поле HL содержит длину заголовка, начиная с признака начала заголовка и завершая контрольной суммой минус 1. Заголовки с количеством слов менее 5 (HL<0×04) или более 64 (HL>0×3F) коммутатором игнорируется.

- байт 3 содержит следующие поля:

- TL - копия соответствующего поля из описателя получателя сообщения. Несовпадение двух копий полей является нарушением формата заголовка и приводит к его игнорированию.

- ABCD - поле признаков,

А - Address. Признак должен быть установлен, если в заголовке присутствует необязательный параметр Mem_Address - адрес памяти в составе ОУ. Разряд А должен быть установлен именно в том случае, когда слово параметра используется ОУ в качестве адреса памяти, так как само наличие параметра/параметров определяется длиной заголовка через поле HL. Данный разряд введен для унифицированного обращения к адресам памяти в составе ОУ;

В - Body - признак наличия тела сообщения.

При установленном разряде В поле BL содержит длину тела сообщения, при сброшенном - произвольный параметр.

С - Custom - резервный признак.

D - Delete - признак удаления заголовка сообщения. При установке данного признака коммутатор передает на выходной порт только тело сообщения. Заголовок сообщения может быть также удален коммутатором независимо от признака D, если об этом есть указания в таблице маршрутизации коммутатора.

Слова 4-HL-1 - Параметры

Формат необязательных параметров и, в частности, адреса памяти ОУ Mem_Address должен определяться соглашениями для конкретных ОУ.

Слово HL - Контрольная сумма

Контрольная сумма CRC подсчитывается методом поразрядного сложения по модулю 2 (исключающего ИЛИ) всех слов заголовка, предшествующих контрольной сумме. Таким образом, поразрядное суммирование по модулю 2 всех слов заголовка, включая контрольную сумму должно давать нулевой результат. В противном случае заголовок сообщения должен игнорироваться.

При программном способе задания адреса ОУ он определяется при помощи коммутатора LINK-портов, к которому подключено ОУ.

Для обеспечения возможности получения адреса от коммутатора LINK-портов в начальный момент времени, когда адрес коммутатора LINK-портов для ОУ еще неизвестен, имеется зарезервированный адрес получателя DST=0×FF и зарезервированный код протокола PID=0×FF.

При поступлении сообщения адресом назначения DST=0×FF коммутатор LINK-портов должен считать, что сообщение адресовано ему, и должен выдать ответное сообщение на интерфейс, по которому поступило сообщение.

В ответном сообщении коммутатор LINK-портов должен выдавать служебную информацию, содержащую адрес коммутатора LINK-портов, номер интерфейса, по которому выдано ответное сообщение и другую служебную информацию.

Информация по адресу 0×FF доступна только по чтению. Для записи управляющей информации в коммутатор LINK-портов, должен использоваться его собственный адрес (адрес входящего в коммутатор LINK-портов ОУ).

Для получения адреса от коммутатора LINK-портов ОУ должно выдать на него сообщение формата, представленного на фиг.14.

Коммутатор LINK-портов должен выдать ответное сообщение формата, представленного на фиг.15.

В поле DST коммутатор LINK-портов подставляет адрес, назначаемый ОУ. В поле SRC коммутатор LINK-портов подставляет адрес ОУ, входящего в состав коммутатора LINK-портов и предназначенного для управления им.

В поле параметра коммутатор LINK-портов подставляет максимальный номер внешнего LINK-интерфейса коммутатора LINK-портов. Внешние интерфейсы (порты) коммутатора имеют номера от 0 до N. В зависимости от числа внешних портов и, соответственно, от числа N, для аппаратного задания адреса коммутатора LINK-портов требуется различное число сигнальных линий.

Например, при количестве внешних интерфейсов коммутатора LINK-портов равном 32, они нумеруются от 0 до MaxPort=0×001F. Пять младших разряда адреса ОУ будут определяться номером интерфейса коммутатора LINK-портов, к которому они подключены. Для адреса ОУ управления коммутатором LINK-портов пять младших разрядов должны быть равны «лог.1».

Старшие три разряда адреса ОУ подключенных к коммутатору LINK-портов и ОУ управления коммутатором LINK-портов, входящего в его состав, должны задаваться аппаратно, например перемычками на внешних выводах коммутатора LINK-портов (см. пример задания адресов, представленных на фиг.16).

Описанный выше способ соответствует случаю, когда адрес ОУ назначается ближайшим к нему коммутатором LINK-портов по инициативе ОУ. Этот способ ориентирован на процессорные ОУ, например LINK-интерфейсы процессоров «Мультикор».

Для аппаратных ОУ более удобным является способ, когда адрес назначается ОУ принудительно по инициативе одного из других, процессорных ОУ.

Для этого процессорное ОУ с адресом AdrSRC должно выдать на ОУ, которому требуется задать адрес AdrDST, сообщение, представленное на фиг.17.

ОУ, получившее сообщение указанного вида, в котором код протокола PID равен 0×FF, а адрес получателя DST=AdrDST отличен от 0×FF, должно зафиксировать AdrDST в качестве своего адреса и послать ответное сообщение, представленное на фиг.18.

Входной LINK-порт 11 предназначен для побайтного асинхронного приема слов данных в соответствии с временной диаграммой, представленной на фиг.12 и синхронной записи слова данных во входной буферный регистр 12. Во входном порту происходит переход от привязки входных сигналов LDAT_R 44 к асинхронной частоте LCLK_R 46 к синхронной привязке всех сигналов к частоте работы коммутатора LINK-портов CLK. Все остальные функциональные блоки коммутатора LINK-портов, за исключением входных LINK-портов, работают синхронно на частоте CLK.

После приема полного слова во входной порт 11 и при отсутствии сигналов Full (признак заполнения FIFO) и Stop (сигнал 51 приостановки приема данных от контроллера 2) вырабатывается сигнал записи WrD полученного слова во входной буферный регистр, после чего входной порт готов к приему следующего слова.

При наличии любого из сигналов Full или Stop выдача сигнала WrD откладывается до их снятия, а прием следующего слова во входной порт запрещается снятием сигнала подтверждения приема LACK_R 47. Для контроля состояния источника информации входной порт 11 вырабатывает сигнал разрешения отсчета тайм-аута RTOI. Этот сигнал вырабатывается при наличии сигнала подтверждения приема LACK_R 47 и отсутствии частоты LCLK_R 46 от источника.

Счетчик тайм-аута приема 13 предназначен для обработки ошибочных ситуаций, возникающих в источнике информации. Так как предполагается, что при передаче сообщений используется аппаратный механизм доступа в память, и, раз начавшись, сообщение должно передаваться без пауз, даже с учетом его прохождения через коммутаторы LINK-портов, то под ошибочной ситуацией понимается пауза в передаче сообщения, обусловленная передатчиком, большая чем Ti=12.8 мкс.

Пауза в передаче сообщения, обусловленная приемником сообщения, то есть пауза, возникшая из-за снятия сигнала LACK_R 47, не засчитывается при отсчете тайм-аута.

Счетчик тайм-аута приема 13 отсчитывает длительность поступающего на него сигнала RTOI и при превышении величины Ti, вырабатывает сигнал тайм-аута TOI (первый сигнал третьей группы выходов 52). Снятие сигнала RTOI приводит к сбросу счетчика тайм-аута 13 в исходное состояние.

Счетчик тайм-аута выдачи 17 предназначен для обработки ошибочных ситуаций, возникающих в приемнике информации.

Сигнал тайм-аута выходного порта ТОО (второй сигнал третьей группы выходов 52) возникает в случае, когда прерывается прием сообщения из выходного порта и длительность паузы больше чем запрограммированное значение в диапазоне от 400 мкс до 100 мс.

По сигналу начальной установки тайм-ауты отключены. Включение/выключение тайм-аутов входных и выходных портов осуществляется путем установки соответствующих битов в регистре RTO, адрес регистра RTO - 0×0000D:

- 1 бит - разрешение работы тайм-аута входных портов (EITO - enable input time-out). Управляет режимом работы одновременно всех входных портов.

- 0 бит - разрешение работы тайм-аута выходных портов (ЕОТО - enable output time-out). Управляет режимом работы одновременно всех выходных портов.

Разрешение тайм-аута - установка «1» в соответствующем бите.

Регистр RTO полностью доступен и по записи и по чтению.

Тайм-аут входного порта возникает при следующих условиях:

- в регистре RTO бит EITO = «1»;

- началась передача сообщения во входной порт;

- LACK 47 входного порта равен «1»;

- LCLK 46 входного порта равен «0» в течение 12,8 мкс.

При возникновении тайм-аута входного порта осуществляются следующие действия:

- очищается входной буфер соответствующего входного порта;

- логическая схема соответствующего входного порта устанавливается в состояние готовности к приему следующего сообщения.

Тайм-аут выходного порта возникает при следующих условиях:

- в регистре RTO бит ЕОТО = «1»;

- началась работа выходного порта;

- LCLK 49 выходного порта выдается «1»;

- LACK 48 выходного порта равен «0» в течение 400 мкс - 100 мс.

При возникновении тайм-аута выходного порта осуществляются следующие действия:

- происходит считывание сообщения из входного и игнорирование считанной части сообщения;

- если началась выдача слова из выходного порта, и возник тайм-аут, то сигнал LCLK 49 равен «1» и на шине данных LDAT 45 стоит старший байт слова до тех пор, пока не будет LACK 48 равен «1». Как только LACK 48 становиться равным «1» формируется спадающий фронт частоты LCLK 49 и выдается часть сообщения, которая успела записаться в выходной порт (8 байт), причем последние 4 байта равны 0×FF;

- если сигнал LACK 48 равен «0» с начала работы выходного порта, то после установки сигнала LACK 48 в «1» формируется спадающий фронт частоты LCLK 49 и выдаются 8 байт сообщения, которые успели записаться в выходной порт, причем последние 4 байта равны 0×FF.

Длительность времени по истечении которого сработает выходной тайм-аут 17 является программируемым. Диапазон времени составляет: 400 мкс - 100 мс.

Программирование длительности паузы для выходных портов осуществляется путем установки соответствующих битов в регистре RPRTO, адрес регистра RPRTO - 0×00001. Таким образом, можно задать 256 различных длительностей паузы с шагом 400 мкс. При нулевом значении регистра RPRTO длительность паузы составляет 400 мкс.

Регистр RPRTO полностью доступен и по записи и по чтению. Максимальная погрешность при срабатывании тайм-аута порядка 6,6 мкс.

Входной буферный регистр 12 предназначен для временного хранения принятых слов данных, их анализа УМС24 и дальнейшей записи в буферную память FIFO 23.

Выходной LINK-порт 15 предназначен для побайтовой асинхронной передачи слов данных в соответствии с временной диаграммой, представленной на фиг.12.

В исходном состоянии, при отсутствии запросов на обслуживание от входных портов Rq_T (восьмой сигнал третьей 58 группы входов LINK-порта 1) и, соответственно, запроса на выдачу ответного сообщения Rq_R (восьмой сигнал второй 55 группы выходов контроллера LINK-порта 2) счетчик выбора входного порта 16 циклически опрашивает входные порты путем перебора от 0 до N.

По запросу от входного порта Rq_T (восьмой сигнал третьей группы входов 58) с номером NPT_R запрашиваемого выходного порта (с первого по шестой сигналы третьей группы входов 58) счетчик выбора входного порта 16 увеличивается на единицу, а номер NPR_T сравнивается на схеме сравнения 18 с константой 19 (номер порта от 0 до N) и в случае сравнения формируется сигнал, блокирующий работу счетчика выбора входного порта 16 и на четвертую 57 группу выходов подается номер опрашиваемого входного порта NPR_T (с 1 по 6 сигналы). Этот же номер используется, при необходимости ответа, в качестве номера запрашиваемого выходного порта NPT_R (первый-шестой сигналы третьей 58 группы входов LINK-порта 1). Это означает, что коммутатор LINK-портов все ответные сообщения выдает на тот же LINK-интерфейс, от которого было получено сообщение - запрос. При этом в случаях, когда требуется выдача ответного сообщения от коммутатора LINK-портов, счетчик выбора входного порта 16 не будет изменяться до тех пор, пока ответное сообщение не будет полностью выдано (с учетом возможности отработки тайм-аута 17 выходным портом).

Выходной буферный регистр 14 предназначен для хранения передаваемых данных. Алгоритм работы контроллера порта 2 представлен на фиг.19, 19а, 196, 19в, 19г, 19д, 19е.

Информационные слова при прохождении через коммутатор LINK-портов не изменяются за единственным исключением - при прохождении через коммутатор LINK-портов уменьшается на единицу значение поля TL в заголовке сообщения.

Для изменения этого поля и предназначен узел модификации TL 20, который при поступлении управляющего сигнала Sub (десятый выход УМС24) производит вычитание 1 из поля TL, находящегося в разрядах Dl[27:24] принятого слова данных. Содержимое других разрядов информационного слова не изменяется. Следует отметить, что если в принятом слове поле TL нулевое, то результат вычитания не имеет значения, так как сообщение будет игнорировано и модифицированное слово не будет записано в FIFO 23.

Буферная память FIFO 23 предназначена для временного хранения заголовка сообщения до окончания его проверки на достоверность и допустимость. Емкость FIFO должна быть не меньше, чем максимальный размер заголовка, то есть 64 слова.

Запись в FIFO 23 осуществляется по сигналу WrF (одиннадцатый выход УМС24). Чтение осуществляется по сигналу RdF_R (первый вход 54 контроллера порта 2), поступающему через КМ 3 от выходного LINK-порта 1. Очистка FIFO 23 производится по сигналу CIF (четырнадцатый выход УМС24), который вырабатывается УМС24 при необходимости игнорировать уже принятую часть заголовка.

Управляющая машина состояний УМС24 предназначена для выделения и анализа заголовков сообщения во входном потоке данных, выдачи управляющих воздействий на узлы контроллера на основе анализа заголовка и других управляющих признаков.

Функциональная схема счетчика слов и аккумулятора контрольной суммы 40 представлена на фиг.7.

Сигнал сброса CLA (девятый выход УМС24) устанавливает аккумулятор контрольной суммы 93 и счетчик слов 94 в исходное, нулевое состояние.

Сигнал ENT (первый вход) прибавляет 1 к содержимому счетчик слов 94.

Сигнал WrF (второй сигнал) одновременно с записью слова в FIFO разрешает запись в аккумулятор 92, 93 новой контрольной суммы, получаемой сложением по модулю 2 текущего содержимого аккумулятора и входных данных DI.

Сигнал CRC ОК (первый выход) формируется, если полученная контрольная сумма нулевая.

Выходы со счетчика слов 94 (первая группа выходов) поступают на УМС24 для сравнения количества слов с длиной HL заголовка.

Регистры первого слова заголовка 41 RGH1 и третьего слова заголовка 42 RGH3 предназначены для хранения признаков и полей, которые содержатся в первом и третьем словах заголовка. Запись первого слова заголовка осуществляется в регистр RGH1 41 по сигналу WrRG1 (двенадцатый выход УМС24). Из первого слова используются поле признаков RQ, поля TL и DST. Третье слово заголовка записывается в регистр RGH3 42 по сигналу WrRG3 (тринадцатый выход УМС24). Из него используются признаки В, D и поля HL и BL.

Таблица коммутации, состоящая из ОЗУ1 таблицы коммутации 26 и ОЗУ2 30, предназначена для хранения следующей информации для каждого из 256 абонентов системы, идентифицируемых адресом назначения DST:

а) номер выходного порта NPT_R на который нужно выдавать сообщения для абонента с адресом DST. Количество разрядов в данном поле должно быть достаточным для адресации выходных портов от 0 до N.

Для коммутатора с количеством внешних портов до 32 требуется 5 разрядов для задания номера выходного порта.

Принимается, что номер выходного порта, содержащий все «1», используется для обращения к встроенному ОУ управления коммутатором, а номера выходных портов от 0 до N используются для адресации внешних портов.

б) признак удаления заголовка Del для данного адреса DST формируется на элементе И 35.

в) признак NPOk наличия (достоверности) записи для данного адреса DST формируется на элементе ИЛИ 39.

Для хранения информации в составе таблицы коммутации имеется ОЗУ емкостью 256 байт. Количество ячеек ОЗУ соответствует количеству допустимых адресов абонентов DST. В составе байта по одному разряду отведено на хранение признака четности Par и на хранение признака удаления заголовка. На хранение номера выходного порта 5 разрядов, что должно быть достаточным для построения коммутаторов до 32 портов.

Признак четности Par должен дополнять количество «1» в байте до нечетного, в этом случае данный байт ОЗУ считается достоверным.

В исходном состоянии содержимое ОЗУ должно быть нулевым и, таким образом, ОЗУ не должно содержать достоверных записей. Записи в ОЗУ должны вноситься через интерфейс с оконечным устройством управления коммутатором (ОУК).

При занесении записи в ОЗУ признак Par должен соответствующим образом формироваться. При стирании ОЗУ содержимое байта должно обнуляться.

Алгоритм работы оконечного устройства управления коммутатором представлен на фиг.20, 20а, 206, 20в, 20г, 20д, 20е.

В начальный момент времени после включения питания ОЗУ не содержит записей, при этом необходимо обеспечить коммутацию сообщений, предназначенных для ОУК.

Для этого таблица коммутации содержит схемы проверки адреса сообщений DST на предмет их назначения для ОУК.

Сообщения, направленные ОУК, имеют DST, в котором все разряды равны «1» (элементы И 32, И 33, ИЛИ 37, И 34), или старшие разряды соответствуют аппаратно заданному адресу коммутатора АК (пятая группа входов 82, схема сравнения 28, элемент ИЛИ 37), а младшие разряды равны «1» (элементы И 32, И 34).

Схема сравнения в итоге формирует признак обращения к ОУК, по которому в обход ОЗУ формируется номер выходного порта, все разряды которого содержат «1», формируется признак достоверности NPOk (элемент ИЛИ 39, первый вход УМС) и блокируется формирование признака удаления заголовка Del (тринадцатый вход УМС).

Счетчик номера LINK-портов 9 обеспечивает обслуживание запросов к ОУК. В исходном состоянии, при отсутствии запросов на обслуживание к ОУК от входных портов Rq_T (первый сигнал пятой группы выходов 63), и, соответственно, запроса на выдачу ответного сообщения Rq_R (первый сигнал шестой группы входов 65), счетчик циклически опрашивает входные порты путем перебора их номера от 0 до N. При обнаружении запроса от входного порта Rq_T счет останавливается, и на выходе счетчика фиксируется номер обслуживаемого входного порта NPR_T (группа входов 64). Этот же номер используется, при необходимости ответа, в качестве номера запрашиваемого выходного порта NPT_R (шестая группа выходов 77) коммутационной матрицы 3. Это означает, что коммутатор LINK-портов все ответные сообщения выдает на тот же LINK-интерфейс, от которого было получено сообщение - запрос. При этом в случаях, когда требуется выдача ответного сообщения от коммутатора LINK-портов, счетчик номера порта 9 не будет изменяться до тех пор, пока ответное сообщение не будет полностью выдано из ОУК (с учетом возможности обработки тайм-аута выходным портом).

Блок регистров 4 предназначен для хранения первых четырех слов, поступающих в ОУК в составе сообщения. Данные слова поступают в ОУК из входных портов, где они проходят проверку на достоверность, формирую сигнал 73, разрешающий работу дешифратору протокола выдачи адреса 5 и формирователю 10 протокола RCP-2. Информация из блоков регистров 4 используется формирователем ответного сообщения 6.

Для обеспечения возможности получения адреса от коммутатора LINK-портов имеется зарезервированный адрес получателя DST=0×FF и зарезервированный код протокола PID=0×FF.

При поступлении сообщения адресом назначения DST=0×FF коммутатор LINK-портов должен считать, что сообщение адресовано ему, и должен выдать ответное сообщение на интерфейс, по которому поступило сообщение.

В ответном сообщении коммутатор LINK-портов должен выдать служебную информацию, содержащую адрес коммутатора, номер интерфейса, по которому выдано ответное сообщение и другую служебную информацию.

Информация по адресу 0×FF доступна только по чтению. Для записи управляющей информации в коммутатор LINK-портов, должен использоваться его собственный адрес (адрес входящего в коммутатор LINK-портов ОУК).

Для получения адреса от коммутатора LINK-портов ОУК должно выдать на него сообщение, представленное на фиг.17.

Если поля PID и PIS содержат 0×FF, то дешифратор протокола выдачи адреса 5 распознает номер протокола как протокол предоставления адреса и начинает его обработку.

Дополнительно анализируя поле DST, которое должно быть равно 0×FF и поле RQ, которое должно быть равно 0×1.

При выполнении всех перечисленных условий дешифратор протокола выдачи адреса 5 формирует сигнал 61 на выдачу ответного сообщения, которое имеет формат, представленный на фиг.18.

Формирователь ответного сообщения 6 запускается по сигналам 61 и 76 от дешифратора протокола выдачи адреса 5 и формирователя 10 протокола RCP-2. Формирователь отвечает за правильность формата выдаваемого ответного сообщения. При формировании сообщения используется информация, хранимая в блоке регистров 4, а также поступающая от обработчиков 5 и 10 соответствующих протоколов. Слово с контрольной суммой генерируется на аккумуляторе KΣ 89 самим формирователем ответного сообщения 6.

Для обмена с коммутационной матрицей 3 используется тот же набор сигналов 62, 65, 66, что и для входного порта, который формируется на буферном регистре 90 и ОЗУ 91.

Формирователь протокола RCP-2 предназначен для обращения к таблицам коммутации и записи (чтения) в (из) управляющие(х) регистры(ов) оконечных устройств в коммуникационных системах на основе LINK-интерфейсов. Условное обозначение протокола RCP-2. Код протокола PID=0×02.

Обмен информацией с оконечным устройством осуществляется в соответствии с командами, содержащимися во входном сообщении, поступающем на ОУ от инициатора обмена.

Для обмена информацией в соответствии с протоколом RCP-2 используются сообщения, содержащие только заголовок, защищенный контрольной суммой. Сообщение поступившее на ОУ должно быть в нем полностью буферизовано, проверено на достоверность, после чего ОУ может приступить к исполнению команд, содержащихся в сообщении. Недостоверные сообщения, а также сообщения, формат которых не соответствует данному протоколу, игнорируются.

Для совершения обмена с ОУ коммутатора от инициатора обмена на ОУ должно быть подано сообщение, имеющее формат, представленный на фиг.21.

Разряд Q должен содержать «1» если в ответ на входное сообщение ОУ должно выдать ответное сообщение. Для того чтобы инициатор обмена мог установить соответствие между исходным сообщением и ответным сообщением используется идентификатор обмена IDM. IDM размещается в поле BL/Parameter заголовка. Так как тело в сообщении отсутствует (В=0), то используется возможность данного поля в качестве параметра, в данном случае параметром является IDM.

Отслеживать уникальность параметра IDM, обеспечивающую возможность установления однозначности связи между исходным и ответным сообщением является задачей инициатора сообщения.

Команды в CMD имеют два формата, представленные на фиг.22, различаемые по значению старшего, 31-ого разряда.

Параметр заголовка предназначен для идентификации последующих команд обмена. Параметр заголовка без изменения переписывается из входного сообщения в ответное.

Команды обмена предназначены для записи, модификации содержимого регистров и ячеек памяти и чтения их содержимого. Если в одной команде заданы одновременно команды записи/модификации и чтения, то сначала производится запись/модификация, а затем чтение регистра/ячейки памяти.

Команда обмена имеет следующие поля:

Address - начальный физический адрес массива регистров или ячеек памяти ОУ с точностью до байта. При выполнении команд обмена поле Address переписывается в счетчик адреса 98 узла управления 85, реализованный в ОУ.

Для каждого ОУ должна быть определена размерность регистров или ячеек памяти. Размерность может быть равна байту, 16-разрядному слову или 32-х разрядному слову. Если в команде задается обращение к 16-разрядному регистру или ячейке памяти, то младший 0-й разряд адреса должен содержать «0». При обращении к 32-х разрядному регистру или ячейке памяти два младших разряда адреса должны содержать «0». При нарушении этого правила обмен с регистром или ячейкой памяти не совершается и фиксируется ошибка обмена.

После успешного завершения единичной операции обмена с регистром или ячейкой памяти счетчик адреса инкрементируется на 1, 2 или 4 в зависимости от размерности регистров ОУ.

Команда выполняется до тех пор, пока не будет передано количество данных, заданное полем Size, или не будет зафиксирована ошибка обмена.

Size - количество байт во входном массиве данной команды записи или количество байт в ответном массиве для чтения. Также как поле Address, поле Size должно быть кратно размерности регистров или ячеек памяти ОУ, иначе фиксируется ошибка обмена (error_size).

W - тип операции записи/модификации, представленный на фиг.23.

R - «1» в данном разряде означает задание операции чтения массива регистров/ячеек памяти в выходной массив, «0» в данном разряде означает отсутствие операции чтения и выходного массива данных. Данный признак действует только при установленном признаке Q в заголовке входного сообщения.

При одновременном задании операции записи/модификации и чтения сначала осуществляется операция записи/модификации регистра из входного массива, затем чтение регистра в выходной массив, затем осуществляется переход к следующему регистру или ячейке памяти.

Входной массив данных поступает во входном сообщении вслед за командой CMD при отличном от нулевого содержимом поля W.

Размер входного массива N в словах определяется совместно полями Size и Address.

В случае, если поле Size равно нулю, требуется выдать ответное слово RPL без записи либо чтения регистров, входные и выходные массивы при этом отсутствуют. При установленном разряде Q во входном сообщении ОУК формирует ответное сообщение, формат которого представлен на фиг.24. Ответные слова, также как и командные, имеют два формата, различаемые по назначению старшего, 31-ого разряда. Формат ответного слова представлен на фиг.25. Параметр заголовка переносится без изменений из соответствующей команды.

Поля результата обмена имеют следующие значения:

AddressR - содержимое счетчика адреса ОУ после завершения обмена. Если обмен информацией был завершен без ошибок, то AddressR = Address + Size.

SizeR - количество байтов записанных и/или считанных из ОУ. Если обмен информацией завершен без ошибок, то SizeR = Size. В любом случае AddressR = Address + SizeR.

Er - поле кода ошибки, представлено на фиг.26.

R - признак чтения массива, соответствует признаку из командного слова. «1» в данном признаке означает наличие выходного информационного массива (при SizeR≠0).

Преобразователь 83 данных предназначен для преобразования тридцати двух разрядных слов в восьми разрядные. Узел выполнения команд 84 предназначен для выполнения команд модификации. По выходному сигналу «признак записи модифицированных данных» из узла управления 85 узел выполнения команд 84 принимает восьмиразрядные данные 70 из ТК (регистров), предназначенные для модификации и восьми разрядные данные из преобразователя данных 83 для управления модификацией. По нулевому разряду кода операции W (1:0) узел выполняет либо сброс в «0» битов данных 70 из ТК (регистров), отмеченных «0» во входном массиве модификации (при W(0)=«0»), либо установку в «1» битов данных 70 из ТК, отмеченных «1» во входном массиве модификации (при W(0)=«1»).

Формирователь ответного массива 87 с помощью двух младших разрядов поля Address, по признаку 76 «формирования выходного массива» заполняет считанными данными 70 из ТК тридцати двух разрядный регистр. Сброс этого регистра производится после записи сформированного 32-разрядного слова в ответное сообщение.

Счетчик тайм-аута 86 при превышении времени ожидания сигнала «разрешения на доступ (HLDA) к ТК» (первый сигнал второй 75 группы входов) или времени ожидания сигнала «готовности к завершению операции» (RPLY) (второй сигнал второй 75 группы входов), которое составляет 12,8 мкс, формирует сигнал «тайм-аута».

После приема заголовка и команды блок регистров 4 производит проверку номера протокола и, если PID=0×02, то формирует сигнал «признак гср2», в команде производит проверку формата адреса на наличие «1» в 19 разряде и «0» в 18р…13р и формирует сигнал «достоверности адреса» 73, которые поступают на узел управления 85.

Функциональная схема узла управления представлена на фиг.8. Узел управления 85 состоит из регистра 96, на котором хранится команда, машины состояний 97, формирующей управляющей управляющие сигналы, счетчика адреса 98 ячеек ОЗУ и счетчика обмена 99, формирующего сигнал «завершение обмена» 81.

Операции протокола RCP-2 выполняются в следующем порядке:

1) узел управления 85 устанавливает адрес ТК 69 (Address) (регистра) и сигнал требования на доступ к ТК (регистрам) (HOLD) (первый сигнал третьей 74 группы выходов);

2) ТК (регистр) дешифрирует адрес и при возможности обращения к ТК (регистру) устанавливает сигнал разрешения на доступ (HLDA) первый сигнал второй 75 группы входов) и сигнал достоверности адреса (DA73);

3) формирователь 10 протокола RCP-2 при получении сигнала разрешения на доступ (первый сигнал второй 75 группы входов), анализирует сигнал достоверности адреса 73 и устанавливает сигнал чтения (RD) (третий сигнал третьей 74 группы выходов) или сигнал записи (WR) (второй сигнал третьей 74 группы выходов) и данные для записи 70 (Dout) (при записи);

4) ТК (регистр) начинает выполнять запрашиваемую операцию чтения или записи и при готовности к завершению операции выставляет сигнал готовности к завершению операции (RPLY) (второй сигнал второй 75 группы входов) и данные для чтения 70 (при чтении) (Din);

5) формирователь 10 протокола RCP-2 при выполнении операции из 1 действия при получении сигнала готовности к завершению операции снимает сигнал требования на доступ и сигнал чтения или сигнал записи и фиксирует данные для чтения (при чтении);

6) формирователь 10 протокола RCP-2 при выполнении операции из двух и более действий при получении сигнала готовности к завершению операции снимает сигнал чтения или сигнал записи, фиксирует данные для чтения (при чтении), выполняет при необходимости модификацию данных и переходит к выполнению следующего действия. Временная диаграмма выполнения операции чтение-модификация-запись-чтение представлена на фиг.27. Формирование всех управляющих сигналов осуществляется с помощью машины состояний 97. Алгоритм работы машины состояний 97 узла управления 85 представлен на фиг.28.

Каждый этап - это определенное состояние машины. Всего таких состояний в данной машине семь. Это:

1) Ожидание - состояние идентификации команды;

2) Чтение/модификация - состояние чтения-модификации;

3) Запись - состояние записи;

4) Чтение - состояние чтения;

5) Окончание обработки данных - состояние окончания обработки данных;

6) Ошибка - состояние ошибочной обработки байта;

7) Стоп - состояние окончания текущей команды и ожидания следующей.

Работа машины состояний 97 основана на анализе входных управляющих сигналов. По сигналу начальной инициализации «сброс» машина состояний 97 устанавливается в состояние «стоп».

1) состояние «стоп» является не только начальным (когда машина состояний ожидает новую команду), но и состоянием, в которое она приходит при завершении обработки каждого байта входного/выходного массива. Если машина состояний в состоянии «стоп» находится в ожидании новой команды, то переход из состояния «стоп» к следующему состоянию «ожидание» осуществляется при появлении признака обращения к ТК (31р К=1). Иначе переход будет выполнен при отсутствии признака завершения обработки команды (завершение обработки (зав.об.) равно «0»). Если данные условия не выполняются, то следующему состоянию присваивается текущее значение.

2) в состоянии «ожидание» проверяется либо отсутствие достоверного адреса (DA=0) при уже имеющемся разрешении на доступ (HLDA=1), либо наличие признака тайм-аута обращения к ТК (Timeout =1). В этих случаях фиксируется ошибка и следующим состоянием становится «ошибка». В остальных случаях машина состояний 97 начинает идентификацию команды, анализируя поля W и R:

- при нулевом значении данных полей отсутствует любой тип записи/модификации данных в ТК и чтения в выходной массив, операция считается завершенной и машина переходит в состояние окончания обработки байта («ок.об.б.»).

- при значении R=1 и W=00 происходит переход к чтению массива ячеек ТК в выходной массив.

- при наличии признака записи входного массива W=01 следующим состоянием становиться состояние записи (поле R здесь не анализируется).

- при наличии признака модификации входного массива W=10 или W=11 следующим состоянием становится состояние чтение-модификация (поле R здесь не анализируется).

При любых других значениях полей W и R машина состояний 97 возвращается в состояние ожидания команды.

3) состояние «чтение» - это состояние чтения массива ячеек ТК в выходной массив. В данном состоянии анализируется признак тайм-аута обращения к ТК. При наличии этого признака следующим становится состояние «ошибка». Иначе, так как операция чтения в выходной массив осуществляется после операции записи/модификации при их одновременном задании, то машина состояний переходит в состояние «окончание обработки байта».

4) состояние «запись» - это состояние записи входного массива в ТК. Как и в состоянии «чтение» при наличии признака тайм-аута следующим становится состояние «ошибка», иначе машина состояний 97 переходит либо в состояние «окончание обработки байта», либо при значении R=1 происходит чтение в выходной массив.

5) состояние «чтение-модификация» - это состояние чтения массива ячеек ТК для последующей модификации его с помощью входного массива. Как и в предыдущих состояниях проводится проверка на тайм-аут и осуществляется переход к состоянию «запись».

6) из состояний «ошибка» и «окончание обработки байта» по умолчанию можно прейти только в состояние «стоп».

Смена состояний происходит синхронно по переднему фронту тактовой частоты CLK=100 Мгц.

Смена состояний «чтение-модификация», «запись», «чтение» происходит либо при наличии сигнала готовности к завершению операции RPLY (второй сигнал второй 75 группы входов), либо при обнаружении тайм-аута обращения к ТК.

Сигнал «требование на доступ» НОLD (первый сигнал второй 74 группы выходов узла управления 85) формируется при текущих состояниях «ожидание», «запись», «чтение», «чтение-модификация», на первом 100 элементе ИЛИ, сигнал чтения (rd - третий сигнал второй 74 группы выходов) формируется при текущих состояниях «чтение», «чтение-модификация» на втором 101 элементе ИЛИ.

Источники информации

1. Патент RU № 2257678, H04L 12/56, H04L 12/413, 2005 г.

2. Патент US 7408957 B2, H04J 3/24, H04L 12/28, 2008 г.

3. Электроника: Наука, Технология, Бизнес 1/2007 г.

| название | год | авторы | номер документа |

|---|---|---|---|

| ПАРАЛЛЕЛЬНАЯ ВЫЧИСЛИТЕЛЬНАЯ СИСТЕМА С ПРОГРАММИРУЕМОЙ АРХИТЕКТУРОЙ | 2012 |

|

RU2486581C1 |

| КОНТРОЛЛЕР | 1991 |

|

RU2012043C1 |

| СПУТНИКОВАЯ СИСТЕМА СВЯЗИ "КИБОЛ" | 1992 |

|

RU2033693C1 |

| Устройство для сопряжения ЭВМ с магистралью локальной сети | 1990 |

|

SU1839258A1 |

| Устройство для коммутации сообщений | 1984 |

|

SU1247879A1 |

| Распределенная система управления | 1989 |

|

SU1732345A1 |

| Устройство для управления обменом | 1983 |

|

SU1151976A1 |

| Устройство для контроля и диагностики логических узлов | 1980 |

|

SU960825A1 |

| Устройство микропроцессорной связи | 1981 |

|

SU934466A1 |

| Многоканальная система для контроля и диагностики цифровых блоков | 1984 |

|

SU1269137A1 |

Изобретение относится к построению коммутируемых локальных сетей для обмена данными между вычислительными модулями параллельных вычислительных систем или распределенных вычислительных комплексов. Техническим результатом изобретения является коммутация данных, представленных в виде байтов, обеспечение множественности путей доставки сообщений, исключение зацикливания сообщений, исключение блокировки сообщений. Коммутатор LINK-портов, содержит N LINK-портов, N контроллеров LINK-портов, коммутационную матрицу, блок регистров, дешифратор протокола выдачи адреса, формирователь ответного сообщения, схема сравнения, константа, счетчик номера LINK-портов, формирователь RCP-2, в каждый LINK-порт дополнительно введены входной LINK-порт, входной буферный регистр, входной LINK-порт, счетчик выбора входного порта, счетчик тайм-аута выдачи, схема сравнения, константа, в каждый контроллер LINK-порта дополнительно введены узел модификации поля TL, два JK-триггера, три элемента ИЛИ, буферная память FIFO, управляющая машина состояний, регистр состояния, ОЗУ1 таблицы коммутации, мультиплексор, схема сравнения, константа, ОЗУ2, пять элементов И, узел контроля на нечет, счетчик слов, аккумулятор контрольной суммы, регистр первого заголовка, регистр третьего слова заголовка, узел проверки слов заголовка. 6 з.п. ф-лы 28 ил.

1. Коммутатор LINK-портов, содержащий N LINK-портов, N контроллеров LINK-портов, коммутационную матрицу, блок регистров, отличающийся тем, что в коммутатор LINK-портов дополнительно введены дешифратор протокола выдачи адреса, формирователь ответного сообщения, схема сравнения, константа, счетчик номера LINK-портов, формирователь RCP-2, в каждый LINK-порт дополнительно введены входной LINK-порт, входной буферный регистр, счетчик тайм-аута приема, выходной LINK-порт, выходной буферный регистр, счетчик выбора входного порта, счетчик тайм-аута выдачи, схема сравнения, константа, в каждый контроллер LINK-порта дополнительно введены узел модификации поля TL, первый JK-триггер, первый элемент ИЛИ, буферная память FIFO, управляющая машина состояний, регистр состояния, ОЗУ1 таблицы коммутации, мультиплексор, схема сравнения, константа, ОЗУ2, первый элемент И, второй элемент И, третий элемент И, четвертый элемент И, пятый элемент И, узел контроля на нечет, второй элемент ИЛИ, третий элемент ИЛИ, счетчик слов и аккумулятор контрольной суммы, регистр первого слова заголовка, регистр третьего слова заголовка, узел проверки слов заголовка, второй JK-триггер, причем N первые группы входов коммутатора LINK-портов соединены с N первыми группами входов N LINK-портов, N первые группы выходов которых являются N группами выходов коммутатора LINK-портов, N первые входы которого соединены с N первыми входами N LINK-портов, N первые выходы которых являются N первыми выходами коммутатора LINK-портов, N вторые входы которого соединены с N вторыми входами N LINK-портов, N вторые выходы которых являются N вторыми выходами коммутатора LINK-портов, причем N вторые группы выходов N LINK-портов соединены с N группами входов N контроллеров LINK-портов, выходы которых соединены с третьими входами N LINK-портов, третья группа выходов которых соединена со вторыми группами входов N контроллеров LINK-портов, первые группы выходов которых соединены с N первыми группами входов коммутационной матрицы, N выходы которой соединены с первыми входами N контроллеров LINK-портов, вторые группы выходов которых соединены с N вторыми группами входов коммутационной матрицы, N первые группы выходов которой соединены со вторыми группами входов N LINK-портов, четвертые группы выходов которых соединены с N третьими группами входов коммутационной матрицы, N вторые группы выходов которой соединены с третьими группами входов N LINK-портов, причем четвертая группа выходов коммутационной матрицы соединена с группой входов блока регистров, первая группа выходов которого соединена с группой входов дешифратора протокола выдачи адреса, выход которого соединен с первым входом формирователя ответного сообщения, первая группа выходов которого соединена с четвертой группой входов коммутационной матрицы, пятая группа выходов которой соединена со второй группой входов блока регистров и первым входом счетчика номера LINK-портов, группа выходов которого соединена с пятой группой входов коммутационной матрицы, шестая группа входов которой соединена со вторым входом счетчика номера LINK-портов и второй группой выходов формирователя ответного сообщения, второй вход которого соединен с первым выходом коммутационной матрицы, первый вход которой соединен с первым выходом блока регистров, вторая группа выходов которого соединена с первыми группами входов формирователя ответного сообщения и формирователя протокола RCP-2, первая группа выходов которого соединена с третьими группами входов N контроллеров LINK-портов, группы входов-выходов которых соединены с группой входов-выходов формирователя протокола RCP-2, вторая группа выходов которого соединена со второй группой входов формирователя ответного сообщения, третий вход которого соединен с первым выходом блока регистров, второй выход которого соединен с дешифратором протокола выдачи адреса и с первым входом формирователя протокола RCP-2, третья группа выходов которого соединена с четвертыми группами входов N контроллеров LINK-портов, третьи группы выходов которых соединены со второй группой входов формирователя протокола RCP-2, первый выход которого соединен с четвертым входом формирователя ответного сообщения, причем шестая группа выходов коммутационной матрицы соединена с первой группой входов схемы сравнения, вторая группа входов которой соединена с константой, а выход - с третьим входом счетчика номера LINK-портов, причем третий выход блока регистров соединен со вторым входом формирователя протокола RCP-2, второй выход которого соединен со входом блока регистров, N вторые группы входов коммутатора LINK-портов соединены с пятыми группами входов N контроллеров LINK-портов.

2. Коммутатор LINK-портов по п.1, отличающийся тем, что каждый LINK-порт содержит входной LINK-порт, входной буферный регистр, счетчик тайм-аута приема, выходной буферный регистр, выходной LINK-порт, счетчик выбора входного порта, счетчик тайм-аута выдачи, схему сравнения, константу, группа выходов которой соединена с первой группой входов схемы сравнения, вторая группа входов которой соединена с первой группой входов выходного буферного регистра и является третьей группой входов LINK-порта, вторая группа входов которого соединена со второй группой входов выходного буферного регистра, группа выходов которого соединена с группой входов выходного LINK-порта, группа выходов которого является первой группой выходов LINK-порта, вторая группа выходов которого является выходами входного буферного регистра, группа входов которого соединена с группой выходов входного LINK-порта, группа входов которого является первой группой входов LINK-порта, первый вход которого является первым входом входного LINK-порта, первый выход которого соединен со входом входного буферного регистра, второй вход которого соединен с выходом счетчика тайм-аута приема и является первым сигналом третьей группы выходов LINK-порта, второй сигнал которой соединен с первым входом счетчика выбора входного порта и выходом счетчика тайм-аута выдачи, вход счетчика тайм-аута приема соединен со вторым выходом входного LINK-порта, третий выход которого является первым выходом LINK-порта, второй вход которого соединен со вторым входом входного LINK-порта, причем восьмой сигнал третьей группы входов LINK-порта соединен со вторым входом счетчика выбора входного порта, группа выходов которого является шестью сигналами четвертой группы выходов LINK-порта, седьмой сигнал которой соединен со входами счетчика тайм-аута выдачи и выходного буферного регистра и первым выходом выходного LINK-порта, второй выход которого является вторым выходом LINK-порта, третий вход которого соединен с первым входом выходного LINK-порта, причем выход схемы сравнения соединен с третьим входом счетчика выбора входного порта, выход выходного буферного регистра соединен со вторым входом выходного LINK-порта.