Перекрестная ссылка на родственные заявки

Настоящая заявка притязает на приоритет предварительной патентной заявки № 60/866240, озаглавленной "METHOD AND APPARATUS OF CONTENT ADDRESSABLE MEMORY (CAM) STRUCTURE WITH INTERLEAVED SET SCHEME", которая была подана 17 ноября 2006. Вышеупомянутая заявка полностью включена в данный документ посредством ссылки.

Область техники

Настоящее раскрытие относится, в целом, к архитектуре памяти и, более конкретно, к способам и системам для ассоциативной (адресуемой по содержимому) памяти (CAM).

Уровень техники

CAM могут включать в себя обычную полупроводниковую память (например, статическая оперативная память (SRAM)) и схему сравнения, которая позволяет быстро завершить операцию поиска (например, за один тактовый цикл). Эта возможность позволяет осуществить алгоритмы поиска с помощью аппаратных средств, которая обеспечивает большую скорость, чем поиски с помощью программного обеспечения. Для физической конструкции структуры массива CAM желательно иметь правильную форму, например прямоугольник, с целью уменьшения размера структуры массива CAM и эффективного использования пространства. Скорость и потребляемая мощность представляют собой проблемы в высокопроизводительных конструкциях, которые решаются посредством исключения ненужной паразитной емкости. Физическая компоновка, которая уменьшает критическую площадь и маршрутизацию, уменьшает и паразитную емкость. Однако некоторые особенности конструкций CAM делают проблематичным достижение максимальной эффективности их физической конструкции.

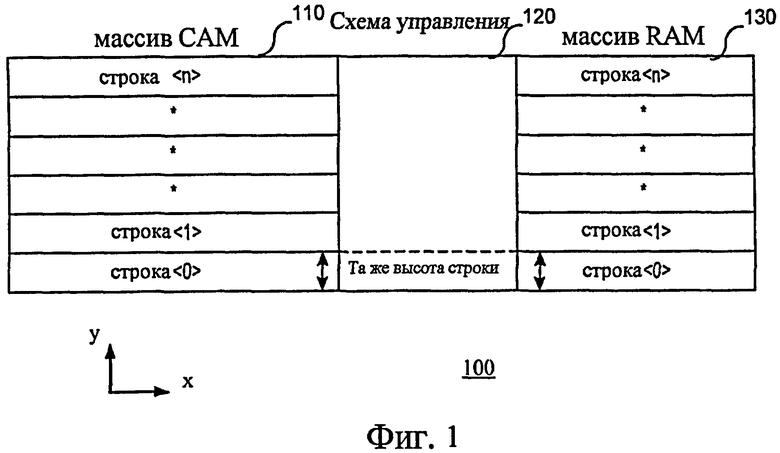

На Фиг.1 показана концептуальная блок-схема 100 кэша верхнего уровня массивов CAM 110 и RAM 130, имеющих строки <0>, <1>,... <n>. CAM 110 и RAM 130 разделены схемой управления 120. Как показано на Фиг.1, CAM массив 110 и RAM массив 130, каждый, имеет одно и то же число строк. Для создания эффективной конструкции желательно согласовать высоту строки массива 110 CAM с высотой строки массива 130 RAM, как показано на Фиг.1, так чтобы полная форма массива CAM была прямоугольной, если ее рассматривать в x-у плоскости (то есть контур массива RAM), тем самым делая эффективным использование площади. В данном раскрытии "высота строки" относится к расстоянию в направлении оси у, как показано, например, на Фиг.1.

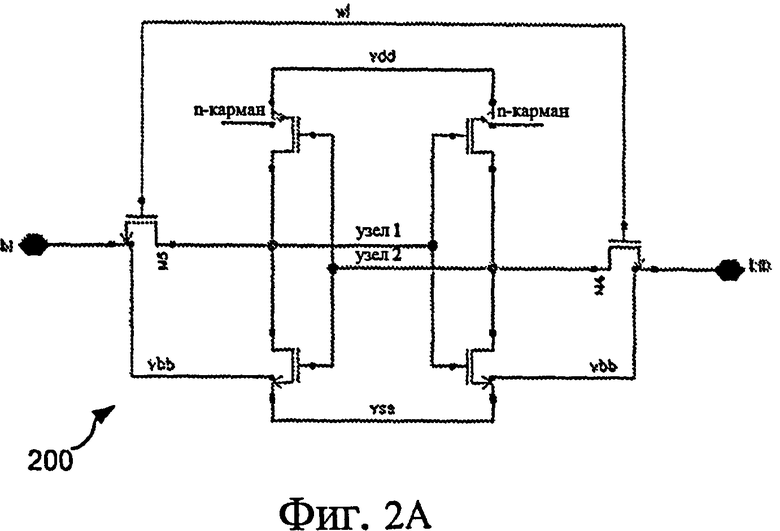

В конструкции статической оперативной памяти (SRAM) 6-T ячейка хранения часто определяет минимально возможную высоту строки в структуре массива. Для этой ячейки RAM обеспечивается специальное отклонение от технологической нормы литья таким образом, что технологии обработки можно довести до предела их возможностей для производства ячейки с минимальной площадью. На Фиг.2A показана принципиальная схема обычной ячейки 200 массива RAM, которая состоит из 6-T ячейки хранения. На Фиг.2B показана компоновка ячейки массива RAM. Обычно ячейка 201 RAM выполняется посредством литья. При конструировании значительные усилия предпринимаются для уменьшения физического размера ячейки RAM и тем самым получения эффективного использования области, используемой для ячейки, как показано на Фиг.1 и 2B. Кроме того, при конструировании массива 110 CAM площадь на стороне CAM (то есть массив 110 CAM на Фиг.1) должна также быть уменьшена, поскольку желательно получить взаимно-однозначное соответствие между высотой стороны массива 110 CAM и стороны массива 130 RAM.

Обращаясь снова к Фиг.1, массив 110 ассоциативной памяти (CAM) обычно включает в себя ячейку хранения, например 6-T ячейку 201 RAM, и схему сравнения для каждого бита в массиве. Для получения эффективной конструкции желательно, по меньшей мере, по существу согласовать высоту строки массива 110 CAM с высотой строки RAM массива 130 так, чтобы имело место полное взаимно-однозначное соответствие массива 110 CAM и массива 130 RAM.

Например, один вариант согласования высоты строки массива 110 CAM с высотой строки массива 130 RAM состоит в том, чтобы ограничить высоту ячеек CAM до высоты ячейки 201 RAM, которая присутствует здесь же. Соответственно, имеется взаимно-однозначное соответствие по высоте между высотой каждой строки массива 110 CAM и каждой строки массива 130 RAM, как показано на Фиг.1.

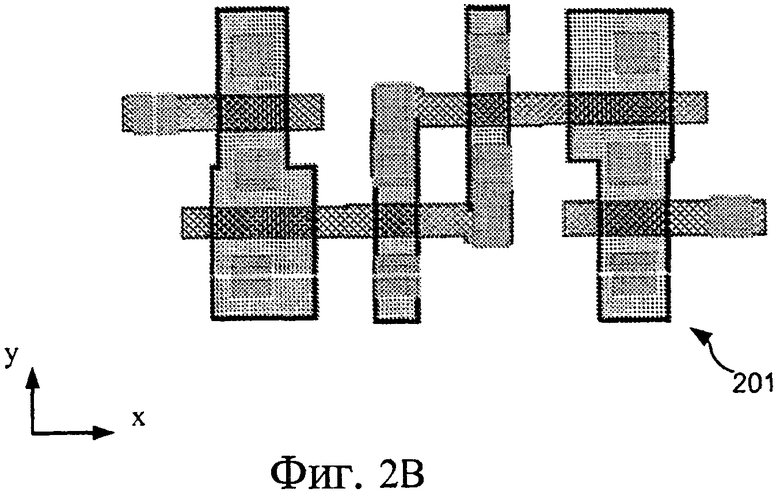

На Фиг.3 показан один обычный вариант осуществления конструкции кэша с согласованной высотой строк. В частности, на Фиг.3 показана компоновка 300 ячеек массива CAM с нерасслоенным набором, в которой высота стеков 310 и 320 сравнения совпадает по высоте с ячейкой хранения (то есть ячейкой 301 массива RAM). В обычных конструкциях для поддержания общей высоты узлы 315 и 316, которые могут быть соединены с согласующей линией, разделяют с той и другой стороны ячейки, что приводит к появлению дополнительной емкости.

На Фиг.3 ячейка хранения, то есть ячейка 301 массива RAM, скомпонована так, что два стека 310 сравнения (ложный/дополнительный) и 320 (истинный) находятся на каждой стороне ячейки 301 массива RAM. Высота строки каждого из стеков 310 и 320 сравнения сделана не большей, чем высота строки ячейки 301 массива RAM. Узлы 315 и 316 могут быть соединены посредством сети. В данном случае сеть - это провод, соединяющий два или несколько узлов (две или несколько точек). Когда строки располагаются в стек последовательно, как на Фиг.3, и линии сравнения выровнены по вертикали, к узлам 315 и 316 добавляется значительная емкость. Сети согласующих линий соединяются через каждый бит в пределах строки, но могут быть и уникальными от строки к строке, как показано на Фиг.4.

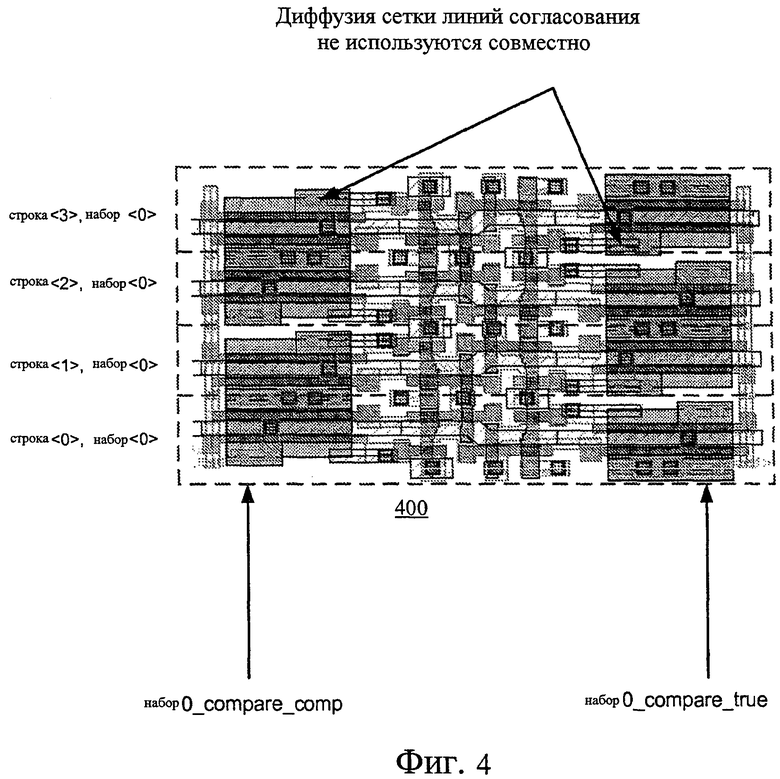

На Фиг.4 показана обычная конструкция 400 CAM, в которой строки в пределах массива размещены последовательно. Каждая ячейка массива CAM идентифицируется пунктирными линиями. На Фиг.4 линии сравнения выровнены по вертикали. Однако на Фиг.4 стеки транзисторов сравнения, каждый, имеют свою собственную линию согласования, что приводит к увеличенной емкости. Таким образом, на Фиг.4 согласующие линии не используют совместно диффузию.

Как описано выше, обычные конструкции массивов CAM, например, как показано на Фиг.3 и 4, приводят к увеличенной емкости, которая ухудшает работу массива памяти. Таким образом, существует потребность в конструкции массива CAM, которая делает эффективным использование пространства, уменьшает критическую площадь и упрощает маршрутизацию и снижает паразитную емкость.

Сущность изобретения

Примерные варианты реализации изобретения относятся к системам и способам для ассоциативной (адресуемой по содержимому) памяти (CAM).

Например, примерный вариант реализации относится к ассоциативной памяти (CAM), включающей в себя первую ячейку CAM, имеющую первую схему хранения, и первую схему сравнения, и вторую ячейку CAM, имеющую вторую схему хранения и вторую схему сравнения. Первая ячейка CAM и вторая ячейка CAM помещаются по существу в прямоугольную область. Первая и вторая схемы хранения расположены в стеке вертикально. Первая и вторая схемы сравнения, каждая, расположены на соответственных внешних краях прямоугольника.

Другой примерный вариант реализации относится к процессору, имеющему массив ассоциативной памяти (CAM), включающий в себя множество блоков ячеек CAM. Каждый блок ячеек CAM включает в себя первую ячейку CAM, имеющую первую схему хранения и первую схему сравнения, и вторую ячейку CAM, имеющую вторую схему хранения и вторую схему сравнения. Каждая ячейка CAM сконфигурирована как L-образная, и первая и вторая ячейки CAM размещены в конфигурацию со взаимозацеплением для формирования по существу прямоугольной формы.

Другой примерный вариант реализации относится к способу создания ассоциативной памяти (CAM), включающему в себя формирование L-образной первой ячейки CAM, имеющей первую схему хранения и первую схему сравнения, формирование L-образной второй ячейки CAM, имеющей вторую схему памяти и вторую схему сравнения, и размещение первых и вторых ячеек CAM в конфигурации со взаимозацеплением, чтобы сформировать по существу прямоугольную форму.

Краткое описание чертежей

Сопровождающие чертежи являются вспомогательными при описании вариантов реализации изобретения и предоставлены исключительно для иллюстрации вариантов реализации без их ограничений.

Фиг.1 изображает концептуальную блок-схему кэша верхнего уровня, иллюстрирующую массивы RAM и CAM.

Фиг.2A представляет собой принципиальную схему, иллюстрирующую ячейки массива RAM, и Фиг.2B представляет собой компоновку ячейки массива RAM.

Фиг.3 представляет собой иллюстрацию компоновки ячейки массива CAM с нерасслоенным набором.

Фиг.4 представляет собой иллюстрацию схемы конструкции CAM с нерасслоенным набором.

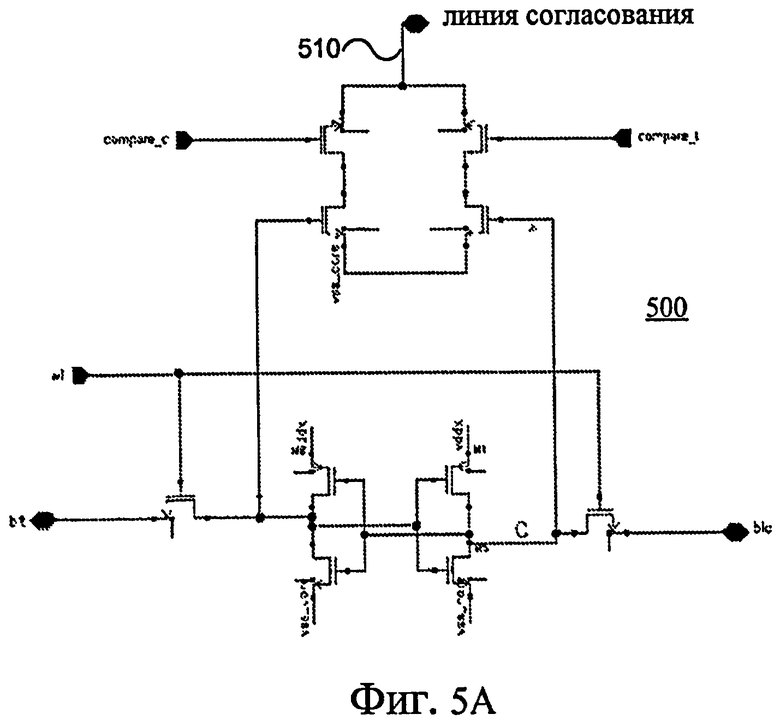

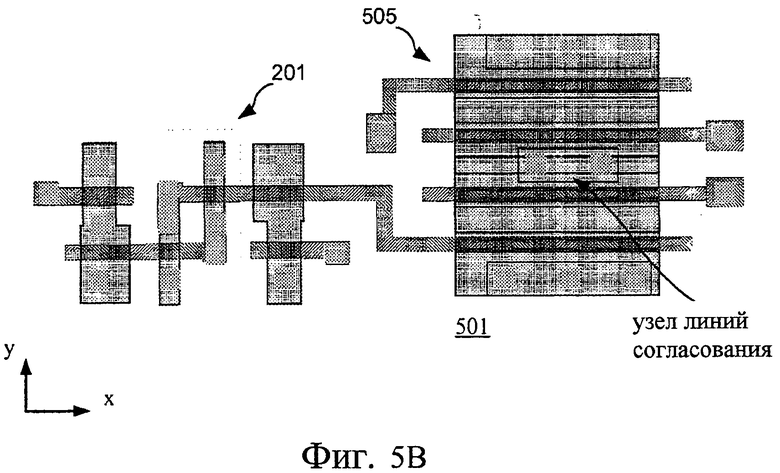

Фиг.5A представляет собой принципиальную схему, иллюстрирующую ячейку массива CAM, и Фиг.5B представляет собой компоновку ячеек массива CAM.

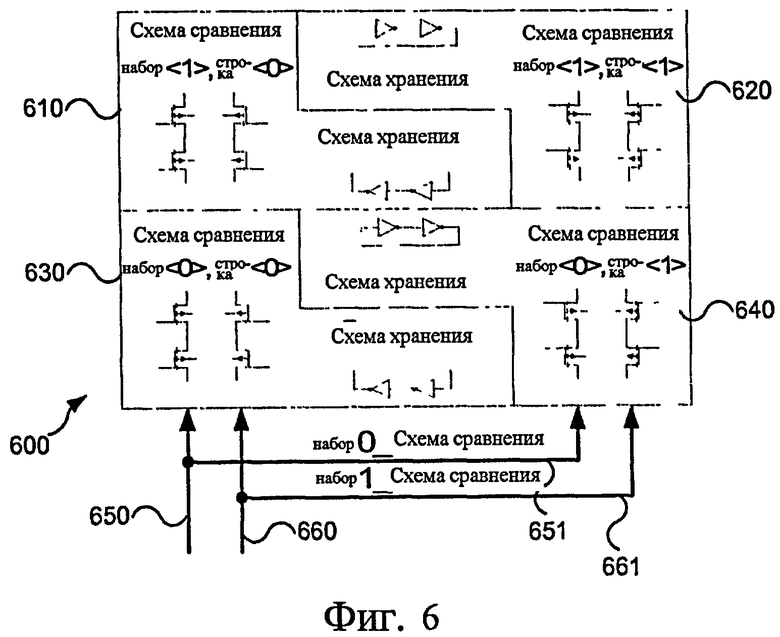

Фиг.6 представляет собой блок-схему, иллюстрирующую схему массива CAM с нерасслоенным набором.

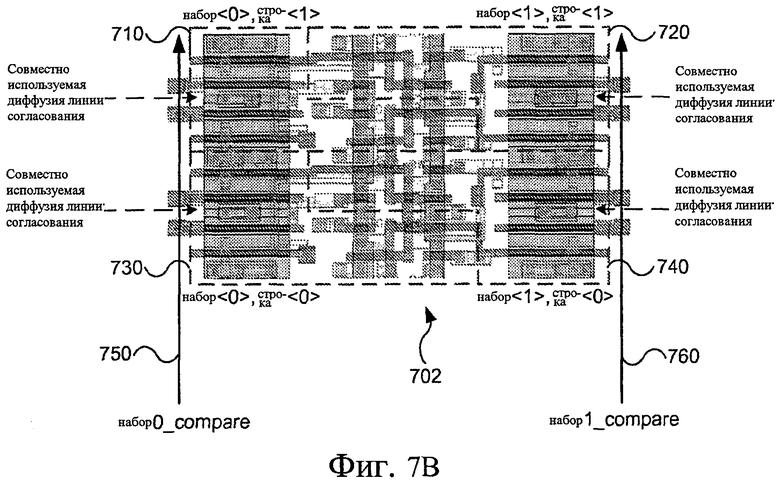

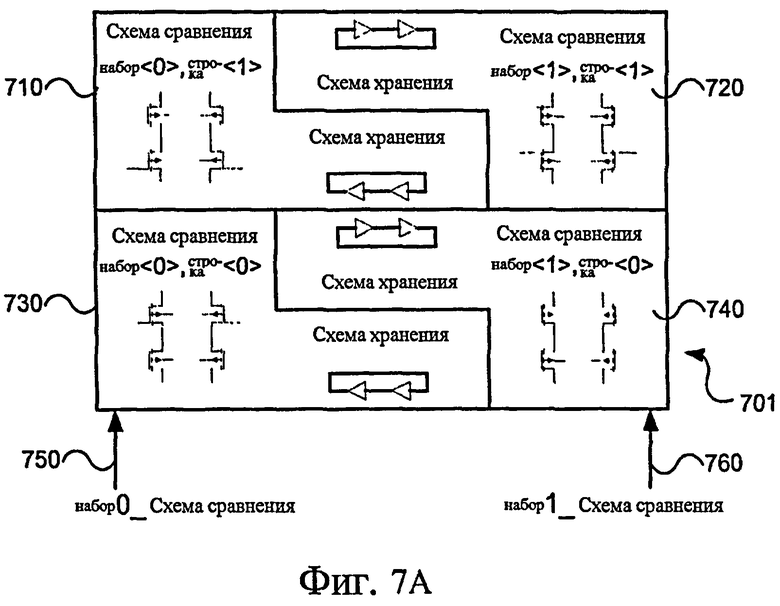

Фиг.7A представляет собой блок-схему, иллюстрирующую расслоенную структуру CAM, и Фиг.7B представляет собой компоновку набора <0>, набора <1>, расслоенной структуры CAM.

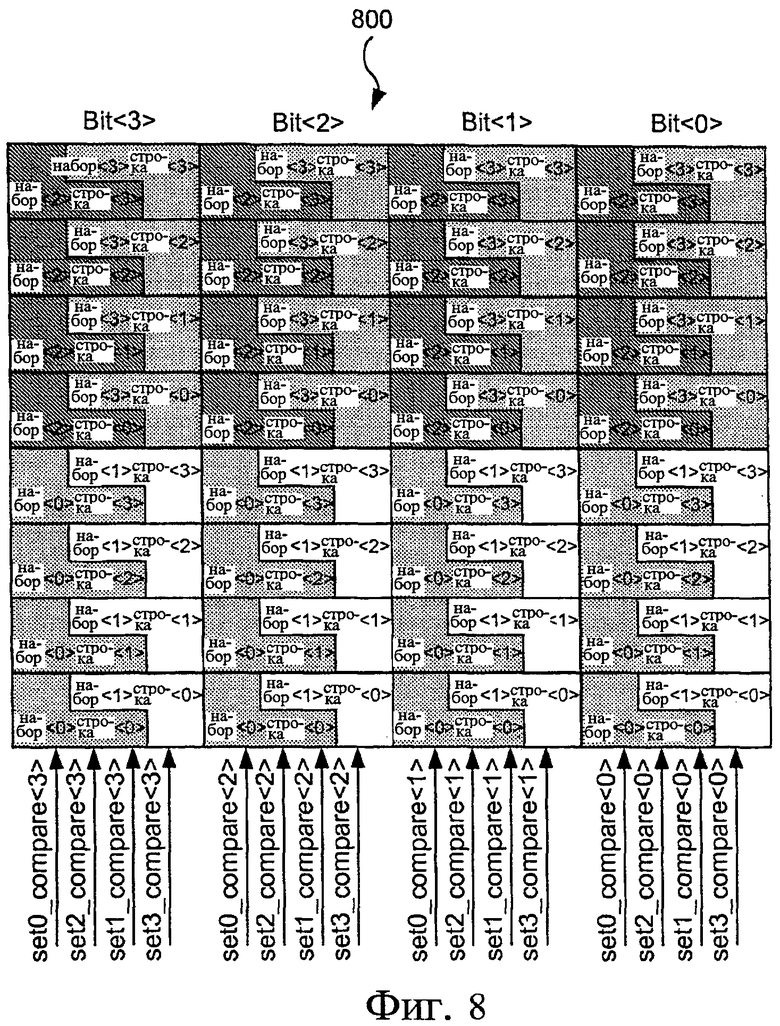

Фиг.8 представляет собой блок-схему, иллюстрирующую ассоциативный банк массивов CAM с расслоенным 4-х канальным набором.

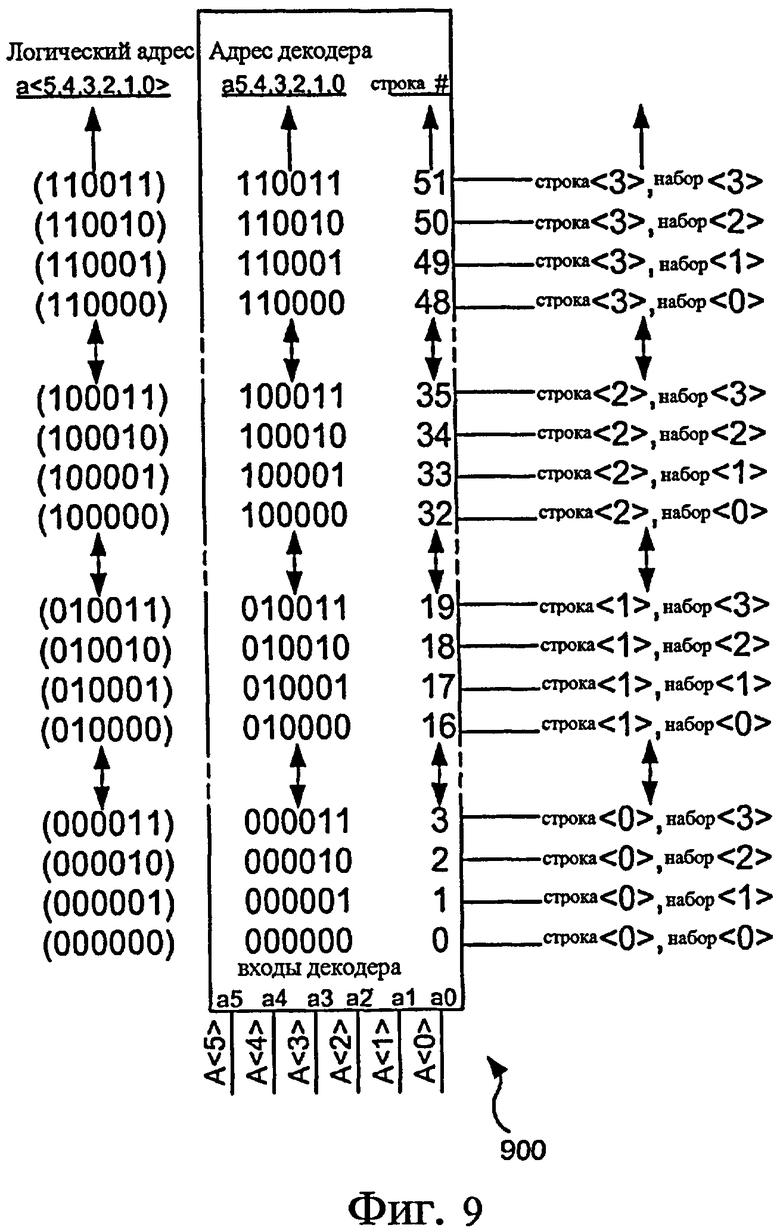

Фиг.9 представляет собой схему, иллюстрирующую декодер прямого отображения.

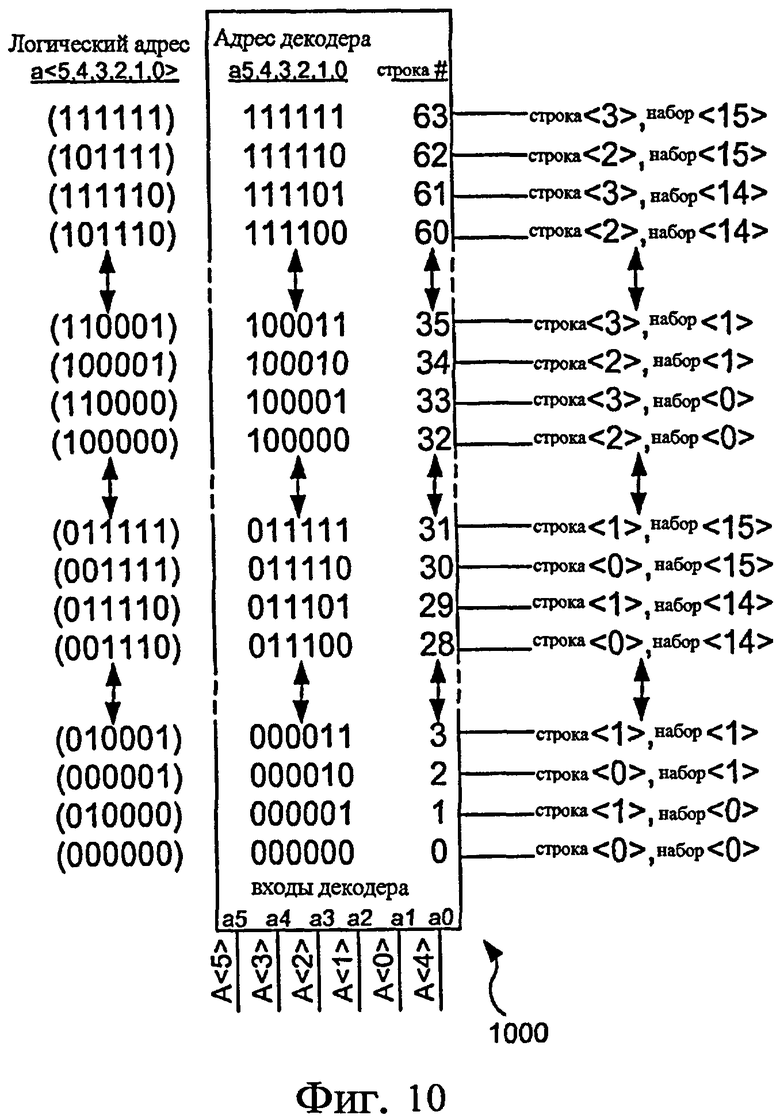

Фиг.10 - схема, иллюстрирующая декодер прямого отображения для кэша с расслоенным набором.

Подробное описание

Аспекты изобретения раскрываются в следующем описании и соответствующих чертежах, относящихся к конкретным вариантам реализации изобретения. Альтернативные варианты реализации могут быть разработаны без отступления от объема изобретения. Кроме того, хорошо известные элементы изобретения не описываются подробно или будут вовсе опущены, чтобы не затруднять понимание относящихся к изобретению подробностей.

Слово "примерный" означает в данном случае "служит в качестве примера, варианта или иллюстрации". Любой описанный в данном документе в качестве примера вариант реализации не обязательно должен рассматриваться как предпочтительный или преимущественный относительно других вариантов реализации. Аналогично, термин "варианты реализации изобретения" не требует, чтобы все варианты реализации изобретения включали в себя рассмотренный признак, преимущество или режим работы.

Варианты реализации изобретения относятся в общем случае к структурам ассоциативной памяти (CAM) и, более определенно, к способам и системам для предоставления ассоциативной памяти (CAM), имеющей множество ячеек CAM (например, первые и вторые ячейки CAM), размещенных для снижения используемой площади и упрощения маршрутизации, тем самым снижая паразитную емкость.

В одном варианте реализации совпадающие высоты строк CAM и RAM создаются посредством поворота чередующихся строк CAM на 180° относительно соседних строк CAM, как показано, например, на Фиг.5 и 6, которые подробно описываются ниже. Желательно избежать добавления усложненных требований маршрутизации и значительной емкости, которые ухудшают характеристики конструкции. Таким образом, будет описан другой примерный вариант реализации, который применяет схему расслоенного набора для предоставления уплотненной физической расстановки с согласованными высотами строк CAM и RAM. В соответствии с одной особенностью этого варианта реализации сетевая емкость снижается с помощью совместного использования диффузии при поддержании регулярной минимальной маршрутизации сигнала. Примерные варианты реализации уменьшают площадь, потребляемую мощность и увеличивают максимальную операционную скорость конструкции CAM. Другая особенность этого варианта реализации заключается в том, что не требуется новая схема декодирования. Декодер прямого отображения используется посредством переключения входного порядка адресной шины. Примеры особенностей этого варианта реализации будут описаны ниже в соответствии, например, с Фиг.7-10.

В одном варианте реализации массив CAM включает в себя 6-T ячейку 502 хранения, которая подобна 6T ячейке хранения, показанной на Фиг.2, и схему сравнения 505 для каждого бита в массиве, как показано на Фиг.5A. Относительно характеристики ячейки 500 массива CAM, узел, обозначенный как согласующая линия 510 на Фиг.5A, является одним узлом, который определяет эффективность поиска CAM. Поэтому желательно уменьшить емкость на узле 510 линии согласования. Соответственно, по меньшей мере, в одном варианте реализации диффузионная область транзистора, связанного со сравнением на дополнение/ложь (compare_c), совместно используется с диффузионной областью транзистора, связанного со сравнением на истину (compare_t) так, что емкость узла линии согласования снижается. Соответственно, посредством совместного использования диффузии и снижения емкости линии согласования варианты реализации могут снизить мощность и улучшить рабочие характеристики ячейки 500 массива CAM.

На Фиг.5B показана компоновка 501 ячейки массива CAM в соответствии, по меньшей мере, с одним вариантом реализации изобретения. Соответствующие обозначения, например узел 510 линии согласования, истина T, дополнение C, сравнение на истину (compare_t), сравнение на дополнение/ложь (compare_c) и Vss (vss_core), предоставлены для корреляции с принципиальной схемой на Фиг.5A. Как показано на Фиг.5B, компоновка ячейки 501 массива CAM предоставляет большее совместное использование диффузии посредством обеспечения смежной схемы сравнения 505, которая снижает емкость линии согласования посредством совместного использования общего узла 510 линии согласования и диффузионных областей смежных транзисторов, как рассмотрено в связи с Фиг.5A. Кроме того, варианты реализации предоставляют L-образную ячейку (как обозначено пунктирными линиями), которая имеет больший размер по оси у, чем обычная ячейка массива RAM. То есть высота в у-направлении стека 505 сравнения, как показано на Фиг.5B, больше, чем высота в у-направлении обычной ячейки матрицы RAM (см., например, Фиг.2B) или ячейки CAM (см., например, Фиг.3).

В соответствии с Фиг.6 вариант реализации изобретения может включать в себя массив CAM по схеме с расслоенным набором, размещенный в L-форме со взаимозацеплением, предусматривающую минимальную площадь, обеспечивая при этом уменьшенную емкость линии согласования для варианта реализации на Фиг.5B. На Фиг.6 показан массив 600 CAM, имеющий ячейки 610, 620, 630 и 640 массива CAM, причем каждая включает в себя схему сравнения и схему хранения (то есть ячейку RAM). Как упомянуто выше, компоновка ячейки массива CAM выполнена так, чтобы обеспечить L-образную ячейку, которая выше, чем обычные ячейки RAM, но все же предусматривает уменьшенную площадь массива 600 памяти. Соответственно, каждая смежная ячейка массива CAM повернута на 180° относительно ее соседней ячейки для формирования L-формы со взаимозацеплением, показанной на Фиг.6.

Например, ячейка 620 массива CAM повернута на 180° относительно ячейки 610 массива CAM, и ячейка 640 массива CAM повернута на 180° относительно ячейки 630 массива CAM. Каждая L-группа со взаимозацеплением предусматривает две ячейки хранения и две схемы сравнения. Примерный вариант реализации на Фиг.6 обеспечивает компактную конструкцию, в которой каждый блок смежных ячеек массива CAM (например, 610 и 620, 630 и 640 и т.д.) образует прямоугольную форму, имеющую высоту, которая по существу равна двойной высоте обычной ячейки массива RAM. Таким образом, конфигурация на Фиг.6 предоставляет конструкцию, которая имеет полное взаимно-однозначное соответствие ячейки RAM ячейке сравнения, обеспечивая при этом снижение емкости линии согласования.

В целях этого раскрытия расположение в стек повернутых строк последовательно в пределах набора означает, что входы сравнения каждой другой строки будут в отдельном вертикальном столбце. Дополнительный столбец входов приводит к двум дорожкам маршрутизации на сигнал сравнения (например, set_compare сигнал), как показано на Фиг.6. То есть если повернутые строки помещены последовательно в пределах набора, то будут две дорожки маршрутизации для каждого входа сравнения набора (например, set0_compare ввод 650 и 651 и setl_compare ввод 660 и 661); один для каждого вертикального столбца. Дополнительный столбец входов (например, 651 и 661) приводит к дополнительным требованиям к маршрутизации.

Для снижения требований к маршрутизации и ассоциированной паразитной емкости с дополнительными линиями может быть использована схема расслоенного набора в соответствии с вариантами реализации изобретения. Например, как показано на Фиг.7A, расслоенная конструкция также имеет полное взаимно-однозначное соответствие между высотами строк CAM и RAM, при снижении маршрутизации и паразитной емкости. Сетевая емкость снижается с помощью совместного использования диффузии при ограничении или поддержании маршрутизации сигнала (например, регулярная минимальная маршрутизация сигнала). Примерные варианты реализации уменьшают площадь, потребляемую мощность и увеличивают максимальную операционную скорость массива CAM. Кроме того, по меньшей мере, один примерный вариант реализации осуществлен, не требуя новой схемы декодирования. В одном варианте реализации может быть использован декодер прямого отображения посредством реконфигурации входного порядка адресной шины.

CAM с расслоенным набором в одном варианте реализации использует конструкцию массива с ассоциативным набором. Вместо вертикального размещения последовательных строк в пределах набора, как показано на Фиг.6, строки от двух вертикально-смежных наборов физически расслаиваются и ячейки массива CAM повернуты на 180° относительно своих соседних ячеек. Расслоенные пары наборов располагаются в стек вертикально для заполнения каждого банка CAM. По меньшей мере, в одном варианте реализации сигналы специального управления набором в пределах банка CAM вертикально выровнены так, как примерно показано на Фиг.7A и 7B.

На Фиг.7A показана блок-схема расслоенного массива 701 CAM. Массив 701 CAM имеет ячейки 710, 720, 730 и 740 CAM, причем каждая включает в себя схему сравнения и схему хранения (например, ячейку SRAM). Каждая ячейка массива CAM выполнена с возможностью обеспечения L-образной ячейки, которая больше в у-измерении, чем обычная ячейка RAM. Для уменьшения площади, используемой конструкцией, каждая смежная ячейка массива CAM повернута на 180° относительно соседней ячейки CAM. В связи с Фиг.7A ячейка 720 CAM повернута на 180° относительно ячейки 710 CAM и размещена в L-конфигурации со взаимозацеплением. Ячейка 740 массива CAM аналогично повернута на 180° относительно ячейки 730 массива CAM в L-конфигурации со взаимозацеплением, тем самым обеспечивая компактную конструкцию, в которой каждый блок смежных ячеек CAM (например, 710 и 720, 730 и 740 и т.д.) образует прямоугольную форму, имеющую высоту, равную приблизительно двойной высоте ячейки хранения (например, ячейки SRAM). Конфигурацию со взаимозацеплением L-образных ячеек CAM (например, 710 и 720) можно считать блоком 705 ячеек CAM, и блоки ячеек CAM могут быть расположены в стек для формирования массива CAM так, как показано на Фиг.8.

На Фиг.7B показана компоновка схемы расслоенной структуры 702 CAM. Расслоенные наборы, в соответствии с вариантами реализации изобретения, образуют ячейки CAM с вертикально выровненными сигналами сравнения наборов, снижают паразитную емкость и понижают потребляемую мощность конструкции. Посредством расслоения наборов сигналы сравнения, характерные для наборов (например, set0_compare 750 и set1_compare 760) вертикально выровнены. Дополнительно, поскольку одна линия используется на один компонент сравнения (например, compare_true), маршрутизация, используемая для линий сравнения, сокращается. Две L-образные ячейки совместно используют диффузионную область линии согласования, как рассмотрено выше в соответствии с Фиг.5A и 5B. Получающаяся физическая площадь массива и емкость в конструкции уменьшаются. Соответственно, варианты реализации изобретения, как показано на Фиг.7A и 7B, уменьшают паразитную емкость как линии согласования, так и линии сравнения.

Другой вариант реализации рассматривается в соответствии с Фиг.8. На Фиг.8 показан ассоциативный банк 800 массивов CAM с расслоенным 4-х канальным набором. На Фиг.8 показаны четыре строки в каждом наборе (4 канала), и каждая строка имеет ширину в четыре бита (например, четыре столбца). Смежные пары набора расслаиваются (набор 0/набор 1, набор 2/набор 3). Каждая ячейка CAM имеет ассоциированный набор и строку, и, как обсуждалось выше, каждый блок ячеек CAM имеет две ячейки CAM. Соответственно, массив 800 CAM может быть сформирован из множества блоков ячеек CAM, установленных так, чтобы соответствовать желаемому числу битов, наборов и строк. В расслоенной конструкции, в соответствии с вариантами реализации изобретения, каждый блок ячеек CAM имеет те же номера строк, но имеет последовательные номера наборов. Например, блок ячеек CAM может иметь первую ячейку CAM с набором <0>, строкой <0> и вторую ячейку CAM с набором <l>, строкой <0>. При размещении, как показано на Фиг.8, уникальный сигнал сравнения может быть предоставлен для каждого бита каждого набора. Кроме того, строки в данном бите и наборе (например, бит 0, набор 0, строки 1-4) принимают те же самые сигналы сравнения битового уровня. Таким образом, входы сравнения каждой строки в пределах набора вертикально выровнены и связаны с одной дорожкой маршрутизации на один бит.

Другие варианты реализации связаны с расслоенными наборами, которые являются несмежными наборами. Следует отметить, что любые два набора могут быть расслоенными. В другом варианте реализации расслаиваются два физически смежных набора, которые не являются логически смежными. Однако варианты реализации изобретения не ограничиваются 4-х канальным набором ассоциативных массивов CAM. Другие варианты реализации могут быть применены к другой ассоциативной памяти, например 2-х канальной, 16-ти канальной и т.д. Варианты реализации изобретения могут использовать преимущество в физической компоновке ячеек CAM для уменьшения емкости и улучшения рабочих характеристик в таких массивах ассоциативной памяти.

Как рассмотрено выше, схема расслоенного набора может быть применена к массиву CAM для предоставления компактной физической расстановки с полным соответствием высот строк CAM и RAM (например, на две ячейки), при снижении или минимизации маршрутизации и паразитной емкости. Сетевая емкость уменьшается с помощью совместного использования при поддержании нормальной минимальной (или уменьшенной) маршрутизации сигнала. Соответственно, варианты реализации изобретения уменьшают площадь, потребляемую мощность и позволяют иметь увеличенную операционную скорость конструкции CAM. Кроме того, по меньшей мере, один вариант реализации осуществляется с декодером прямого отображения.

На Фиг.9 показан декодер 900 прямого отображения. Декодер 900 прямого отображения использует 6-битовый адрес и декодирует на 64 выхода. Каждый выход соединен с одной из 64 строк в массиве памяти или кэше. Например, если логические адресные биты А<5:0> связаны с входами a5-a0 декодера, как показано, отображение информации коррелирует с физическим размещением, при котором наборы и строки размещены последовательно. Кэш имеет четыре набора, которые отображены логическими адресными битами А<5> и А<4>. Каждый из четырех наборов имеет шестнадцать строк (то есть строки 0-15, 16-31, 32-47 и 48-63), отображенные логическими адресными битами А<3:0>. Декодер 900 прямого отображения выполнен для последовательных адресов строк. Однако применение декодера 900 прямого отображения к расслоенному массиву CAM может привести к сложной маршрутизации выходных сигналов декодера.

На Фиг.10 показана блок-схема декодера 1000 прямого отображения, который может использоваться с массивом CAM расслоенного набора в соответствии, по меньшей мере, с одним вариантом реализации изобретения. Например, логические адресные биты А<5:0> могут быть переупорядочены для соответствия с массивом CAM расслоенного набора. Логические адресные биты А<5:0> могут быть переупорядочены и связаны с входами a5-a0 декодера, как показано на Фиг.10. Отображение коррелирует с физическим размещением, при котором наборы и строки размещены последовательно на основе схемы расслоенного набора. Кэш имеет четыре набора, которые отображены логическими адресными битами А<5> и А<4>. Каждый из четырех наборов имеет шестнадцать строк (то есть строки 0-15, 16-31, 32-47 и 48-63), отображенные логическими адресными битами А<3:0>. Логический адресный бит А<4> связан со входом a0. Логические адресные биты А<3:0>, каждый, сдвинуты на одно положение для соответствия входам a4-al соответственно. Логический адресный бит А<5> связан со входом a5. Например, если логические адресные биты А<5:0> связаны со входами a5-a0 декодера, как показано, отображение коррелирует с физическим размещением, имеющим чередующиеся наборы, где строки остаются теми же для каждой группы (например, блок ячеек) чередующихся наборов (например, набор <0>, строка <0>; набор <1>, строка <0>; набор <0>, строка <l>; набор <l>, строка <l> и т.д.). Поэтому расслоенный декодер 1000 на Фиг.10 может непосредственно отображать в массив CAM расслоенного набора и не приводит к сложной маршрутизации выходов декодера 1000. Таким образом, примерные варианты реализации расслаивают строки смежных наборов и изменяют порядок подключений адресной шины к декодеру 1000 для обеспечения правильного отображения в строки массива CAM.

В других вариантах реализации процессор включает в себя массив CAM в соответствии с описанными выше вариантами реализации. В данном случае процессор может включать в себя одну или несколько схем обработки, например микропроцессоры, процессоры цифровых сигналов (DSP), микроконтроллеры, специализированные интегральные схемы (ASICS) и их комбинации. Соответственно, вариант реализации может включать в себя процессор, содержащий массив CAM, имеющий множество блоков ячеек CAM, в котором каждый блок ячейки CAM включает в себя первую ячейку CAM, имеющую первую схему хранения и первую схему сравнения, и вторую ячейку CAM, имеющую вторую схему хранения и вторую схему сравнения. Каждая ячейка CAM может быть сконфигурирована как L-образная так, что первые и вторые ячейки CAM размещаются в конфигурации со взаимозацеплением, чтобы сформировать по существу прямоугольную форму, тем самым минимизируя физическую площадь массива и/или емкость в конструкции. Соответственно, описанные выше варианты реализации могут уменьшить паразитную емкость как в линии согласования, так и в линии сравнения в массиве CAM, интегрированной в процессор.

Другой вариант реализации относится к способу формирования массива CAM или процессора, включающего в себя массив CAM, имеющий множество ячеек CAM (например, первую и вторую ячейки CAM) в соответствии с описанными выше вариантами реализации, выполненные с возможностью уменьшения используемой площади, сложности маршрутизации и паразитной емкости.

Например, вариант реализации относится к способу, имеющему этапы формирования L-образной первой ячейки CAM, имеющей первую схему хранения и первую схему сравнения, и формирования второй L-образной ячейки CAM, имеющей вторую схему хранения и вторую схему сравнения. Способ включает в себя размещение первых и вторых ячеек CAM в конфигурации со взаимным зацеплением, чтобы сформировать по существу прямоугольную форму, в которой первая и вторая схемы хранения располагаются вертикально и первая и вторая схемы сравнения, каждая, размещаются на соответствующих внешних краях прямоугольника. Способ дополнительно включает в себя ассоциирование каждой ячейки CAM с набором и строкой.

Например, в одном варианте реализации первая ячейка CAM ассоциируется с первой строкой первого набора и вторая ячейка CAM соотносится со второй строкой первого набора. Вариант реализации включает в себя конфигурирование декодера, который имеет последовательные выходы данных, отображаемые в первую строку первого набора и во вторую строку первого набора.

В другом варианте реализации первая ячейка CAM ассоциируется с первой строкой первого набора и вторая ячейка CAM ассоциируется с первой строкой второго набора. Вариант реализации включает в себя конфигурирование декодера, который имеет последовательные выходы, отображаемые на первую строку первого набора и на первую строку второго набора. Соответственно, примерные способы могут предоставить массив CAM или процессор, имеющий массив CAM, в котором может быть уменьшена физическая площадь массива и/или емкость. Описанные выше варианты реализации могут уменьшить паразитную емкость как линии согласования, так и линии сравнения.

Следует отметить, что информация и сигналы могут быть представлены с использованием любых многочисленных технологий и методик. Например, данные, инструкции, команды, информация, сигналы, биты, символы и элементарные сигналы, которые могут иметь отношение к вышеприведенному описанию, могут быть представлены напряжениями, токами, электромагнитными волнами, магнитными полями или частицами, оптическими полями или частицами или любой их комбинацией.

Кроме того, следует отметить, что различные иллюстративные логические блоки, модули, схемы и этапы алгоритмов, описанные в связи с раскрытыми в этом документе вариантами реализации, могут быть реализованы как электронные аппаратные средства, программное обеспечение или комбинации того и другого. Чтобы ясно проиллюстрировать эту взаимозаменяемость аппаратных средств и программного обеспечения, различные иллюстративные компоненты, блоки, модули, схемы и этапы были описаны выше в целом, в смысле их функциональных возможностей. Осуществляются ли такие функциональные возможности в виде аппаратных средств или программного обеспечения зависит от конкретного применения и конструктивных ограничений, накладываемых на всю систему. Специалисты в данной области техники могут осуществить описанные функциональные возможности различным образом в каждом конкретном применении, но такие решения о конкретном осуществлении не должны интерпретироваться как основание для отклонения от объема вариантов реализации настоящего изобретения.

Хотя приведенное раскрытие показывает иллюстративные варианты реализации изобретения, следует отметить, что возможны различные изменения и модификации без отступления от объема изобретения, как это определено в прилагаемой формуле изобретения. Функции, этапы и/или действия заявленного способа в соответствии с описанными вариантами реализации изобретения не обязательно должны быть выполнены в какой-либо определенной последовательности. Кроме того, хотя элементы изобретения возможно и описаны, или заявлены, как индивидуальные, множественность при этом предполагается, если ограничение для индивидуального явно не заявлено.

Изобретение относится к архитектуре памяти и, более конкретно, к способам и системам для ассоциативной памяти (САМ). Техническим результатом является уменьшение паразитной емкости за счет уменьшения физической площади массива и/или емкости памяти. Ассоциативная память содержит: первую ячейку САМ, имеющую первую схему хранения и первую схему сравнения; и вторую ячейку САМ, имеющую вторую схему хранения и вторую схему сравнения, причем первая ячейка САМ и вторая ячейка САМ расположены, по существу, в прямоугольной области, причем первая и вторая схемы хранения расположены в стек вертикально и являются смежными друг с другом и причем первая и вторая схемы сравнения разделены первой и второй схемами хранения и каждая расположены на соответственных внешних краях, по существу, прямоугольной области. 3 н. и 25 з.п. ф-лы, 13 ил.

1. Ассоциативная память (САМ), содержащая:

первую ячейку САМ, имеющую первую схему хранения и первую схему сравнения, и вторую ячейку САМ, имеющую вторую схему хранения и вторую схему сравнения,

причем первая ячейка САМ и вторая ячейка САМ расположены, по существу, в прямоугольной области, причем первая и вторая схемы хранения расположены в стек вертикально и являются смежными друг с другом, и причем первая и вторая схемы сравнения разделены первой и второй схемами хранения, и, каждая, расположены на соответственных внешних краях, по существу, прямоугольной области.

2. Ассоциативная память по п.1, в которой строки первой и второй схем сравнения размещены последовательно.

3. Ассоциативная память по п.1, в которой первая ячейка САМ ассоциируется с первой строкой первого набора, и вторая ячейка САМ ассоциируется со второй строкой первого набора.

4. Ассоциативная память по п.1, в которой смежные наборы первой и второй схем сравнения размещены последовательно.

5. Ассоциативная память по п.1, в которой первая ячейка САМ ассоциируется с первой строкой первого набора, и вторая ячейка САМ ассоциируется с первой строкой второго набора.

6. Ассоциативная память по п.1, дополнительно содержащая:

множество первых и вторых ячеек САМ, как указано по п.1, причем каждая ячейка САМ имеет ассоциированный набор и строку, и причем входы сравнения каждой строки в пределах набора выровнены по вертикали.

7. Ассоциативная память по п.6, в которой каждый вход сравнения каждой строки в пределах одного набора соединен с одной дорожкой маршрутизации.

8. Ассоциативная память по п.1, в которой высота первой схемы сравнения больше высоты первой схемы хранения.

9. Ассоциативная память по п.1, в которой высота прямоугольной области приблизительно равна высоте схем хранения, расположенных в стек вертикально.

10. Ассоциативная память по п.1, в которой первая и вторая схемы хранения расположены в центральной части в пределах прямоугольной области.

11. Процессор, имеющий массив ассоциативной памяти (САМ), содержащий:

множество блоков ячеек САМ, причем каждый блок ячеек САМ включает в себя:

первую ячейку САМ, имеющую первую схему хранения и первую схему сравнения; и

вторую ячейку САМ, имеющую вторую схему хранения и вторую схему сравнения,

причем каждая ячейка САМ сконфигурирована в L-форме, и причем первая и вторая ячейки САМ размещены в конфигурации со взаимозацеплением, чтобы сформировать, по существу, прямоугольную форму, и причем первая и вторая схемы хранения являются смежными друг с другом, и первая и вторая схемы сравнения разделены первой и второй схемами хранения, и каждая схема сравнения расположена на соответственном внешнем крае, по существу, прямоугольной области.

12. Процессор по п.11, причем каждая ячейка САМ имеет ассоциированные набор и строку.

13. Процессор по п.12, в котором строки первой и второй схем сравнения размещены последовательно.

14. Процессор по п.12, в котором первая ячейка САМ ассоциируется с первой строкой первого набора, и вторая ячейка САМ ассоциируется со второй строкой первого набора.

15. Процессор по п.14, дополнительно содержащий:

декодер, сконфигурированный с возможностью прямого отображения в строки первой и второй ячеек САМ.

16. Процессор по п.15, причем декодер сконфигурирован с возможностью иметь последовательные выходы, отображаемые в первую строку первого набора и во вторую строку первого набора.

17. Процессор по п.12, в котором смежные наборы первой и второй схем сравнения размещены последовательно.

18. Процессор по п.12, в котором первая ячейка САМ ассоциируется с первой строкой первого набора, и вторая ячейка САМ ассоциируется с первой строкой второго набора.

19. Процессор по п.18, дополнительно содержащий:

декодер, сконфигурированный с возможностью непосредственного отображения в строки первой и второй ячеек САМ.

20. Процессор по п.19, причем декодер сконфигурирован с возможностью иметь последовательные выходы, отображаемые в первую строку первого набора и в первую строку второго набора.

21. Процессор по п.11, в котором, по меньшей мере, два блока ячеек САМ расположены в стек вертикально, и в котором входы каждой строки в пределах набора выровнены по вертикали.

22. Процессор по п.11, содержащий:

первый блок ячеек САМ и второй блок ячеек САМ из множества блоков ячеек САМ, размещенных вертикально, причем первая и вторая ячейки САМ первого и второго блоков ячеек САМ выровнены по вертикали.

23. Способ создания ассоциативной памяти (САМ), содержащий этапы, на которых:

формируют L-образную первую ячейку САМ, имеющую первую схему хранения и первую схему сравнения;

формируют L-образную вторую ячейку САМ, имеющую вторую схему хранения и вторую схему сравнения; и

размещают первую и вторую ячейки САМ в конфигурации со взаимозацеплением, чтобы сформировать, по существу, прямоугольную форму;

располагают в стек вертикально первую и вторую схемы хранения и смежно друг с другом; и

располагают первую и вторую схемы сравнения на соответственных внешних краях, по существу, прямоугольной формы, так что они разделены первой и второй схемами хранения.

24. Способ по п.23, дополнительно содержащий этап, на котором:

ассоциируют каждую ячейку САМ с набором и строкой.

25. Способ по п.24, в котором первая ячейка САМ ассоциируется с первой строкой первого набора, и вторая ячейка САМ ассоциируется со второй строкой первого набора.

26. Способ по п.25, дополнительно содержащий этап, на котором:

конфигурируют декодер для прямого отображения в строки первой и второй ячеек САМ, причем декодер сконфигурирован с возможностью иметь последовательные выходы, отображаемые в первую строку первого набора и во вторую строку первого набора.

27. Способ по п.24, в котором первая ячейка САМ ассоциируется с первой строкой первого набора, и вторая ячейка САМ ассоциируется с первой строкой второго набора.

28. Способ по п.27, дополнительно содержащий этап, на котором:

конфигурируют декодер, чтобы иметь последовательные выходы, отображаемые в первую строку первого набора и в первую строку второго набора.

| US 7126837 B1, 24.10.2006 | |||

| US 6249450 B1, 19.06.2001 | |||

| УСТРОЙСТВО АССОЦИАТИВНОЙ ПАМЯТИ (ВАРИАНТЫ) И СПОСОБ РАСПОЗНАВАНИЯ ОБРАЗОВ (ВАРИАНТЫ) | 1991 |

|

RU2193797C2 |

| RU 97112940 A, 20.06.1999. | |||

Авторы

Даты

2012-05-27—Публикация

2007-11-19—Подача